Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 80KB (40K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2682-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 2.6 Internal Oscillator Block

The PIC18F2682/2685/4682/4685 devices include an internal oscillator block which generates two different clock signals; either can be used as the microcontroller's clock source. This may eliminate the need for external oscillator circuits on the OSC1 and/or OSC2 pins.

The main output (INTOSC) is an 8 MHz clock source, which can be used to directly drive the device clock. It also drives a postscaler, which can provide a range of clock frequencies from 31 kHz to 4 MHz. The INTOSC output is enabled when a clock frequency from 125 kHz to 8 MHz is selected.

The other clock source is the internal RC oscillator (INTRC), which provides a nominal 31 kHz output. INTRC is enabled if it is selected as the device clock source; it is also enabled automatically when any of the following are enabled:

- Power-up Timer

- · Fail-Safe Clock Monitor

- Watchdog Timer

- Two-Speed Start-up

These features are discussed in greater detail in Section 24.0 "Special Features of the CPU".

The clock source frequency (INTOSC direct, INTRC direct or INTOSC postscaler) is selected by configuring the IRCF bits of the OSCCON register (Register 2-2).

#### 2.6.1 INTIO MODES

Using the internal oscillator as the clock source eliminates the need for up to two external oscillator pins, which can then be used for digital I/O. Two distinct configurations are available:

- In INTIO1 mode, the OSC2 pin outputs Fosc/4, while OSC1 functions as RA7 for digital input and output.

- In INTIO2 mode, OSC1 functions as RA7 and OSC2 functions as RA6, both for digital input and output.

#### 2.6.2 INTOSC OUTPUT FREQUENCY

The internal oscillator block is calibrated at the factory to produce an INTOSC output frequency of 8.0 MHz.

The INTRC oscillator operates independently of the INTOSC source. Any changes in INTOSC across voltage and temperature are not necessarily reflected by changes in INTRC and vice versa.

#### 2.6.3 OSCTUNE REGISTER

The internal oscillator's output has been calibrated at the factory but can be adjusted in the user's application. This is done by writing to the OSCTUNE register (Register 2-1). The tuning sensitivity is constant throughout the tuning range. When the OSCTUNE register is modified, the INTOSC and INTRC frequencies will begin shifting to the new frequency. The INTRC clock will reach the new frequency within 8 clock cycles (approximately  $8 * 32 \ \mu s = 256 \ \mu s$ ). The INTOSC clock will stabilize within 1 ms. Code execution continues during this shift. There is no indication that the shift has occurred.

The OSCTUNE register also implements the INTSRC and PLLEN bits, which control certain features of the internal oscillator block. The INTSRC bit allows users to select which internal oscillator provides the clock source when the 31 kHz frequency option is selected. This is covered in greater detail in **Section 2.7.1 "Oscillator Control Register"**.

The PLLEN bit controls the operation of the frequency multiplier, PLL, in internal oscillator modes.

#### 2.6.4 PLL IN INTOSC MODES

The 4x frequency multiplier can be used with the internal oscillator block to produce faster device clock speeds than are normally possible with an internal oscillator. When enabled, the PLL produces a clock speed of up to 32 MHz.

Unlike HSPLL mode, the PLL is controlled through software. The control bit, PLLEN (OSCTUNE<6>), is used to enable or disable its operation.

The PLL is available when the device is configured to use the internal oscillator block as its primary clock source (FOSC3:FOSC0 = 1001 or 1000). Additionally, the PLL will only function when the selected output frequency is either 4 MHz or 8 MHz (OSCCON<6:4> = 111 or 110). If both of these conditions are not met, the PLL is disabled.

The PLLEN control bit is only functional in those internal oscillator modes where the PLL is available. In all other modes, it is forced to '0' and is effectively unavailable.

#### 2.6.5 INTOSC FREQUENCY DRIFT

The factory calibrates the internal oscillator block output (INTOSC) for 8 MHz. However, this frequency may drift as VDD or temperature changes, which can affect the controller operation in a variety of ways. It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register. This has no effect on the INTRC clock source frequency.

Tuning the INTOSC source requires knowing when to make the adjustment, in which direction it should be made and in some cases, how large a change is needed. Three compensation techniques are discussed in Section 2.6.5.1 "Compensating with the EUSART", Section 2.6.5.2 "Compensating with the Timers" and Section 2.6.5.3 "Compensating with the CCP1 Module in Capture Mode", but other techniques may be used.

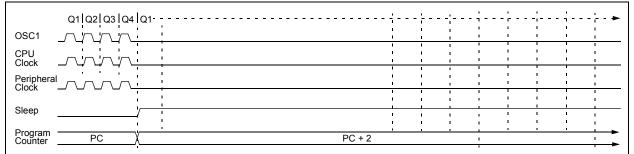

#### 3.3 Sleep Mode

The power-managed Sleep mode in the PIC18F2682/ 2685/4682/4685 devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 3-5). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

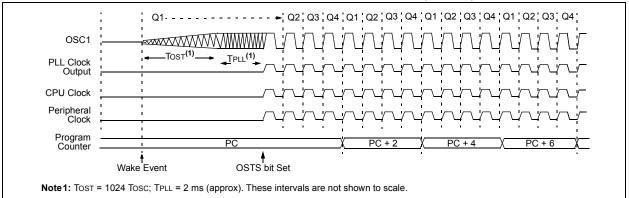

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS1:SCS0 bits becomes ready (see Figure 3-6), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see Section 24.0 "Special Features of the CPU"). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

#### 3.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS1:SCS0 bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD (parameter 38, Table 27-10) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT timeout will result in a WDT wake-up to the Run mode currently specified by the SCS1:SCS0 bits.

FIGURE 3-5: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

#### TRANSITION TIMING FOR WAKE FROM SLEEP (HSPLL)

#### 5.3 Data Memory Organization

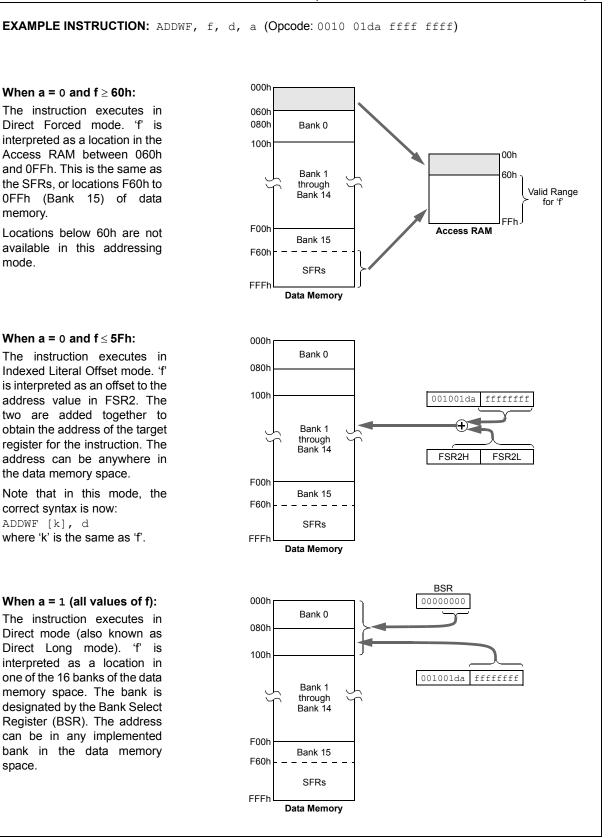

Note: The operation of some aspects of data memory are changed when the PIC18 extended instruction set is enabled. See Section 5.6 "Data Memory and the Extended Instruction Set" for more information.

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The memory space is divided into as many as 16 banks that contain 256 bytes each; PIC18F2682/2685/4682/4685 devices implement all 16 banks. Figure 5-5 shows the data memory organization for the PIC18F2682/2685/4682/4685 devices.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this subsection.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to SFRs and the lower portion of GPR Bank 0 without using the BSR. **Section 5.3.2 "Access Bank"** provides a detailed description of the Access RAM.

#### 5.3.1 BANK SELECT REGISTER (BSR)

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit low-order address and a 4-bit Bank Pointer.

Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the 4 Most Significant bits of a location's address; the instruction itself includes the 8 Least Significant bits. Only the four lower bits of the BSR are implemented (BSR3:BSR0). The upper four bits are unused; they will always read '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory. The 8 bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is shown in Figure 5-6.

Since up to 16 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h while the BSR is 0Fh, will end up resetting the program counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory map in Figure 5-5 indicates which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. This instruction ignores the BSR completely when it executes. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

| TABLE 5-1: | SPECIAL FUNCTION REGISTER MAP FOR             |

|------------|-----------------------------------------------|

|            | PIC18F2682/2685/4682/4685 DEVICES (CONTINUED) |

| D7Fh —<br>D7Eh —<br>D7Eh —<br>D7Dh —<br>D7Ch —<br>D7Ch —<br>D7Bh RXF11EIDL<br>D7Ah RXF11EIDH<br>D7Ah RXF11SIDL<br>D7Ah RXF11SIDL<br>D7Ah RXF10EIDL<br>D78h RXF10EIDL<br>D76h RXF10EIDH<br>D75h RXF10SIDL<br>D74h RXF10SIDL<br>D74h RXF9EIDL<br>D72h RXF9EIDL<br>D72h RXF9EIDL<br>D72h RXF9EIDL<br>D71h RXF9SIDL<br>D70h RXF9SIDL<br>D70h RXF9SIDL<br>D6Eh —<br>D6Eh —<br>D6Eh —<br>D6Bh RXF8SIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8SIDL<br>D68h RXF8SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D61h RXF6SIDL | Address | Name      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|

| D7Dh —<br>D7Ch —<br>D7Bh RXF11EIDL<br>D7Ah RXF11EIDL<br>D7Ah RXF11SIDL<br>D79h RXF11SIDL<br>D79h RXF11SIDH<br>D79h RXF10EIDL<br>D77h RXF10EIDL<br>D76h RXF10EIDH<br>D75h RXF10SIDH<br>D75h RXF10SIDH<br>D73h RXF9EIDL<br>D74h RXF9EIDL<br>D72h RXF9EIDH<br>D71h RXF9SIDL<br>D70h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Bh RXF8SIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDL<br>D66h RXF7EIDL<br>D66h RXF7EIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL                                                                                                                                                        | D7Fh    | _         |

| D7Ch —<br>D7Bh RXF11EIDL<br>D7Ah RXF11EIDH<br>D79h RXF11SIDL<br>D78h RXF11SIDH<br>D79h RXF10EIDL<br>D78h RXF10EIDL<br>D76h RXF10EIDH<br>D75h RXF10SIDL<br>D74h RXF10SIDH<br>D73h RXF9EIDL<br>D72h RXF9EIDL<br>D72h RXF9EIDH<br>D71h RXF9SIDL<br>D70h RXF9SIDL<br>D6Fh —<br>D6Eh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF7EIDH<br>D65h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL                                                                                                                                                                                                            | D7Eh    | _         |

| D7BhRXF11EIDLD7AhRXF11EIDHD79hRXF11SIDLD79hRXF11SIDLD78hRXF10EIDLD77hRXF10EIDLD76hRXF10EIDHD75hRXF10SIDLD74hRXF9EIDLD72hRXF9EIDLD72hRXF9SIDLD70hRXF9SIDLD70hRXF9SIDLD6EhD6BhRXF8EIDLD6AhRXF8EIDLD6AhRXF8EIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF78IDLD6AhRXF78IDLD6AhRXF78IDLD6AhRXF78IDLD6AhRXF78IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDL                                                                                                                                                                                                                                                       | D7Dh    | _         |

| D7Ah RXF11EIDH<br>D79h RXF11SIDL<br>D78h RXF11SIDL<br>D78h RXF10EIDL<br>D77h RXF10EIDL<br>D76h RXF10EIDH<br>D75h RXF10SIDL<br>D74h RXF10SIDH<br>D73h RXF9EIDL<br>D72h RXF9EIDL<br>D72h RXF9EIDH<br>D71h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Bh RXF8SIDH<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDL<br>D66h RXF7EIDL<br>D66h RXF7EIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF6EIDL                                                                                                                                                             | D7Ch    | —         |

| D79hRXF11SIDLD78hRXF11SIDHD77hRXF10EIDLD77hRXF10EIDLD76hRXF10SIDLD75hRXF10SIDLD74hRXF9EIDLD73hRXF9EIDLD72hRXF9EIDHD71hRXF9SIDLD70hRXF9SIDHD6EhD6DhD6BhRXF8EIDLD6AhRXF8EIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF8SIDLD6AhRXF78IDLD6AhRXF78IDLD6AhRXF75IDLD6AhRXF7EIDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF75IDLD6AhRXF6EIDLD6AhRXF6EIDLD6AhRXF6EIDL                                                                                                                                                                                                                                                                                                     | D7Bh    | RXF11EIDL |

| D78hRXF11SIDHD77hRXF10EIDLD77hRXF10EIDLD76hRXF10SIDLD75hRXF10SIDLD74hRXF9EIDLD73hRXF9EIDLD72hRXF9EIDHD71hRXF9SIDLD70hRXF9SIDLD70hRXF9SIDLD6EhD6ChD6BhRXF8EIDLD6AhRXF8EIDLD6AhRXF8EIDLD6AhRXF8EIDLD6AhRXF8SIDLD6AhRXF8EIDHD69hRXF8SIDLD64hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDLD63hRXF6EIDLD63hRXF6EIDLD63hRXF6EIDLD63hRXF6EIDLD63hRXF6EIDLD63hRXF6EIDLD63hRXF6EIDLD63hRXF6EIDLD63hRXF6EIDLD63hRXF6EIDL                                                                                                                                                                                                                                                                                                                  | D7Ah    | RXF11EIDH |

| D77h RXF10EIDL<br>D76h RXF10EIDH<br>D75h RXF10SIDL<br>D74h RXF10SIDH<br>D73h RXF9EIDL<br>D72h RXF9EIDH<br>D72h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Eh —<br>D6Ch —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8SIDL<br>D6Ah RXF8SIDL<br>D68h RXF8SIDL<br>D66h RXF7EIDH<br>D67h RXF7EIDH<br>D65h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D61h RXF6EIDH                                                                                                                                                                                                                                                          | D79h    | RXF11SIDL |

| D76h RXF10EIDH<br>D75h RXF10SIDL<br>D74h RXF10SIDH<br>D73h RXF9EIDL<br>D72h RXF9EIDH<br>D72h RXF9EIDH<br>D71h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Eh —<br>D6Bh RXF8SIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8SIDL<br>D6Ah RXF8SIDL<br>D66h RXF7EIDH<br>D67h RXF7EIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF6EIDL                                                                                                                                                                                                                                                                                                                 | D78h    | RXF11SIDH |

| D75h RXF10SIDL<br>D74h RXF10SIDH<br>D73h RXF9EIDL<br>D72h RXF9EIDH<br>D71h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDL<br>D66h RXF7EIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDH<br>D63h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                  | D77h    | RXF10EIDL |

| D74h RXF10SIDH<br>D73h RXF9EIDL<br>D72h RXF9EIDH<br>D71h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Dh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8SIDL<br>D6Ah RXF8SIDL<br>D68h RXF8SIDL<br>D66h RXF7EIDH<br>D65h RXF7EIDH<br>D65h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL<br>D66h RXF7SIDL                                                                                                                                                                                                                                                                                                                                           | D76h    | RXF10EIDH |

| D73h RXF9EIDL<br>D72h RXF9EIDH<br>D71h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Dh —<br>D6Ch —<br>D6Ch —<br>D6Ch —<br>D6Gh RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDH<br>D69h RXF8SIDL<br>D68h RXF7EIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                         | D75h    | RXF10SIDL |

| D72h RXF9EIDH<br>D71h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Dh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF7EIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                              | D74h    | RXF10SIDH |

| D71h RXF9SIDL<br>D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Dh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDL<br>D6Ah RXF8SIDL<br>D6Ah RXF8SIDL<br>D69h RXF8SIDL<br>D68h RXF7EIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDH<br>D63h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                               | D73h    | RXF9EIDL  |

| D70h RXF9SIDH<br>D6Fh —<br>D6Eh —<br>D6Dh —<br>D6Dh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDH<br>D67h RXF7EIDH<br>D65h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF6EIDH<br>D63h RXF6EIDL                                                                                                                                                                                                                                                                                                                                                                                                                                        | D72h    | RXF9EIDH  |

| D6Fh —<br>D6Eh —<br>D6Dh —<br>D6Dh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDL<br>D68h RXF8SIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDH<br>D63h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                        | D71h    | RXF9SIDL  |

| D6Eh —<br>D6Dh —<br>D6Dh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D69h RXF8SIDL<br>D68h RXF8SIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D70h    | RXF9SIDH  |

| D6Dh —<br>D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D69h RXF8SIDL<br>D68h RXF8SIDH<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDH<br>D63h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D6Fh    | —         |

| D6Ch —<br>D6Bh RXF8EIDL<br>D6Ah RXF8EIDH<br>D69h RXF8SIDL<br>D68h RXF8SIDL<br>D67h RXF7EIDL<br>D66h RXF7EIDH<br>D65h RXF7SIDL<br>D64h RXF7SIDL<br>D64h RXF7SIDL<br>D63h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D6Eh    | —         |

| D6BhRXF8EIDLD6AhRXF8EIDHD69hRXF8SIDLD69hRXF8SIDLD68hRXF78IDLD67hRXF7EIDHD66hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D6Dh    | _         |

| D6AhRXF8EIDHD69hRXF8SIDLD69hRXF8SIDHD68hRXF7EIDLD67hRXF7EIDHD66hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D6Ch    | _         |

| D69hRXF8SIDLD68hRXF8SIDHD67hRXF7EIDLD66hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D6Bh    | RXF8EIDL  |

| D68hRXF8SIDHD67hRXF7EIDLD66hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D6Ah    | RXF8EIDH  |

| D67hRXF7EIDLD66hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D69h    | RXF8SIDL  |

| D66hRXF7EIDHD65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D68h    | RXF8SIDH  |

| D65hRXF7SIDLD64hRXF7SIDHD63hRXF6EIDLD62hRXF6EIDHD61hRXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D67h    | RXF7EIDL  |

| D64h RXF7SIDH<br>D63h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D66h    | RXF7EIDH  |

| D63h RXF6EIDL<br>D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | D65h    | RXF7SIDL  |

| D62h RXF6EIDH<br>D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D64h    | RXF7SIDH  |

| D61h RXF6SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D63h    | RXF6EIDL  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | D62h    | RXF6EIDH  |

| D60h RXF6SIDH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D61h    | RXF6SIDL  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | D60h    | RXF6SIDH  |

**Note 1:** Registers available only on PIC18F4X8X devices; otherwise, the registers read as '0'.

2: When any TX\_ENn bit in RX\_TX\_SELn is set, then the corresponding bit in this register has transmit properties.

3: This is not a physical register.

# PIC18F2682/2685/4682/4685

| File Name            | Bit 7                 | Bit 6                           | Bit 5          | Bit 4           | Bit 3                 | Bit 2                 | Bit 1              | Bit 0                  | Value on<br>POR, BOR | Details<br>on page: |

|----------------------|-----------------------|---------------------------------|----------------|-----------------|-----------------------|-----------------------|--------------------|------------------------|----------------------|---------------------|

| SPBRGH               | EUSART Bau            | ud Rate Gene                    | rator Register | High Byte       |                       |                       |                    |                        | 0000 0000            | 53, 233             |

| SPBRG                | EUSART Bau            | ud Rate Gene                    | rator Register | · Low Byte      |                       |                       |                    |                        | 0000 0000            | 53, 233             |

| RCREG                | EUSART Red            | ceive Register                  |                |                 |                       |                       |                    |                        | 0000 0000            | 53, 240             |

| TXREG                | EUSART Tra            | nsmit Registe                   | r              |                 |                       |                       |                    |                        | 0000 0000            | 53, 238             |

| TXSTA                | CSRC                  | TX9                             | TXEN           | SYNC            | SENDB                 | BRGH                  | TRMT               | TX9D                   | 0000 0010            | 53, 239             |

| RCSTA                | SPEN                  | RX9                             | SREN           | CREN            | ADDEN                 | FERR                  | OERR               | RX9D                   | 0000 000x            | 53, 239             |

| EEADRH               | _                     | _                               | —              | _               | _                     | _                     | EEPROM Addr        | Register High Byte     | 00                   | 53, 110             |

| EEADR                | EEPROM Ad             | EPROM Address Register Low Byte |                |                 |                       |                       |                    |                        |                      |                     |

| EEDATA               | EEPROM Data Register  |                                 |                |                 |                       |                       |                    |                        |                      | 53, 107             |

| EECON2               | EEPROM Co             | ontrol Register                 | 2 (not a phys  | sical register) |                       |                       |                    |                        | 0000 0000            | 53, 107             |

| EECON1               | EEPGD                 | CFGS                            | —              | FREE            | WRERR                 | WREN                  | WR                 | RD                     | xx-0 x000            | 53, 107             |

| IPR3<br>Mode 0       | IRXIP                 | WAKIP                           | ERRIP          | TXB2IP          | TXB1IP                | TXB0IP                | RXB1IP             | RXB0IP                 | 1111 1111            | 53, 128             |

| IPR3<br>Mode 1, 2    | IRXIP                 | WAKIP                           | ERRIP          | TXBnIP          | TXB1IP <sup>(8)</sup> | TXB0IP <sup>(8)</sup> | RXBnIP             | FIFOWMIP               | 1111 1111            | 53, 128             |

| PIR3<br>Mode 0       | IRXIF                 | WAKIF                           | ERRIF          | TXB2IF          | TXB1IF                | TXB0IF                | RXB1IF             | RXB0IF                 | 0000 0000            | 53, 122             |

| PIR3<br>Mode 1, 2    | IRXIF                 | WAKIF                           | ERRIF          | TXBnlF          | TXB1IF <sup>(8)</sup> | TXB0IF <sup>(8)</sup> | RXBnIF             | FIFOWMIF               | 0000 0000            | 53, 122             |

| PIE3<br>Mode 0       | IRXIE                 | WAKIE                           | ERRIE          | TXB2IE          | TXB1IE                | TXB0IE                | RXB1IE             | RXB0IE                 | 0000 0000            | 53, 125             |

| PIE3<br>Mode 1, 2    | IRXIE                 | WAKIE                           | ERRIE          | TXBnIE          | TXB1IE <sup>(8)</sup> | TXB0IE <sup>(8)</sup> | RXBnIE             | FIFOMWIE               | 0000 0000            | 53, 125             |

| IPR2                 | OSCFIP                | CMIP <sup>(9)</sup>             | —              | EEIP            | BCLIP                 | HLVDIP                | TMR3IP             | ECCP1IP <sup>(9)</sup> | 11-1 1111            | 53, 127             |

| PIR2                 | OSCFIF                | CMIF <sup>(9)</sup>             | _              | EEIF            | BCLIF                 | HLVDIF                | TMR3IF             | ECCP1IF <sup>(9)</sup> | 00-0 0000            | 54, 121             |

| PIE2                 | OSCFIE                | CMIE <sup>(9)</sup>             | _              | EEIE            | BCLIE                 | HLVDIE                | TMR3IE             | ECCP1IE <sup>(9)</sup> | 00-0 0000            | 54, 124             |

| IPR1                 | PSPIP <sup>(3)</sup>  | ADIP                            | RCIP           | TXIP            | SSPIP                 | CCP1IP                | TMR2IP             | TMR1IP                 | 1111 1111            | 54, 126             |

| PIR1                 | PSPIF <sup>(3)</sup>  | ADIF                            | RCIF           | TXIF            | SSPIF                 | CCP1IF                | TMR2IF             | TMR1IF                 | 0000 0000            | 54, 120             |

| PIE1                 | PSPIE <sup>(3)</sup>  | ADIE                            | RCIE           | TXIE            | SSPIE                 | CCP1IE                | TMR2IE             | TMR1IE                 | 0000 0000            | 54, 123             |

| OSCTUNE              | INTSRC                | PLLEN <sup>(4)</sup>            | —              | TUN4            | TUN3                  | TUN2                  | TUN1               | TUN0                   | 0q-0 0000            | 29, 54              |

| TRISE <sup>(3)</sup> | IBF                   | OBF                             | IBOV           | PSPMODE         | _                     | TRISE2                | TRISE1             | TRISE0                 | 0000 -111            | 54, 143             |

| TRISD <sup>(3)</sup> | PORTD Data            | Direction Reg                   | gister         |                 |                       |                       |                    | <u>.</u>               | 1111 1111            | 54, 140             |

| TRISC                | PORTC Data            | Direction Reg                   | gister         |                 |                       |                       |                    |                        | 1111 1111            | 54, 137             |

| TRISB                | PORTB Data            | Direction Reg                   | gister         |                 |                       |                       |                    |                        | 1111 1111            | 54, 134             |

| TRISA                | TRISA7 <sup>(6)</sup> | TRISA6 <sup>(6)</sup>           | PORTA Data     | a Direction Reg | gister                |                       |                    |                        | 1111 1111            | 54, 131             |

| LATE <sup>(3)</sup>  | _                     | —                               | —              | —               | —                     | LATE Data Out         | put Register       |                        | xxx                  | 54, 143             |

| LATD <sup>(3)</sup>  | LATD Data O           | utput Registe                   | r              |                 |                       |                       |                    |                        | XXXX XXXX            | 54, 140             |

| LATC                 |                       | utput Registe                   |                |                 |                       |                       |                    |                        | xxxx xxxx            | 54, 137             |

| LATB                 | LATB Data O           | utput Register                  | r              |                 |                       |                       |                    |                        | XXXX XXXX            | 54, 134             |

| LATA                 | LATA7 <sup>(6)</sup>  | LATA6 <sup>(6)</sup>            | LATA Data (    | Dutput Registe  | r                     |                       |                    |                        | XXXX XXXX            | 54, 131             |

| PORTE <sup>(3)</sup> | _                     |                                 | _              | _               | RE3 <sup>(5)</sup>    | RE2 <sup>(3)</sup>    | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup>     | xxxx                 | 54, 147             |

| PORTD <sup>(3)</sup> | RD7                   | RD6                             | RD5            | RD4             | RD3                   | RD2                   | RD1                | RD0                    | XXXX XXXX            | 54, 140             |

| PORTC                | RC7                   | RC6                             | RC5            | RC4             | RC3                   | RC2                   | RC1                | RC0                    | XXXX XXXX            | 54, 137             |

#### TABLE 5-2:REGISTER FILE SUMMARY (PIC18F2682/2685/4682/4685) (CONTINUED)

$Legend: \ x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as '0'.$

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2682/2685 devices and are read as '0'. Reset values are shown for PIC18F4682/4685 devices; individual unimplemented bits should be interpreted as '---'.

4: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

9: These registers and/or bits are available on PIC18F4682/4685 devices only.

# PIC18F2682/2685/4682/4685

#### FIGURE 5-8: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

### 9.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxIF, is set. This interrupt can be disabled by clearing the corresponding enable bit INTxIE. Flag bit, INTxIF, must be cleared in software in the Interrupt.

All external interrupts (INT0, INT1 and INT2) can wake-up the processor from the power-managed modes if bit INTxIE was set prior to going into the power-managed modes. If the Global Interrupt Enable bit, GIE, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high priority interrupt source.

### 9.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 11.0 "Timer0 Module" for further details on the Timer0 module.

#### 9.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

### 9.9 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (See Section 5.3 "Data Memory Organization"), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 9-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| W_TEMP              | ; W_TEMP is in virtual bank                                                   |

|---------------------|-------------------------------------------------------------------------------|

| STATUS, STATUS_TEMP | ; STATUS_TEMP located anywhere                                                |

| BSR, BSR TEMP       | ; BSR TMEP located anywhere                                                   |

|                     |                                                                               |

| ISR CODE            |                                                                               |

|                     |                                                                               |

| BSR_TEMP, BSR       | ; Restore BSR                                                                 |

| W_TEMP, W           | ; Restore WREG                                                                |

| STATUS TEMP, STATUS | ; Restore STATUS                                                              |

|                     | STATUS, STATUS_TEMP<br>BSR, BSR_TEMP<br>SR CODE<br>BSR_TEMP, BSR<br>W_TEMP, W |

EXAMPLE 9-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

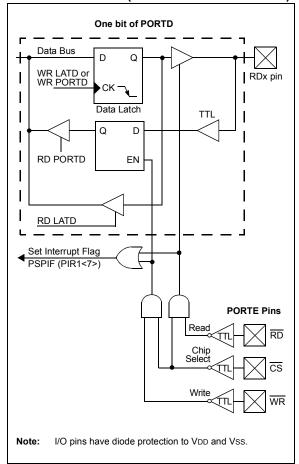

#### **10.6 Parallel Slave Port**

| Note: | The Parallel Slave Port is only available on |

|-------|----------------------------------------------|

|       | PIC18F4682/4685 devices.                     |

In addition to its function as a general I/O port, PORTD can also operate as an 8-bit wide Parallel Slave Port (PSP) or microprocessor port. PSP operation is controlled by the 4 upper bits of the TRISE register (Register 10-1). Setting control bit, PSPMODE (TRISE<4>), enables PSP operation, as long as the Enhanced CCP1 (ECCP1) module is not operating in dual output or quad output PWM mode. In Slave mode, the port is asynchronously readable and writable by the external world.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting the control bit, PSPMODE, enables the PORTE I/O pins to become control inputs for the microprocessor port. When set, port pin RE0 is the RD input, RE1 is the WR input and RE2 is the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PFCG3:PFCG0 (ADCON1<3:0>), must also be set to '1010'.

A write to the PSP occurs when both the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits are both set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit is set. If the user writes new data to PORTD to set OBF, the data is immediately read out; however, the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  line is detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP. When this happens, the IBF and OBF bits can be polled and the appropriate action taken. The timing for the control signals in Write and Read modes is shown in Figure 10-3 and Figure 10-4, respectively.

# PIC18F2682/2685/4682/4685

NOTES:

| Name                    | Bit 7                | Bit 6                                            | Bit 5         | Bit 4         | Bit 3    | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on page |

|-------------------------|----------------------|--------------------------------------------------|---------------|---------------|----------|---------|---------|---------|----------------------------|

| INTCON                  | GIE/GIEH             | PEIE/GIEL                                        | TMR0IE        | INT0IE        | RBIE     | TMR0IF  | INT0IF  | RBIF    | 51                         |

| RCON                    | IPEN                 | SBOREN <sup>(2)</sup>                            | _             | RI            | TO       | PD      | POR     | BOR     | 52                         |

| PIR1                    | PSPIF <sup>(1)</sup> | ADIF                                             | RCIF          | TXIF          | SSPIF    | CCP1IF  | TMR2IF  | TMR1IF  | 54                         |

| PIE1                    | PSPIE <sup>(1)</sup> | ADIE                                             | RCIE          | TXIE          | SSPIE    | CCP1IE  | TMR2IE  | TMR1IE  | 54                         |

| IPR1                    | PSPIP <sup>(1)</sup> | ADIP                                             | RCIP          | TXIP          | SSPIP    | CCP1IP  | TMR2IP  | TMR1IP  | 54                         |

| TRISB                   | PORTB Dat            | a Direction R                                    | egister       |               |          |         |         |         | 54                         |

| TRISC                   | PORTC Da             | ta Direction R                                   | egister       |               |          |         |         |         | 54                         |

| TMR2                    | Timer2 Reg           | ister                                            |               |               |          |         |         |         | 52                         |

| PR2                     | Timer2 Peri          | od Register                                      |               |               |          |         |         |         | 52                         |

| T2CON                   | —                    | T2OUTPS3                                         | T2OUTPS2      | T2OUTPS1      | T2OUTPS0 | TMR2ON  | T2CKPS1 | T2CKPS0 | 52                         |

| CCPR1L                  | Capture/Co           | mpare/PWM                                        | Register 1 Lo | ow Byte       |          |         |         |         | 53                         |

| CCPR1H                  | Capture/Co           | mpare/PWM                                        | Register 1 H  | igh Byte      |          |         |         |         | 53                         |

| CCP1CON                 | —                    | —                                                | DC1B1         | DC1B0         | CCP1M3   | CCP1M2  | CCP1M1  | CCP1M0  | 53                         |

| ECCPR1L <sup>(1)</sup>  | Enhanced (           | Enhanced Capture/Compare/PWM Register 1 Low Byte |               |               |          |         |         |         |                            |

| ECCPR1H <sup>(1)</sup>  | Enhanced (           | Capture/Comp                                     | oare/PWM R    | egister 1 Hig | h Byte   |         |         |         | 53                         |

| ECCP1CON <sup>(1)</sup> | EPWM1M1              | EPWM1M0                                          | EDC1B1        | EDC1B0        | ECCP1M3  | ECCP1M2 | ECCP1M1 | ECCP1M0 | 53                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PWM or Timer2.

**Note 1:** These bits or registers are available on PIC18F4682/4685 devices only.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'.

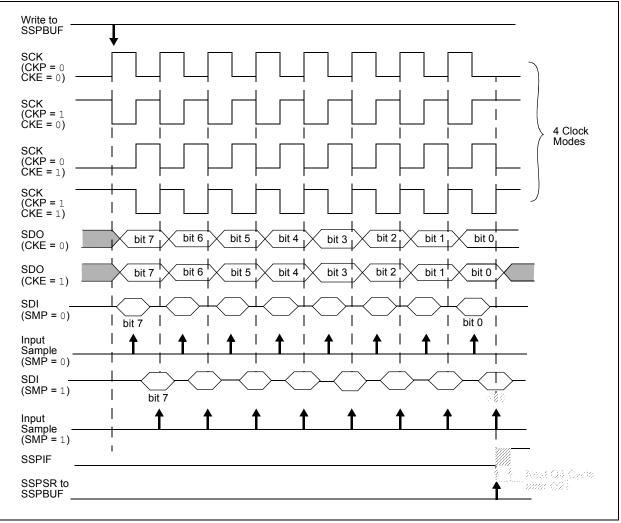

#### 17.3.5 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 17-2) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode. The clock polarity is selected by appropriately programming the CKP bit (SSPCON1<4>). This then, would give waveforms for SPI communication as shown in Figure 17-3, Figure 17-5 and Figure 17-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user-programmable to be one of the following:

- · Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

Figure 17-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

FIGURE 17-3: SPI MODE WAVEFORM (MASTER MODE)

## REGISTER 23-16: RXBnSIDL: RECEIVE BUFFER n STANDARD IDENTIFIER REGISTERS,

| R-x                                                                                                                                                   | R-x                                   | R-x                                                    | R-x            | R-x              | U-0           | R-x          | R-x           |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------|----------------|------------------|---------------|--------------|---------------|--|--|

| SID2                                                                                                                                                  | SID1                                  | SID0                                                   | SRR            | EXID             | _             | EID17        | EID16         |  |  |

| bit 7                                                                                                                                                 |                                       |                                                        |                |                  |               |              | bit 0         |  |  |

|                                                                                                                                                       |                                       |                                                        |                |                  |               |              |               |  |  |

| Legend:                                                                                                                                               |                                       |                                                        |                |                  |               |              |               |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                  |                                       |                                                        |                |                  |               |              |               |  |  |

| -n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown                                                                            |                                       |                                                        |                |                  |               |              | nown          |  |  |

| bit 7-5<br>bit 4                                                                                                                                      | Extended Ider                         | tandard Identifi<br>ntifier bits EID2<br>ite Remote Re | 0:EID18 (if E) | ,                |               |              |               |  |  |

|                                                                                                                                                       |                                       |                                                        |                | I to the value o | f RXRTRRO (RE | 3XnCON<3>) w | hen EXID = 0. |  |  |

| bit 3                                                                                                                                                 | EXID: Extend                          | ed Identifier bit                                      |                |                  |               |              |               |  |  |

| <ul> <li>1 = Received message is an extended data frame, SID10:SID0 are EID28:EID18</li> <li>0 = Received message is a standard data frame</li> </ul> |                                       |                                                        |                |                  |               |              |               |  |  |

| bit 2                                                                                                                                                 | Unimplemented: Read as '0'            |                                                        |                |                  |               |              |               |  |  |

| bit 1-0                                                                                                                                               | EID17:EID16: Extended Identifier bits |                                                        |                |                  |               |              |               |  |  |

#### LOW BYTE $[0 \le n \le 1]$

# REGISTER 23-17: RXBnEIDH: RECEIVE BUFFER n EXTENDED IDENTIFIER REGISTERS, HIGH BYTE [0 $\leq$ n $\leq$ 1]

| R-x   | R-x   | R-x   | R-x   | R-x   | R-x   | R-x  | R-x   |

|-------|-------|-------|-------|-------|-------|------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9 | EID8  |

| bit 7 |       |       |       |       |       |      | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 EID15:EID8: Extended Identifier bits

## REGISTER 23-18: RXBnEIDL: RECEIVE BUFFER n EXTENDED IDENTIFIER REGISTERS, LOW BYTE [0 $\leq$ n $\leq$ 1]

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| EID7  | EID6 | EID5 | EID4 | EID3 | EID2 | EID1 | EID0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                                                                  |                      |                    |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |

bit 7-0 EID7:EID0: Extended Identifier bits

## $\label{eq:register23-24: BnSIDH: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS, \\ HIGH BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| SID10 | SID9 | SID8 | SID7 | SID6 | SID5 | SID4 | SID3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 SID10:SID3: Standard Identifier bits (if EXIDE (BnSIDL<3>) = 0) Extended Identifier bits EID28:EID21 (if EXIDE = 1).

Note 1: These registers are available in Mode 1 and 2 only.

###

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 **SID10:SID3:** Standard Identifier bits (if EXIDE (BnSIDL<3>) = 0) Extended Identifier bits EID28:EID21 (if EXIDE = 1).

Note 1: These registers are available in Mode 1 and 2 only.

### REGISTER 23-59: TXBIE: TRANSMIT BUFFERS INTERRUPT ENABLE REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | U-0 | U-0   |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----|-------|

| —     | —   | —   | TXB2IE <sup>(2)</sup> | TXB1IE <sup>(2)</sup> | TXB0IE <sup>(2)</sup> |     | —     |

| bit 7 |     |     |                       |                       |                       |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                             |

|---------|------------------------------------------------------------------------|

| bit 4-2 | TXB2IE:TXB0IE: Transmit Buffer 2-0 Interrupt Enable bit <sup>(2)</sup> |

|         | 1 = Transmit buffer interrupt is enabled                               |

|         | 0 = Transmit buffer interrupt is disabled                              |

| bit 1-0 | Unimplemented: Read as '0'                                             |

Note 1: This register is available in Mode 1 and 2 only.

**2:** TXBnIE in PIE3 register must be set to get an interrupt.

### REGISTER 23-60: BIE0: BUFFER INTERRUPT ENABLE REGISTER 0<sup>(1)</sup>

| R/W-0                 | R/W-0                 |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-----------------------|-----------------------|

| B5IE <sup>(2)</sup> | B4IE <sup>(2)</sup> | B3IE <sup>(2)</sup> | B2IE <sup>(2)</sup> | B1IE <sup>(2)</sup> | B0IE <sup>(2)</sup> | RXB1IE <sup>(2)</sup> | RXB0IE <sup>(2)</sup> |

| bit 7               |                     |                     |                     | •                   |                     |                       | bit 0                 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-2 B5IE:B0IE: Programmable Transmit/Receive Buffer 5-0 Interrupt Enable bit<sup>(2)</sup> 1 = Interrupt is enabled 0 = Interrupt is disabled bit 1-0 RXB1IE:RXB0IE: Dedicated Receive Buffer 1-0 Interrupt Enable bit<sup>(2)</sup> 1 = Interrupt is enabled 0 = Interrupt is disabled

Note 1: This register is available in Mode 1 and 2 only.

2: Either TXBnIE or RXBnIE in PIE3 register must be set to get an interrupt.

Table 23-3 shows the relation between the clock generated by the PLL and the frequency error from jitter (measured jitter-induced error of 2%, Gaussian distribution, within 3 standard deviations), as a percentage of the nominal clock frequency.

This is clearly smaller than the expected drift of a crystal oscillator, typically specified at 100 ppm or 0.01%. If we add jitter to oscillator drift, we have a total frequency drift of 0.0132%. The total oscillator frequency errors for common clock frequencies and bit rates, including both drift and jitter, are shown in Table 23-4.

| <b>TABLE 23-3</b> : | FREQUENCY ERROR FROM JITTER AT VARIOUS PLL GENERATED CLOCK SPEEDS |

|---------------------|-------------------------------------------------------------------|

|                     |                                                                   |

| PLL    |                            |                     | Frequency Error at Various Nominal Bit Times (Bit Rates) |                    |                    |                  |  |

|--------|----------------------------|---------------------|----------------------------------------------------------|--------------------|--------------------|------------------|--|

| Output | <b>P</b> <sub>jitter</sub> | T <sub>jitter</sub> | 8 μs<br>(125 Kb/s)                                       | 4 μs<br>(250 Kb/s) | 2 μs<br>(500 Kb/s) | 1 μs<br>(1 Mb/s) |  |

| 40 MHz | 0.5 ns                     | 1 ns                | 0.00125%                                                 | 0.00250%           | 0.005%             | 0.01%            |  |

| 24 MHz | 0.83 ns                    | 1.67 ns             | 0.00209%                                                 | 0.00418%           | 0.008%             | 0.017%           |  |

| 16 MHz | 1.25 ns                    | 2.5 ns              | 0.00313%                                                 | 0.00625%           | 0.013%             | 0.025%           |  |

## TABLE 23-4:TOTAL FREQUENCY ERROR AT VARIOUS PLL GENERATED CLOCK SPEEDS<br/>(100 PPM OSCILLATOR DRIFT, INCLUDING ERROR FROM JITTER)

|                    | Frequency Error at Various Nominal Bit Times (Bit Rates) |                    |                    |                  |  |  |  |

|--------------------|----------------------------------------------------------|--------------------|--------------------|------------------|--|--|--|

| Nominal PLL Output | 8 μs<br>(125 Kb/s)                                       | 4 μs<br>(250 Kb/s) | 2 μs<br>(500 Kb/s) | 1 μs<br>(1 Mb/s) |  |  |  |

| 40 MHz             | 0.01125%                                                 | 0.01250%           | 0.015%             | 0.02%            |  |  |  |