Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 80KB (40K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2682t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. The INTOSC multiplexer may be used to select a higher clock frequency, by modifying the IRCF bits, before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value or the INTSRC bit is set, the INTOSC output is enabled. The IOFS bit becomes set, after the INTOSC output becomes stable, after an interval of TIOBST (parameter 39, Table 27-10). Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled, the IOFS bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

## 3.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 3.2 "Run Modes", Section 3.3 "Sleep Mode" and Section 3.4 "Idle Modes").

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or the Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/ GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 9.0 "Interrupts").

A fixed delay of interval TCSD following the wake event is required when leaving the Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## 3.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 3.2 "Run Modes" and Section 3.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 24.2 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by executing a SLEEP or CLRWDT instruction, the loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifying the IRCF bits in the OSCCON register if the internal oscillator block is the device clock source.

## 3.5.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the IOFS bit is set instead.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator if the new clock source is the primary clock. Exit delays are summarized in Table 3-2.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see **Section 24.3 "Two-Speed Start-up"**) or Fail-Safe Clock Monitor (see **Section 24.4 "Fail-Safe Clock Monitor**") is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

## TABLE 5-1:SPECIAL FUNCTION REGISTER MAP FOR<br/>PIC18F2682/2685/4682/4685 DEVICES (CONTINUED)

| Address | Name     | Address | Name    | Address | Name | Address | Name      |

|---------|----------|---------|---------|---------|------|---------|-----------|

| DFFh    | _        | DDFh    | _       | DBFh    | _    | D9Fh    |           |

| DFEh    | _        | DDEh    | _       | DBEh    | _    | D9Eh    |           |

| DFDh    | _        | DDDh    |         | DBDh    | _    | D9Dh    |           |

| DFCh    | TXBIE    | DDCh    | _       | DBCh    | _    | D9Ch    |           |

| DFBh    | _        | DDBh    | _       | DBBh    | _    | D9Bh    | _         |

| DFAh    | BIE0     | DDAh    |         | DBAh    | _    | D9Ah    | _         |

| DF9h    | _        | DD9h    | _       | DB9h    | _    | D99h    | _         |

| DF8h    | BSEL0    | DD8h    | SDFLC   | DB8h    | _    | D98h    | _         |

| DF7h    | _        | DD7h    | _       | DB7h    | _    | D97h    | _         |

| DF6h    | —        | DD6h    | _       | DB6h    | _    | D96h    | _         |

| DF5h    | —        | DD5h    | RXFCON1 | DB5h    | _    | D95h    | _         |

| DF4h    | _        | DD4h    | RXFCON0 | DB4h    | _    | D94h    | _         |

| DF3h    | MSEL3    | DD3h    | _       | DB3h    | _    | D93h    | RXF15EIDL |

| DF2h    | MSEL2    | DD2h    | _       | DB2h    | _    | D92h    | RXF15EIDH |

| DF1h    | MSEL1    | DD1h    | _       | DB1h    | _    | D91h    | RXF15SIDL |

| DF0h    | MSEL0    | DD0h    | —       | DB0h    |      | D90h    | RXF15SIDH |

| DEFh    | _        | DCFh    | —       | DAFh    |      | D8Fh    | _         |

| DEEh    | —        | DCEh    |         | DAEh    | _    | D8Eh    | _         |

| DEDh    | —        | DCDh    | —       | DADh    |      | D8Dh    | _         |

| DECh    | —        | DCCh    | _       | DACh    | _    | D8Ch    | _         |

| DEBh    | —        | DCBh    |         | DABh    | _    | D8Bh    | RXF14EIDL |

| DEAh    | —        | DCAh    | —       | DAAh    |      | D8Ah    | RXF14EIDH |

| DE9h    | —        | DC9h    | _       | DA9h    | _    | D89h    | RXF14SIDL |

| DE8h    | —        | DC8h    | —       | DA8h    | -    | D88h    | RXF14SIDH |

| DE7h    | RXFBCON7 | DC7h    | —       | DA7h    |      | D87h    | RXF13EIDL |

| DE6h    | RXFBCON6 | DC6h    | —       | DA6h    |      | D86h    | RXF13EIDH |

| DE5h    | RXFBCON5 | DC5h    |         | DA5h    | _    | D85h    | RXF13SIDL |

| DE4h    | RXFBCON4 | DC4h    | —       | DA4h    |      | D84h    | RXF13SIDH |

| DE3h    | RXFBCON3 | DC3h    |         | DA3h    | —    | D83h    | RXF12EIDL |

| DE2h    | RXFBCON2 | DC2h    |         | DA2h    |      | D82h    | RXF12EIDH |

| DE1h    | RXFBCON1 | DC1h    |         | DA1h    | —    | D81h    | RXF12SIDL |

| DE0h    | RXFBCON0 | DC0h    | _       | DA0h    | —    | D80h    | RXF12SIDH |

Note 1: Registers available only on PIC18F4X8X devices; otherwise, the registers read as '0'.

2: When any TX\_ENn bit in RX\_TX\_SELn is set, then the corresponding bit in this register has transmit properties.

**3:** This is not a physical register.

| R/W-       | 1 R/W-1                                                        | U-0                                    | R/W-0            | R/W-0             | U-0             | R/W-0              | R/W-0  |

|------------|----------------------------------------------------------------|----------------------------------------|------------------|-------------------|-----------------|--------------------|--------|

| INT2I      | P INT1IP                                                       | —                                      | INT2IE           | INT1IE            | _               | INT2IF             | INT1IF |

| bit 7      |                                                                |                                        |                  |                   |                 |                    | bit 0  |

| Legend:    |                                                                |                                        |                  |                   |                 |                    |        |

| R = Read   | lable bit                                                      | W = Writable                           | bit              | U = Unimplen      | nented bit, rea | ad as '0'          |        |

| -n = Value | e at POR                                                       | '1' = Bit is se                        | t                | '0' = Bit is clea | ared            | x = Bit is unkr    | nown   |

| bit 7      | INT2IP: INT                                                    | 2 External Inter                       | rupt Priority bi | t                 |                 |                    |        |

|            | 1 = High pr<br>0 = Low pri                                     | ,                                      |                  |                   |                 |                    |        |

| bit 6      | INT1IP: INT                                                    | 1 External Inter                       | rupt Priority bi | t                 |                 |                    |        |

|            | 1 = High pr<br>0 = Low pri                                     | •                                      |                  |                   |                 |                    |        |

| bit 5      | Unimpleme                                                      | nted: Read as                          | 0'               |                   |                 |                    |        |

| bit 4      | INT2IE: INT                                                    | 2 External Inter                       | rupt Enable bi   | t                 |                 |                    |        |

|            |                                                                | s the INT2 exter<br>s the INT2 exte    |                  |                   |                 |                    |        |

| bit 3      | INT1IE: INT                                                    | 1 External Inter                       | rupt Enable bi   | t                 |                 |                    |        |

|            |                                                                | s the INT1 exter<br>s the INT1 exte    |                  |                   |                 |                    |        |

| bit 2      | Unimpleme                                                      | nted: Read as                          | 0'               |                   |                 |                    |        |

| bit 1      | INT2IF: INT                                                    | 2 External Inter                       | upt Flag bit     |                   |                 |                    |        |

|            |                                                                | Γ2 external inter<br>Γ2 external inter |                  |                   | ed in software  | )                  |        |

| bit 0      | INT1IF: INT                                                    | 1 External Inter                       | upt Flag bit     |                   |                 |                    |        |

|            |                                                                | Γ1 external inter Γ1 external inter    |                  |                   | ed in software  | )                  |        |

| Note:      | Interrupt flag bits<br>enable bit or the<br>are clear prior to | global interrupt                       | enable bit. Us   | er software sho   | uld ensure th   | e appropriate inte |        |

#### REGISTER 9-3: INTCON3: INTERRUPT CONTROL REGISTER 3

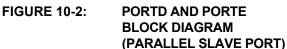

#### **10.6 Parallel Slave Port**

| Note: | The Parallel Slave Port is only available on |

|-------|----------------------------------------------|

|       | PIC18F4682/4685 devices.                     |

In addition to its function as a general I/O port, PORTD can also operate as an 8-bit wide Parallel Slave Port (PSP) or microprocessor port. PSP operation is controlled by the 4 upper bits of the TRISE register (Register 10-1). Setting control bit, PSPMODE (TRISE<4>), enables PSP operation, as long as the Enhanced CCP1 (ECCP1) module is not operating in dual output or quad output PWM mode. In Slave mode, the port is asynchronously readable and writable by the external world.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting the control bit, PSPMODE, enables the PORTE I/O pins to become control inputs for the microprocessor port. When set, port pin RE0 is the RD input, RE1 is the WR input and RE2 is the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PFCG3:PFCG0 (ADCON1<3:0>), must also be set to '1010'.

A write to the PSP occurs when both the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits are both set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit is set. If the user writes new data to PORTD to set OBF, the data is immediately read out; however, the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  line is detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP. When this happens, the IBF and OBF bits can be polled and the appropriate action taken. The timing for the control signals in Write and Read modes is shown in Figure 10-3 and Figure 10-4, respectively.

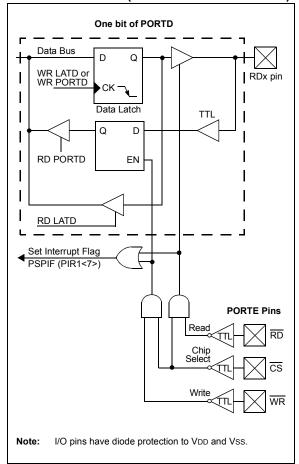

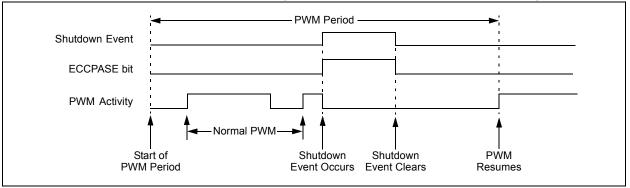

## 16.4.7.1 Auto-Shutdown and Auto-Restart

The auto-shutdown feature can be configured to allow automatic restarts of the module following a shutdown event. This is enabled by setting the PRSEN bit of the ECCP1DEL register (ECCP1DEL<7>).

In Shutdown mode with PRSEN = 1 (Figure 16-10), the ECCPASE bit will remain set for as long as the cause of the shutdown continues. When the shutdown condition clears, the ECCPASE bit is cleared. If PRSEN = 0 (Figure 16-11), once a shutdown condition occurs, the ECCPASE bit will remain set until it is cleared by firmware. Once ECCPASE is cleared, the Enhanced PWM will resume at the beginning of the next PWM period.

| Note: | Writing to the ECCPASE bit is disabled |

|-------|----------------------------------------|

|       | while a shutdown condition is active.  |

Independent of the PRSEN bit setting, if the autoshutdown source is one of the comparators, the shutdown condition is a level. The ECCPASE bit cannot be cleared as long as the cause of the shutdown persists.

The Auto-Shutdown mode can be forced by writing a '1' to the ECCPASE bit.

## 16.4.8 START-UP CONSIDERATIONS

When the ECCP1 module is used in the PWM mode, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins. When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the OFF state until the microcontroller drives the I/O pins with the proper signal levels, or activates the PWM output(s).

The ECCP1M1:ECCP1M0 bits (ECCP1CON<1:0>) allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pins are configured as outputs. Changing the polarity configuration while the PWM pins are configured as outputs is not recommended, since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pins for output at the same time as the ECCP1 module may cause damage to the application circuit. The ECCP1 module must be enabled in the proper output mode and complete a full PWM cycle before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit being set as the second PWM period begins.

#### FIGURE 16-10: PWM AUTO-SHUTDOWN (PRSEN = 1, AUTO-RESTART ENABLED)

## FIGURE 16-11: PWM AUTO-SHUTDOWN (PRSEN = 0, AUTO-RESTART DISABLED)

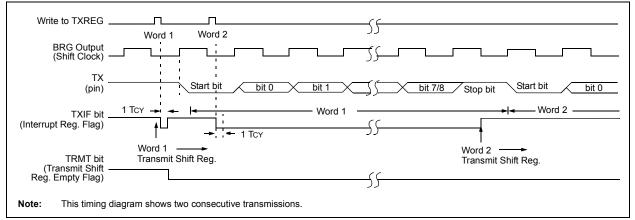

#### FIGURE 18-5: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

#### TABLE 18-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name    | Bit 7                | Bit 6                                         | Bit 5       | Bit 4      | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |  |

|---------|----------------------|-----------------------------------------------|-------------|------------|-------|--------|--------|--------|----------------------------|--|

| INTCON  | GIE/GIEH             | PEIE/GIEL                                     | TMR0IE      | INT0IE     | RBIE  | TMR0IF | INT0IF | RBIF   | 51                         |  |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                                          | RCIF        | TXIF       | SSPIF | CCP1IF | TMR2IF | TMR1IF | 54                         |  |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                                          | RCIE        | TXIE       | SSPIE | CCP1IE | TMR2IE | TMR1IE | 54                         |  |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP                                          | RCIP        | TXIP       | SSPIP | CCP1IP | TMR2IP | TMR1IP | 54                         |  |

| RCSTA   | SPEN                 | RX9                                           | SREN        | CREN       | ADDEN | FERR   | OERR   | RX9D   | 53                         |  |

| TXREG   | EUSART T             | ransmit Reg                                   | jister      |            |       |        |        |        | 53                         |  |

| TXSTA   | CSRC                 | TX9                                           | TXEN        | SYNC       | SENDB | BRGH   | TRMT   | TX9D   | 53                         |  |

| BAUDCON | ABDOVF               | RCIDL                                         | _           | SCKP       | BRG16 | —      | WUE    | ABDEN  | 53                         |  |

| SPBRGH  | EUSART B             | EUSART Baud Rate Generator Register High Byte |             |            |       |        |        |        |                            |  |

| SPBRG   | EUSART B             | aud Rate G                                    | enerator Re | gister Low | Byte  |        |        |        | 53                         |  |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Reserved in PIC18F2682/2685 devices; always maintain these bits clear.

## 22.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

## 22.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6               | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0                  | Reset<br>Values<br>on Page |

|---------|----------|---------------------|--------|--------|--------|--------|--------|------------------------|----------------------------|

| HLVDCON | VDIRMAG  | _                   | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0                 | 52                         |

| INTCON  | GIE/GIEH | PEIE/GIEL           | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF                   | 51                         |

| PIR2    | OSCFIF   | CMIF <sup>(1)</sup> | _      | EEIF   | BCLIF  | HLVDIF | TMR3IF | ECCP1IF <sup>(1)</sup> | 54                         |

| PIE2    | OSCFIE   | CMIE <sup>(1)</sup> |        | EEIE   | BCLIE  | HLVDIE | TMR3IE | ECCP1IE <sup>(1)</sup> | 54                         |

| IPR2    | OSCFIP   | CMIP <sup>(1)</sup> |        | EEIP   | BCLIP  | HLVDIP | TMR3IP | ECCP1IP <sup>(1)</sup> | 53                         |

#### TABLE 22-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

Note 1: These bits are available in PIC18F4682/4685 devices and reserved in PIC18F2682/2685 devices.

#### EXAMPLE 23-3: TRANSMITTING A CAN MESSAGE USING BANKED METHOD

; Need to transmit Standard Identifier message 123h using TXBO buffer. ; To successfully transmit, CAN module must be either in Normal or Loopback mode. ; TXBO buffer is not in access bank. And since we want banked method, we need to make sure ; that correct bank is selected. BANKSEL TXB0CON ; One BANKSEL in beginning will make sure that we are ; in correct bank for rest of the buffer access. ; Now load transmit data into TXB0 buffer. MOVLW MY\_DATA\_BYTE1 ; Load first data byte into buffer ; Compiler will automatically set "BANKED" bit MOVWF TXB0D0 ; Load rest of data bytes - up to 8 bytes into TXBO buffer. . . . ; Load message identifier MOVLW 60H ; Load SID2:SID0, EXIDE = 0 MOVWF TXB0SIDL MOVLW 24H ; Load SID10:SID3 MOVWF TXB0SIDH ; No need to load TXB0EIDL:TXB0EIDH, as we are transmitting Standard Identifier Message only. ; Now that all data bytes are loaded, mark it for transmission. MOVLW B'00001000' ; Normal priority; Request transmission MOVWF TXB0CON ; If required, wait for message to get transmitted BTFSC TXB0CON, TXREQ ; Is it transmitted? BRA \$-2 ; No. Continue to wait... ; Message is transmitted.

## **REGISTER 23-35:** BnDLC: TX/RX BUFFER n DATA LENGTH CODE REGISTERS IN TRANSMIT MODE $[0 \le n \le 5, TXnEN (BSEL \le n) = 1]^{(1)}$

| U-0          | R/W-x                                                        | U-0                                           | U-0           | R/W-x            | R/W-x            | R/W-x           | R/W-x |  |  |  |  |

|--------------|--------------------------------------------------------------|-----------------------------------------------|---------------|------------------|------------------|-----------------|-------|--|--|--|--|

| _            | TXRTR                                                        | —                                             | —             | DLC3             | DLC2             | DLC1            | DLC0  |  |  |  |  |

| bit 7        |                                                              |                                               |               |                  |                  |                 | bit 0 |  |  |  |  |

|              |                                                              |                                               |               |                  |                  |                 |       |  |  |  |  |

| Legend:      |                                                              |                                               |               |                  |                  |                 |       |  |  |  |  |

| R = Readal   | ole bit                                                      | W = Writable                                  | bit           | U = Unimpler     | mented bit, read | l as '0'        |       |  |  |  |  |

| -n = Value a | at POR                                                       | '1' = Bit is set                              |               | '0' = Bit is cle | ared             | x = Bit is unki | nown  |  |  |  |  |

|              |                                                              |                                               |               |                  |                  |                 |       |  |  |  |  |

| bit 7        | Unimplemen                                                   | ted: Read as '                                | )'            |                  |                  |                 |       |  |  |  |  |

| bit 6        | TXRTR: Trans                                                 | smitter Remote                                | Transmission  | n Request bit    |                  |                 |       |  |  |  |  |

|              | 1 = Transmitte                                               | 1 = Transmitted message will have RTR bit set |               |                  |                  |                 |       |  |  |  |  |

|              | 0 = Transmitte                                               | ed message wi                                 | ll have RTR b | it cleared       |                  |                 |       |  |  |  |  |

| bit 5-4      | Unimplemen                                                   | ted: Read as '                                | )'            |                  |                  |                 |       |  |  |  |  |

| bit 3-0      | DLC3:DLC0:                                                   | Data Length C                                 | ode bits      |                  |                  |                 |       |  |  |  |  |

|              | 1111-1001 =                                                  | Reserved                                      |               |                  |                  |                 |       |  |  |  |  |

|              |                                                              | length = 8 byte                               |               |                  |                  |                 |       |  |  |  |  |

|              |                                                              | length = 7 byte                               |               |                  |                  |                 |       |  |  |  |  |

|              |                                                              | length = 6 byte                               |               |                  |                  |                 |       |  |  |  |  |

|              | 0101 = Data length = 5 bytes                                 |                                               |               |                  |                  |                 |       |  |  |  |  |

|              | 0100 = Data length = 4 bytes<br>0011 = Data length = 3 bytes |                                               |               |                  |                  |                 |       |  |  |  |  |

|              |                                                              | length = 2 byte                               |               |                  |                  |                 |       |  |  |  |  |

|              |                                                              | length = 1 byte                               |               |                  |                  |                 |       |  |  |  |  |

|              | 0000 <b>= Data</b>                                           | length = 0 byte                               | S             |                  |                  |                 |       |  |  |  |  |

**Note 1:** These registers are available in Mode 1 and 2 only.

## REGISTER 23-36: BSEL0: BUFFER SELECT REGISTER 0<sup>(1)</sup>

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0         | U-0 | U-0   |

|--------|--------|--------|--------|--------|---------------|-----|-------|

| B5TXEN | B4TXEN | B3TXEN | B2TXEN | B1TXEN | <b>B0TXEN</b> | —   | —     |

| bit 7  |        |        |        |        |               |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-2 B5TXEN:B0TXEN: Buffer 5 to Buffer 0 Transmit Enable bit

- 1 = Buffer is configured in Transmit mode

- 0 = Buffer is configured in Receive mode

- bit 1-0 Unimplemented: Read as '0'

**Note 1:** These registers are available in Mode 1 and 2 only.

| R/W-0              | R/W-0                                                                          | R/W-0                                                                  | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|--------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|---------|

| FIL15_1            | FIL15_0                                                                        | FIL14_1                                                                | FIL14_0         | FIL13_1          | FIL13_0          | FIL12_1         | FIL12_0 |

| bit 7              |                                                                                |                                                                        |                 |                  |                  |                 | bit 0   |

| Legend:            |                                                                                |                                                                        |                 |                  |                  |                 |         |

| R = Readabl        | e bit                                                                          | W = Writable                                                           | bit             | U = Unimpler     | nented bit, read | 1 as '0'        |         |

| -n = Value at      | POR                                                                            | '1' = Bit is set                                                       |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 7-6<br>bit 5-4 | 11 = No masl<br>10 = Filter 15<br>01 = Accepta<br>00 = Accepta                 | nce Mask 1<br>nce Mask 0<br>I <b>4_0:</b> Filter 14<br>k<br>nce Mask 1 |                 |                  |                  |                 |         |

| bit 3-2            | 11 = No masl<br>10 = Filter 15<br>01 = Accepta<br>00 = Accepta                 | nce Mask 1<br>nce Mask 0                                               |                 |                  |                  |                 |         |

| bit 1-0            | FIL12_1:FIL1<br>11 = No masl<br>10 = Filter 15<br>01 = Accepta<br>00 = Accepta | nce Mask 1                                                             | Select bits 1 a | nd 0             |                  |                 |         |

## REGISTER 23-51: MSEL3: MASK SELECT REGISTER 3<sup>(1)</sup>

**Note 1:** This register is available in Mode 1 and 2 only.

| R/W-0        | R/W-0                                                                      | U-0                                          | U-0          | U-0              | R/W-0                  | R/W-0                  | R/W-0                  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------|----------------------------------------------|--------------|------------------|------------------------|------------------------|------------------------|--|--|--|--|--|

| WAKDIS       | WAKFIL                                                                     | —                                            |              | —                | SEG2PH2 <sup>(1)</sup> | SEG2PH1 <sup>(1)</sup> | SEG2PH0 <sup>(1)</sup> |  |  |  |  |  |

| bit 7        |                                                                            |                                              |              |                  |                        |                        | bit 0                  |  |  |  |  |  |

| Legend:      |                                                                            |                                              |              |                  |                        |                        |                        |  |  |  |  |  |

| R = Readat   | ole bit                                                                    | W = Writable I                               | bit          | U = Unimple      | mented bit, rea        | d as '0'               |                        |  |  |  |  |  |

| -n = Value a | at POR                                                                     | '1' = Bit is set                             |              | '0' = Bit is cle | eared                  | x = Bit is unk         | nown                   |  |  |  |  |  |

|              |                                                                            |                                              |              |                  |                        |                        |                        |  |  |  |  |  |

| bit 7        | WAKDIS: Wa                                                                 | ake-up Disable I                             | bit          |                  |                        |                        |                        |  |  |  |  |  |

|              |                                                                            | 1 = Disable CAN bus activity wake-up feature |              |                  |                        |                        |                        |  |  |  |  |  |

|              | 0 = Enable C                                                               | AN bus activity                              | wake-up fea  | iture            |                        |                        |                        |  |  |  |  |  |

| bit 6        | WAKFIL: Selects CAN bus Line Filter for Wake-up bit                        |                                              |              |                  |                        |                        |                        |  |  |  |  |  |

|              |                                                                            | l bus line filter fo                         |              |                  |                        |                        |                        |  |  |  |  |  |

|              | 0 = CAN bus                                                                | line filter is not                           | used for wak | ke-up            |                        |                        |                        |  |  |  |  |  |

| bit 5-3      | Unimplemen                                                                 | nted: Read as '                              | )'           |                  |                        |                        |                        |  |  |  |  |  |

| bit 2-0      | SEG2PH2:SI                                                                 | EG2PH0: Phase                                | e Segment 2  | Time Select bi   | its <sup>(1)</sup>     |                        |                        |  |  |  |  |  |

|              |                                                                            | Segment 2 time                               |              |                  |                        |                        |                        |  |  |  |  |  |

|              | 110 = Phase Segment 2 time = 7 x TQ                                        |                                              |              |                  |                        |                        |                        |  |  |  |  |  |

|              |                                                                            | Segment 2 time                               |              |                  |                        |                        |                        |  |  |  |  |  |

|              | 100 = Phase Segment 2 time = 5 x TQ<br>011 = Phase Segment 2 time = 4 x TQ |                                              |              |                  |                        |                        |                        |  |  |  |  |  |

|              |                                                                            | Segment 2 time                               |              |                  |                        |                        |                        |  |  |  |  |  |

|              |                                                                            | Segment 2 time                               |              |                  |                        |                        |                        |  |  |  |  |  |

|              | 000 <b>= Phase</b>                                                         | Segment 2 time                               | e = 1 x Tq   |                  |                        |                        |                        |  |  |  |  |  |

|              |                                                                            |                                              |              |                  |                        |                        |                        |  |  |  |  |  |

#### REGISTER 23-54: BRGCON3: BAUD RATE CONTROL REGISTER 3

Note 1: Ignored if SEG2PHTS bit (BRGCON2<7>) is '0'.

## TABLE 23-1: CAN CONTROLLER REGISTER MAP (CONTINUED)

| Address <sup>(1)</sup> | Name                       | Address | Name                       | Address | Name                       | Address | Name |

|------------------------|----------------------------|---------|----------------------------|---------|----------------------------|---------|------|

| E7Fh                   | CANCON_RO4 <sup>(2)</sup>  | E5Fh    | CANCON_RO6(2)              | E3Fh    | CANCON_RO8 <sup>(2)</sup>  | E1Fh    | (4)  |

| E7Eh                   | CANSTAT_RO4 <sup>(2)</sup> | E5Eh    | CANSTAT_RO6 <sup>(2)</sup> | E3Eh    | CANSTAT_RO8 <sup>(2)</sup> | E1Eh    | (4)  |

| E7Dh                   | B5D7                       | E5Dh    | B3D7                       | E3Dh    | B1D7                       | E1Dh    | (4)  |

| E7Ch                   | B5D6                       | E5Ch    | B3D6                       | E3Ch    | B1D6                       | E1Ch    | (4)  |

| E7Bh                   | B5D5                       | E5Bh    | B3D5                       | E3Bh    | B1D5                       | E1Bh    | (4)  |

| E7Ah                   | B5D4                       | E5Ah    | B3D4                       | E3Ah    | B1D4                       | E1Ah    | (4)  |

| E79h                   | B5D3                       | E59h    | B3D3                       | E39h    | B1D3                       | E19h    | (4)  |

| E78h                   | B5D2                       | E58h    | B3D2                       | E38h    | B1D2                       | E18h    | (4)  |

| E77h                   | B5D1                       | E57h    | B3D1                       | E37h    | B1D1                       | E17h    | (4)  |

| E76h                   | B5D0                       | E56h    | B3D0                       | E36h    | B1D0                       | E16h    | (4)  |

| E75h                   | B5DLC                      | E55h    | B3DLC                      | E35h    | B1DLC                      | E15h    | (4)  |

| E74h                   | B5EIDL                     | E54h    | B3EIDL                     | E34h    | B1EIDL                     | E14h    | (4)  |

| E73h                   | B5EIDH                     | E53h    | <b>B3EIDH</b>              | E33h    | B1EIDH                     | E13h    | (4)  |

| E72h                   | B5SIDL                     | E52h    | B3SIDL                     | E32h    | B1SIDL                     | E12h    | (4)  |

| E71h                   | B5SIDH                     | E51h    | B3SIDH                     | E31h    | B1SIDH                     | E11h    | (4)  |

| E70h                   | B5CON                      | E50h    | B3CON                      | E30h    | B1CON                      | E10h    | (4)  |

| E6Fh                   | CANCON_RO5                 | E4Fh    | CANCON_RO7                 | E2Fh    | CANCON_RO9                 | E0Fh    | (4)  |

| E6Eh                   | CANSTAT_RO5                | E4Eh    | CANSTAT_RO7                | E2Eh    | CANSTAT_RO9                | E0Eh    | (4)  |

| E6Dh                   | B4D7                       | E4Dh    | B2D7                       | E2Dh    | B0D7                       | E0Dh    | (4)  |

| E6Ch                   | B4D6                       | E4Ch    | B2D6                       | E2Ch    | B0D6                       | E0Ch    | (4)  |

| E6Bh                   | B4D5                       | E4Bh    | B2D5                       | E2Bh    | B0D5                       | E0Bh    | (4)  |

| E6Ah                   | B4D4                       | E4Ah    | B2D4                       | E2Ah    | B0D4                       | E0Ah    | (4)  |

| E69h                   | B4D3                       | E49h    | B2D3                       | E29h    | B0D3                       | E09h    | (4)  |

| E68h                   | B4D2                       | E48h    | B2D2                       | E28h    | B0D2                       | E08h    | (4)  |

| E67h                   | B4D1                       | E47h    | B2D1                       | E27h    | B0D1                       | E07h    | (4)  |

| E66h                   | B4D0                       | E46h    | B2D0                       | E26h    | B0D0                       | E06h    | (4)  |

| E65h                   | B4DLC                      | E45h    | B2DLC                      | E25h    | B0DLC                      | E05h    | (4)  |

| E64h                   | B4EIDL                     | E44h    | B2EIDL                     | E24h    | B0EIDL                     | E04h    | (4)  |

| E63h                   | B4EIDH                     | E43h    | B2EIDH                     | E23h    | B0EIDH                     | E03h    | (4)  |

| E62h                   | B4SIDL                     | E42h    | B2SIDL                     | E22h    | B0SIDL                     | E02h    | (4)  |

| E61h                   | B4SIDH                     | E41h    | B2SIDH                     | E21h    | B0SIDH                     | E01h    | (4)  |

| E60h                   | B4CON                      | E40h    | B2CON                      | E20h    | B0CON                      | E00h    | (4)  |

Note 1: Shaded registers are available in Access Bank low area, while the rest are available in Bank 15.

2: CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the controller register due to the Microchip header file requirement.

**3:** These registers are not CAN registers.

4: Unimplemented registers are read as '0'.

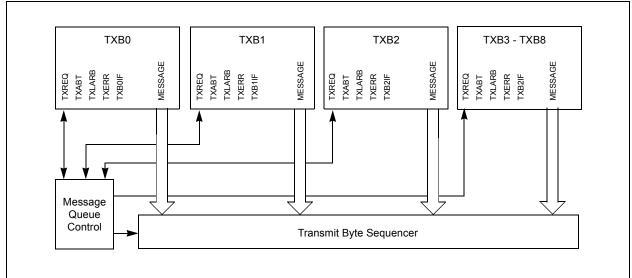

#### 23.6.3 TRANSMIT PRIORITY

Transmit priority is a prioritization within the PIC18F2682/2685/4682/4685 devices of the pending transmittable messages. This is independent from and not related to any prioritization implicit in the message arbitration scheme built into the CAN protocol. Prior to sending the SOF, the priority of all buffers that are queued for transmission is compared. The transmit buffer with the highest priority will be sent first. If two buffers have the same priority setting, the buffer with the highest buffer number will be sent first. There are four levels of transmit priority. If TXP bits for a particular message buffer are set to '11', that buffer has the highest possible priority. If TXP bits for a particular message buffer are set to '00', that buffer has the lowest possible priority.

FIGURE 23-2: TRANSMIT BUFFERS

## REGISTER 24-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| U-0           | U-0                                                            | U-0                  | R/P-1                     | R/P-1        | R/P-1                 | R/P-1                 | R/P-1                 |  |

|---------------|----------------------------------------------------------------|----------------------|---------------------------|--------------|-----------------------|-----------------------|-----------------------|--|

| _             | _                                                              | —                    | BORV1                     | BORV0        | BOREN1 <sup>(1)</sup> | BOREN0 <sup>(1)</sup> | PWRTEN <sup>(1)</sup> |  |

| bit 7         |                                                                |                      |                           | •            |                       |                       | bit 0                 |  |

|               |                                                                |                      |                           |              |                       |                       |                       |  |

| Legend:       |                                                                |                      |                           |              |                       |                       |                       |  |

| R = Readabl   | e bit                                                          | P = Program          | nable bit                 | U = Unimpler | mented bit, read      | as '0'                |                       |  |

| -n = Value wl | hen device is unp                                              | programmed           |                           | u = Unchang  | ed from progran       | nmed state            |                       |  |

|               |                                                                |                      |                           |              |                       |                       |                       |  |

| bit 7-5       | Unimplement                                                    | ted: Read as '       | 0'                        |              |                       |                       |                       |  |

| bit 4-3       | 4-3 BORV1:BORV0: Brown-out Reset Voltage bits                  |                      |                           |              |                       |                       |                       |  |

|               | 11 = Minimum                                                   | 11 = Minimum setting |                           |              |                       |                       |                       |  |

|               | •                                                              |                      |                           |              |                       |                       |                       |  |

|               | •                                                              |                      |                           |              |                       |                       |                       |  |

|               | 00 = Maximur                                                   | n setting            |                           |              |                       |                       |                       |  |

| bit 2-1       |                                                                | REN0: Brown-         | out Posot End             | blo bite(1)  |                       |                       |                       |  |

| DIL 2-1       |                                                                |                      |                           |              | EN is disabled)       |                       |                       |  |

|               |                                                                |                      |                           |              | abled in Sleep r      | node (SBORE           | N is disabled)        |  |

|               |                                                                |                      |                           |              | re (SBOREN is         |                       |                       |  |

|               |                                                                | ut Reset disab       |                           | •            |                       | ,                     |                       |  |

|               | bit 0 <b>PWRTEN</b> : Power-up Timer Enable bit <sup>(1)</sup> |                      |                           |              |                       |                       |                       |  |

| bit 0         | <b>PWRTEN</b> : Po                                             | wer-up Timer         | Enable bit <sup>(1)</sup> |              |                       |                       |                       |  |

| bit 0         | <b>PWRTEN:</b> Po<br>1 = PWRT dis                              | •                    | Enable bit <sup>(1)</sup> |              |                       |                       |                       |  |

© 2009 Microchip Technology Inc.

controlled.

| IORLW                         | Inclusive                             | OR Lite       | eral w | ith \ | w       |  |

|-------------------------------|---------------------------------------|---------------|--------|-------|---------|--|

| Syntax:                       | IORLW k                               | IORLW k       |        |       |         |  |

| Operands:                     | $0 \le k \le 255$                     | 5             |        |       |         |  |

| Operation:                    | (W) .OR. k                            | $\to W$       |        |       |         |  |

| Status Affected:              | N, Z                                  | N, Z          |        |       |         |  |

| Encoding:                     | 0000                                  | 1001          | kkk    | k     | kkkk    |  |

| Description:                  | The conter<br>eight-bit lite<br>in W. |               |        |       |         |  |

| Words:                        | 1                                     | 1             |        |       |         |  |

| Cycles:                       | 1                                     |               |        |       |         |  |

| Q Cycle Activity:             |                                       |               |        |       |         |  |

| Q1                            | Q2                                    | Q3            | 3      |       | Q4      |  |

| Decode                        | Read<br>literal 'k'                   | Proce<br>Data |        | Wri   | te to W |  |

| Example:                      | IORLW                                 | 35h           |        |       |         |  |

| Before Instruction<br>W = 9Ah |                                       |               |        |       |         |  |

BFh

After Instruction W

=

| IORWF             | Inclusive OR W with f                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                    |                                                                                                                       |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:           | IORWF f                                                                                                                                                                                                        | IORWF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                    |                                                                                                                       |  |  |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                            | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                    |                                                                                                                       |  |  |

| Operation:        | (W) .OR. (f                                                                                                                                                                                                    | $) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                    |                                                                                                                       |  |  |

| Status Affected:  | N, Z                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                    |                                                                                                                       |  |  |

| Encoding:         | 0001 00da ffff ffff                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                    |                                                                                                                       |  |  |

| Description:      | Inclusive O<br>'0', the result is<br>(default).<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode when<br>Section 25<br>Bit-Oriente<br>Literal Offs | It is placed by the Access the BSR is (default). It default). Ind the exact the the formula of the exact the e | ed in W. I<br>back in reg<br>ss Bank is<br>is used to<br>xtended in<br>nstruction<br>ffset Addro<br>95 (5Fh).<br><b>te-Oriento</b> | f 'd' is '1',<br>gister 'f'<br>selected.<br>select the<br>struction<br>operates<br>essing<br>See<br>ed and<br>Indexed |  |  |

| Words:            | 1                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                    |                                                                                                                       |  |  |