#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

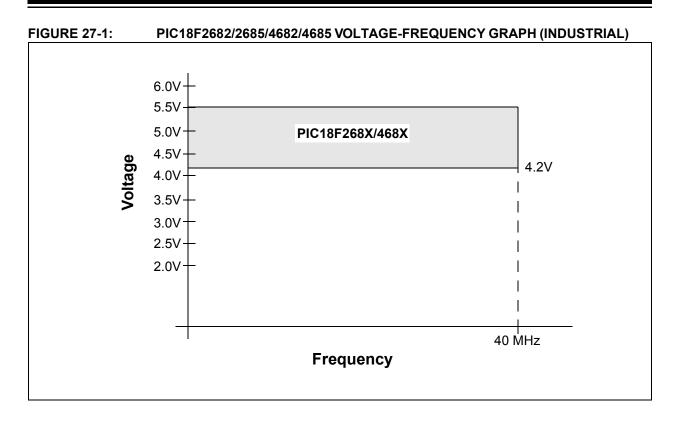

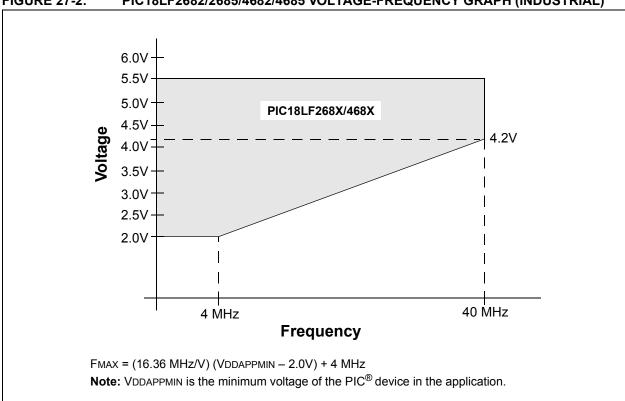

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                              |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 96KB (48K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 1K x 8                                                                   |

| RAM Size                   | 3.25K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4685-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

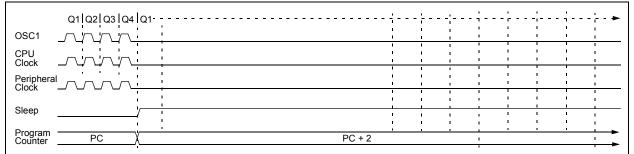

## 3.3 Sleep Mode

The power-managed Sleep mode in the PIC18F2682/ 2685/4682/4685 devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 3-5). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

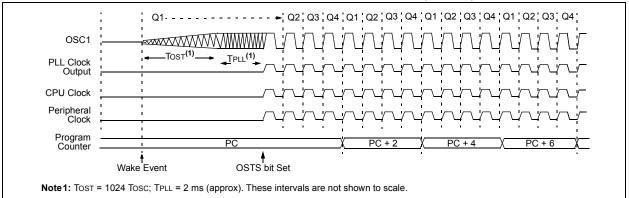

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS1:SCS0 bits becomes ready (see Figure 3-6), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see Section 24.0 "Special Features of the CPU"). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

## 3.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS1:SCS0 bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD (parameter 38, Table 27-10) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT timeout will result in a WDT wake-up to the Run mode currently specified by the SCS1:SCS0 bits.

FIGURE 3-5: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

### TRANSITION TIMING FOR WAKE FROM SLEEP (HSPLL)

## 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode where the primary clock source is not stopped

- The primary clock source is not any of the LP, XT, HS or HSPLL modes

In these instances, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving the Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

# TABLE 3-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Clock Source<br>Before Wake-up          | Clock Source<br>After Wake-up | Exit Delay                            | Clock Ready Status<br>Bit (OSCCON) |

|-----------------------------------------|-------------------------------|---------------------------------------|------------------------------------|

|                                         | LP, XT, HS                    |                                       |                                    |

|                                         | HSPLL                         |                                       | OSTS                               |

| Primary Device Clock<br>(PRI_IDLE mode) | EC, RC                        | TCSD <sup>(2)</sup>                   |                                    |

|                                         | INTRC <sup>(1)</sup>          |                                       | —                                  |

|                                         | INTOSC <sup>(3)</sup>         |                                       | IOFS                               |

|                                         | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |

|                                         | HSPLL                         | Tost + t <sub>rc</sub> (4)            | OSTS                               |

| T1OSC or INTRC <sup>(1)</sup>           | EC, RC                        | T <sub>CSD</sub> (2)                  |                                    |

|                                         | INTRC <sup>(1)</sup>          |                                       | —                                  |

|                                         | INTOSC <sup>(3)</sup>         | TIOBST <sup>(5)</sup>                 | IOFS                               |

|                                         | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |

|                                         | HSPLL                         | Tost + t <sub>rc</sub> <sup>(4)</sup> | OSTS                               |

| INTOSC <sup>(3)</sup>                   | EC, RC                        | T <sub>CSD</sub> (2)                  |                                    |

|                                         | INTRC <sup>(1)</sup>          | 1030.7                                | —                                  |

|                                         | INTOSC <sup>(3)</sup>         | None                                  | IOFS                               |

|                                         | LP, XT, HS                    | Tost <sup>(4)</sup>                   |                                    |

| News                                    | HSPLL                         | Tost + t <sub>rc</sub> <sup>(4)</sup> | OSTS                               |

| None<br>(Sleep mode)                    | EC, RC                        | T <sub>CSD</sub> (2)                  |                                    |

|                                         | INTRC <sup>(1)</sup>          | 105017                                | —                                  |

|                                         | INTOSC <sup>(3)</sup>         | TIOBST <sup>(5)</sup>                 | IOFS                               |

Note 1: In this instance, refers specifically to the 31 kHz INTRC clock source.

2: TCSD (parameter 38) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see Section 3.4 "Idle Modes").

3: Includes both the INTOSC 8 MHz source and postscaler derived frequencies.

**4:** TOST is the Oscillator Start-up Timer (parameter 32). t<sub>rc</sub> is the PLL Lock-out Timer (parameter F12); it is also designated as TPLL.

5: Execution continues during TIOBST (parameter 39), the INTOSC stabilization period.

## 4.6 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register,  $\overline{RI}$ ,  $\overline{TO}$ ,

PD, POR and BOR, are set or cleared differently in different Reset situations, as indicated in Table 4-3. These bits are used in software to determine the nature of the Reset.

Table 4-4 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets and WDT wake-ups.

# TABLE 4-3:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

|                                                              | Deserves              |              | RCC |    | STKPTR Register |     |     |        |        |

|--------------------------------------------------------------|-----------------------|--------------|-----|----|-----------------|-----|-----|--------|--------|

| Condition                                                    | Program<br>Counter    | SBOREN       | RI  | то | PD              | POR | BOR | STKFUL | STKUNF |

| Power-on Reset                                               | 0000h                 | 1            | 1   | 1  | 1               | 0   | 0   | 0      | 0      |

| RESET instruction                                            | 0000h                 | u <b>(2)</b> | 0   | u  | u               | u   | u   | u      | u      |

| Brown-out Reset                                              | 0000h                 | u <b>(2)</b> | 1   | 1  | 1               | u   | 0   | u      | u      |

| MCLR during power-managed Run modes                          | 0000h                 | u <b>(2)</b> | u   | 1  | u               | u   | u   | u      | u      |

| MCLR during power-managed Idle modes and Sleep mode          | 0000h                 | u <b>(2)</b> | u   | 1  | 0               | u   | u   | u      | u      |

| WDT time-out during full power or<br>power-managed Run modes | 0000h                 | u <b>(2)</b> | u   | 0  | u               | u   | u   | u      | u      |

| MCLR during full power execution                             | 0000h                 | u <b>(2)</b> | u   | u  | u               | u   | u   | u      | u      |

| Stack Full Reset (STVREN = 1)                                | 0000h                 | u <b>(2)</b> | u   | u  | u               | u   | u   | 1      | u      |

| Stack Underflow Reset<br>(STVREN = 1)                        | 0000h                 | u <b>(2)</b> | u   | u  | u               | u   | u   | u      | 1      |

| Stack Underflow Error (not an actual<br>Reset, STVREN = 0)   | 0000h                 | u <b>(2)</b> | u   | u  | u               | u   | u   | u      | 1      |

| WDT time-out during power-managed Idle or Sleep modes        | PC + 2                | u <b>(2)</b> | u   | 0  | 0               | u   | u   | u      | u      |

| Interrupt exit from<br>power-managed modes                   | PC + 2 <sup>(1)</sup> | u <b>(2)</b> | u   | u  | 0               | u   | u   | u      | u      |

**Legend:** u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bit is set, the PC is loaded with the interrupt vector (008h or 0018h).

2: Reset state is '1' for POR and unchanged for all other Resets when software BOR is enabled (BOREN1:BOREN0 Configuration bits = 01 and SBOREN = 1); otherwise, the Reset state is '0'.

## 5.3.5 STATUS REGISTER

The STATUS register, shown in Register 5-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the status is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('000u u1uu'). It is recommended that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in Table 25-2 and Table 25-3.

Note: The C and DC bits operate as the borrow and digit borrow bits respectively in subtraction.

## **REGISTER 5-2:** STATUS REGISTER

|           |                                                   |                                                                        |                   | DAA              | DAA             | DAA                | DAA           |

|-----------|---------------------------------------------------|------------------------------------------------------------------------|-------------------|------------------|-----------------|--------------------|---------------|

| U-0       | U-0                                               | U-0                                                                    | R/W-x             | R/W-x            | R/W-x           | R/W-x              | R/W-x         |

|           | —                                                 | —                                                                      | N                 | OV               | Z               | DC <sup>(1)</sup>  | , v           |

| oit 7     |                                                   |                                                                        |                   |                  |                 |                    | bit (         |

| _egend:   |                                                   |                                                                        |                   |                  |                 |                    |               |

| R = Read  | dable bit                                         | W = Writable                                                           | bit               | U = Unimpler     | nented bit, rea | nd as '0'          |               |

| -n = Valu | e at POR                                          | '1' = Bit is se                                                        | t                 | '0' = Bit is cle | ared            | x = Bit is unkr    | nown          |

| bit 7-5   | Unimplem                                          | ented: Read as                                                         | '∩'               |                  |                 |                    |               |

| bit 4     | N: Negative                                       |                                                                        | 0                 |                  |                 |                    |               |

| UII 4     | •                                                 | used for signed a                                                      | rithmetic (2's    | complement). It  | indicates whe   | ether the result w | vas negative  |

|           |                                                   | was negative<br>was positive                                           |                   |                  |                 |                    |               |

| bit 3     | which caus                                        | ow bit<br>ised for signed a<br>ses the sign bit (b<br>w occurred for s | oit 7 of the resu | ult) to change s | tate.           |                    | bit magnitude |

|           |                                                   | rflow occurred                                                         | •                 | ,                | ·               |                    |               |

| bit 2     | Z: Zero bit                                       |                                                                        |                   |                  |                 |                    |               |

|           |                                                   | sult of an arithme<br>sult of an arithme                               |                   |                  | ero             |                    |               |

| bit 1     |                                                   | arry/Borrow bit <sup>(1</sup><br>ADDLW, SUBLW ;                        |                   | structions:      |                 |                    |               |

|           | 1 = A carry                                       | r-out from the 4th<br>ry-out from the 4                                | low-order bit     | of the result oc | curred          |                    |               |

| bit 0     | C: Carry/Bo                                       | -                                                                      |                   |                  |                 |                    |               |

|           |                                                   | ADDLW, SUBLW                                                           | and SUBWF ins     | structions:      |                 |                    |               |

|           | •                                                 | -out from the Mo                                                       | •                 |                  |                 |                    |               |

|           | 0 – NO Call                                       | ry-out from the N                                                      | iost Significali  |                  |                 |                    |               |

| Note 1:   | For Borrow, the operand. For rot                  |                                                                        |                   |                  |                 |                    |               |

| 2:        | For Borrow, the operand. For rot source register. |                                                                        |                   |                  |                 |                    |               |

## 10.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

Pins RB2 through RB3 are multiplexed with the ECAN peripheral. Refer to **Section 23.0** "**ECAN™ Technol-ogy**" for proper settings of TRISB when CAN is enabled.

| CLRF  | PORTB  | ; Initialize PORTB by     |

|-------|--------|---------------------------|

|       |        | ; clearing output         |

|       |        | ; data latches            |

| CLRF  | LATB   | ; Alternate method        |

|       |        | ; to clear output         |

|       |        | ; data latches            |

| MOVLW | OEh    | ; Set RB<4:0> as          |

| MOVWF | ADCON1 | ; digital I/O pins        |

|       |        | ; (required if config bit |

|       |        | ; PBADEN is set)          |

| MOVLW | OCFh   | ; Value used to           |

|       |        | ; initialize data         |

|       |        | ; direction               |

| MOVWF | TRISB  | ; Set RB<3:0> as inputs   |

|       |        | ; RB<5:4> as outputs      |

|       |        | ; RB<7:6> as inputs       |

|       |        |                           |

EXAMPLE 10-2: INITIALIZING PORTB

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn <u>on all</u> the pull-ups. This is performed by clearing bit RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on all device Resets.

Note: On a Power-on Reset, RB4:RB0 are configured as analog inputs by default and read as '0'; RB7:RB5 are configured as digital inputs.

> By programming the Configuration bit, PBADEN (CONFIG3H<1>), RB4:RB0 will alternatively be configured as digital inputs on POR.

Four of the PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF (ANY), PORTB instruction). This will end the mismatch condition.

- b) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

## 10.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 10-5). The pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

## Note: On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

## EXAMPLE 10-3: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by ; clearing output |

|-------|-------|-----------------------------------------|

|       |       | ; data latches                          |

| CLRF  | LATC  | ; Alternate method                      |

|       |       | ; to clear output                       |

|       |       | ; data latches                          |

| MOVLW | OCFh  | ; Value used to                         |

|       |       | ; initialize data                       |

|       |       | ; direction                             |

| MOVWF | TRISC | ,                                       |

|       |       | ; RC<5:4> as outputs                    |

|       |       | ; RC<7:6> as inputs                     |

|       |       |                                         |

|                         |                      |                        |              |              |                       | _       |         |                        |                            |

|-------------------------|----------------------|------------------------|--------------|--------------|-----------------------|---------|---------|------------------------|----------------------------|

| Name                    | Bit 7                | Bit 6                  | Bit 5        | Bit 4        | Bit 3                 | Bit 2   | Bit 1   | Bit 0                  | Reset<br>Values<br>on page |

| INTCON                  | GIE/GIEH             | PEIE/GIEL              | TMR0IE       | INT0IE       | RBIE                  | TMR0IF  | INT0IF  | RBIF                   | 51                         |

| RCON                    | IPEN                 | SBOREN <sup>(2)</sup>  | _            | RI           | TO                    | PD      | POR     | BOR                    | 52                         |

| IPR1                    | PSPIP <sup>(1)</sup> | ADIP                   | RCIP         | TXIP         | SSPIP                 | CCP1IP  | TMR2IP  | TMR1IP                 | 54                         |

| PIR1                    | PSPIF <sup>(1)</sup> | ADIF                   | RCIF         | TXIF         | SSPIF                 | CCP1IF  | TMR2IF  | TMR1IF                 | 54                         |

| PIE1                    | PSPIE <sup>(1)</sup> | ADIE                   | RCIE         | TXIE         | SSPIE                 | CCP1IE  | TMR2IE  | TMR1IE                 | 54                         |

| IPR2                    | OSCFIP               | CMIP <sup>(1)</sup>    |              | EEIP         | BCLIP                 | HLVDIP  | TMR3IP  | ECCP1IP <sup>(1)</sup> | 54                         |

| PIR2                    | OSCFIF               | CMIF <sup>(1)</sup>    |              | EEIF         | BCLIF                 | HLVDIF  | TMR3IF  | ECCP1IF <sup>(1)</sup> | 54                         |

| PIE2                    | OSCFIE               | CMIE <sup>(1)</sup>    | _            | EEIE         | BCLIE                 | HLVDIE  | TMR3IE  | ECCP1IE <sup>(1)</sup> | 53                         |

| TRISB                   | PORTB Dat            | a Direction R          | egister      |              |                       |         |         |                        | 54                         |

| TRISC                   | PORTC Dat            | ta Direction R         | egister      |              |                       |         |         |                        | 54                         |

| TMR1L                   | Timer1 Reg           | ister Low Byte         | е            |              |                       |         |         |                        | 52                         |

| TMR1H                   | Timer1 Reg           | ister High Byt         | e            |              |                       |         |         |                        | 52                         |

| T1CON                   | RD16                 | T1RUN                  | T1CKPS1      | T1CKPS0      | T1OSCEN               | T1SYNC  | TMR1CS  | TMR10N                 | 52                         |

| TMR3H                   | Timer3 Reg           | ister High Byt         | e            |              |                       |         |         |                        | 53                         |

| TMR3L                   | Timer3 Reg           | ister Low Byte         | е            |              |                       |         |         |                        | 53                         |

| T3CON                   | RD16                 | T3ECCP1 <sup>(1)</sup> | T3CKPS1      | T3CKPS0      | T3CCP1 <sup>(1)</sup> | T3SYNC  | TMR3CS  | TMR3ON                 | 53                         |

| CCPR1L                  | Capture/Co           | mpare/PWM              | Register 1 L | ow Byte      |                       |         |         |                        | 53                         |

| CCPR1H                  | Capture/Co           | mpare/PWM              | Register 1 H | ligh Byte    |                       |         |         |                        | 53                         |

| CCP1CON                 |                      | —                      | DC1B1        | DC1B0        | CCP1M3                | CCP1M2  | CCP1M1  | CCP1M0                 | 53                         |

| ECCPR1L <sup>(1)</sup>  | Enhanced C           | Capture/Comp           | are/PWM R    | egister 1 Lo | ow Byte               |         |         |                        | 53                         |

| ECCPR1H <sup>(1)</sup>  | Enhanced C           | Capture/Comp           | are/PWM R    | egister 1 H  | igh Byte              |         |         |                        | 53                         |

| ECCP1CON <sup>(1)</sup> | EPWM1M1              | EPWM1M0                | EDC1B1       | EDC1B0       | ECCP1M3               | ECCP1M2 | ECCP1M1 | ECCP1M0                | 53                         |

## TABLE 15-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

Legend: — = unimplemented, read as '0'. Shaded cells are not used by Capture and Compare, Timer1 or Timer3.

Note 1: These bits or registers are available on PIC18F4682/4685 devices only.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'.

## 16.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the ECCPR1L register and to the ECCP1CON<5:4> bits. Up to 10-bit resolution is available. The ECCPR1L contains the eight MSbs and the ECCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by ECCPR1L:ECCP1CON<5:4>. The PWM duty cycle is calculated by the following equation.

## EQUATION 16-2:

| PWM Duty Cycle = | (ECCPR1L:ECCP1CON<5:4> •     |

|------------------|------------------------------|

|                  | TOSC • (TMR2 Prescale Value) |

ECCPR1L and ECCP1CON<5:4> can be written to at any time, but the duty cycle value is not copied into ECCPR1H until a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, ECCPR1H is a read-only register.

The ECCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation. When the ECCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or two bits of the TMR2 prescaler, the ECCP1 pin is cleared. The maximum PWM resolution (bits) for a given PWM frequency is given by the following equation.

## **EQUATION 16-3:**

PWM Resolution (max) =

$$\frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the ECCP1 pin will not be cleared.

## 16.4.3 PWM OUTPUT CONFIGURATIONS

The EPWM1M1:EPWM1M0 bits in the ECCP1CON register allow one of four configurations:

- Single Output

- · Half-Bridge Output

- Full-Bridge Output, Forward mode

- Full-Bridge Output, Reverse mode

The Single Output mode is the standard PWM mode discussed in **Section 16.4 "Enhanced PWM Mode"**. The Half-Bridge and Full-Bridge Output modes are covered in detail in the sections that follow.

The general relationship of the outputs in all configurations is summarized in Figure 16-2.

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

TABLE 16-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

## 17.3.2 OPERATION

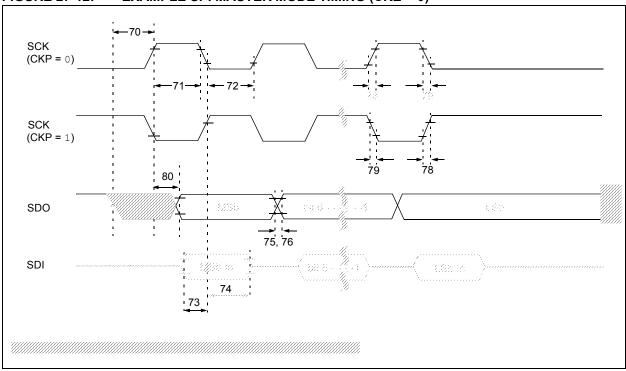

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

The MSSP module consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full detect bit, BF (SSPSTAT<0>) and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL (SSPCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 17-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

## EXAMPLE 17-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | BTFSS | SSPSTAT, BF | ;Has data been received (transmit complete)? |

|------|-------|-------------|----------------------------------------------|

|      | BRA   | LOOP        | ;No                                          |

|      | MOVF  | SSPBUF, W   | ;WREG reg = contents of SSPBUF               |

|      | MOVWF | RXDATA      | ;Save in user RAM, if data is meaningful     |

|      | MOVF  | TXDATA, W   | ;W reg = contents of TXDATA                  |

|      | MOVWF | SSPBUF      | ;New data to xmit                            |

| Moden      | R/C-0                                                                                                                                                                                  | R/W-0                       | R/W-0            | U-0           | R-0             | R/W-0         | R-0           | R-0     |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|---------------|-----------------|---------------|---------------|---------|--|--|--|--|--|

| Mode 0     | RXFUL <sup>(1)</sup>                                                                                                                                                                   | RXM1                        | RXM0             |               | RXRTRRO         | FILHIT2       | FILHIT1       | FILHIT0 |  |  |  |  |  |

|            | <b>D</b> / <b>D</b> / <b>D</b>                                                                                                                                                         |                             |                  |               |                 |               |               |         |  |  |  |  |  |

| Mode 1,2   | R/C-0                                                                                                                                                                                  | R/W-0                       | R-0              | R-0           | R-0             | R-0           | R-0           | R-0     |  |  |  |  |  |

|            | RXFUL <sup>(1)</sup>                                                                                                                                                                   | RXM1                        | RTRRO            | FILHIT4       | FILHIT3         | FILHIT2       | FILHIT1       | FILHITO |  |  |  |  |  |

|            | bit 7                                                                                                                                                                                  |                             |                  |               |                 |               |               | bit (   |  |  |  |  |  |

| Legend:    |                                                                                                                                                                                        |                             | C = Clearabl     | e bit         |                 |               |               |         |  |  |  |  |  |

| R = Reada  | able bit                                                                                                                                                                               |                             | W = Writable     | bit           | U = Unimple     | mented bit, r | ead as '0'    |         |  |  |  |  |  |

| -n = Value | at POR                                                                                                                                                                                 |                             | '1' = Bit is se  | t             | '0' = Bit is cl | eared         | x = Bit is un | known   |  |  |  |  |  |

|            |                                                                                                                                                                                        |                             | (1)              |               |                 |               |               |         |  |  |  |  |  |

| bit 7      | RXFUL: Rece                                                                                                                                                                            |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | 1 = Receive buffer contains a received message                                                                                                                                         |                             |                  |               |                 |               |               |         |  |  |  |  |  |

| bit 6      | 0 = Receive buffer is open to receive a new message<br>Mode 0:                                                                                                                         |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | <b>RXM1:</b> Receive Buffer Mode bit 1 (combines with RXM0 to form RXM<1:0> bits, see bit 5)                                                                                           |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | 11 = Receive all messages (including those with errors); filter criteria is ignored                                                                                                    |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | 10 = Receive only valid messages with extended identifier; EXIDEN in RXFnSIDL must be '1'<br>01 = Receive only valid messages with standard identifier, EXIDEN in RXFnSIDL must be '0' |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | 01 = Receive only valid messages with standard identifier, EXIDEN in RXFNSIDL must be '0'<br>00 = Receive all valid messages as per EXIDEN bit in RXFnSIDL register                    |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | Mode 1, 2:                                                                                                                                                                             |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | RXM1: Receive Buffer Mode bit                                                                                                                                                          |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | <ul> <li>1 = Receive all messages (including those with errors); acceptance filters are ignored</li> <li>0 = Receive all valid messages as per acceptance filters</li> </ul>           |                             |                  |               |                 |               |               |         |  |  |  |  |  |

| bit 5      | Mode 0:<br><b>RXM0:</b> Receive Buffer Mode bit 0 (combines with RXM1 to form RXM<1:0> bits, see bit 6)                                                                                |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | Mode 1, 2:                                                                                                                                                                             |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | RTRRO: Remote Transmission Request bit for Received Message (read-only)                                                                                                                |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | <ul> <li>1 = A remote transmission request is received</li> <li>0 = A remote transmission request is not received</li> </ul>                                                           |                             |                  |               |                 |               |               |         |  |  |  |  |  |

| bit 4      |                                                                                                                                                                                        | ransmission                 | request is not   | received      |                 |               |               |         |  |  |  |  |  |

| DIL 4      | Mode 0:<br>Unimplement                                                                                                                                                                 | ed: Read as                 | <b>s</b> 'O'     |               |                 |               |               |         |  |  |  |  |  |

|            | Mode 1, 2:                                                                                                                                                                             |                             |                  |               |                 |               |               |         |  |  |  |  |  |

|            | FILHIT4: Filter                                                                                                                                                                        |                             |                  | <b>c</b>      |                 |               |               |         |  |  |  |  |  |

|            | This bit combi                                                                                                                                                                         | nes with oth                | er bits to form  | filter accept | ance bits <4:0  | )>.           |               |         |  |  |  |  |  |

|            | <u>Mode 0:</u><br>RXRTRRO: R                                                                                                                                                           | emote Trans                 | smission Requ    | est bit for R | eceived Mess    | age (read-or  | nlv)          |         |  |  |  |  |  |

| bit 3      | <b>RXRTRRO:</b> Remote Transmission Request bit for Received Message (read-only)<br>1 = A remote transmission request is received                                                      |                             |                  |               |                 |               |               |         |  |  |  |  |  |

| bit 3      |                                                                                                                                                                                        |                             |                  |               |                 |               |               |         |  |  |  |  |  |

| bit 3      | 0 = A remote t                                                                                                                                                                         |                             |                  |               |                 |               |               |         |  |  |  |  |  |

| bit 3      | 0 = A remote t<br><u>Mode 1, 2:</u>                                                                                                                                                    | transmission                |                  |               |                 |               |               |         |  |  |  |  |  |

| dit 3      | 0 = A remote t                                                                                                                                                                         | transmission<br>r Hit bit 3 | n request is not | received      | ance bits <4:0  | )>.           |               |         |  |  |  |  |  |

## REGISTER 23-14: RXB1CON: RECEIVE BUFFER 1 CONTROL REGISTER

| RXFBCON6         R/W-0                                                                                                                                             |          |         |         |         |         |         |         |         |         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|---------|---------|---------|---------|---------|---------|---------|

| F1BP_3         F1BP_2         F1BP_1         F1BP_0         F0BP_3         F0BP_2         F0BP_1         F0BP_0           RXFBCON1         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-1         R/W-0         R/W-0         R/W-1         F3BP_2         F3BP_1         F3BP_0         F2BP_3         F2BP_2         F2BP_1         F2BP_1         F2BP_0           RXFBCON2         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-1         R/W-0         R/W-0         R/W-1         F3BP_2         F3BP_1         F3BP_0         F3BP_3         F3BP_1         F3BP_0         F3BP_3         F3BP_2         F3BP_1         F3BP_0         R/W-0         R/W-0         R/W-1         F4BP_0           RXFBCON3         R/W-0         R/W-0 <t< td=""><td></td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td></t<>                     |          | R/W-0   |

| RXFBCON1         F3BP_3         F3BP_2         F3BP_1         F3BP_0         F2BP_3         F2BP_2         F2BP_1         F2BP_0           RXFBCON2         R/W-0         R/W-1         R/W-0         R/W-0         R/W-1         F4BP_3         F4BP_2         F4BP_1         F4BP_0           RXFBCON3         R/W-0         R/W-0 <td>KAFBCUNU</td> <td>F1BP_3</td> <td>F1BP_2</td> <td>F1BP_1</td> <td>F1BP_0</td> <td>F0BP_3</td> <td>F0BP_2</td> <td>F0BP_1</td> <td>F0BP_0</td> | KAFBCUNU | F1BP_3  | F1BP_2  | F1BP_1  | F1BP_0  | F0BP_3  | F0BP_2  | F0BP_1  | F0BP_0  |

| RXFBCON1         F3BP_3         F3BP_2         F3BP_1         F3BP_0         F2BP_3         F2BP_2         F2BP_1         F2BP_0           RXFBCON2         R/W-0         R/W-1         R/W-0         R/W-0         R/W-1         F4BP_3         F4BP_2         F4BP_1         F4BP_0           RXFBCON3         R/W-0         R/W-0 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                         |          |         |         |         |         |         |         |         |         |

| F3BP_3         F3BP_2         F3BP_1         F3BP_0         F2BP_3         F2BP_2         F2BP_1         F2BP_0           RXFBCON2         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-1         R/W-0         R/W-0         R/W-1         R/W-0         R/W-0         R/W-1         F3BP_2         F4BP_3         F4BP_2         F4BP_1         F4BP_0           RXFBCON3         R/W-0                                                                                                                                                     | DYERCON1 | R/W-0   | R/W-0   | R/W-0   | R/W-1   | R/W-0   | R/W-0   | R/W-0   | R/W-1   |

| RXFBCON2         F5BP_3         F5BP_2         F5BP_1         F5BP_0         F4BP_3         F4BP_2         F4BP_1         F4BP_0           RXFBCON3         R/W-0                                                                                                                                              | KAFBCONT | F3BP_3  | F3BP_2  | F3BP_1  | F3BP_0  | F2BP_3  | F2BP_2  | F2BP_1  | F2BP_0  |

| RXFBCON2         F5BP_3         F5BP_2         F5BP_1         F5BP_0         F4BP_3         F4BP_2         F4BP_1         F4BP_0           RXFBCON3         R/W-0                                                                                                                                              |          |         |         |         |         |         |         |         |         |

| F5BP_3         F5BP_2         F5BP_1         F5BP_0         F4BP_3         F4BP_2         F4BP_1         F4BP_0           RXFBCON3         R/W-0                                                                                                                                                 | PYERCON? | R/W-0   | R/W-0   | R/W-0   | R/W-1   | R/W-0   | R/W-0   | R/W-0   | R/W-1   |

| RXFBCON3         F7BP_3         F7BP_2         F7BP_1         F7BP_0         F6BP_3         F6BP_2         F6BP_1         F6BP_0           RXFBCON4         R/W-0                                                                                                                                              |          | F5BP_3  | F5BP_2  | F5BP_1  | F5BP_0  | F4BP_3  | F4BP_2  | F4BP_1  | F4BP_0  |

| RXFBCON3         F7BP_3         F7BP_2         F7BP_1         F7BP_0         F6BP_3         F6BP_2         F6BP_1         F6BP_0           RXFBCON4         R/W-0                                                                                                                                              |          |         |         |         |         |         |         |         |         |

| F7BP_3         F7BP_2         F7BP_1         F7BP_0         F6BP_3         F6BP_2         F6BP_1         F6BP_0           RXFBCON4         R/W-0                                                                                                                                                 | PYERCON3 | R/W-0   |

| RXFBCON4         F9BP_3         F9BP_2         F9BP_1         F9BP_0         F8BP_3         F8BP_2         F8BP_1         F8BP_0           RXFBCON5         R/W-0                                                                                                                                              |          | F7BP_3  | F7BP_2  | F7BP_1  | F7BP_0  | F6BP_3  | F6BP_2  | F6BP_1  | F6BP_0  |

| RXFBCON4         F9BP_3         F9BP_2         F9BP_1         F9BP_0         F8BP_3         F8BP_2         F8BP_1         F8BP_0           RXFBCON5         R/W-0                                                                                                                                              |          |         |         |         |         |         |         |         |         |

| F9BP_3         F9BP_2         F9BP_1         F9BP_0         F8BP_3         F8BP_2         F8BP_1         F8BP_0           RXFBCON5         R/W-0                                                                                                                                                 | RYEBCON4 | R/W-0   |

| RXFBCON5         F11BP_3         F11BP_2         F11BP_1         F11BP_0         F10BP_3         F10BP_2         F10BP_1         F10BP_0           RXFBCON6         R/W-0         R/W-                                                                                                                                       |          | F9BP_3  | F9BP_2  | F9BP_1  | F9BP_0  | F8BP_3  | F8BP_2  | F8BP_1  | F8BP_0  |

| RXFBCON5         F11BP_3         F11BP_2         F11BP_1         F11BP_0         F10BP_3         F10BP_2         F10BP_1         F10BP_0           RXFBCON6         R/W-0         R/W-                                                                                                                                       |          |         |         |         |         |         |         |         |         |

| RXFBCON6         R/W-0                                                                                                                                             | RYFRCONS | R/W-0   | R/W-0   | R/W-0   | R/W-0   |         | R/W-0   | R/W-0   | R/W-0   |

| RXFBCON6         F13BP_3         F13BP_2         F13BP_1         F13BP_0         F12BP_3         F12BP_2         F12BP_1         F12BP_0           RXFBCON7         R/W-0         R/W-                                                                                                                                       |          | F11BP_3 | F11BP_2 | F11BP_1 | F11BP_0 | F10BP_3 | F10BP_2 | F10BP_1 | F10BP_0 |

| RXFBCON6         F13BP_3         F13BP_2         F13BP_1         F13BP_0         F12BP_3         F12BP_2         F12BP_1         F12BP_0           RXFBCON7         R/W-0         R/W-                                                                                                                                       |          | 1       |         |         |         |         |         |         |         |

| RXFBCON7         R/W-0                                                                                                                                             | RXFRCONG | R/W-0   |

| <b>F15BP_3</b> F15BP_2 F15BP_1 F15BP_0 F14BP_3 F14BP_2 F14BP_1 F14BP_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | F13BP_3 | F13BP_2 | F13BP_1 | F13BP_0 | F12BP_3 | F12BP_2 | F12BP_1 | F12BP_0 |

| <b>F15BP_3</b> F15BP_2 F15BP_1 F15BP_0 F14BP_3 F14BP_2 F14BP_1 F14BP_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 1       |         |         |         |         |         |         |         |

| F15BP_3 F15BP_2 F15BP_1 F15BP_0 F14BP_3 F14BP_2 F14BP_1 F14BP_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RXFBCON7 | R/W-0   |

| bit 7 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | F15BP_3 | F15BP_2 | F15BP_1 | F15BP_0 | F14BP_3 | F14BP_2 | F14BP_1 | F14BP_0 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | bit 7   |         |         |         |         |         |         | bit C   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |         |         |         |         |         |         |         |         |

## REGISTER 23-47: RXFBCONn: RECEIVE FILTER BUFFER CONTROL REGISTER n<sup>(1)</sup>

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 7-0 FnBP\_3:FnBP\_0: Filter n Buffer Pointer Nibble bits 0000 = Filter n is associated with RXB0 0001 = Filter n is associated with RXB1 0010 = Filter n is associated with B0 0011 = Filter n is associated with B1 ... 0111 = Filter n is associated with B5 1111-1000 = Reserved

Note 1: This register is available in Mode 1 and 2 only.

## 23.15.5 BUS ACTIVITY WAKE-UP INTERRUPT

When the PIC18F2682/2685/4682/4685 devices are in Sleep mode and the bus activity wake-up interrupt is enabled, an interrupt will be generated and the WAKIF bit will be set when activity is detected on the CAN bus. This interrupt causes the PIC18F2682/2685/4682/ 4685 devices to exit Sleep mode. The interrupt is reset by the MCU, clearing the WAKIF bit.

## 23.15.6 ERROR INTERRUPT

When the error interrupt is enabled, an interrupt is generated if an overflow condition occurs or if the error state of the transmitter or receiver has changed. The error flags in COMSTAT will indicate one of the following conditions.

## 23.15.6.1 Receiver Overflow

An overflow condition occurs when the MAB has assembled a valid received message (the message meets the criteria of the acceptance filters) and the receive buffer associated with the filter is not available for loading of a new message. The associated RXBnOVFL bit in the COMSTAT register will be set to indicate the overflow condition. This bit must be cleared by the MCU.

## 23.15.6.2 Receiver Warning

The receive error counter has reached the MCU warning limit of 96.

## 23.15.6.3 Transmitter Warning

The transmit error counter has reached the MCU warning limit of 96.

## 23.15.6.4 Receiver Bus Passive

The receive error counter has exceeded the errorpassive limit of 127 and the device has gone to error-passive state.

## 23.15.6.5 Transmitter Bus Passive

The transmit error counter has exceeded the errorpassive limit of 127 and the device has gone to error-passive state.

## 23.15.6.6 Bus-Off

The transmit error counter has exceeded 255 and the device has gone to bus-off state.

## 23.15.6.7 Interrupt Acknowledge

Interrupts are directly associated with one or more status flags in the PIR register. Interrupts are pending as long as one of the flags is set. Once an interrupt flag is set by the device, the flag can not be reset by the microcontroller until the interrupt condition is removed.

## REGISTER 24-14: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| -         -         -         -         SWDTEN <sup>(1)</sup> bit 7         bit 0         bit 0 | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                 |

|-------------------------------------------------------------------------------------------------|-------|-----|-----|-----|-----|-----|-----|-----------------------|

| bit 7 bit 0                                                                                     | —     | —   |     |     | —   | —   | _   | SWDTEN <sup>(1)</sup> |

|                                                                                                 | bit 7 |     |     |     |     |     |     | bit 0                 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-1 | Unimplemented: Read as '0'                                           |

|---------|----------------------------------------------------------------------|

| bit 0   | SWDTEN: Software Controlled Watchdog Timer Enable bit <sup>(1)</sup> |

|         | 1 = Watchdog Timer is on                                             |

|         | 0 = Watchdog Timer is off                                            |

**Note 1:** This bit has no effect if the Configuration bit, WDTEN, is enabled.

## TABLE 24-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|--------|-------|-------|-------|-------|-------|--------|----------------------------|

| RCON   | IPEN  | SBOREN | _     | RI    | TO    | PD    | POR   | BOR    | 50                         |

| WDTCON | —     | _      | _     | _     | _     |       |       | SWDTEN | 52                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

Move W to f

$\begin{array}{l} 0 \leq f \leq 255 \\ a \, \in \, [0,1] \end{array}$

MOVWF f {,a}

MOVWF

Operands:

W REG

Syntax:

| MOVLW             | V                   |               |          |     |           |

|-------------------|---------------------|---------------|----------|-----|-----------|

| Syntax:           | MOVLW               | k             |          |     |           |

| Operands:         | $0 \le k \le 255$   | 5             |          |     |           |

| Operation:        | $k\toW$             |               |          |     |           |

| Status Affected:  | None                |               |          |     |           |

| Encoding:         | 0000                | 1110          | kkk      | k   | kkkk      |

| Description:      | The eight-          | bit literal ' | k' is lo | ade | d into W. |

| Words:            | 1                   |               |          |     |           |

| Cycles:           | 1                   |               |          |     |           |

| Q Cycle Activity: |                     |               |          |     |           |

| Q1                | Q2                  | Q3            | 5        |     | Q4        |

| Decode            | Read<br>literal 'k' | Proce<br>Data |          | Wr  | ite to W  |

|                   |                     |               |          |     |           |

| Example:          | MOVLW               | 5Ah           |          |     |           |

| After Instructio  | n                   |               |          |     |           |

W

=

5Ah

| Opera  | tion:                                                                                                                                                                                                                                                                                | $(W) \to f$                                  |               |           |                     |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------|-----------|---------------------|--|--|

| Status | Affected:                                                                                                                                                                                                                                                                            | None                                         |               |           |                     |  |  |

| Encod  | ing:                                                                                                                                                                                                                                                                                 | 0110                                         | 111a          | ffff      | ffff                |  |  |

| Descri | ption:                                                                                                                                                                                                                                                                               | Move data<br>Location 1<br>256-byte b        | ľ can be a    | U         |                     |  |  |

|        |                                                                                                                                                                                                                                                                                      | If 'a' is '0',<br>If 'a' is '1',<br>GPR bank | the BSR i     | s used to |                     |  |  |

|        | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                              |               |           |                     |  |  |