Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 96KB (48K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4685-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.1.2.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 5-1) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bit. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to Section 24.1 "Configuration Bits" for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop returns a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Returning a value of zero to the PC on an<br>underflow has the effect of vectoring the<br>program to the Reset vector, where the<br>stack conditions can be verified and<br>appropriate actions can be taken. This is<br>not the same as a Reset as the contents |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| not the same as a Reset, as the contents of the SFRs are not affected.                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                  |

#### 5.1.2.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

#### DECISTED E 4. STRDTD. STACK DOINTED DECISTED

| REGISTER 5            | -1: STKP1                                                                                                                                                                                                                       | R: STACK P                                              | OINTER RE | GISTER                             |       |                    |       |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------|------------------------------------|-------|--------------------|-------|--|

| R/C-0                 | R/C-0                                                                                                                                                                                                                           | U-0                                                     | R/W-0     | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

| STKFUL <sup>(1)</sup> | STKUNF <sup>(1)</sup>                                                                                                                                                                                                           | _                                                       | SP4       | SP3                                | SP2   | SP1                | SP0   |  |

| bit 7                 |                                                                                                                                                                                                                                 |                                                         |           |                                    |       |                    | bit 0 |  |

|                       |                                                                                                                                                                                                                                 |                                                         |           |                                    |       |                    |       |  |

| Legend:               |                                                                                                                                                                                                                                 | C = Clearable                                           | bit       |                                    |       |                    |       |  |

| R = Readable          | bit                                                                                                                                                                                                                             | W = Writable                                            | bit       | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at F       | POR                                                                                                                                                                                                                             | '1' = Bit is set                                        |           | '0' = Bit is cle                   | ared  | x = Bit is unknown |       |  |

| bit 7<br>bit 6        | <b>STKFUL:</b> Stack Full Flag bit <sup>(1)</sup><br>1 = Stack became full or overflowed<br>0 = Stack has not become full or overflow<br><b>STKUNF:</b> Stack Underflow Flag bit <sup>(1)</sup><br>1 = Stack underflow occurred |                                                         |           |                                    |       |                    |       |  |

| bit 5<br>bit 4-0      | Unimplemen                                                                                                                                                                                                                      | lerflow did not o<br>ted: Read as 'o<br>ack Pointer Loc | כי        |                                    |       |                    |       |  |

Note 1: Bit 7 and bit 6 are cleared by user software or by a POR.

| Name   | Bit 7                                               | Bit 6               | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1                     | Bit 0                  | Reset<br>Values<br>on page |

|--------|-----------------------------------------------------|---------------------|-------------|--------|-------|--------|---------------------------|------------------------|----------------------------|

| INTCON | GIE/GIEH                                            | PEIE/GIEL           | TMR0IE      | INT0IE | RBIE  | TMR0IF | INT0IF                    | RBIF                   | 51                         |

| EEADRH | —                                                   | —                   |             | —      | —     | —      | EEPROM Ac<br>Register Hig | 53                     |                            |

| EEADR  | EEPROM /                                            | Address Reg         | ister Low B | yte    |       |        |                           |                        | 53                         |

| EEDATA | EEPROM I                                            | Data Registe        | r           |        |       |        |                           |                        | 53                         |

| EECON2 | EEPROM Control Register 2 (not a physical register) |                     |             |        |       |        |                           | 53                     |                            |

| EECON1 | EEPGD                                               | CFGS                | —           | FREE   | WRERR | WREN   | WR                        | RD                     | 53                         |

| IPR2   | OSCFIP                                              | CMIP <sup>(1)</sup> | —           | EEIP   | BCLIP | HLVDIP | TMR3IP                    | ECCP1IP <sup>(1)</sup> | 53                         |

| PIR2   | OSCFIF                                              | CMIF <sup>(1)</sup> | _           | EEIF   | BCLIF | HLVDIF | TMR3IF                    | ECCP1IF <sup>(1)</sup> | 54                         |

| PIE2   | OSCFIE                                              | CMIE <sup>(1)</sup> |             | EEIE   | BCLIE | HLVDIE | TMR3IE                    | ECCP1IE <sup>(1)</sup> | 54                         |

### TABLE 7-1: REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

Legend: — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

Note 1: These bits are available in PIC18F4682/4685 devices and reserved in PIC18F2682/2685 devices.

## 11.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS2:T0PS0 bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

### 11.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

## 11.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

|        | I. KEOK                  |                           |          |              |                                                                   |        |        |       |                            |  |

|--------|--------------------------|---------------------------|----------|--------------|-------------------------------------------------------------------|--------|--------|-------|----------------------------|--|

| Name   | Bit 7                    | Bit 6                     | Bit 5    | Bit 4        | Bit 3                                                             | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |  |

| TMR0L  | Timer0 Register Low Byte |                           |          |              |                                                                   |        |        |       | 52                         |  |

| TMR0H  | Timer0 Reg               | Timer0 Register High Byte |          |              |                                                                   |        |        |       | 52                         |  |

| INTCON | GIE/GIEH                 | PEIE/GIEL                 | TMR0IE   | INT0IE       | RBIE                                                              | TMR0IF | INT0IF | RBIF  | 51                         |  |

| TOCON  | TMR0ON                   | T08BIT                    | TOCS     | T0SE         | PSA                                                               | T0PS2  | T0PS1  | T0PS0 | 52                         |  |

| TRISA  | TRISA7 <sup>(1)</sup>    | TRISA6 <sup>(1)</sup>     | PORTA Da | ta Direction | <sup>1)</sup> TRISA6 <sup>(1)</sup> PORTA Data Direction Register |        |        |       |                            |  |

TABLE 11-1: REGISTERS ASSOCIATED WITH TIMER0

Legend: x = unknown, u = unchanged, — = unimplemented locations, read as '0'. Shaded cells are not used by Timer0.

**Note 1:** RA7:RA6 and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

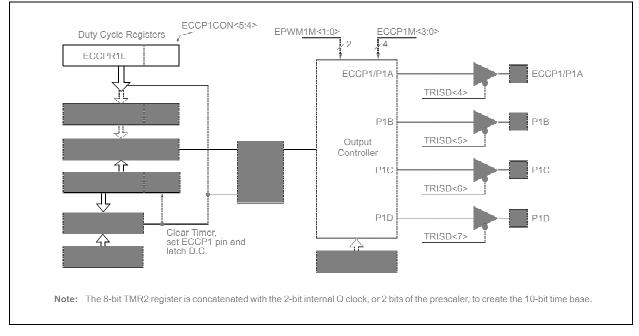

## 16.4 Enhanced PWM Mode

The Enhanced PWM mode provides additional PWM output options for a broader range of control applications. The module is a backward compatible version of the standard CCP1 module and offers up to four outputs, designated P1A through P1D. Users are also able to select the polarity of the signal (either active-high or active-low). The module's output mode and polarity are configured by setting the EPWM1M1:EPWM1M0 and ECCP1M3:ECCP1M0 bits of the ECCP1CON register.

Figure 16-1 shows a simplified block diagram of PWM operation. All control registers are double-buffered and are loaded at the beginning of a new PWM cycle (the period boundary when Timer2 resets) in order to prevent glitches on any of the outputs. The exception is the PWM Dead-Band Delay register, ECCP1DEL, which is loaded at either the duty cycle boundary or the boundary period (whichever comes first). Because of the buffering, the module waits until the assigned timer resets instead of starting immediately. This means that Enhanced PWM waveforms do not exactly match the standard PWM waveforms, but are instead offset by one full instruction cycle (4 Tosc).

As before, the user must manually configure the appropriate TRIS bits for output.

### 16.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following equation.

### EQUATION 16-1:

$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 Prescale Value)$

PWM frequency is defined as 1/[PWM period]. When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The ECCP1 pin is set (if PWM duty cycle = 0%, the ECCP1 pin will not be set)

- The PWM duty cycle is copied from ECCPR1L into ECCPR1H

- Note: The Timer2 postscaler (see Section 13.0 "Timer2 Module") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

## FIGURE 16-1: SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODULE

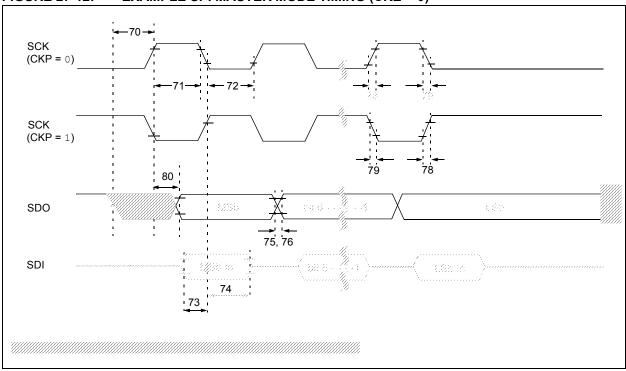

## REGISTER 17-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE)

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | CKP   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | WCOL: Write Collision Detect bit (Transmit mode only)                                                                                                                                                                                                                                                                                                                                           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = The SSPBUF register is written while it is still transmitting the previous word<br/>(must be cleared in software)</li> <li>0 = No collision</li> </ul>                                                                                                                                                                                                                             |

| bit 6   | SSPOV: Receive Overflow Indicator bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>SPI Slave mode:</li> <li>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. The user must read the SSPBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software).</li> <li>0 = No overflow</li> </ul>                   |

| bit 5   | SSPEN: Master Synchronous Serial Port Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = Enables serial port and configures SCK, SDO, SDI and $\overline{SS}$ as serial port pins <sup>(2)</sup><br>0 = Disables serial port and configures these pins as I/O port pins <sup>(2)</sup>                                                                                                                                                                                               |

| bit 4   | CKP: Clock Polarity Select bit                                                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Idle state for clock is a high level</li> <li>0 = Idle state for clock is a low level</li> </ul>                                                                                                                                                                                                                                                                                   |

| bit 3-0 | SSPM3:SSPM0: Master Synchronous Serial Port Mode Select bits <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>0101 = SPI Slave mode, clock = SCK pin, SS pin control disabled, SS can be used as I/O pin</li> <li>0100 = SPI Slave mode, clock = SCK pin, SS pin control enabled</li> <li>0011 = SPI Master mode, clock = TMR2 output/2</li> <li>0010 = SPI Master mode, clock = Fosc/64</li> <li>0001 = SPI Master mode, clock = Fosc/16</li> <li>0000 = SPI Master mode, clock = Fosc/4</li> </ul> |

| Note 1: | In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.                                                                                                                                                                                                                                                         |

- 2: When enabled, these pins must be properly configured as input or output.

- **3:** Bit combinations not specifically listed here are either reserved or implemented in  $I^2C^{TM}$  mode only.

## 17.4.2 OPERATION

The MSSP module functions are enabled by setting MSSP Enable bit, SSPEN (SSPCON<5>).

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock = (Fosc/4) x (SSPADD + 1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 17.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Through the mode select bits, the user can also choose to interrupt on Start and Stop bits

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter 100 and parameter 101.

## 17.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. MSSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated, if enabled) on the falling edge of the ninth SCL pulse.

In 10-Bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit, SSPIF.

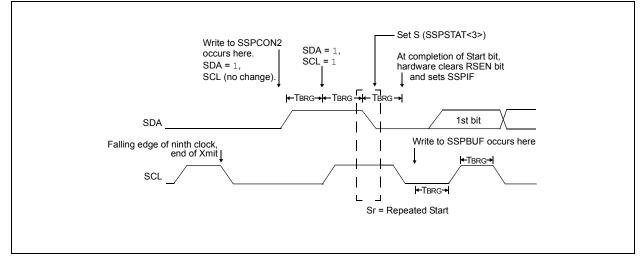

## 17.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an  $\overline{ACK}$  is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

### 17.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

## FIGURE 17-20: REPEATED START CONDITION WAVEFORM

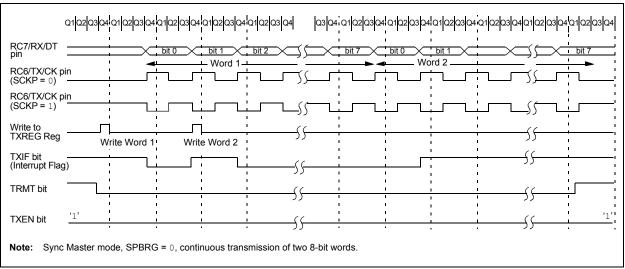

## 18.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the SCKP bit (BAUDCON<4>); setting SCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

#### 18.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 18-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available).

Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## FIGURE 18-11: SYNCHRONOUS TRANSMISSION

| REGISTER 23-1: | CANCON: CAN CONTROL REGISTER |

|----------------|------------------------------|

|----------------|------------------------------|

| Mode 0 | R/W-1  | R/W-0  | R/W-0  | R/S-0 | R/W-0 | R/W-0 | R/W-0 | U-0   |

|--------|--------|--------|--------|-------|-------|-------|-------|-------|

| wode u | REQOP2 | REQOP1 | REQOP0 | ABAT  | WIN2  | WIN1  | WIN0  | —     |

|        | _      |        |        |       |       |       |       |       |

| Mode 1 | R/W-1  | R/W-0  | R/W-0  | R/S-0 | U0    | U-0   | U-0   | U-0   |

|        | REQOP2 | REQOP1 | REQOP0 | ABAT  | —     | _     | —     | —     |

|        |        |        |        |       |       |       |       |       |

| Mode 2 | R/W-1  | R/W-0  | R/W-0  | R/S-0 | R-0   | R-0   | R-0   | R-0   |

| woue z | REQOP2 | REQOP1 | REQOP0 | ABAT  | FP3   | FP2   | FP1   | FP0   |

|        | bit 7  |        |        |       |       |       |       | bit 0 |

|        |        |        |        |       |       |       |       |       |

| Legend:           | S = Settable bit |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 7-5 **REQOP2:REQOP0:** Request CAN Operation Mode bits

- 1xx = Request Configuration mode

- 011 = Request Listen Only mode

- 010 = Request Loopback mode

- 001 = Request Disable mode

- 000 = Request Normal mode

#### bit 4 ABAT: Abort All Pending Transmissions bit

- 1 = Abort all pending transmissions (in all transmit buffers)

- 0 = Transmissions proceeding as normal

#### bit 3-1 Mode 0:

#### WIN2:WIN0: Window Address bits

These bits select which of the CAN buffers to switch into the access bank area. This allows access to the buffer registers from any data memory bank. After a frame has caused an interrupt, the ICODE3:ICODE0 bits can be copied to the WIN3:WIN0 bits to select the correct buffer. See Example 23-2 for a code example.

- 111 = Receive Buffer 0

- 110 = Receive Buffer 0

- 101 = Receive Buffer 1

- 100 = Transmit Buffer 0

- 011 = Transmit Buffer 1

- 010 = Transmit Buffer 2

- 001 = Receive Buffer 0

- 000 = Receive Buffer 0

#### bit 0 Unimplemented: Read as '0'

#### bit 4-0 <u>Mode 1:</u>

Unimplemented: Read as '0'

#### Mode 2:

FP3:FP0: FIFO Read Pointer bits

These bits point to the message buffer to be read.

- 0111:0000 = Message buffer to be read

- 1111:1000 = Reserved

#### REGISTER 23-21: RXERRCNT: RECEIVE ERROR COUNT REGISTER

| REC6 | REC5 | REC4 |      | <b>DE00</b> |      | 5500  |

|------|------|------|------|-------------|------|-------|

|      |      | NLO4 | REC3 | REC2        | REC1 | REC0  |

|      |      |      |      |             |      | bit 0 |

|      |      |      |      |             |      |       |

|      |      |      |      |             |      |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 REC7:REC0: Receive Error Counter bits

This register contains the receive error value as defined by the CAN specifications. When RXERRCNT > 127, the module will go into an error-passive state. RXERRCNT does not have the ability to put the module in "bus-off" state.

#### EXAMPLE 23-5: READING A CAN MESSAGE

```

; Need to read a pending message from RXBO buffer.

; To receive any message, filter, mask and RXM1:RXM0 bits in RXB0CON registers must be

; programmed correctly.

;

; Make sure that there is a message pending in RXBO.

BTFSS RXBOCON, RXFUL

; Does RXB0 contain a message?

BRA

NoMessage

; No. Handle this situation...

; We have verified that a message is pending in RXBO buffer.

; If this buffer can receive both Standard or Extended Identifier messages,

; identify type of message received.

BTFSS RXBOSIDL, EXID

; Is this Extended Identifier?

BRA

StandardMessage

; No. This is Standard Identifier message.

; Yes. This is Extended Identifier message.

; Read all 29-bits of Extended Identifier message.

; Now read all data bytes

MOVFF RXB0DO, MY DATA BYTE1

. . .

; Once entire message is read, mark the RXB0 that it is read and no longer FULL.

RXB0CON, RXFUL

; This will allow CAN Module to load new messages

BCF

; into this buffer.

. . .

```

# 23.2.3.1 Programmable TX/RX and Auto-RTR Buffers

The ECAN module contains 6 message buffers that can be programmed as transmit or receive buffers. Any of these buffers can also be programmed to automatically handle RTR messages.

**Note:** These registers are not used in Mode 0.

# REGISTER 23-22: BnCON: TX/RX BUFFER n CONTROL REGISTERS IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL0 \le n) = 0]^{(1)}$

| R/W-0                | R/W-0 | R-0     | R-0     | R-0     | R-0     | R-0     | R-0     |

|----------------------|-------|---------|---------|---------|---------|---------|---------|

| RXFUL <sup>(2)</sup> | RXM1  | RXRTRRO | FILHIT4 | FILHIT3 | FILHIT2 | FILHIT1 | FILHIT0 |

| bit 7                |       |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | <b>RXFUL:</b> Receive Full Status bit <sup>(2)</sup>                                                                                                                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Receive buffer contains a received message                                                                                                                                |

|         | 0 = Receive buffer is open to receive a new message                                                                                                                           |

| bit 6   | RXM1: Receive Buffer Mode bit                                                                                                                                                 |

|         | <ul> <li>1 = Receive all messages including partial and invalid (acceptance filters are ignored)</li> <li>0 = Receive all valid messages as per acceptance filters</li> </ul> |

| bit 5   | RXRTRRO: Read-Only Remote Transmission Request for Received Message bit                                                                                                       |

|         | 1 = Received message is a remote transmission request                                                                                                                         |

|         | 0 = Received message is not a remote transmission request                                                                                                                     |

| bit 4-0 | FILHIT4:FILHIT0: Filter Hit bits                                                                                                                                              |

|         | These bits indicate which acceptance filter enabled the last message reception into this buffer.                                                                              |

|         | 01111 = Acceptance Filter 15 (RXF15)                                                                                                                                          |

|         | 01110 = Acceptance Filter 14 (RXF14)                                                                                                                                          |

|         |                                                                                                                                                                               |

|         | 00001 = Acceptance Filter 1 (RXF1)                                                                                                                                            |

|         | 00000 = Acceptance Filter 0 (RXF0)                                                                                                                                            |

|         |                                                                                                                                                                               |

- **Note 1:** These registers are available in Mode 1 and 2 only.

- 2: This bit is set by the CAN module upon receiving a message and must be cleared by software after the buffer is read. As long as RXFUL is set, no new message will be loaded and the buffer will be considered full.

# REGISTER 23-34: BnDLC: TX/RX BUFFER n DATA LENGTH CODE REGISTERS IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL \le n) = 0]^{(1)}$

| U-0   | R-x   | R-x | R-x | R-x  | R-x  | R-x  | R-x   |

|-------|-------|-----|-----|------|------|------|-------|

| —     | RXRTR | RB1 | RB0 | DLC3 | DLC2 | DLC1 | DLC0  |

| bit 7 |       |     |     |      |      |      | bit 0 |

| Legend:    |                                       |                                                            |                       |                    |  |  |  |

|------------|---------------------------------------|------------------------------------------------------------|-----------------------|--------------------|--|--|--|

| R = Reada  | ble bit                               | W = Writable bit                                           | U = Unimplemented bit | , read as '0'      |  |  |  |

| -n = Value | at POR                                | '1' = Bit is set                                           | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |

| bit 7      | Unimpler                              | nented: Read as '0'                                        |                       |                    |  |  |  |

| bit 6      | RXRTR:                                | Receiver Remote Transmiss                                  | sion Request bit      |                    |  |  |  |

|            |                                       | s a remote transmission rec<br>s not a remote transmission | -                     |                    |  |  |  |

| bit 5      | RB1: Res                              | erved bit 1                                                |                       |                    |  |  |  |

|            | Reserved                              | by CAN Spec and read as                                    | ʻ0'.                  |                    |  |  |  |

| bit 4      | RB0: Res                              | erved bit 0                                                |                       |                    |  |  |  |

|            | Reserved by CAN Spec and read as '0'. |                                                            |                       |                    |  |  |  |

| bit 3-0    | DLC3:DLC0: Data Length Code bits      |                                                            |                       |                    |  |  |  |

|            | 1111 <b>= R</b>                       | eserved                                                    |                       |                    |  |  |  |

|            | 1110 <b>= R</b>                       | eserved                                                    |                       |                    |  |  |  |

|            | 1101 <b>= R</b>                       |                                                            |                       |                    |  |  |  |

|            | 1100 <b>= R</b>                       |                                                            |                       |                    |  |  |  |

|            | 1011 <b>= R</b>                       |                                                            |                       |                    |  |  |  |

|            | 1010 = R<br>1001 = R                  |                                                            |                       |                    |  |  |  |

|            |                                       | ata length = 8 bytes                                       |                       |                    |  |  |  |

|            |                                       | ata length = 7 bytes                                       |                       |                    |  |  |  |

|            |                                       | ata length = 6 bytes                                       |                       |                    |  |  |  |

|            |                                       | ata length = 5 bytes                                       |                       |                    |  |  |  |

|            | 0100 <b>= D</b>                       | ata length = 4 bytes                                       |                       |                    |  |  |  |

|            | 0011 <b>= D</b>                       | ata length = 3 bytes                                       |                       |                    |  |  |  |

|            |                                       | ata length = 2 bytes                                       |                       |                    |  |  |  |

|            |                                       | ata length = 1 bytes                                       |                       |                    |  |  |  |

|            | 0000 <b>= D</b>                       | ata length = 0 bytes                                       |                       |                    |  |  |  |

Note 1: These registers are available in Mode 1 and 2 only.

| RXFCON0           | R/W-0   | R/W-0            | R/W-1        | R/W-1          | R/W-1           | R/W-1         | R/W-1          | R/W-1  |

|-------------------|---------|------------------|--------------|----------------|-----------------|---------------|----------------|--------|

| KAFCONU           | RXF7EN  | RXF6EN           | RXF5EN       | RXF4EN         | RXF3EN          | RXF2EN        | RXF1EN         | RXF0EN |

|                   |         |                  |              |                |                 |               |                |        |

| RXFCON1           | R/W-0   | R/W-0            | R/W-0        | R/W-1          | R/W-0           | R/W-0         | R/W-0          | R/W-0  |

| KAFCONT           | RXF15EN | RXF14EN          | RXF13EN      | RXF12EN        | RXF11EN         | RXF10EN       | RXF9EN         | RXF8EN |

|                   | bit 7   |                  |              |                |                 |               |                | bit 0  |

|                   |         |                  |              |                |                 |               |                |        |

| Legend:           |         |                  | C = Clearabl | e bit          |                 |               |                |        |

| R = Readable bit  |         | W = Writable bit |              | U = Unimple    | emented bit, re | ead as '0'    |                |        |

| -n = Value at POR |         | '1' = Bit is se  | t            | '0' = Bit is c | leared          | x = Bit is un | Bit is unknown |        |

|                   |         |                  |              |                |                 |               |                |        |

## **REGISTER 23-45: RXFCONn: RECEIVE FILTER CONTROL REGISTER n** $[0 \le n \le 1]^{(1)}$

bit 7-0 **RXFnEN:** Receive Filter n Enable bits

0 = Filter is disabled

1 = Filter is enabled

Note 1: This register is available in Mode 1 and 2 only.

Note: Register 23-46 through Register 23-51 are writable in Configuration mode only.

## REGISTER 23-46: SDFLC: STANDARD DATA BYTES FILTER LENGTH COUNT REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | FLC4  | FLC3  | FLC2  | FLC1  | FLC0  |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:             |                 |             |                            |                          |                                                                        |  |  |

|---------------------|-----------------|-------------|----------------------------|--------------------------|------------------------------------------------------------------------|--|--|

| R = Readat          | ole bit         | W = Writ    | ' = Writable bit U = Unimp |                          | emented bit, read as '0'                                               |  |  |

| -n = Value a        | at POR          | '1' = Bit i | s set                      | '0' = Bit is cleared     | x = Bit is unknown                                                     |  |  |

|                     |                 |             |                            |                          |                                                                        |  |  |

| bit 7-5             | Unimplemer      | ited: Read  | <b>as '</b> 0'             |                          |                                                                        |  |  |

| bit 4-0             | FLC4:FLC0:      | Filter Leng | gth Count bits             |                          |                                                                        |  |  |

|                     | Mode 0:         |             |                            |                          |                                                                        |  |  |

|                     | Not used; for   | ced to '00  | 000'.                      |                          |                                                                        |  |  |

|                     | 00000-10010 = 0 |             | depends on DL              |                          | e filter. Actual number of bits use<br>3:0> or BnDLC<3:0> if configure |  |  |

|                     | If DLC3:DLC0    | ) = 0000    |                            | ompared with incoming da | ta bits.                                                               |  |  |

| If DLC3:DLC0 = 0001 |                 |             | Up to 8 data bi            | ts of RXFnEID<7:0>, as c | letermined by FLC2:FLC0, will be<br>per of data bits of the incoming   |  |  |

|                     |                 | ) = 0010    | Up to 16 data b            |                          | determined by FLC3:FLC0, will b<br>per of data bits of the incomin     |  |  |

| If DLC3:DLC0 = 0011 |                 |             | Up to 18 data b            |                          | determined by FLC4:FLC0, will b<br>per of data bits of the incomin     |  |  |

Note 1: This register is available in Mode 1 and 2 only.

## TABLE 23-1: CAN CONTROLLER REGISTER MAP

| Address <sup>(1)</sup> | Name                    | Address | Name                       | Address | Name                       | Address | Name     |

|------------------------|-------------------------|---------|----------------------------|---------|----------------------------|---------|----------|

| F7Fh                   | SPBRGH <sup>(3)</sup>   | F5Fh    | CANCON_RO0                 | F3Fh    | CANCON_RO2                 | F1Fh    | RXM1EIDL |

| F7Eh                   | BAUDCON <sup>(3)</sup>  | F5Eh    | CANSTAT_RO0                | F3Eh    | CANSTAT_RO2                | F1Eh    | RXM1EIDH |

| F7Dh                   | (4)                     | F5Dh    | RXB1D7                     | F3Dh    | TXB1D7                     | F1Dh    | RXM1SIDL |

| F7Ch                   | (4)                     | F5Ch    | RXB1D6                     | F3Ch    | TXB1D6                     | F1Ch    | RXM1SIDH |

| F7Bh                   | (4)                     | F5Bh    | RXB1D5                     | F3Bh    | TXB1D5                     | F1Bh    | RXM0EIDL |

| F7Ah                   | (4)                     | F5Ah    | RXB1D4                     | F3Ah    | TXB1D4                     | F1Ah    | RXM0EIDH |

| F79h                   | ECCP1DEL <sup>(3)</sup> | F59h    | RXB1D3                     | F39h    | TXB1D3                     | F19h    | RXM0SIDL |

| F78h                   | (4)                     | F58h    | RXB1D2                     | F38h    | TXB1D2                     | F18h    | RXM0SIDH |

| F77h                   | ECANCON                 | F57h    | RXB1D1                     | F37h    | TXB1D1                     | F17h    | RXF5EIDL |

| F76h                   | TXERRCNT                | F56h    | RXB1D0                     | F36h    | TXB1D0                     | F16h    | RXF5EIDH |

| F75h                   | RXERRCNT                | F55h    | RXB1DLC                    | F35h    | TXB1DLC                    | F15h    | RXF5SIDL |

| F74h                   | COMSTAT                 | F54h    | RXB1EIDL                   | F34h    | TXB1EIDL                   | F14h    | RXF5SIDH |

| F73h                   | CIOCON                  | F53h    | RXB1EIDH                   | F33h    | TXB1EIDH                   | F13h    | RXF4EIDL |

| F72h                   | BRGCON3                 | F52h    | RXB1SIDL                   | F32h    | TXB1SIDL                   | F12h    | RXF4EIDH |

| F71h                   | BRGCON2                 | F51h    | RXB1SIDH                   | F31h    | TXB1SIDH                   | F11h    | RXF4SIDL |

| F70h                   | BRGCON1                 | F50h    | RXB1CON                    | F30h    | TXB1CON                    | F10h    | RXF4SIDH |

| F6Fh                   | CANCON                  | F4Fh    | CANCON_RO1 <sup>(2)</sup>  | F2Fh    | CANCON_RO3 <sup>(2)</sup>  | F0Fh    | RXF3EIDL |

| F6Eh                   | CANSTAT                 | F4Eh    | CANSTAT_RO1 <sup>(2)</sup> | F2Eh    | CANSTAT_RO3 <sup>(2)</sup> | F0Eh    | RXF3EIDH |

| F6Dh                   | RXB0D7                  | F4Dh    | TXB0D7                     | F2Dh    | TXB2D7                     | F0Dh    | RXF3SIDL |

| F6Ch                   | RXB0D6                  | F4Ch    | TXB0D6                     | F2Ch    | TXB2D6                     | F0Ch    | RXF3SIDH |

| F6Bh                   | RXB0D5                  | F4Bh    | TXB0D5                     | F2Bh    | TXB2D5                     | F0Bh    | RXF2EIDL |

| F6Ah                   | RXB0D4                  | F4Ah    | TXB0D4                     | F2Ah    | TXB2D4                     | F0Ah    | RXF2EIDH |

| F69h                   | RXB0D3                  | F49h    | TXB0D3                     | F29h    | TXB2D3                     | F09h    | RXF2SIDL |

| F68h                   | RXB0D2                  | F48h    | TXB0D2                     | F28h    | TXB2D2                     | F08h    | RXF2SIDH |

| F67h                   | RXB0D1                  | F47h    | TXB0D1                     | F27h    | TXB2D1                     | F07h    | RXF1EIDL |

| F66h                   | RXB0D0                  | F46h    | TXB0D0                     | F26h    | TXB2D0                     | F06h    | RXF1EIDH |

| F65h                   | RXB0DLC                 | F45h    | TXB0DLC                    | F25h    | TXB2DLC                    | F05h    | RXF1SIDL |

| F64h                   | RXB0EIDL                | F44h    | TXB0EIDL                   | F24h    | TXB2EIDL                   | F04h    | RXF1SIDH |

| F63h                   | RXB0EIDH                | F43h    | TXB0EIDH                   | F23h    | TXB2EIDH                   | F03h    | RXF0EIDL |

| F62h                   | RXB0SIDL                | F42h    | TXB0SIDL                   | F22h    | TXB2SIDL                   | F02h    | RXF0EIDH |

| F61h                   | RXB0SIDH                | F41h    | TXB0SIDH                   | F21h    | TXB2SIDH                   | F01h    | RXF0SIDL |

| F60h                   | RXB0CON                 | F40h    | TXB0CON                    | F20h    | TXB2CON                    | F00h    | RXF0SIDH |

Note 1: Shaded registers are available in Access Bank low area, while the rest are available in Bank 15.

2: CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the controller register due to the Microchip header file requirement.

**3:** These registers are not CAN registers.

4: Unimplemented registers are read as '0'.

#### 23.9.1 EXTERNAL CLOCK, INTERNAL CLOCK AND MEASURABLE JITTER IN HSPLL-BASED OSCILLATORS

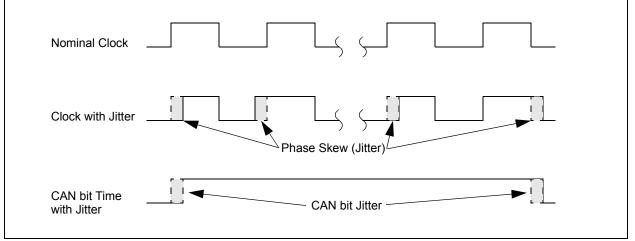

The microcontroller clock frequency generated from a PLL circuit is subject to a jitter, also defined as Phase Jitter or Phase Skew. For its PIC18 Enhanced microcontrollers, Microchip specifies phase jitter ( $P_{\text{jitter}}$ ) as being 2% (Gaussian distribution, within 3 standard deviations, see parameter F13 in Table 27-7) and Total Jitter ( $T_{\text{jitter}}$ ) as being 2 \*  $P_{\text{jitter}}$ .

The CAN protocol uses a bit-stuffing technique that inserts a bit of a given polarity following five bits with the opposite polarity. This gives a total of 10 bits transmitted without re-synchronization (compensation for jitter or phase error).

Given the random nature of the jitter error added, it can be shown that the total error caused by the jitter tends to cancel itself over time. For a period of 10 bits, it is necessary to add only two jitter intervals to correct for jitter-induced error: one interval in the beginning of the 10-bit period and another at the end. The overall effect is shown in Figure 23-5.

## FIGURE 23-5: EFFECTS OF PHASE JITTER ON THE MICROCONTROLLER CLOCK AND CAN BIT TIME

Once these considerations are taken into account, it is possible to show that the relation between the jitter and the total frequency error can be defined as:

#### EQUATION 23-4:

$$\Delta f = \frac{T_{\text{jitter}}}{10 \times \text{NBT}} = \frac{2 \times P_{\text{jitter}}}{10 \times \text{NBT}}$$

where jitter is expressed in terms of time and NBT is the Nominal Bit Time.

For example, assume a CAN bit rate of 125 Kb/s, which gives an NBT of 8  $\mu$ s. For a 16 MHz clock generated from a 4x PLL, the jitter at this clock frequency is:

#### **EQUATION 23-5:**

$$2\% \times \frac{1}{16 \text{ MHz}} = \frac{0.02}{16 \times 10^6} = 1.25 \text{ ns}$$

The resultant frequency error is:

#### EQUATION 23-6:

$$\frac{2 \times (1.25 \times 10^{-9})}{10 \times (8 \times 10^{-6})} = 3.125 \times 10^{-5} = 0.0031\%$$

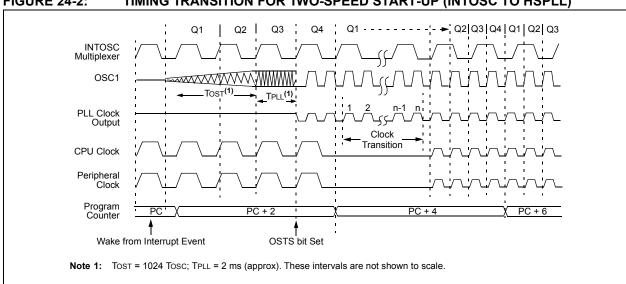

#### 24.3 **Two-Speed Start-up**

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is LP, XT, HS or HSPLL (Crystal-based modes). Other sources do not require an OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI RUN mode.

Because the OSCCON register is cleared on Reset events, the INTOSC (or postscaler) clock source is not initially available after a Reset event; the INTRC clock is used directly at its base frequency. To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF2:IRCF0, immediately after

Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF2:IRCF0 bits prior to entering Sleep mode.

In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 24.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including serial SLEEP instructions (refer to Section 3.1.4 "Multiple Sleep Commands"). In practice, this means that user code can change the SCS1:SCS0 bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

#### **FIGURE 24-2:** TIMING TRANSITION FOR TWO-SPEED START-UP (INTOSC TO HSPLL)

# PIC18F2682/2685/4682/4685

| Syntax:       CPFSGT       f {a}         Operands: $0 \le f \le 255$ $a \in [0,1]$ Operation:       (f) - (W),       skip if (f) > (W)         (unsigned comparison)       Status Affected:       None         Encoding:       0110       010a       ffff         Description:       Compares the contents of data memory location 'f to the contents of the W by performing an unsigned subtraction. If the contents of 'f are greater than the contents of WREG, then the fetched instruction is discarded and a NOP is executed instruction.         If 'a' is '0', the Access Bank is selected. If 'a' is '0', the Access Bank is selected. If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f < 95 (5Fh). See         Section 25.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Addressing mode whenever f < 95 (5Fh). See         Section 25.2.3 "Byte-Oriented and Bit-Oriented Instruction.         Q1       Q2       Q3       Q4         Decode       Read       Process       No         If skip:       Q1       Q2       Q3       Q4         Decode       Read       Process       No         If skip and followed by 2-word instruction:       Q1       Q2       Q3       Q4         Decode       Read       Process       No       No       No <th>CPF</th> <th>SGT</th> <th>Compare</th> <th colspan="4">Compare f with W, Skip if f &gt; W</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CPF     | SGT               | Compare                 | Compare f with W, Skip if f > W |                 |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|-------------------------|---------------------------------|-----------------|--|--|--|--|

| $a \in [0,1]$ Operation: $(f) - (W),$ skip if (f) > (W)<br>(unsigned comparison) Status Affected: None Encoding: $Ollo_0loa_ffff_fff fff_ Description: Compares the contents of data memory location 'f to the contents of data memory location 'f to the contents of the W by performing an unsigned subtraction. If the contents of 'f are greater than the contents of WREG, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. If 'a' is '0', the Access Bank is selected. If 'a' is '0', the Access Bank is selected. If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 25.2.3 "Byte-Oriented and Bit-Oriented Instructions. If skip: Q1 Q2 Q3 Q4 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 No No No No No operation operation operation If skip: Q1 Q2 Q3 Q4 No No No No No Operation operation operation If skip: Q1 Q2 Q3 Q4 No No No No No No No No No operation operation operation If skip and followed by 2-word instruction: Q1 Q2 Q3 Q4 No No No No No Operation operation operation If skip and followed by 2-word instruction: Q1 Q2 Q3 Q4 No No No No No Operation operation operation If skip and followed by 2-word instruction: Q1 Q2 Q3 Q4 No No No No No Operation operation operation No Operation operation operation PC = Address (HERE) M REG > W; HEEG < W; HEG = W;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Synta   | ax:               | CPFSGT                  | CPFSGT f {,a}                   |                 |  |  |  |  |

| Operation:(f) - (W),<br>skip if (f) > (W)<br>(unsigned comparison)Status Affected:NoneEncoding:010 010 ffff ffffDescription:Compares the contents of data memory<br>location f to the contents of the W by<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Oper    | ands:             | $0 \le f \le 255$       |                                 |                 |  |  |  |  |

| $\begin{array}{rcl} & skip if (f) > (W) \\ (unsigned comparison) \\ \\ \mbox{Status Affected: None} \\ \\ \mbox{Encoding: } & 0110 & 010a & ffff & ffff \\ \\ \mbox{Description: } & Compares the contents of data memory location if to the contents of the W by performing an unsigned subtraction. If the contents of WREG, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. If 'a' is '0', the Access Bank is selected. If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f \leq 95 (5Fh). See Section 25.23 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •       |                   | a ∈ [0,1]               |                                 |                 |  |  |  |  |