Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 96KB (48K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4685t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 28/40/44-Pin Enhanced Flash Microcontrollers with ECAN<sup>™</sup> Technology, 10-Bit A/D and nanoWatt Technology

#### **Power-Managed Modes:**

- · Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- · Sleep: CPU off, peripherals off

- Idle mode currents down to 5.8 μA typical

- Sleep mode currents down to 0.1 μÅ typical

- Timer1 Oscillator: 1.1 μA, 32 kHz, 2V

- Watchdog Timer: 2.1 μA

- Two-Speed Oscillator Start-up

#### **Flexible Oscillator Structure:**

- Four Crystal modes, up to 40 MHz

- 4x Phase Lock Loop (PLL) available for crystal and internal oscillators

- · Two External RC modes, up to 4 MHz

- Two External Clock modes, up to 40 MHz

- Internal Oscillator Block:

- 8 user-selectable frequencies, from 31 kHz to 8 MHz

- Provides a complete range of clock speeds,

- from 31 kHz to 32 MHz when used with PLL User-tunable to compensate for frequency drift

- Secondary Oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor

- Allows for safe shutdown if peripheral clock stops

#### **Special Microcontroller Features:**

- C compiler Optimized Architecture with optional Extended Instruction Set

- 100,000 Erase/Write Cycle Enhanced Flash Program Memory typical

- 1,000,000 Erase/Write Cycle Data EEPROM Memory typical

- Flash/Data EEPROM Retention: > 40 years

- Self-Programmable under Software Control

- Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 41 ms to 131s

- Single-Supply 5V In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

- In-Circuit Debug (ICD) via two pins

- Wide operating voltage range: 2.0V to 5.5V

#### Peripheral Highlights:

- High-Current Sink/source 25 mA/25 mA

- Three External Interrupts

- One Capture/Compare/PWM (CCP1) module

- Enhanced Capture/Compare/PWM (ECCP1) module (40/44-pin devices only):

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-shutdown and auto-restart

- Master Synchronous Serial Port (MSSP) module supporting 3-Wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- Enhanced Addressable USART module:

- Supports RS-485, RS-232 and LIN 1.3

- RS-232 operation using internal oscillator block (no external crystal required)

- Auto-wake-up on Start bit

- Auto-Baud Detect

- 10-Bit, up to 11-Channel Analog-to-Digital Converter module (A/D), up to 100 ksps:

- Auto-acquisition capability

- Conversion available during Sleep

- · Dual Analog Comparators with Input Multiplexing

#### **ECAN Module Features:**

- Message bit rates up to 1 Mbps

- · Conforms to CAN 2.0B ACTIVE Specification

- Fully Backward Compatible with PIC18XXX8 CAN modules

- Three Modes of Operation:

- Legacy, Enhanced Legacy, FIFO

- · Three Dedicated Transmit Buffers with Prioritization

- Two Dedicated Receive Buffers

- Six Programmable Receive/Transmit Buffers

- · Three Full, 29-Bit Acceptance Masks

- 16 Full, 29-Bit Acceptance Filters w/Dynamic Association

- DeviceNet™ Data Byte Filter Support

- Automatic Remote Frame Handling

- Advanced Error Management Features

|            | Prog             | ram Memory                    | Data Memory CCP1/ MSSP |                   | RT    |                        | Time and       |     |                             |      |       |                    |

|------------|------------------|-------------------------------|------------------------|-------------------|-------|------------------------|----------------|-----|-----------------------------|------|-------|--------------------|

| Device     | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes)        | EEPROM<br>(bytes) | I/O   | I/O 10-Bit<br>A/D (ch) | ECCP1<br>(PWM) | SPI | Master<br>I <sup>2</sup> C™ | EUSA | Comp. | Timers<br>8/16-bit |

| PIC18F2682 | 80K              | 40960                         | 3328                   | 1024              | 28    | 8                      | 1/0            | Y   | Y                           | 1    | 0     | 1/3                |

| PIC18F2685 | 96K              | 49152                         | 3328                   | 1024              | 28    | 8                      | 1/0            | Y   | Y                           | 1    | 0     | 1/3                |

| PIC18F4682 | 80K              | 40960                         | 3328                   | 1024              | 40/44 | 11                     | 1/1            | Y   | Y                           | 1    | 2     | 1/3                |

| PIC18F4685 | 96K              | 49152                         | 3328                   | 1024              | 40/44 | 11                     | 1/1            | Y   | Y                           | 1    | 2     | 1/3                |

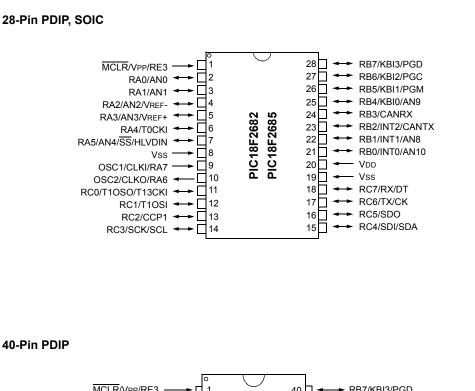

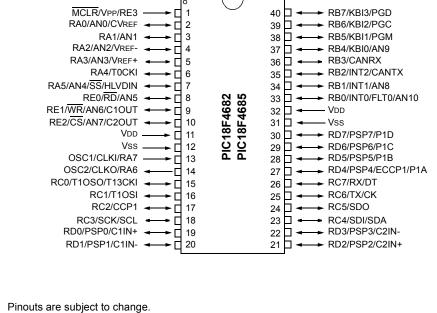

#### **Pin Diagrams**

Note:

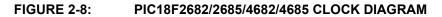

#### 2.7 Clock Sources and Oscillator Switching

Like previous PIC18 devices, the PIC18F2682/2685/ 4682/4685 family includes a feature that allows the device clock source to be switched from the main oscillator to an alternate low-frequency clock source. PIC18F2682/2685/4682/4685 devices offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- · Primary oscillators

- · Secondary oscillators

- · Internal oscillator block

The **primary oscillators** include the External Crystal and Resonator modes, the External RC modes, the External Clock modes and the internal oscillator block. The particular mode is defined by the FOSC3:FOSC0 Configuration bits. The details of these modes are covered earlier in this chapter. The **secondary oscillators** are those external sources not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

PIC18F2682/2685/4682/4685 devices offer the Timer1 oscillator as a secondary oscillator. In all power-managed modes, this oscillator is often the time base for functions such as a Real-Time Clock.

Most often, a 32.768 kHz watch crystal is connected between the RC0/T1OSO/T13CKI and RC1/T1OSI pins. Like the LP mode oscillator circuit, loading capacitors are also connected from each pin to ground.

The Timer1 oscillator is discussed in greater detail in **Section 12.3 "Timer1 Oscillator"**.

In addition to being a primary clock source, the **internal oscillator block** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor.

The clock sources for the PIC18F2682/2685/4682/4685 devices are shown in Figure 2-8. See **Section 24.0 "Special Features of the CPU"** for Configuration register details.

NOTES:

| RXB1SIDH         26           RXB1CON         26           TXB0D7         26           TXB0D6         26           TXB0D5         26           TXB0D3         26           TXB0D2         26           TXB0D1         26           TXB0D2         26           TXB0D1         26 |         | e Devi | ces  | Power-on Reset, | MCLR Resets,<br>WDT Reset,         | Waka un via WDT                 |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|------|-----------------|------------------------------------|---------------------------------|--|--|

| RXB1CON         26           TXB0D7         26           TXB0D6         26           TXB0D5         26           TXB0D4         26           TXB0D3         26           TXB0D2         26           TXB0D1         26           TXB0D2         26           TXB0D1         26   | 00 000- |        |      | Brown-out Reset | RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |

| TXB0D7         26           TXB0D6         26           TXB0D5         26           TXB0D4         26           TXB0D3         26           TXB0D2         26           TXB0D1         26           TXB0D2         26           TXB0D1         26                                | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB0D6         26           TXB0D5         26           TXB0D4         26           TXB0D3         26           TXB0D2         26           TXB0D1         26           TXB0D1         26                                                                                        | 82 2685 | 4682   | 4685 | 0000 - 0000     | 000- 0000                          | uuu- uuuu                       |  |  |

| TXB0D5         26           TXB0D4         26           TXB0D3         26           TXB0D2         26           TXB0D1         26           TXB0D1         26           TXB0D1         26                                                                                        | 82 2685 | 4682   | 4685 | XXXX XXXX       | นนนน นนนน                          | นนนน นนนน                       |  |  |

| TXB0D4         26           TXB0D3         26           TXB0D2         26           TXB0D1         26           TXB0D1         26           TXB0D1         26                                                                                                                    | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | นนนน นนนน                       |  |  |

| TXB0D3         26           TXB0D2         26           TXB0D1         26           TXB0D1         26           TXB0D0         26                                                                                                                                                | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB0D2         26           TXB0D1         26           TXB0D0         26                                                                                                                                                                                                        | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | uuuu uuuu                       |  |  |

| TXB0D1         26           TXB0D0         26                                                                                                                                                                                                                                    | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB0D0 26                                                                                                                                                                                                                                                                        | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

|                                                                                                                                                                                                                                                                                  | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

|                                                                                                                                                                                                                                                                                  | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB0DLC 26                                                                                                                                                                                                                                                                       | 82 2685 | 4682   | 4685 | -x xxxx         | -u uuuu                            | -u uuuu                         |  |  |

| TXB0EIDL 26                                                                                                                                                                                                                                                                      | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB0EIDH 26                                                                                                                                                                                                                                                                      | 82 2685 | 4682   | 4685 | XXXX XXXX       | นนนน นนนน                          | นนนน นนนน                       |  |  |

| TXB0SIDL 26                                                                                                                                                                                                                                                                      | 82 2685 | 4682   | 4685 | XXX- X-XX       | uuu- u-uu                          | uuu- u-uu                       |  |  |

| TXB0SIDH 26                                                                                                                                                                                                                                                                      | 82 2685 | 4682   | 4685 | XXXX XXXX       | นนนน นนนน                          | นนนน นนนน                       |  |  |

| TXB0CON 26                                                                                                                                                                                                                                                                       | 82 2685 | 4682   | 4685 | 0000 0-00       | 0000 0-00                          | uuuu u-uu                       |  |  |

| TXB1D7 26                                                                                                                                                                                                                                                                        | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB1D6 26                                                                                                                                                                                                                                                                        | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB1D5 26                                                                                                                                                                                                                                                                        | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB1D4 26                                                                                                                                                                                                                                                                        | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB1D3 26                                                                                                                                                                                                                                                                        | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB1D2 26                                                                                                                                                                                                                                                                        | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB1D1 26                                                                                                                                                                                                                                                                        | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB1D0 26                                                                                                                                                                                                                                                                        | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB1DLC 26                                                                                                                                                                                                                                                                       | 82 2685 | 4682   | 4685 | -x xxxx         | -u uuuu                            | -u uuuu                         |  |  |

|                                                                                                                                                                                                                                                                                  | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB1EIDH 26                                                                                                                                                                                                                                                                      | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB1SIDL 26                                                                                                                                                                                                                                                                      | 82 2685 | 4682   | 4685 | XXX- X-XX       | uuu- u-uu                          | uuu- uu-u                       |  |  |

| TXB1SIDH 26                                                                                                                                                                                                                                                                      | 82 2685 | 4682   | 4685 | XXXX XXXX       | սսսս սսսս                          | սսսս սսսս                       |  |  |

| TXB1CON 26                                                                                                                                                                                                                                                                       |         |        |      |                 |                                    |                                 |  |  |

| TXB2D7 26                                                                                                                                                                                                                                                                        | 82 2685 | 4682   | 4685 | 0000 0-00       | 0000 0-00                          | uuuu u-uu                       |  |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

5: Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

6: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

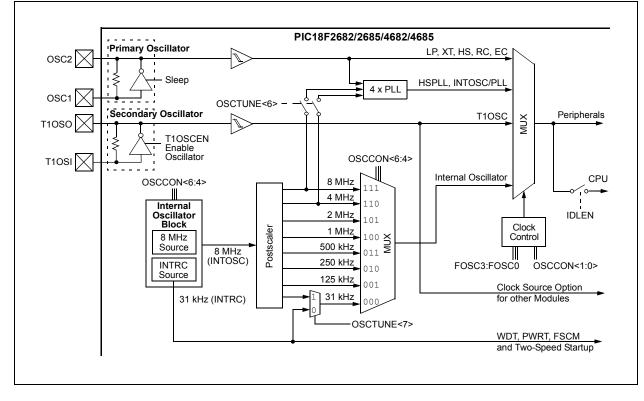

#### 5.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 Enhanced microcontroller devices:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 6.0 "Flash Program Memory"**. Data EEPROM is discussed separately in **Section 7.0 "Data EEPROM Memory"**.

#### 5.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The PIC18F2682 and PIC18F4682 each have 80 Kbytes of Flash memory and can store up to 40,960 single-word instructions. The PIC18F2685 and PIC18F4685 each have 96 Kbytes of Flash memory and can store up to 49,152 single-word instructions.

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory maps for PIC18F2682/4682 and PIC18F2685/4685 devices are shown in Figure 5-1.

FIGURE 5-1: PROGRAM MEMORY MAP AND STACK FOR PIC18F2682/2685/4682/4685 DEVICES

### TABLE 5-1:SPECIAL FUNCTION REGISTER MAP FOR<br/>PIC18F2682/2685/4682/4685 DEVICES (CONTINUED)

| Address | Name | Address | Name | Address | Name | Address | Name |

|---------|------|---------|------|---------|------|---------|------|

| EFFh    | _    | EDFh    | _    | EBFh    | _    | E9Fh    | _    |

| EFEh    | _    | EDEh    | _    | EBEh    | _    | E9Eh    | _    |

| EFDh    | —    | EDDh    | _    | EBDh    | _    | E9Dh    | _    |

| EFCh    | —    | EDCh    | _    | EBCh    | _    | E9Ch    | _    |

| EFBh    | —    | EDBh    | _    | EBBh    | _    | E9Bh    | _    |

| EFAh    | _    | EDAh    | _    | EBAh    | _    | E9Ah    | _    |

| EF9h    | —    | ED9h    | —    | EB9h    |      | E99h    | —    |

| EF8h    | —    | ED8h    | _    | EB8h    | _    | E98h    | _    |

| EF7h    | —    | ED7h    | _    | EB7h    | _    | E97h    | _    |

| EF6h    | —    | ED6h    | —    | EB6h    |      | E96h    | —    |

| EF5h    | _    | ED5h    | —    | EB5h    |      | E95h    | _    |

| EF4h    | —    | ED4h    | —    | EB4h    | -    | E94h    | —    |

| EF3h    | —    | ED3h    | —    | EB3h    |      | E93h    | —    |

| EF2h    | —    | ED2h    | —    | EB2h    |      | E92h    | —    |

| EF1h    | —    | ED1h    | —    | EB1h    | —    | E91h    | —    |

| EF0h    |      | ED0h    |      | EB0h    | —    | E90h    | —    |

| EEFh    | —    | ECFh    | —    | EAFh    |      | E8Fh    | —    |

| EEEh    | —    | ECEh    | —    | EAEh    | -    | E8Eh    | —    |

| EEDh    | —    | ECDh    | —    | EADh    |      | E8Dh    | —    |

| EECh    | —    | ECCh    | —    | EACh    |      | E8Ch    | —    |

| EEBh    | —    | ECBh    | —    | EABh    | —    | E8Bh    | —    |

| EEAh    | —    | ECAh    | —    | EAAh    |      | E8Ah    | —    |

| EE9h    | —    | EC9h    | —    | EA9h    |      | E89h    | —    |

| EE8h    |      | EC8h    |      | EA8h    | —    | E88h    | —    |

| EE7h    |      | EC7h    |      | EA7h    | —    | E87h    | —    |

| EE6h    | —    | EC6h    | —    | EA6h    |      | E86h    | —    |

| EE5h    |      | EC5h    |      | EA5h    | _    | E85h    | —    |

| EE4h    |      | EC4h    |      | EA4h    | —    | E84h    | —    |

| EE3h    | —    | EC3h    | —    | EA3h    | _    | E83h    | —    |

| EE2h    | —    | EC2h    | _    | EA2h    | _    | E82h    | _    |

| EE1h    | —    | EC1h    | _    | EA1h    | _    | E81h    | —    |

| EE0h    | _    | EC0h    | _    | EA0h    | _    | E80h    | _    |

Note 1: Registers available only on PIC18F4X8X devices; otherwise, the registers read as '0'.

2: When any TX\_ENn bit in RX\_TX\_SELn is set, then the corresponding bit in this register has transmit properties.

**3:** This is not a physical register.

|           |         |         |         |         |         |         | 82/4685) (0 |         | Value on  | Details  |

|-----------|---------|---------|---------|---------|---------|---------|-------------|---------|-----------|----------|

| File Name | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1       | Bit 0   | POR, BOR  | on page: |

| TXB1CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   | _       | TXPRI1      | TXPRI0  | 0000 0-00 | 56, 284  |

| TXB2D7    | TXB2D77 | TXB2D76 | TXB2D75 | TXB2D74 | TXB2D73 | TXB2D72 | TXB2D71     | TXB2D70 | XXXX XXXX | 56, 286  |

| TXB2D6    | TXB2D67 | TXB2D66 | TXB2D65 | TXB2D64 | TXB2D63 | TXB2D62 | TXB2D61     | TXB2D60 | XXXX XXXX | 57, 286  |

| TXB2D5    | TXB2D57 | TXB2D56 | TXB2D55 | TXB2D54 | TXB2D53 | TXB2D52 | TXB2D51     | TXB2D50 | XXXX XXXX | 57, 286  |

| TXB2D4    | TXB2D47 | TXB2D46 | TXB2D45 | TXB2D44 | TXB2D43 | TXB2D42 | TXB2D41     | TXB2D40 | XXXX XXXX | 57, 286  |

| TXB2D3    | TXB2D37 | TXB2D36 | TXB2D35 | TXB2D34 | TXB2D33 | TXB2D32 | TXB2D31     | TXB2D30 | XXXX XXXX | 57, 286  |

| TXB2D2    | TXB2D27 | TXB2D26 | TXB2D25 | TXB2D24 | TXB2D23 | TXB2D22 | TXB2D21     | TXB2D20 | XXXX XXXX | 57, 286  |

| TXB2D1    | TXB2D17 | TXB2D16 | TXB2D15 | TXB2D14 | TXB2D13 | TXB2D12 | TXB2D11     | TXB2D10 | XXXX XXXX | 57, 286  |

| TXB2D0    | TXB2D07 | TXB2D06 | TXB2D05 | TXB2D04 | TXB2D03 | TXB2D02 | TXB2D01     | TXB2D00 | XXXX XXXX | 57, 286  |

| TXB2DLC   | _       | TXRTR   | _       |         | DLC3    | DLC2    | DLC1        | DLC0    | -x xxxx   | 57, 287  |

| TXB2EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1        | EID0    | XXXX XXXX | 57, 286  |

| TXB2EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9        | EID8    | XXXX XXXX | 57, 285  |

| TXB2SIDL  | SID2    | SID1    | SID0    | -       | EXIDE   | _       | EID17       | EID16   | xxxx x-xx | 57, 285  |

| TXB2SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4        | SID3    | xxx- x-xx | 57, 285  |

| TXB2CON   | TXBIF   | TXABT   | TXLARB  | TXERR   | TXREQ   | _       | TXPRI1      | TXPRI0  | 0000 0-00 | 57, 284  |

| RXM1EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1        | EID0    | XXXX XXXX | 57, 307  |

| RXM1EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9        | EID8    | XXXX XXXX | 57, 307  |

| RXM1SIDL  | SID2    | SID1    | SID0    | -       | EXIDEN  | _       | EID17       | EID16   | xxx- x-xx | 57, 307  |

| RXM1SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4        | SID3    | XXXX XXXX | 57, 306  |

| RXM0EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1        | EID0    | XXXX XXXX | 57, 307  |

| RXM0EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9        | EID8    | XXXX XXXX | 57, 307  |

| RXM0SIDL  | SID2    | SID1    | SID0    |         | EXIDEN  | _       | EID17       | EID16   | xxx- x-xx | 57, 307  |

| RXM0SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4        | SID3    | XXXX XXXX | 57, 306  |

| RXF5EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1        | EID0    | XXXX XXXX | 57, 306  |

| RXF5EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9        | EID8    | XXXX XXXX | 57, 306  |

| RXF5SIDL  | SID2    | SID1    | SID0    |         | EXIDEN  | _       | EID17       | EID16   | xxx- x-xx | 57, 305  |

| RXF5SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4        | SID3    | XXXX XXXX | 57, 306  |

| RXF4EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1        | EID0    | XXXX XXXX | 57, 306  |

| RXF4EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9        | EID8    | XXXX XXXX | 57, 306  |

| RXF4SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17       | EID16   | xxx- x-xx | 57, 305  |

| RXF4SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4        | SID3    | XXXX XXXX | 57, 306  |

| RXF3EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1        | EID0    | XXXX XXXX | 57, 306  |

| RXF3EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9        | EID8    | XXXX XXXX | 57, 306  |

| RXF3SIDL  | SID2    | SID1    | SID0    |         | EXIDEN  | _       | EID17       | EID16   | xxx- x-xx | 58, 305  |

| RXF3SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4        | SID3    | XXXX XXXX | 58, 306  |

| RXF2EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1        | EID0    | XXXX XXXX | 58, 306  |

| RXF2EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9        | EID8    | XXXX XXXX | 58, 306  |

| RXF2SIDL  | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17       | EID16   | xxx- x-xx | 58, 305  |

| RXF2SIDH  | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4        | SID3    | XXXX XXXX | 58, 306  |

| RXF1EIDL  | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1        | EID0    | XXXX XXXX | 58, 306  |

| RXF1EIDH  | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9        | EID8    | XXXX XXXX | 58, 306  |

| TABLE 5-2: | REGISTER FILE SUMMARY ( | PIC18F2682/2685/4682/4685 | (CONTINUED) |

|------------|-------------------------|---------------------------|-------------|

|            |                         |                           | (           |

$\label{eq:logarder} \mbox{Legend: } x \mbox{=} unknown, u \mbox{$

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2682/2685 devices and are read as '0'. Reset values are shown for PIC18F4682/4685 devices; individual unimplemented bits should be interpreted as '---'.

4: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2.

9: These registers and/or bits are available on PIC18F4682/4685 devices only.

|                    | ORTB I/O            | i   |                                                                |        | <b>D</b> 1.4                                                                                                     |

|--------------------|---------------------|-----|----------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------|

| Pin Name           | Function            | I/O | TRIS                                                           | Buffer | Description                                                                                                      |

| RB0/INT0/FLT0/AN10 | RB0                 | OUT | 0                                                              | DIG    | LATB<0> data output.                                                                                             |

|                    |                     | IN  | 1                                                              | TTL    | PORTB<0> data input. Weak pull-up available only in this mode.                                                   |

|                    | INT0                | IN  | 1                                                              | ST     | External interrupt 0 input.                                                                                      |

|                    | FLT0 <sup>(1)</sup> | IN  | 1                                                              | ST     | Enhanced PWM Fault input.                                                                                        |

|                    | AN10                | IN  | 1                                                              | ANA    | A/D input channel 10. Enabled on POR, this analog input overrides the digital input (read as clear – low level). |

| RB1/INT1/AN8       | RB1                 | OUT | 0                                                              | DIG    | LATB<1> data output.                                                                                             |

|                    |                     | IN  | PORTB<1> data input. Weak pull-up available only in this mode. |        |                                                                                                                  |

|                    | INT1                | IN  | 1                                                              | ST     | External interrupt 1 input.                                                                                      |

|                    | AN8                 | IN  | 1                                                              | ANA    | A/D input channel 8. Enabled on POR, this analog input overrides the digital input (read as clear – low level).  |

| RB2/INT2/CANTX     | RB2                 | OUT | х                                                              | DIG    | LATB<2> data output.                                                                                             |

|                    |                     | IN  | 1                                                              | TTL    | PORTB<2> data input. Weak pull-up available only in this mode.                                                   |

|                    | INT2                | IN  | 1                                                              | ST     | External interrupt 2 input.                                                                                      |

|                    | CANTX               | OUT | 1                                                              | DIG    | CAN transmit signal output. The CAN interface overrides the TRIS<2> control when enabled.                        |

| RB3/CANRX          | RB3                 | OUT | 0                                                              | DIG    | LATB<3> data output.                                                                                             |

|                    |                     | IN  | 1                                                              | TTL    | PORTB<3> data input. Weak pull-up available only in this mode.                                                   |

|                    | CANRX               | IN  | 1                                                              | ST     | CAN receive signal input. Pin must be configured as a digital input b setting TRISB<3>.                          |

| RB4/KBI0/AN9       | RB4                 | OUT | 0                                                              | DIG    | LATB<4> data output.                                                                                             |

|                    |                     | IN  | 1                                                              | TTL    | PORTB<4> data input. Weak pull-up available only in this mode.                                                   |

|                    | KBI0                | IN  | 1                                                              | TTL    | Interrupt-on-pin change.                                                                                         |

|                    | AN9                 | IN  | 1                                                              | ANA    | A/D input channel 9. Enabled on POR, this analog input overrides the digital input (read as clear – low level).  |

| RB5/KBI1/PGM       | RB5                 | OUT | 0                                                              | DIG    | LATB<5> data output.                                                                                             |

|                    |                     | IN  | 1                                                              | TTL    | PORTB<5> data input. Weak pull-up available only in this mode.                                                   |

|                    | KBI1                | IN  | 1                                                              | TTL    | Interrupt-on-pin change.                                                                                         |

|                    | PGM                 | IN  | х                                                              | ST     | Low-Voltage Programming mode entry (ICSP™). Enabling this function overrides digital output.                     |

| RB6/KBI2/PGC       | RB6                 | OUT | 0                                                              | DIG    | LATB<6> data output.                                                                                             |

|                    |                     | IN  | 1                                                              | TTL    | PORTB<6> data input. Weak pull-up available only in this mode.                                                   |

|                    | KBI2                | IN  | 1                                                              | TTL    | Interrupt-on-pin change.                                                                                         |

|                    | PGC                 | IN  | Х                                                              | ST     | Low-Voltage Programming mode entry (ICSP) clock input.                                                           |

| RB7/KBI3/PGD       | RB7                 | OUT | 0                                                              | DIG    | LATB<7> data output.                                                                                             |

|                    |                     | IN  | 1                                                              | TTL    | PORTB<7> data input. Weak pull-up available only in this mode.                                                   |

|                    | KBI3                | IN  | 1                                                              | TTL    | Interrupt-on-pin change.                                                                                         |

|                    | PGD                 | OUT | х                                                              | DIG    | Low-Voltage Programming mode entry (ICSP) clock output.                                                          |

|                    |                     | IN  | х                                                              | ST     | Low-Voltage Programming mode entry (ICSP) clock input.                                                           |

|--|

Legend: OUT = Output; IN = Input; ANA = Analog Signal; DIG = Digital Output; ST = Schmitt Buffer Input; TTL – TTL Buffer Input Note 1: This bit is unimplemented on PIC18F2682/2685 devices.

#### 11.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS2:T0PS0 bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

#### 11.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

#### 11.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name                           | Bit 7                           | Bit 6                 | Bit 5    | Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |          |        |        |      |    |  |  |

|--------------------------------|---------------------------------|-----------------------|----------|-------------------------------------|----------|--------|--------|------|----|--|--|

| TMR0L Timer0 Register Low Byte |                                 |                       |          |                                     |          |        |        | 52   |    |  |  |

| TMR0H                          | TMR0H Timer0 Register High Byte |                       |          |                                     |          |        |        |      | 52 |  |  |

| INTCON                         | GIE/GIEH                        | PEIE/GIEL             | TMR0IE   | INT0IE                              | RBIE     | TMR0IF | INT0IF | RBIF | 51 |  |  |

| TOCON                          | TMR0ON                          | T08BIT                | TOCS     | 52                                  |          |        |        |      |    |  |  |

| TRISA                          | TRISA7 <sup>(1)</sup>           | TRISA6 <sup>(1)</sup> | PORTA Da | ta Direction                        | Register |        |        |      | 54 |  |  |

TABLE 11-1: REGISTERS ASSOCIATED WITH TIMER0

Legend: x = unknown, u = unchanged, — = unimplemented locations, read as '0'. Shaded cells are not used by Timer0.

**Note 1:** RA7:RA6 and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

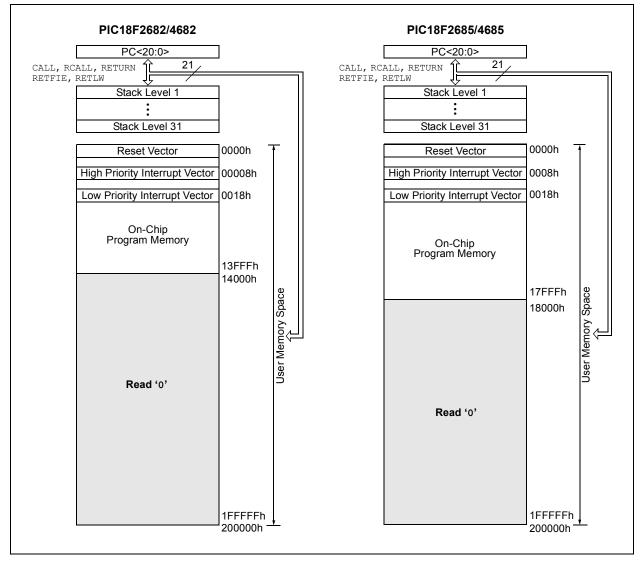

#### 15.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with a PORTB or PORTC data latch, the appropriate TRIS bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force     |

|-------|----------------------------------------------|

|       | the RC2 output latch to the default low      |

|       | level. This is not the PORTC I/O data latch. |

Figure 15-3 shows a simplified block diagram of the CCP1 module in PWM mode.

For a step-by-step procedure on how to set up the CCP1 module for PWM operation, see Section 15.4.4 "Setup for PWM Operation".

#### FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

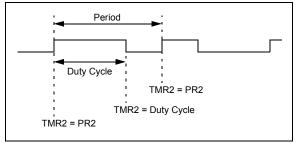

A PWM output (Figure 15-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/ period).

#### FIGURE 15-4: PWM OUTPUT

#### 15.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 (PR4) register. The PWM period can be calculated using the following formula.

#### EQUATION 15-1:

$$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 Prescale Value)$$

PWM frequency is defined as 1/[PWM period].

When TMR1 (TMR3) is equal to PR2 (PR4), the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

```

Note: The Timer2 postscaler (see Section 13.0

"Timer2 Module") is not used in the

determination of the PWM frequency. The

postscaler could be used to have a servo

update rate at a different frequency than

the PWM output.

```

#### 15.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time.

#### EQUATION 15-2:

PWM Duty Cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 Prescale Value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

| R/W-0        | U-0                                                                              | R/W-0                                                           | R/W-0          | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------|--------------------------|------------------|-----------------|-------|--|--|--|--|--|

| ADFM         |                                                                                  | ACQT2                                                           | ACQT1          | ACQT0                    | ADCS2            | ADCS1           | ADCS0 |  |  |  |  |  |

| bit 7        |                                                                                  |                                                                 |                |                          |                  |                 | bit ( |  |  |  |  |  |

|              |                                                                                  |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

| Legend:      |                                                                                  |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                                                           | W = Writable                                                    | bit            | U = Unimpler             | nented bit, read | d as '0'        |       |  |  |  |  |  |

| -n = Value a | t POR                                                                            | '1' = Bit is set                                                |                | '0' = Bit is cle         | ared             | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 7        | ADFM: A/D F                                                                      | Result Format S                                                 | Select bit     |                          |                  |                 |       |  |  |  |  |  |

|              | 1 = Right just<br>0 = Left justifi                                               |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

| bit 6        | Unimplemen                                                                       | Unimplemented: Read as '0'                                      |                |                          |                  |                 |       |  |  |  |  |  |

| bit 5-3      | ACQT2:ACQ                                                                        | T0: A/D Acquis                                                  | sition Time Se | elect bits               |                  |                 |       |  |  |  |  |  |

|              | 111 <b>= 20 T</b> AD                                                             |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

|              | 110 = 16 TAD                                                                     |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

|              | 101 = 12 TAD                                                                     |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

|              | 100 = 8 TAD<br>011 = 6 TAD                                                       |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

|              | 011 = 6 TAD<br>010 = 4 TAD                                                       |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

|              | 001 = 2 TAD                                                                      |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

|              | $000 = 0 \text{ TAD}^{(1)}$                                                      |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

| bit 2-0      | ADCS2:ADC                                                                        | S0: A/D Conve                                                   | ersion Clock S | elect bits               |                  |                 |       |  |  |  |  |  |

|              | 111 = FRC (C                                                                     | lock derived fro                                                | om A/D RC os   | cillator) <sup>(1)</sup> |                  |                 |       |  |  |  |  |  |

|              | 111 = FRC (clock derived from A/D RC oscillator) <sup>(1)</sup><br>110 = Fosc/64 |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

|              | 101 <b>= Fosc/16</b>                                                             |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

|              | 100 = Fosc/4                                                                     |                                                                 |                | ···· (1)                 |                  |                 |       |  |  |  |  |  |

|              | •                                                                                | 011 = FRC (clock derived from A/D RC oscillator) <sup>(1)</sup> |                |                          |                  |                 |       |  |  |  |  |  |

|              | 010 = Fosc/3<br>001 = Fosc/8                                                     |                                                                 |                |                          |                  |                 |       |  |  |  |  |  |

|              |                                                                                  | )                                                               |                |                          |                  |                 |       |  |  |  |  |  |

#### REGISTER 19-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D FRC clock source is selected, a delay of one TcY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

### $\label{eq:register23-24: BnSIDH: TX/RX BUFFER n STANDARD IDENTIFIER REGISTERS, \\ HIGH BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| SID10 | SID9 | SID8 | SID7 | SID6 | SID5 | SID4 | SID3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 SID10:SID3: Standard Identifier bits (if EXIDE (BnSIDL<3>) = 0) Extended Identifier bits EID28:EID21 (if EXIDE = 1).

Note 1: These registers are available in Mode 1 and 2 only.

####

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 **SID10:SID3:** Standard Identifier bits (if EXIDE (BnSIDL<3>) = 0) Extended Identifier bits EID28:EID21 (if EXIDE = 1).

Note 1: These registers are available in Mode 1 and 2 only.

| BCF                                  | Bit Clear f                                                                                                                                                                                                                                                                                                                                                                                                                 | BN                                                                                           | Branch if Negative                                                                                                                                                                                                                                                                                      |  |  |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                              | BCF                                                                                                                                                                                                                                                                                                                                                                                                                         | Syntax:                                                                                      | BN n                                                                                                                                                                                                                                                                                                    |  |  |  |

| Operands:                            | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                           | Operands:                                                                                    | $-128 \le n \le 127$                                                                                                                                                                                                                                                                                    |  |  |  |

|                                      | $\begin{array}{l} 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                               | Operation:                                                                                   | if Negative bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                                |  |  |  |

| Operation:                           | $0 \rightarrow f \le b >$                                                                                                                                                                                                                                                                                                                                                                                                   | Status Affected:                                                                             | None                                                                                                                                                                                                                                                                                                    |  |  |  |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                                                                                                        | Encoding:                                                                                    | 1110 0110 nnnn nnnn                                                                                                                                                                                                                                                                                     |  |  |  |

| Encoding:<br>Description:            | 1001bbbaffffffBit 'b' in register 'f' is cleared.If 'a' is '0', the Access Bank is selected.If 'a' is '1', the BSR is used to select theGPR bank (default).If 'a' is '0' and the extended instructionset is enabled, this instruction operatesin Indexed Literal Offset Addressingmode whenever $f \le 95$ (5Fh). SeeSection 25.2.3 "Byte-Oriented andBit-Oriented Instructions in IndexedLiteral Offset Mode" for details. | Description:<br>Words:<br>Cycles:                                                            | If the Negative bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction.<br>1<br>1(2) |  |  |  |

| Words:                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                           | Q Cycle Activity:<br>If Jump:                                                                |                                                                                                                                                                                                                                                                                                         |  |  |  |

| Cycles:                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                           | Q1                                                                                           | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                |  |  |  |

| Q Cycle Activity:                    |                                                                                                                                                                                                                                                                                                                                                                                                                             | Decode                                                                                       | Read literal         Process         Write to PC           'n'         Data         Vite to PC                                                                                                                                                                                                          |  |  |  |

| Q1<br>Decode                         | Q2 Q3 Q4<br>Read Process Write                                                                                                                                                                                                                                                                                                                                                                                              | No<br>operation                                                                              | NoNoNooperationoperationoperation                                                                                                                                                                                                                                                                       |  |  |  |

|                                      | register 'f' Data register 'f'                                                                                                                                                                                                                                                                                                                                                                                              | If No Jump:                                                                                  |                                                                                                                                                                                                                                                                                                         |  |  |  |

| Evennley                             |                                                                                                                                                                                                                                                                                                                                                                                                                             | Q1                                                                                           | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                |  |  |  |

| Example:<br>Before Instruc<br>FLAG_R | BCF FLAG_REG, 7, 0<br>tion<br>EG = C7h                                                                                                                                                                                                                                                                                                                                                                                      | Decode                                                                                       | Read literalProcessNo'n'Dataoperation                                                                                                                                                                                                                                                                   |  |  |  |

| After Instruction                    |                                                                                                                                                                                                                                                                                                                                                                                                                             | Example:<br>Before Instruct<br>PC<br>After Instruction<br>If Negati<br>PC<br>If Negati<br>PC | = address (HERE)<br>on<br>ive = 1;<br>= address (Jump)<br>ive = 0;                                                                                                                                                                                                                                      |  |  |  |

| BNC         | C                                                                            | Branch if                                  | Not Carry                                                                                   |                                         | BNN          | l                                                                           | Branch if                                  | Not Negat                                                | ive                     |  |  |  |

|-------------|------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------|--------------|-----------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------|-------------------------|--|--|--|

| Synt        | ax:                                                                          | BNC n                                      |                                                                                             |                                         | Synta        | Syntax: BNN                                                                 |                                            | NN n                                                     |                         |  |  |  |

| Ope         | rands:                                                                       | -128 ≤ n ≤ 1                               | 27                                                                                          |                                         | Oper         | ands:                                                                       | -128 ≤ n ≤ ′                               | 127                                                      |                         |  |  |  |

| Ope         | ration:                                                                      | if Carry bit i<br>(PC) + 2 + 2             |                                                                                             |                                         | Oper         | ation:                                                                      | 0                                          | if Negative bit is '0'<br>(PC) + 2 + 2n $\rightarrow$ PC |                         |  |  |  |

| Statu       | us Affected:                                                                 | None                                       |                                                                                             |                                         | Statu        | s Affected:                                                                 | None                                       |                                                          |                         |  |  |  |

| Enco        | oding:                                                                       | 1110                                       | 0011 nn                                                                                     | nn nnnn                                 | Enco         | ding:                                                                       | 1110                                       | 0111 n:                                                  | nnn nnnn                |  |  |  |

| Desc        | cription:                                                                    | If the Carry will branch.                  | bit is '0', then                                                                            | the program                             | Desc         | ription:                                                                    | If the Nega<br>program wi                  | tive bit is '0',<br>Il branch.                           | then the                |  |  |  |

|             |                                                                              | added to th<br>have incren<br>instruction, | nplement num<br>e PC. Since the<br>nented to fetch<br>the new addro<br>n. This instruction. | ne PC will<br>h the next<br>ess will be |              |                                                                             | added to th<br>incremente<br>instruction,  | d to fetch the<br>the new add<br>n. This instru          | he PC will have<br>next |  |  |  |