Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 80KB (40K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4682-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

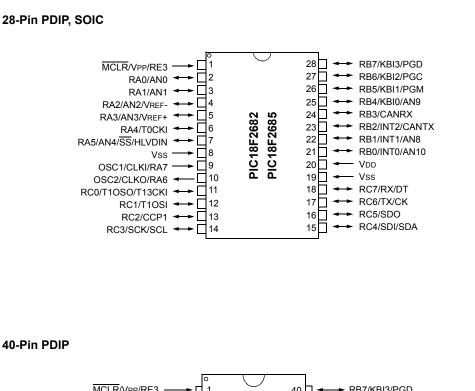

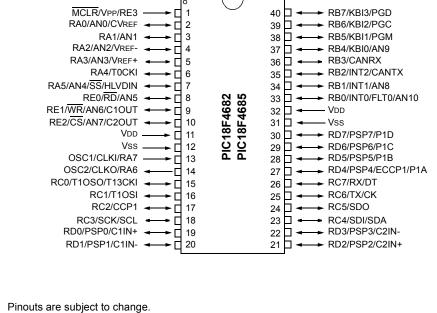

## **Pin Diagrams**

Note:

| Pin Name                                           | Pin<br>Number<br>PDIP,<br>SOIC | Pin<br>Type | Buffer<br>Type | Description                                                            |

|----------------------------------------------------|--------------------------------|-------------|----------------|------------------------------------------------------------------------|

|                                                    |                                |             |                | PORTA is a bidirectional I/O port.                                     |

| RA0/AN0                                            | 2                              |             |                |                                                                        |

| RA0                                                |                                | I/O         | TTL            | Digital I/O.                                                           |

| AN0                                                |                                | I           | Analog         | Analog input 0.                                                        |

| RA1/AN1                                            | 3                              |             |                |                                                                        |

| RA1                                                |                                | I/O         | TTL            | Digital I/O.                                                           |

| AN1                                                |                                | I           | Analog         | Analog input 1.                                                        |

| RA2/AN2/VREF-                                      | 4                              |             |                |                                                                        |

| RA2                                                |                                | I/O         | TTL            | Digital I/O.                                                           |

| AN2                                                |                                | I           | Analog         | Analog input 2.                                                        |

| VREF-                                              |                                | I           | Analog         | A/D reference voltage (low) input.                                     |

| RA3/AN3/VREF+                                      | 5                              |             |                |                                                                        |

| RA3                                                |                                | I/O         | TTL            | Digital I/O.                                                           |

| AN3                                                |                                | I           | Analog         | Analog input 3.                                                        |

| VREF+                                              |                                | I           | Analog         | A/D reference voltage (high) input.                                    |

| RA4/T0CKI                                          | 6                              |             |                |                                                                        |

| RA4                                                |                                | I/O         | TTL            | Digital I/O.                                                           |

| TOCKI                                              |                                | I           | ST             | Timer0 external clock input.                                           |

| RA5/AN4/SS/HLVDIN                                  | 7                              |             |                |                                                                        |

| RA5                                                |                                | I/O         | TTL            | Digital I/O.                                                           |

| AN4                                                |                                | I           | Analog         | Analog input 4.                                                        |

| SS                                                 |                                | I           | TTL            | SPI slave select input.                                                |

| HLVDIN                                             |                                | I           | Analog         | High/Low-Voltage Detect input.                                         |

| RA6                                                |                                |             |                | See the OSC2/CLKO/RA6 pin.                                             |

| RA7                                                |                                |             |                | See the OSC1/CLKI/RA7 pin.                                             |

| Legend: TTL = TTL co<br>ST = Schmitt<br>O = Output | t Trigger inp                  |             | CMOS le        | CMOS = CMOS compatible input or output<br>evels I = Input<br>P = Power |

| <b>TABLE 1-2</b> : | PIC18F2682/2685 PINOUT I/O DESCRIPTIONS (CONTINUE | ED) |

|--------------------|---------------------------------------------------|-----|

|                    |                                                   |     |

| R/W-0      | ) R/W-1                     | R/W-0                    | R/W-0           | R <sup>(1)</sup>  | R-0             | R/W-0           | R/W-0 |

|------------|-----------------------------|--------------------------|-----------------|-------------------|-----------------|-----------------|-------|

| IDLEN      | IRCF2                       | IRCF1                    | IRCF0           | OSTS              | IOFS            | SCS1            | SCS0  |

| bit 7      |                             |                          |                 |                   |                 |                 | bit C |

|            |                             |                          |                 |                   |                 |                 |       |

| Legend:    |                             |                          |                 |                   |                 |                 |       |

| R = Reada  |                             | W = Writable             |                 | -                 | nented bit, rea |                 |       |

| -n = Value | e at POR                    | '1' = Bit is set         |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

| bit 7      | IDLEN: Idle                 | Enable bit               |                 |                   |                 |                 |       |

|            |                             | enters Idle mod          | e on SLEEP in   | struction         |                 |                 |       |

|            |                             | enters Sleep mo          |                 |                   |                 |                 |       |

| bit 6-4    | IRCF2:IRCF                  | <b>-0:</b> Internal Osci | llator Frequen  | cy Select bits    |                 |                 |       |

|            |                             | z (INTOSC drive          | es clock direct | ly)               |                 |                 |       |

|            | 110 <b>= 4 MH</b>           | —                        |                 |                   |                 |                 |       |

|            | 101 = 2 MH<br>100 = 1 MH    |                          |                 |                   |                 |                 |       |

|            | 011 <b>= 500 k</b>          |                          |                 |                   |                 |                 |       |

|            | 010 <b>= 250 k</b>          | Hz                       |                 |                   |                 |                 |       |

|            | 001 = <b>125</b> k          |                          | 17000/050       |                   | ·(2)            |                 |       |

|            |                             | Iz (from either IN       |                 | -                 | y)(=/           |                 |       |

| bit 3      |                             | Ilator Start-up Ti       |                 |                   |                 |                 |       |

|            |                             | or Start-up Time         |                 |                   |                 |                 |       |

| bit 2      | IOFS: INTO                  | SC Frequency S           | Stable bit      |                   |                 |                 |       |

|            |                             | C frequency is st        |                 | requency is pro   | vided by one o  | of the RC modes | 6     |

|            |                             | C frequency is no        |                 |                   |                 |                 |       |

| bit 1-0    |                             | : System Clock           |                 |                   |                 |                 |       |

|            | 1x = Interna<br>01 = Timer1 | al oscillator block      |                 |                   |                 |                 |       |

|            | 00 = Primar                 |                          |                 |                   |                 |                 |       |

| Note 1:    | Depends on state            | e of the IESO Co         | onfiguration bi | t.                |                 |                 |       |

|            |                             |                          |                 | •-                |                 |                 |       |

| 2:         | Source selected             | by the INTSRC            | bit (OSCTUNE    | E<7>), see text.  |                 |                 |       |

# REGISTER 2-2: OSCCON: OSCILLATOR CONTROL REGISTER

# 9.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxIF, is set. This interrupt can be disabled by clearing the corresponding enable bit INTxIE. Flag bit, INTxIF, must be cleared in software in the Interrupt.

All external interrupts (INT0, INT1 and INT2) can wake-up the processor from the power-managed modes if bit INTxIE was set prior to going into the power-managed modes. If the Global Interrupt Enable bit, GIE, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high priority interrupt source.

# 9.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 11.0 "Timer0 Module" for further details on the Timer0 module.

# 9.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

# 9.9 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (See Section 5.3 "Data Memory Organization"), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 9-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| W_TEMP              | ; W_TEMP is in virtual bank                                                   |

|---------------------|-------------------------------------------------------------------------------|

| STATUS, STATUS_TEMP | ; STATUS_TEMP located anywhere                                                |

| BSR, BSR TEMP       | ; BSR TMEP located anywhere                                                   |

|                     |                                                                               |

| ISR CODE            |                                                                               |

|                     |                                                                               |

| BSR_TEMP, BSR       | ; Restore BSR                                                                 |

| W_TEMP, W           | ; Restore WREG                                                                |

| STATUS TEMP, STATUS | ; Restore STATUS                                                              |

|                     | STATUS, STATUS_TEMP<br>BSR, BSR_TEMP<br>SR CODE<br>BSR_TEMP, BSR<br>W_TEMP, W |

EXAMPLE 9-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

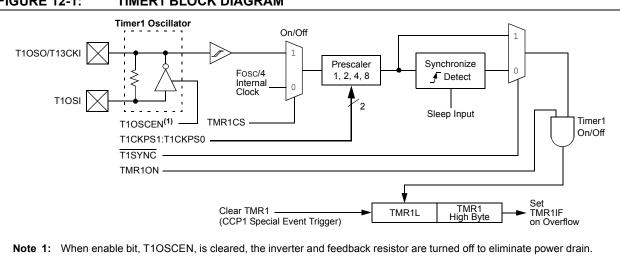

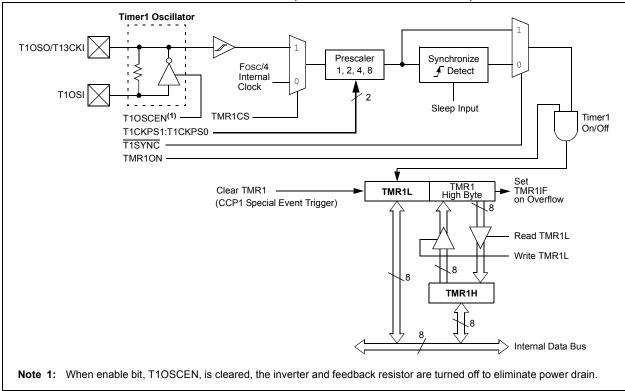

#### 12.1 **Timer1** Operation

Timer1 can operate in one of these modes:

- Timer

- Synchronous Counter

- Asynchronous Counter

The operating mode is determined by the clock select bit, TMR3CS (T3CON<1>). When TMR3CS is cleared (= 0), Timer3 increments on every internal instruction cycle (Fosc/4). When the bit is set, Timer3 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

When Timer1 is enabled, the RC1/T1OSI and RC0/ T1OSO/T13CKI pins become inputs. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

#### **FIGURE 12-2:** TIMER1 BLOCK DIAGRAM (16-BIT READ/WRITE MODE)

#### **TIMER1 BLOCK DIAGRAM FIGURE 12-1:**

# 15.2 Capture Mode

In Capture mode, the CCPR1H:CCPR1L (or ECCPR1H:ECCPR1L) register pair captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on the CCP1/ECCP1 pin (RC2 for 28/40/44-pin devices and RD4 for 40/44-pin devices). An event is defined as one of the following:

- · every falling edge

- every rising edge

- · every 4th rising edge

- every 16th rising edge

The event is selected by the mode select bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set; it must be cleared in software. If another capture occurs before the value in the CCPR1 register pair is read, the old captured value is overwritten by the new captured value.

#### 15.2.1 CCP1 PIN CONFIGURATION

In Capture mode, the appropriate CCP1/ECCP1 pin should be configured as an input by setting the corresponding TRIS direction bit.

| Note: | If RC2/CCP1 or RD4/PSP4/ECCP1/P1A          |

|-------|--------------------------------------------|

|       | is configured as an output, a write to the |

|       | port can cause a capture condition.        |

#### 15.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each CCP1 module is selected in the T3CON register (see Section 15.1.1 "CCP1 Modules and Timer Resources").

#### 15.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP1IE or ECCP1IE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCP1IF or ECCP1IF, should also be cleared following any such change in operating mode.

# 15.2.4 CCP1 PRESCALER

There are four prescaler settings in Capture mode; they are specified as part of the operating mode selected by the mode select bits (CCP1M3:CCP1M0). Whenever the CCP1 module is turned off or the CCP1 module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 15-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

# 15.2.5 CAN MESSAGE TIME-STAMP

The CAN capture event occurs when a message is received in any of the receive buffers. When configured, the CAN module provides the trigger to the CCP1 module to cause a capture event. This feature is provided to "time-stamp" the received CAN messages.

This feature is enabled by setting the CANCAP bit of the CAN I/O Control register (CIOCON<4>). The message receive signal from the CAN module then takes the place of the events on the RC2/CCP1 pin.

If this feature is selected, then four different capture options for CCP1M<3:0> are available:

- 0100 every time a CAN message is received

- 0101 every time a CAN message is received

- 0110 every 4th time a CAN message is received

- 0111 Capture mode, every 16th time a CAN message is received

#### EXAMPLE 15-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ; | Turn CCP1 module off |

|-------|-------------|---|----------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the   |

|       |             | ; | new prescaler mode   |

|       |             | ; | value and CCP1 ON    |

| MOVWF | CCP1CON     | ; | Load CCP1CON with    |

|       |             | ; | this value           |

## 16.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP1 module for PWM operation:

- 1. Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- Configure the ECCP1 module for the desired PWM mode and configuration by loading the ECCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the EPWM1M1:EPWM1M0 bits.

- Select the polarities of the PWM output signals with the ECCP1M3:ECCP1M0 bits.

- 4. Set the PWM duty cycle by loading the ECCPR1L register and ECCP1CON<5:4> bits.

- 5. For Half-Bridge Output mode, set the deadband delay by loading ECCP1DEL<6:0> with the appropriate value.

- 6. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCPAS2:ECCPAS0 bits.

- Select the shutdown states of the PWM output pins using PSSAC1:PSSAC0 and PSSBD1:PSSBD0 bits.

- Set the ECCPASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 7. If auto-restart operation is required, set the PRSEN bit (ECCP1DEL<7>).

- 8. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 9. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRx overflows (TMRxIF bit is set).

- Enable the ECCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCPASE bit (ECCP1AS<7>).

### 16.4.10 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the ECCP1 registers to their Reset states.

This forces the Enhanced CCP1 module to reset to a state compatible with the standard CCP1 module.

NOTES:

| R/W-0        | R/W-0              | U-0                              | U-0            | U-0              | R/W-0                  | R/W-0                  | R/W-0                  |

|--------------|--------------------|----------------------------------|----------------|------------------|------------------------|------------------------|------------------------|

| WAKDIS       | WAKFIL             | —                                |                | —                | SEG2PH2 <sup>(1)</sup> | SEG2PH1 <sup>(1)</sup> | SEG2PH0 <sup>(1)</sup> |

| bit 7        |                    |                                  |                |                  |                        |                        | bit 0                  |

| Legend:      |                    |                                  |                |                  |                        |                        |                        |

| R = Readat   | ole bit            | W = Writable I                   | bit            | U = Unimple      | mented bit, rea        | d as '0'               |                        |

| -n = Value a | at POR             | '1' = Bit is set                 |                | '0' = Bit is cle | eared                  | x = Bit is unk         | nown                   |

|              |                    |                                  |                |                  |                        |                        |                        |

| bit 7        | WAKDIS: Wa         | ake-up Disable I                 | bit            |                  |                        |                        |                        |

|              |                    | CAN bus activity                 |                | ature            |                        |                        |                        |

|              | 0 = Enable C       | AN bus activity                  | wake-up fea    | iture            |                        |                        |                        |

| bit 6        | WAKFIL: Sel        | lects CAN bus L                  | ine Filter for | Wake-up bit      |                        |                        |                        |

|              |                    | l bus line filter fo             |                |                  |                        |                        |                        |

|              | 0 = CAN bus        | line filter is not               | used for wak   | ke-up            |                        |                        |                        |

| bit 5-3      | Unimplemen         | nted: Read as '                  | )'             |                  |                        |                        |                        |

| bit 2-0      | SEG2PH2:SI         | EG2PH0: Phase                    | e Segment 2    | Time Select bi   | its <sup>(1)</sup>     |                        |                        |

|              |                    | Segment 2 time                   |                |                  |                        |                        |                        |

|              |                    | Segment 2 time                   |                |                  |                        |                        |                        |

|              |                    | Segment 2 time                   |                |                  |                        |                        |                        |

|              |                    | Segment 2 time<br>Segment 2 time |                |                  |                        |                        |                        |

|              |                    | Segment 2 time                   |                |                  |                        |                        |                        |

|              |                    | Segment 2 time                   |                |                  |                        |                        |                        |

|              | 000 <b>= Phase</b> | Segment 2 time                   | e = 1 x Tq     |                  |                        |                        |                        |

|              |                    |                                  |                |                  |                        |                        |                        |

### REGISTER 23-54: BRGCON3: BAUD RATE CONTROL REGISTER 3

Note 1: Ignored if SEG2PHTS bit (BRGCON2<7>) is '0'.

| Mode C     | R/W-1                                                                            | R/W-1                                                                                     | R/W-1           | R/W-1           | R/W-1                          | R/W-1                          | R/W-1           | R/W-1             |

|------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------|-----------------|--------------------------------|--------------------------------|-----------------|-------------------|

| Mode 0     | IRXIP                                                                            | WAKIP                                                                                     | ERRIP           | TXB2IP          | TXB1IP <sup>(1)</sup>          | TXB0IP <sup>(1)</sup>          | RXB1IP          | RXB0IP            |

|            | D 44/ 4                                                                          | D 44/ 4                                                                                   | D 44/ 4         |                 |                                | D 44/ 4                        | <b>D</b> (14) 4 | D 44/ 4           |

| Mode 1,2   | R/W-1                                                                            | R/W-1<br>WAKIP                                                                            | R/W-1<br>ERRIP  | R/W-1<br>TXBnIP | R/W-1<br>TXB1IP <sup>(1)</sup> | R/W-1<br>TXB0IP <sup>(1)</sup> | R/W-1<br>RXBnIP | R/W-1<br>FIFOWMIP |

|            | bit 7                                                                            | WAKIP                                                                                     | ERRIP           | TXBUIP          | TXBIIP                         | I XBUIP(*)                     | RABNIP          | bit               |

|            |                                                                                  |                                                                                           |                 |                 |                                |                                |                 | Dit               |

| Legend:    |                                                                                  |                                                                                           |                 |                 |                                |                                |                 |                   |

| R = Reada  | ble bit                                                                          |                                                                                           | W = Writabl     | e bit           | U = Unimple                    | emented bit, r                 | ead as '0'      |                   |

| -n = Value | at POR                                                                           |                                                                                           | '1' = Bit is s  | et              | '0' = Bit is cl                | eared                          | x = Bit is un   | known             |

| bit 7      | IRXIP: CAN<br>1 = High prid<br>0 = Low prid                                      |                                                                                           | ived Messag     | e Interrupt P   | riority bit                    |                                |                 |                   |

| bit 6      | <b>WAKIP:</b> CA<br>1 = High pric<br>0 = Low pric                                |                                                                                           | / Wake-up Ini   | terrupt Priori  | ty bit                         |                                |                 |                   |

| bit 5      | ERRIP: CAN<br>1 = High pric<br>0 = Low pric                                      |                                                                                           | iterrupt Priori | ty bit          |                                |                                |                 |                   |

| bit 4      | <b>TXB2IP:</b> CA<br>1 = High prid<br>0 = Low prid<br><u>When CAN</u>            | ority<br><u>is in Mode 1 (</u><br>AN Transmit E<br>ority                                  | or <u>2:</u>    | . ,             |                                |                                |                 |                   |

| bit 3      | <b>TXB1IP:</b> CA<br>1 = High pric<br>0 = Low pric                               | •                                                                                         | Buffer 1 Interr | upt Priority t  | bit <sup>(1)</sup>             |                                |                 |                   |

| bit 2      | <b>TXB0IP:</b> CA<br>1 = High prid<br>0 = Low prid                               |                                                                                           | Buffer 0 Interr | upt Priority k  | <sub>Dit</sub> (1)             |                                |                 |                   |

| bit 1      | <b>RXB1IP:</b> CA<br>1 = High prid<br>0 = Low prid<br><u>When CAN</u>            | ority<br><u>is in Mode 1 (</u><br>AN Receive B<br>ority                                   | or <u>2:</u>    |                 |                                |                                |                 |                   |

| bit 0      | When CAN<br>RXB0IP: CA<br>1 = High prid<br>0 = Low prid<br>When CAN<br>Unimpleme | is in Mode 0:<br>AN Receive B<br>ority<br>is in Mode 1:<br>ented: Read a<br>is in Mode 2: | as '0'          |                 | it                             |                                |                 |                   |

#### REGISTER 23-58: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3

Note 1: In CAN Mode 1 and 2, these bits are forced to '0'.

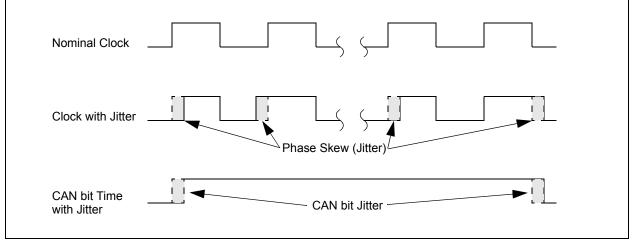

#### 23.9.1 EXTERNAL CLOCK, INTERNAL CLOCK AND MEASURABLE JITTER IN HSPLL-BASED OSCILLATORS

The microcontroller clock frequency generated from a PLL circuit is subject to a jitter, also defined as Phase Jitter or Phase Skew. For its PIC18 Enhanced microcontrollers, Microchip specifies phase jitter ( $P_{\text{jitter}}$ ) as being 2% (Gaussian distribution, within 3 standard deviations, see parameter F13 in Table 27-7) and Total Jitter ( $T_{\text{jitter}}$ ) as being 2 \*  $P_{\text{jitter}}$ .

The CAN protocol uses a bit-stuffing technique that inserts a bit of a given polarity following five bits with the opposite polarity. This gives a total of 10 bits transmitted without re-synchronization (compensation for jitter or phase error).

Given the random nature of the jitter error added, it can be shown that the total error caused by the jitter tends to cancel itself over time. For a period of 10 bits, it is necessary to add only two jitter intervals to correct for jitter-induced error: one interval in the beginning of the 10-bit period and another at the end. The overall effect is shown in Figure 23-5.

# FIGURE 23-5: EFFECTS OF PHASE JITTER ON THE MICROCONTROLLER CLOCK AND CAN BIT TIME

Once these considerations are taken into account, it is possible to show that the relation between the jitter and the total frequency error can be defined as:

#### EQUATION 23-4:

$$\Delta f = \frac{T_{\text{jitter}}}{10 \times \text{NBT}} = \frac{2 \times P_{\text{jitter}}}{10 \times \text{NBT}}$$

where jitter is expressed in terms of time and NBT is the Nominal Bit Time.

For example, assume a CAN bit rate of 125 Kb/s, which gives an NBT of 8  $\mu$ s. For a 16 MHz clock generated from a 4x PLL, the jitter at this clock frequency is:

#### **EQUATION 23-5:**

$$2\% \times \frac{1}{16 \text{ MHz}} = \frac{0.02}{16 \times 10^6} = 1.25 \text{ ns}$$

The resultant frequency error is:

#### EQUATION 23-6:

$$\frac{2 \times (1.25 \times 10^{-9})}{10 \times (8 \times 10^{-6})} = 3.125 \times 10^{-5} = 0.0031\%$$

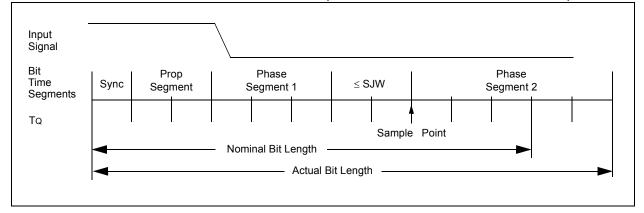

# 23.10 Synchronization

To compensate for phase shifts between the oscillator frequencies of each of the nodes on the bus, each CAN controller must be able to synchronize to the relevant signal edge of the incoming signal. When an edge in the transmitted data is detected, the logic will compare the location of the edge to the expected time (Sync\_Seg). The circuit will then adjust the values of Phase Segment 1 and Phase Segment 2 as necessary. There are two mechanisms used for synchronization.

#### 23.10.1 HARD SYNCHRONIZATION

Hard synchronization is only done when there is a recessive to dominant edge during a bus Idle condition, indicating the start of a message. After hard synchronization, the bit time counters are restarted with Sync\_Seg. Hard synchronization forces the edge which has occurred to lie within the synchronization segment of the restarted bit time. Due to the rules of synchronization, if a hard synchronization occurs, there will not be a resynchronization within that bit time.

#### 23.10.2 RESYNCHRONIZATION

As a result of resynchronization, Phase Segment 1 may be lengthened or Phase Segment 2 may be shortened. The amount of lengthening or shortening of the phase buffer segments has an upper bound given by the Synchronization Jump Width (SJW). The value of the SJW will be added to Phase Segment 1 (see Figure 23-6) or subtracted from Phase Segment 2 (see Figure 23-7). The SJW is programmable between 1 TQ and 4 TQ.

Clocking information will only be derived from recessive to dominant transitions. The property, that only a fixed maximum number of successive bits have the same value, ensures resynchronization to the bit stream during a frame. The phase error of an edge is given by the position of the edge relative to Sync\_Seg, measured in Tq. The phase error is defined in magnitude of Tq as follows:

- e = 0 if the edge lies within Sync\_Seg.

- e > 0 if the edge lies before the sample point.

- e < 0 if the edge lies after the sample point of the previous bit.

If the magnitude of the phase error is less than, or equal to, the programmed value of the Synchronization Jump Width, the effect of a resynchronization is the same as that of a hard synchronization.

If the magnitude of the phase error is larger than the Synchronization Jump Width and if the phase error is positive, then Phase Segment 1 is lengthened by an amount equal to the Synchronization Jump Width.

If the magnitude of the phase error is larger than the resynchronization jump width and if the phase error is negative, then Phase Segment 2 is shortened by an amount equal to the Synchronization Jump Width.

#### 23.10.3 SYNCHRONIZATION RULES

- Only one synchronization within one bit time is allowed.

- An edge will be used for synchronization only if the value detected at the previous sample point (previously read bus value) differs from the bus value immediately after the edge.

- All other recessive to dominant edges fulfilling rules 1 and 2 will be used for resynchronization, with the exception that a node transmitting a dominant bit will not perform a resynchronization as a result of a recessive to dominant edge with a positive phase error.

#### FIGURE 23-6: LENGTHENING A BIT PERIOD (ADDING SJW TO PHASE SEGMENT 1)

# 23.14 Error Detection

The CAN protocol provides sophisticated error detection mechanisms. The following errors can be detected.

#### 23.14.1 CRC ERROR

With the Cyclic Redundancy Check (CRC), the transmitter calculates special check bits for the bit sequence, from the start of a frame until the end of the data field. This CRC sequence is transmitted in the CRC field. The receiving node also calculates the CRC sequence using the same formula and performs a comparison to the received sequence. If a mismatch is detected, a CRC error has occurred and an error frame is generated. The message is repeated.

### 23.14.2 ACKNOWLEDGE ERROR

In the Acknowledge field of a message, the transmitter checks if the Acknowledge slot (which was sent out as a recessive bit) contains a dominant bit. If not, no other node has received the frame correctly. An Acknowledge error has occurred, an error frame is generated and the message will have to be repeated.

#### 23.14.3 FORM ERROR

If a node detects a dominant bit in one of the four segments, including End-of-Frame, interframe space, Acknowledge delimiter or CRC delimiter, then a form error has occurred and an error frame is generated. The message is repeated.

#### 23.14.4 BIT ERROR

A bit error occurs if a transmitter sends a dominant bit and detects a recessive bit, or if it sends a recessive bit and detects a dominant bit, when monitoring the actual bus level and comparing it to the just transmitted bit. In the case where the transmitter sends a recessive bit and a dominant bit is detected during the arbitration field and the Acknowledge slot, no bit error is generated because normal arbitration is occurring.

#### 23.14.5 STUFF BIT ERROR

If, between the Start-of-Frame and the CRC delimiter, six consecutive bits with the same polarity are detected, the bit stuffing rule has been violated. A stuff bit error occurs and an error frame is generated. The message is repeated.

### 23.14.6 ERROR STATES

Detected errors are made public to all other nodes via error frames. The transmission of the erroneous message is aborted and the frame is repeated as soon as possible. Furthermore, each CAN node is in one of the three error states: "error-active", "error-passive" or "bus-off", according to the value of the internal error counters. The error-active state is the usual state where the bus node can transmit messages and activate error frames (made of dominant bits) without any restrictions. In the error-passive state, messages and passive error frames (made of recessive bits) may be transmitted. The bus-off state makes it temporarily impossible for the station to participate in the bus communication. During this state, messages can neither be received nor transmitted.

### 23.14.7 ERROR MODES AND ERROR COUNTERS

The PIC18F2682/2685/4682/4685 devices contain two error counters: the Receive Error Counter (RXERRCNT) and the Transmit Error Counter (TXERRCNT). The values of both counters can be read by the MCU. These counters are incremented or decremented in accordance with the CAN bus specification.

The PIC18F2682/2685/4682/4685 devices are erroractive if both error counters are below the error-passive limit of 128. They are error-passive if at least one of the error counters equals or exceeds 128. They go to busoff if the transmit error counter equals or exceeds the bus-off limit of 256. The devices remain in this state until the bus-off recovery sequence is received. The bus-off recovery sequence consists of 128 occurrences of 11 consecutive recessive bits (see Figure 23-8). Note that the CAN module, after going bus-off, will recover back to error-active without any intervention by the MCU if the bus remains Idle for 128 x 11 bit times. If this is not desired, the error Interrupt Service Routine should address this. The current Error mode of the CAN module can be read by the MCU via the COMSTAT register.

Additionally, there is an Error State Warning flag bit, EWARN, which is set if at least one of the error counters equals or exceeds the error warning limit of 96. EWARN is reset if both error counters are less than the error warning limit.

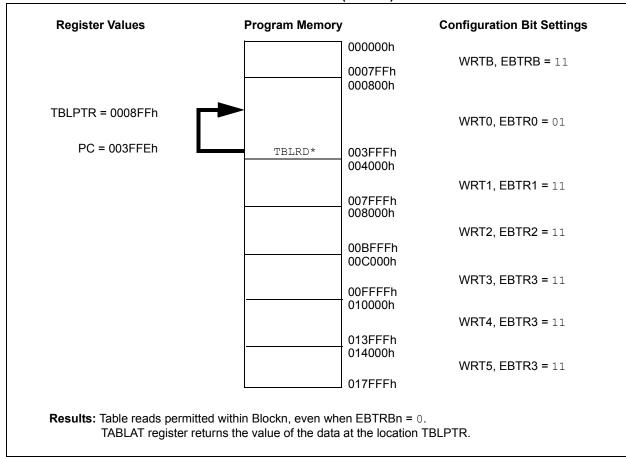

## FIGURE 24-8: EXTERNAL BLOCK TABLE READ (EBTRn) ALLOWED

| BRA                                                                                                                                                                                                                           | BRA Unconditional Branch              |                     |                     |               |     |              |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------|---------------------|---------------|-----|--------------|--|--|

| Synta                                                                                                                                                                                                                         | ax:                                   | BRA n               |                     |               |     |              |  |  |

| Oper                                                                                                                                                                                                                          | ands:                                 | -1024 ≤ n ≤         | 1023                |               |     |              |  |  |

| Oper                                                                                                                                                                                                                          | ation:                                | (PC) + 2 + 2        | $2n \rightarrow PC$ | ;             |     |              |  |  |

| Statu                                                                                                                                                                                                                         | is Affected:                          | None                |                     |               |     |              |  |  |

| Enco                                                                                                                                                                                                                          | oding:                                | 1101                | Onnn                | nnr           | n   | nnnn         |  |  |

| Description: Add the 2's complement number '2n' to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is a<br>two-cycle instruction. |                                       |                     |                     |               |     | e<br>vill be |  |  |

| Word                                                                                                                                                                                                                          | ls:                                   | 1                   | 1                   |               |     |              |  |  |

| Cycle                                                                                                                                                                                                                         | es:                                   | 2                   | 2                   |               |     |              |  |  |

| QC                                                                                                                                                                                                                            | ycle Activity:                        |                     |                     |               |     |              |  |  |

|                                                                                                                                                                                                                               | Q1                                    | Q2                  | Q3                  |               |     | Q4           |  |  |

|                                                                                                                                                                                                                               | Decode                                | Read literal<br>'n' | Proce<br>Data       |               | Wri | te to PC     |  |  |

|                                                                                                                                                                                                                               | No                                    | No                  | No                  |               |     | No           |  |  |

|                                                                                                                                                                                                                               | operation                             | operation           | operat              | ion           | ор  | eration      |  |  |

| <u>Exar</u>                                                                                                                                                                                                                   | n <u>ple:</u><br>Before Instruc<br>PC |                     |                     | Jump<br>HERE) |     |              |  |  |

|                                                                                                                                                                                                                               | After Instruction                     | on                  |                     |               |     |              |  |  |

| PC | = | address | (Jump) |

|----|---|---------|--------|

| BSF               | Bit Set f                                                                                                                                                                                                                                                                            |                                                                                                                  |         |                      |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------|----------------------|--|--|--|--|

| Syntax:           | BSF f, b {                                                                                                                                                                                                                                                                           | [,a}                                                                                                             |         |                      |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                                                                                                                   | $0 \le b \le 7$                                                                                                  |         |                      |  |  |  |  |

| Operation:        | $1 \rightarrow f \le b >$                                                                                                                                                                                                                                                            | $1 \rightarrow f < b >$                                                                                          |         |                      |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                 |                                                                                                                  |         |                      |  |  |  |  |

| Encoding:         | 1000                                                                                                                                                                                                                                                                                 | bbba                                                                                                             | ffff    | ffff                 |  |  |  |  |

| Description:      | Bit 'b' in reg                                                                                                                                                                                                                                                                       | gister 'f' i                                                                                                     | s set.  |                      |  |  |  |  |

|                   | lf 'a' is '1', t                                                                                                                                                                                                                                                                     | f 'a' is '0', the Access Bank is selected.<br>f 'a' is '1', the BSR is used to select the<br>GPR bank (default). |         |                      |  |  |  |  |

|                   | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                                                                                  |         |                      |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                    |                                                                                                                  |         |                      |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                    |                                                                                                                  |         |                      |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                      |                                                                                                                  |         |                      |  |  |  |  |

| Q1                | Q2                                                                                                                                                                                                                                                                                   | Q3                                                                                                               | 5       | Q4                   |  |  |  |  |

| Decode            | Read<br>register 'f'                                                                                                                                                                                                                                                                 | Proce<br>Data                                                                                                    |         | Write<br>egister 'f' |  |  |  |  |

| Example:          | BSF E                                                                                                                                                                                                                                                                                | T.AC RE                                                                                                          | G, 7, 1 |                      |  |  |  |  |

Before Instruction FLAG\_REG = 0Ah After Instruction FLAG\_REG = 8Ah

| DAW                                                          | Decimal Adjust W Register                                                                                                                                                                |                           |            | DECF                                                 | Decrement f                                                                                                                                                                                                                                                         |                 |                      |  |  |  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|--|--|--|

| Syntax:                                                      | DAW                                                                                                                                                                                      |                           |            | Syntax:                                              | Syntax: DECF f {,d {,a}}                                                                                                                                                                                                                                            |                 |                      |  |  |  |

| Operands:<br>Operation:                                      | None<br>If [W<3:0> >9] or [DC = 1] then                                                                                                                                                  |                           |            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                                                                                                                                                                                                                                     |                 |                      |  |  |  |

|                                                              | (W<3:0>) +<br>else                                                                                                                                                                       | $6 \rightarrow W < 3:0>;$ |            | Operation: $(f) - 1 \rightarrow dest$                |                                                                                                                                                                                                                                                                     |                 |                      |  |  |  |

|                                                              | (W<3:0>) –                                                                                                                                                                               | → W<3:0>                  |            | Status Affected:                                     | C, DC, N, OV, Z                                                                                                                                                                                                                                                     |                 |                      |  |  |  |

|                                                              | (W<7:4>) +<br>C = 1;<br>else                                                                                                                                                             |                           |            | Encoding:<br>Description:                            | 0000 01da ffff fff<br>Decrement register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default).                                                                                                |                 |                      |  |  |  |

| Status Affected:                                             | С                                                                                                                                                                                        |                           |            |                                                      | If 'a' is '0', the Access Bank is selected                                                                                                                                                                                                                          |                 |                      |  |  |  |

| Encoding:                                                    | 000000000111DAW adjusts the eight-bit value in W,<br>resulting from the earlier addition of two<br>variables (each in packed BCD format)<br>and produces a correct packed BCD<br>result. |                           |            |                                                      | If 'a' is '1', the BSR is used to select the GPR bank (default).<br>If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever $f \le 95$ (5Fh). See Section 25.2.3 "Byte-Oriented and |                 |                      |  |  |  |

| Description:                                                 |                                                                                                                                                                                          |                           |            |                                                      |                                                                                                                                                                                                                                                                     |                 |                      |  |  |  |

| Words:                                                       | 1                                                                                                                                                                                        |                           |            |                                                      |                                                                                                                                                                                                                                                                     |                 | ns in Indexed        |  |  |  |

| Cycles:                                                      | 1                                                                                                                                                                                        |                           |            | M/anda.                                              |                                                                                                                                                                                                                                                                     | set Mode" for   | details.             |  |  |  |

| Q Cycle Activity:                                            |                                                                                                                                                                                          |                           |            | Words:                                               | 1                                                                                                                                                                                                                                                                   |                 |                      |  |  |  |

| Q1                                                           | Q2                                                                                                                                                                                       | Q3                        | Q4         | Cycles:                                              | 1                                                                                                                                                                                                                                                                   |                 |                      |  |  |  |

| Decode                                                       | Read<br>register W                                                                                                                                                                       | Process<br>Data           | Write<br>W | Q Cycle Activity:<br>Q1                              | Q2                                                                                                                                                                                                                                                                  | Q3              | Q4                   |  |  |  |

| Example 1:                                                   | DAW                                                                                                                                                                                      | 2010                      |            | Decode                                               | Read<br>register 'f'                                                                                                                                                                                                                                                | Process<br>Data | Write to destination |  |  |  |

| Before Instruc                                               | ction                                                                                                                                                                                    |                           |            |                                                      |                                                                                                                                                                                                                                                                     |                 |                      |  |  |  |

| W<br>C                                                       | = A5h<br>= 0                                                                                                                                                                             |                           |            | Example:                                             | DECF                                                                                                                                                                                                                                                                | CNT, 1, 0       | )                    |  |  |  |

| ĎC                                                           | = 0                                                                                                                                                                                      |                           |            | Before Instruction                                   |                                                                                                                                                                                                                                                                     |                 |                      |  |  |  |

| After Instructio<br>W<br>C<br>DC                             | on<br>= 05h<br>= 1<br>= 0                                                                                                                                                                |                           |            | CNT<br>Z<br>After Instructi                          |                                                                                                                                                                                                                                                                     |                 |                      |  |  |  |

| Example 2:                                                   | - 0                                                                                                                                                                                      |                           |            | CNT<br>Z                                             | = 00h<br>= 1                                                                                                                                                                                                                                                        |                 |                      |  |  |  |

| Before Instruc<br>W<br>C<br>DC<br>After Instructio<br>W<br>C | = CEh<br>= 0<br>= 0                                                                                                                                                                      |                           |            |                                                      |                                                                                                                                                                                                                                                                     |                 |                      |  |  |  |

| RCA      | LL                                                        | Relative (                                                                                                                                                                                                                                                                               | Call       |                                                                             | RES      | ET                                           | Reset    |       |                                                        |      |  |  |

|----------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------|----------|----------------------------------------------|----------|-------|--------------------------------------------------------|------|--|--|

| Synta    | ix:                                                       | RCALL n                                                                                                                                                                                                                                                                                  |            |                                                                             | Synt     | Syntax:                                      |          | RESET |                                                        |      |  |  |

| Opera    | ands:                                                     | -1024 ≤ n ≤                                                                                                                                                                                                                                                                              | Ope        | Operands: None                                                              |          |                                              |          |       |                                                        |      |  |  |

| Opera    | ation:                                                    | (PC) + 2 →<br>(PC) + 2 + 2                                                                                                                                                                                                                                                               | Ope        | Operation: Reset all registers and flags that are affected by a MCLR Reset. |          |                                              |          |       |                                                        |      |  |  |

| Statu    | s Affected:                                               | None                                                                                                                                                                                                                                                                                     |            |                                                                             | Statu    | Status Affected: All                         |          |       |                                                        |      |  |  |

| Enco     | ding:                                                     | 1101                                                                                                                                                                                                                                                                                     | 1nnn nn    | inn nnnn                                                                    | Enco     | Encoding:                                    |          | 0000  | 1111                                                   | 1111 |  |  |

| Desc     | ription:                                                  | Subroutine call with a jump up to 1K<br>from the current location. First, return<br>address (PC + 2) is pushed onto the<br>stack. Then, add the 2's complement<br>number '2n' to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be |            |                                                                             | Desc     |                                              |          |       | ruction provides a way to<br>a MCLR Reset in software. |      |  |  |

|          |                                                           |                                                                                                                                                                                                                                                                                          |            |                                                                             | Wore     | Words:                                       |          | 1     |                                                        |      |  |  |

|          |                                                           |                                                                                                                                                                                                                                                                                          |            |                                                                             | Cycl     | es:                                          | 1        |       |                                                        |      |  |  |