#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 96KB (48K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4685-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 28/40/44-Pin Enhanced Flash Microcontrollers with ECAN<sup>™</sup> Technology, 10-Bit A/D and nanoWatt Technology

#### **Power-Managed Modes:**

- · Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- · Sleep: CPU off, peripherals off

- Idle mode currents down to 5.8 μA typical

- Sleep mode currents down to 0.1 μÅ typical

- Timer1 Oscillator: 1.1 μA, 32 kHz, 2V

- Watchdog Timer: 2.1 μA

- Two-Speed Oscillator Start-up

#### **Flexible Oscillator Structure:**

- Four Crystal modes, up to 40 MHz

- 4x Phase Lock Loop (PLL) available for crystal and internal oscillators

- · Two External RC modes, up to 4 MHz

- Two External Clock modes, up to 40 MHz

- Internal Oscillator Block:

- 8 user-selectable frequencies, from 31 kHz to 8 MHz

- Provides a complete range of clock speeds,

- from 31 kHz to 32 MHz when used with PLL User-tunable to compensate for frequency drift

- Secondary Oscillator using Timer1 @ 32 kHz

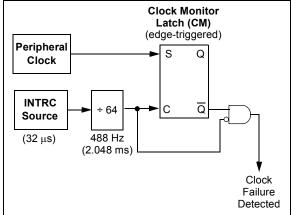

- Fail-Safe Clock Monitor

- Allows for safe shutdown if peripheral clock stops

#### **Special Microcontroller Features:**

- C compiler Optimized Architecture with optional Extended Instruction Set

- 100,000 Erase/Write Cycle Enhanced Flash Program Memory typical

- 1,000,000 Erase/Write Cycle Data EEPROM Memory typical

- Flash/Data EEPROM Retention: > 40 years

- Self-Programmable under Software Control

- Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 41 ms to 131s

- Single-Supply 5V In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

- In-Circuit Debug (ICD) via two pins

- Wide operating voltage range: 2.0V to 5.5V

#### Peripheral Highlights:

- High-Current Sink/source 25 mA/25 mA

- Three External Interrupts

- One Capture/Compare/PWM (CCP1) module

- Enhanced Capture/Compare/PWM (ECCP1) module (40/44-pin devices only):

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-shutdown and auto-restart

- Master Synchronous Serial Port (MSSP) module supporting 3-Wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- Enhanced Addressable USART module:

- Supports RS-485, RS-232 and LIN 1.3

- RS-232 operation using internal oscillator block (no external crystal required)

- Auto-wake-up on Start bit

- Auto-Baud Detect

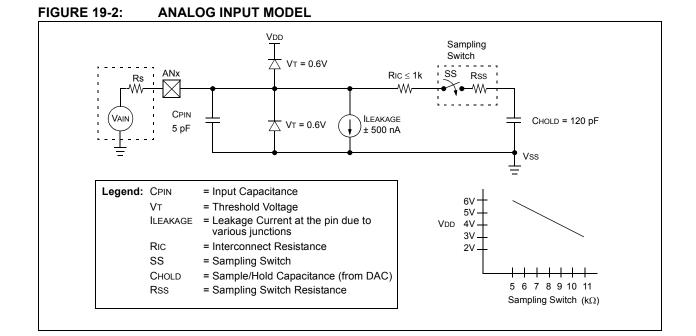

- 10-Bit, up to 11-Channel Analog-to-Digital Converter module (A/D), up to 100 ksps:

- Auto-acquisition capability

- Conversion available during Sleep

- · Dual Analog Comparators with Input Multiplexing

#### **ECAN Module Features:**

- Message bit rates up to 1 Mbps

- · Conforms to CAN 2.0B ACTIVE Specification

- Fully Backward Compatible with PIC18XXX8 CAN modules

- Three Modes of Operation:

- Legacy, Enhanced Legacy, FIFO

- · Three Dedicated Transmit Buffers with Prioritization

- Two Dedicated Receive Buffers

- Six Programmable Receive/Transmit Buffers

- · Three Full, 29-Bit Acceptance Masks

- 16 Full, 29-Bit Acceptance Filters w/Dynamic Association

- DeviceNet™ Data Byte Filter Support

- Automatic Remote Frame Handling

- Advanced Error Management Features

|            | Prog             | ram Memory                    | Data            | Memory            |       | 40 84                  | CCP1/ | MS  | SSP                         | RT   |       | Time               |

|------------|------------------|-------------------------------|-----------------|-------------------|-------|------------------------|-------|-----|-----------------------------|------|-------|--------------------|

| Device     | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O   | I/O 10-Bit<br>A/D (ch) |       | SPI | Master<br>I <sup>2</sup> C™ | EUSA | Comp. | Timers<br>8/16-bit |

| PIC18F2682 | 80K              | 40960                         | 3328            | 1024              | 28    | 8                      | 1/0   | Y   | Y                           | 1    | 0     | 1/3                |

| PIC18F2685 | 96K              | 49152                         | 3328            | 1024              | 28    | 8                      | 1/0   | Y   | Y                           | 1    | 0     | 1/3                |

| PIC18F4682 | 80K              | 40960                         | 3328            | 1024              | 40/44 | 11                     | 1/1   | Y   | Y                           | 1    | 2     | 1/3                |

| PIC18F4685 | 96K              | 49152                         | 3328            | 1024              | 40/44 | 11                     | 1/1   | Y   | Y                           | 1    | 2     | 1/3                |

#### 1.2 Other Special Features

- **Memory Endurance:** The Enhanced Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles – up to 100,000 for program memory and 1,000,000 for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-Programmability: These devices can write to their own program memory spaces under internal software control. By using a bootloader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18F2682/ 2685/4682/4685 family introduces an optional extension to the PIC18 instruction set, which adds 8 new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Enhanced CCP1 Module: In PWM mode, this module provides 1, 2 or 4 modulated outputs for controlling half-bridge and full-bridge drivers. Other features include auto-shutdown, for disabling PWM outputs on interrupt or other select conditions, and auto-restart to reactivate outputs once the condition has cleared.

- Enhanced Addressable USART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN bus protocol. Other enhancements include Auto-Baud Rate Detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reduce code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing a time-out range from 4 ms to over 131 seconds, that is stable across operating voltage and temperature.

#### 1.3 Details on Individual Family Members

Devices in the PIC18F2682/2685/4682/4685 family are available in 28-pin (PIC18F2682/2685) and 40/44-pin (PIC18F4682/4685) packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2.

The devices are differentiated from each other in six ways:

- 1. Flash program memory (80 Kbytes for PIC18F2682/4682 devices, 96 Kbytes for PIC18F2685/4685 devices).

- 2. A/D channels (8 for PIC18F2682/2685 devices, 11 for PIC18F4682/4685 devices).

- 3. I/O ports (3 bidirectional ports and 1 input only port on PIC18F2682/2685 devices, 5 bidirectional ports on PIC18F4682/4685 devices).

- CCP1 and Enhanced CCP1 implementation (PIC18F2682/2685 devices have 1 standard CCP1 module, PIC18F4682/4685 devices have one standard CCP1 module and one ECCP1 module).

- 5. Parallel Slave Port (present only on PIC18F4682/4685 devices).

- 6. PIC18F4682/4685 devices provide two comparators.

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in Table 1-2 and Table 1-3.

Like all Microchip PIC18 devices, members of the PIC18F2682/2685/4682/4685 family are available as both standard and low-voltage devices. Standard devices with Enhanced Flash memory, designated with an "F" in the part number (such as PIC18F2685), accommodate an operating VDD range of 4.2V to 5.5V. Low-voltage parts, designated by "LF" (such as PIC18LF2685), function over an extended VDD range of 2.0V to 5.5V.

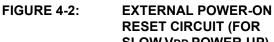

#### 4.2 Master Clear Reset (MCLR)

The MCLR pin provides a method for triggering an external Reset of the device. A Reset is generated by holding the pin low. These devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The MCLR pin is not driven low by any internal Resets, including the WDT.

In PIC18F2682/2685/4682/4685 devices, the  $\overline{\text{MCLR}}$  input can be disabled with the MCLRE Configuration bit. When  $\overline{\text{MCLR}}$  is disabled, the pin becomes a digital input. See **Section 10.5 "PORTE, TRISE and LATE Registers"** for more information.

#### 4.3 **Power-on Reset (POR)**

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the POR bit (RCON<1>). The state of the bit is set to '0' whenever a Power-on Reset occurs; it does not change for any other Reset event. POR is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any Power-on Reset.

#### 12.2 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 12-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. The Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

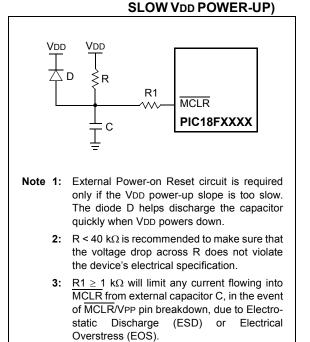

#### 12.3 Timer1 Oscillator

An on-chip crystal oscillator circuit is incorporated between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting the Timer1 Oscillator Enable bit, T1OSCEN (T1CON<3>). The oscillator is a low-power circuit rated for 32 kHz crystals. It will continue to run during all power-managed modes. The circuit for a typical LP oscillator is shown in Figure 12-3. Table 12-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper start-up of the Timer1 oscillator.

#### FIGURE 12-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

## TABLE 12-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR<sup>(1,2,3,4)</sup>

| USCILLATOR                                                                                        |                                                                                                                                                                     |                |              |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|--|--|--|--|--|--|--|

| Osc Type                                                                                          | Freq                                                                                                                                                                | C1             | C2           |  |  |  |  |  |  |  |

| LP                                                                                                | 32.768 kHz                                                                                                                                                          | 27 pF          | 27 pF        |  |  |  |  |  |  |  |

| Note 1: Microchip suggests these values as a starting point in validating the oscillator circuit. |                                                                                                                                                                     |                |              |  |  |  |  |  |  |  |

|                                                                                                   | Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time.                                                            |                |              |  |  |  |  |  |  |  |

|                                                                                                   | Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components. |                |              |  |  |  |  |  |  |  |

|                                                                                                   | Capacitor valu<br>only.                                                                                                                                             | es are for des | ign guidance |  |  |  |  |  |  |  |

#### 12.3.1 USING TIMER1 AS A CLOCK SOURCE

The Timer1 oscillator is also available as a clock source in power-managed modes. By setting the Clock Select bits, SCS1:SCS0 (OSCCON<1:0>), to '01', the device switches to SEC\_RUN mode; both the CPU and peripherals are clocked from the Timer1 oscillator. If the IDLEN bit (OSCCON<7>) is cleared and a SLEEP instruction is executed, the device enters SEC\_IDLE mode. Additional details are available in **Section 3.0 "Power-Managed Modes"**.

Whenever the Timer1 oscillator is providing the clock source, the Timer1 system clock status flag, T1RUN (T1CON<6>), is set. This can be used to determine the controller's current clocking mode. It can also indicate the clock source being currently used by the Fail-Safe Clock Monitor. If the Clock Monitor is enabled and the Timer1 oscillator fails while providing the clock, polling the T1RUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

#### 12.3.2 LOW-POWER TIMER1 OPTION

The Timer1 oscillator can operate at two distinct levels of power consumption based on device configuration. When the LPT1OSC Configuration bit is set, the Timer1 oscillator operates in a low-power mode. When LPT1OSC is not set, Timer1 operates at a higher power level. Power consumption for a particular mode is relatively constant, regardless of the device's operating mode. The default Timer1 configuration is the higher power mode.

As the low-power Timer1 mode tends to be more sensitive to interference, high noise environments may cause some oscillator instability. The low-power option is, therefore, best suited for low noise applications where power conservation is an important design consideration.

NOTES:

#### REGISTER 17-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE)

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | CKP   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | WCOL: Write Collision Detect bit (Transmit mode only)                                                                                                                                                                                                                                                                                                                                           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = The SSPBUF register is written while it is still transmitting the previous word<br/>(must be cleared in software)</li> <li>0 = No collision</li> </ul>                                                                                                                                                                                                                             |

| bit 6   | SSPOV: Receive Overflow Indicator bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>SPI Slave mode:</li> <li>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. The user must read the SSPBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software).</li> <li>0 = No overflow</li> </ul>                   |

| bit 5   | SSPEN: Master Synchronous Serial Port Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = Enables serial port and configures SCK, SDO, SDI and $\overline{SS}$ as serial port pins <sup>(2)</sup><br>0 = Disables serial port and configures these pins as I/O port pins <sup>(2)</sup>                                                                                                                                                                                               |

| bit 4   | CKP: Clock Polarity Select bit                                                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Idle state for clock is a high level</li> <li>0 = Idle state for clock is a low level</li> </ul>                                                                                                                                                                                                                                                                                   |

| bit 3-0 | SSPM3:SSPM0: Master Synchronous Serial Port Mode Select bits <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>0101 = SPI Slave mode, clock = SCK pin, SS pin control disabled, SS can be used as I/O pin</li> <li>0100 = SPI Slave mode, clock = SCK pin, SS pin control enabled</li> <li>0011 = SPI Master mode, clock = TMR2 output/2</li> <li>0010 = SPI Master mode, clock = Fosc/64</li> <li>0001 = SPI Master mode, clock = Fosc/16</li> <li>0000 = SPI Master mode, clock = Fosc/4</li> </ul> |

| Note 1: | In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.                                                                                                                                                                                                                                                         |

- 2: When enabled, these pins must be properly configured as input or output.

- **3:** Bit combinations not specifically listed here are either reserved or implemented in  $I^2C^{TM}$  mode only.

The value in the ADRESH/ADRESL registers is not modified for a Power-on Reset. The ADRESH/ADRESL registers will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs. To determine acquisition time, see **Section 19.1 "A/D Acquisition Requirements"**. After this acquisition time has elapsed, the A/D conversion can be started. An acquisition time can be programmed to occur between setting the GO/DONE bit and the actual start of the conversion. The following steps should be followed to perform an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D acquisition time (ADCON2)

- Select A/D conversion clock (ADCON2)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear ADIF bit

- Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time (if required).

- 4. Start conversion:

- Set GO/DONE bit (ADCON0 register)

- 5. Wait for A/D conversion to complete, by either:

Polling for the GO/DONE bit to be cleared

OR

- Waiting for the A/D interrupt

- 6. Read A/D Result registers (ADRESH:ADRESL); clear bit, ADIF, if required.

- 7. For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before next acquisition starts.

#### 21.0 COMPARATOR VOLTAGE REFERENCE MODULE

Note: Comparators are only available in 40/44-pin devices (PIC18F4682/4685).

The comparator voltage reference is a 16-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram is of the module shown in Figure 21-1. The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

#### 21.1 Configuring the Comparator Voltage Reference

The voltage reference module is controlled through the CVRCON register (Register 21-1). The comparator voltage reference provides two ranges of output

voltage, each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF selection bits (CVR3:CVR0), with one range offering finer resolution. The equations used to calculate the output of the comparator voltage reference are as follows:

<u>If CVRR = 1:</u> CVREF = ((CVR3:CVR0)/24) x CVRSRC <u>If CVRR = 0:</u> CVREF = (CVDD x 1/4) + (((CVR3:CVR0)/32) x CVRSRC)

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF- that are multiplexed with RA2 and RA3. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 27-3 in Section 27.0 "Electrical Characteristics").

#### REGISTER 21-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|----------------------|-------|-------|-------|-------|-------|-------|

| CVREN | CVROE <sup>(1)</sup> | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  |

| bit 7 | •                    |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

| bit 7   | CVREN: Comparator Voltage Reference Enable bit                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = CVREF circuit powered on                                                                                                                              |

|         | 0 = CVREF circuit powered down                                                                                                                            |

| bit 6   | CVROE: Comparator VREF Output Enable bit <sup>(1)</sup>                                                                                                   |

|         | <ul> <li>1 = CVREF voltage level is also output on the RA0/AN0/CVREF pin</li> <li>0 = CVREF voltage is disconnected from the RA0/AN0/CVREF pin</li> </ul> |

| bit 5   | CVRR: Comparator VREF Range Selection bit                                                                                                                 |

|         | <ul> <li>1 = 0.00 CVRsRc to 0.75 CVRsRc, with CVRsRc/24 step size</li> <li>0 = 0.25 CVRsRc to 0.75 CVRsRc, with CVRsRc/32 step size</li> </ul>            |

| bit 4   | CVRSS: Comparator VREF Source Selection bit                                                                                                               |

|         | <ul> <li>1 = Comparator reference source, CVRSRC = (VREF+) – (VREF-)</li> <li>0 = Comparator reference source, CVRSRC = VDD – VSS</li> </ul>              |

| bit 3-0 | <b>CVR3:CVR0:</b> Comparator VREF Value Selection bits ( $0 \le (CVR3:CVR0) \le 15$ )                                                                     |

|         | <u>When CVRR = 1:</u><br>CVREF = ((CVR3:CVR0)/24) • (CVRsRc)                                                                                              |

|         | When CVRR = 0:                                                                                                                                            |

|         | CVREF = (CVRSRC/4) + ((CVR3:CVR0)/32) • (CVRSRC)                                                                                                          |

|         |                                                                                                                                                           |

**Note 1:** CVROE overrides the TRISA<0> bit setting. If enabled for output, RA2 must also be configured as an input by setting TRISA<2> to '1'.

| Moden      | R/C-0                                                                                                                                                                                  | R/W-0                       | R/W-0            | U-0           | R-0             | R/W-0                                             | R-0           | R-0     |  |  |  |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|---------------|-----------------|---------------------------------------------------|---------------|---------|--|--|--|--|--|--|--|--|

| Mode 0     | RXFUL <sup>(1)</sup>                                                                                                                                                                   | RXM1                        | RXM0             |               | RXRTRRO         | FILHIT2                                           | FILHIT1       | FILHIT0 |  |  |  |  |  |  |  |  |

|            | <b>D</b> / <b>D</b> / <b>D</b>                                                                                                                                                         |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

| Mode 1,2   | R/C-0                                                                                                                                                                                  | R/W-0                       | R-0              | R-0           | R-0             | R-0                                               | R-0           | R-0     |  |  |  |  |  |  |  |  |

|            | RXFUL <sup>(1)</sup>                                                                                                                                                                   | RXM1                        | RTRRO            | FILHIT4       | FILHIT3         | FILHIT2                                           | FILHIT1       | FILHITO |  |  |  |  |  |  |  |  |

|            | bit 7                                                                                                                                                                                  |                             |                  |               |                 |                                                   |               | bit (   |  |  |  |  |  |  |  |  |

| Legend:    |                                                                                                                                                                                        |                             | C = Clearabl     | e bit         |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

| R = Reada  | able bit                                                                                                                                                                               |                             | W = Writable     | bit           | U = Unimple     | mented bit, r                                     | ead as '0'    |         |  |  |  |  |  |  |  |  |

| -n = Value | at POR                                                                                                                                                                                 |                             | '1' = Bit is se  | t             | '0' = Bit is cl | eared                                             | x = Bit is un | known   |  |  |  |  |  |  |  |  |

|            |                                                                                                                                                                                        |                             | (1)              |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

| bit 7      | RXFUL: Rece                                                                                                                                                                            |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            | 1 = Receive b                                                                                                                                                                          |                             |                  |               | P               |                                                   |               |         |  |  |  |  |  |  |  |  |

| bit 6      | <ul><li>0 = Receive buffer is open to receive a new message</li><li>Mode 0:</li></ul>                                                                                                  |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            | <b>RXM1:</b> Receive Buffer Mode bit 1 (combines with RXM0 to form RXM<1:0> bits, see bit 5)                                                                                           |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            | 11 = Receive all messages (including those with errors); filter criteria is ignored                                                                                                    |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            | 10 = Receive only valid messages with extended identifier; EXIDEN in RXFnSIDL must be '1'<br>01 = Receive only valid messages with standard identifier, EXIDEN in RXFnSIDL must be '0' |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            | 01 = Receive only valid messages with standard identifier, EXIDEN in RXFnSIDL must be '0'<br>00 = Receive all valid messages as per EXIDEN bit in RXFnSIDL register                    |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            | Mode 1, 2:                                                                                                                                                                             |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            | RXM1: Receive Buffer Mode bit                                                                                                                                                          |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            | <ul> <li>1 = Receive all messages (including those with errors); acceptance filters are ignored</li> <li>0 = Receive all valid messages as per acceptance filters</li> </ul>           |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

| bit 5      | <u>Mode 0:</u><br><b>RXM0:</b> Receiv                                                                                                                                                  | /e Buffer Mo                | de bit 0 (comb   | ines with R   | XM1 to form F   | RXM<1:0> bit                                      | s. see bit 6) |         |  |  |  |  |  |  |  |  |

|            | <u>Mode 1, 2:</u>                                                                                                                                                                      |                             | ·                |               |                 |                                                   | , ,           |         |  |  |  |  |  |  |  |  |

|            | RTRRO: Remote Transmission Request bit for Received Message (read-only)                                                                                                                |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            | <ul> <li>1 = A remote transmission request is received</li> <li>0 = A remote transmission request is not received</li> </ul>                                                           |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

| bit 4      |                                                                                                                                                                                        | ransmission                 | request is not   | received      |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

| DIL 4      | Mode 0:<br>Unimplement                                                                                                                                                                 | ed: Read as                 | <b>s</b> 'O'     |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            | Mode 1, 2:                                                                                                                                                                             |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            | <b>FILHIT4:</b> Filter Hit bit 4<br>This bit combines with other bits to form filter acceptance bits <4:0>.                                                                            |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

|            |                                                                                                                                                                                        | nes with oth                | er bits to form  | filter accept | ance bits <4:0  | )>.                                               |               |         |  |  |  |  |  |  |  |  |

|            | <u>Mode 0:</u><br>RXRTRRO: R                                                                                                                                                           | emote Trans                 | smission Requ    | est bit for R | eceived Mess    | age (read-or                                      | nlv)          |         |  |  |  |  |  |  |  |  |

| bit 3      | <b>RXRTRRO:</b> Remote Transmission Request bit for Received Message (read-only)<br>1 = A remote transmission request is received                                                      |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

| bit 3      |                                                                                                                                                                                        |                             |                  |               |                 | 0 = A remote transmission request is not received |               |         |  |  |  |  |  |  |  |  |

| bit 3      | 0 = A remote t                                                                                                                                                                         |                             |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

| bit 3      | 0 = A remote t<br><u>Mode 1, 2:</u>                                                                                                                                                    | transmission                |                  |               |                 |                                                   |               |         |  |  |  |  |  |  |  |  |

| DIT 3      | 0 = A remote t                                                                                                                                                                         | transmission<br>r Hit bit 3 | n request is not | received      | ance bits <4:0  | )>.                                               |               |         |  |  |  |  |  |  |  |  |

#### REGISTER 23-14: RXB1CON: RECEIVE BUFFER 1 CONTROL REGISTER

#### 23.2.6 CAN INTERRUPT REGISTERS

Register 23-56 through Register 23-58 in this section are the same as described in **Section 9.0 "Interrupts"**. They are duplicated here for convenience.

#### REGISTER 23-56: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

| Mode 0       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                 | R/W-0                                                                                | R/W-0                                                 | R/W-0                 | R/W-0                                | R/W-0         | R/W-0    |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------|--------------------------------------|---------------|----------|--|

| Mode o       | IRXIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WAKIF                                                                                                                 | ERRIF                                                                                | TXB2IF                                                | TXB1IF <sup>(1)</sup> | TXB0IF <sup>(1)</sup>                | RXB1IF        | RXB0IF   |  |

| Mode 1,2     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                 | R/W-0                                                                                | R/W-0                                                 | R/W-0                 | R/W-0                                | R/W-0         | R/W-0    |  |

|              | IRXIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WAKIF                                                                                                                 | ERRIF                                                                                | TXBnIF                                                | TXB1IF <sup>(1)</sup> | TXB0IF <sup>(1)</sup>                | RXBnlF        | FIFOWMIF |  |

|              | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                       |                                                                                      |                                                       |                       |                                      |               | bit C    |  |

| Legend:      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                       |                                                                                      |                                                       |                       |                                      |               |          |  |

| R = Readab   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                       | W = Writable                                                                         |                                                       | •                     | emented bit, r                       | ead as '0'    |          |  |

| -n = Value a | It POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                       | '1' = Bit is se                                                                      | et                                                    | '0' = Bit is c        | leared                               | x = Bit is un | known    |  |

| bit 7        | 1 = An invali                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Invalid Recei<br>id message h<br>id message c                                                                         | as occurred                                                                          |                                                       |                       |                                      |               |          |  |

| bit 6        | WAKIF: CAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | N bus Activity<br>on CAN bus h<br>ity on CAN bu                                                                       | Wake-up Int                                                                          | errupt Flag I                                         | bit                   |                                      |               |          |  |

| bit 5        | ERRIF: CAN<br>1 = An error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | l bus Error In                                                                                                        | terrupt Flag b<br>d in the CAN                                                       |                                                       | Itiple sources        | )                                    |               |          |  |

| bit 4        | TXB2IF: CA<br>1 = Transm<br>0 = Transm<br>When CAN i<br>TXBnIF: An<br>1 = One or                                                                                                                                                                                                                                                                                                                                                                                                                                               | it Buffer 2 has<br><u>is in Mode 1 d</u><br>y Transmit Bu                                                             | s completed t<br>s not complet<br>o <u>r 2:</u><br>uffer Interrupt<br>t buffers have | ransmission<br>ed transmis<br>Flag bit<br>e completed | sion of a mes         | e and may be<br>sage<br>of a message |               | reloaded |  |

| bit 3        | 1 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                       | completed tr                                                                         | ansmission                                            |                       | e and may be<br>sage                 | reloaded      |          |  |

| bit 2        | <b>TXB0IF:</b> CA<br>1 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | N Transmit B<br>t Buffer 0 has                                                                                        | uffer 0 Interru<br>completed tr                                                      | upt Flag bit <sup>(1</sup><br>ansmission              | )<br>of a message     | e and may be                         | reloaded      |          |  |

| bit 1        | <ul> <li>0 = Transmit Buffer 0 has not completed transmission of a message</li> <li>When CAN is in Mode 0:</li> <li>RXB1IF: CAN Receive Buffer 1 Interrupt Flag bit</li> <li>1 = Receive Buffer 1 has received a new message</li> <li>0 = Receive Buffer 1 has not received a new message</li> <li>When CAN is in Mode 1 or 2:</li> <li>RXBnIF: Any Receive Buffer Interrupt Flag bit</li> <li>1 = One or more receive buffers has received a new message</li> <li>0 = No receive buffer has received a new message</li> </ul> |                                                                                                                       |                                                                                      |                                                       |                       |                                      |               |          |  |

| bit 0        | When CAN is<br><b>RXB0IF:</b> CA<br>1 = Receive<br>0 = Receive<br>When CAN is<br><b>Unimpleme</b>                                                                                                                                                                                                                                                                                                                                                                                                                              | is in Mode 0:<br>N Receive B<br>Buffer 0 has<br>Buffer 0 has<br>is in Mode 1:<br><b>nted:</b> Read a<br>is in Mode 2: | uffer 0 Interru<br>received a ne<br>not received                                     | ipt Flag bit<br>ew message                            | 9                     |                                      |               |          |  |

**Note 1:** In CAN Mode 1 and 2, these bits are forced to '0'.

| Address <sup>(1)</sup> | Name     | Address | Name    | Address | Name | Address | Name      |

|------------------------|----------|---------|---------|---------|------|---------|-----------|

| DFFh                   | (4)      | DDFh    | (4)     | DBFh    | (4)  | D9Fh    | (4)       |

| DFEh                   | (4)      | DDEh    | (4)     | DBEh    | (4)  | D9Eh    | (4)       |

| DFDh                   | (4)      | DDDh    | (4)     | DBDh    | (4)  | D9Dh    | (4)       |

| DFCh                   | TXBIE    | DDCh    | (4)     | DBCh    | (4)  | D9Ch    | (4)       |

| DFBh                   | (4)      | DDBh    | (4)     | DBBh    | (4)  | D9Bh    | (4)       |

| DFAh                   | BIE0     | DDAh    | (4)     | DBAh    | (4)  | D9Ah    | (4)       |

| DF9h                   | (4)      | DD9h    | (4)     | DB9h    | (4)  | D99h    | (4)       |

| DF8h                   | BSEL0    | DD8h    | SDFLC   | DB8h    | (4)  | D98h    | (4)       |

| DF7h                   | (4)      | DD7h    | (4)     | DB7h    | (4)  | D97h    | (4)       |

| DF6h                   | (4)      | DD6h    | (4)     | DB6h    | (4)  | D96h    | (4)       |

| DF5h                   | (4)      | DD5h    | RXFCON1 | DB5h    | (4)  | D95h    | (4)       |

| DF4h                   | (4)      | DD4h    | RXFCON0 | DB4h    | (4)  | D94h    | (4)       |

| DF3h                   | MSEL3    | DD3h    | (4)     | DB3h    | (4)  | D93h    | RXF15EIDL |

| DF2h                   | MSEL2    | DD2h    | (4)     | DB2h    | (4)  | D92h    | RXF15EIDH |

| DF1h                   | MSEL1    | DD1h    | (4)     | DB1h    | (4)  | D91h    | RXF15SIDL |

| DF0h                   | MSEL0    | DD0h    | (4)     | DB0h    | (4)  | D90h    | RXF15SIDH |

| DEFh                   | (4)      | DCFh    | (4)     | DAFh    | (4)  | D8Fh    | (4)       |

| DEEh                   | (4)      | DCEh    | (4)     | DAEh    | (4)  | D8Eh    | (4)       |

| DEDh                   | (4)      | DCDh    | (4)     | DADh    | (4)  | D8Dh    | (4)       |

| DECh                   | (4)      | DCCh    | (4)     | DACh    | (4)  | D8Ch    | (4)       |

| DEBh                   | (4)      | DCBh    | (4)     | DABh    | (4)  | D8Bh    | RXF14EIDL |

| DEAh                   | (4)      | DCAh    | (4)     | DAAh    | (4)  | D8Ah    | RXF14EIDH |

| DE9h                   | (4)      | DC9h    | (4)     | DA9h    | (4)  | D89h    | RXF14SIDL |

| DE8h                   | (4)      | DC8h    | (4)     | DA8h    | (4)  | D88h    | RXF14SIDH |

| DE7h                   | RXFBCON7 | DC7h    | (4)     | DA7h    | (4)  | D87h    | RXF13EIDL |

| DE6h                   | RXFBCON6 | DC6h    | (4)     | DA6h    | (4)  | D86h    | RXF13EIDH |

| DE5h                   | RXFBCON5 | DC5h    | (4)     | DA5h    | (4)  | D85h    | RXF13SIDL |

| DE4h                   | RXFBCON4 | DC4h    | (4)     | DA4h    | (4)  | D84h    | RXF13SIDH |

| DE3h                   | RXFBCON3 | DC3h    | (4)     | DA3h    | (4)  | D83h    | RXF12EIDL |

| DE2h                   | RXFBCON2 | DC2h    | (4)     | DA2h    | (4)  | D82h    | RXF12EIDH |

| DE1h                   | RXFBCON1 | DC1h    | (4)     | DA1h    | (4)  | D81h    | RXF12SIDL |

| DE0h                   | RXFBCON0 | DC0h    | (4)     | DA0h    | (4)  | D80h    | RXF12SIDH |

#### TABLE 23-1: CAN CONTROLLER REGISTER MAP (CONTINUED)

Note 1: Shaded registers are available in Access Bank low area, while the rest are available in Bank 15.

2: CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the controller register due to the Microchip header file requirement.

**3:** These registers are not CAN registers.

4: Unimplemented registers are read as '0'.

#### TABLE 23-1: CAN CONTROLLER REGISTER MAP (CONTINUED)

| Address <sup>(1)</sup> | Name      |

|------------------------|-----------|

| D7Fh                   | (4)       |

| D7Eh                   | (4)       |

| D7Dh                   | (4)       |

| D7Ch                   | (4)       |

| D7Bh                   | RXF11EIDL |

| D7Ah                   | RXF11EIDH |

| D79h                   | RXF11SIDL |

| D78h                   | RXF11SIDH |

| D77h                   | RXF10EIDL |

| D76h                   | RXF10EIDH |

| D75h                   | RXF10SIDL |

| D74h                   | RXF10SIDH |

| D73h                   | RXF9EIDL  |

| D72h                   | RXF9EIDH  |

| D71h                   | RXF9SIDL  |

| D70h                   | RXF9SIDH  |

| D6Fh                   | (4)       |

| D6Eh                   | (4)       |

| D6Dh                   | (4)       |

| D6Ch                   | (4)       |

| D6Bh                   | RXF8EIDL  |

| D6Ah                   | RXF8EIDH  |

| D69h                   | RXF8SIDL  |

| D68h                   | RXF8SIDH  |

| D67h                   | RXF7EIDL  |

| D66h                   | RXF7EIDH  |

| D65h                   | RXF7SIDL  |

| D64h                   | RXF7SIDH  |

| D63h                   | RXF6EIDL  |

| D62h                   | RXF6EIDH  |

| D61h                   | RXF6SIDL  |

| D60h                   | RXF6SIDH  |

**Note 1:** Shaded registers are available in Access Bank low area while the rest are available in Bank 15.

- **2:** CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the controller register due to the Microchip header file requirement.

- 3: These registers are not CAN registers.

- 4: Unimplemented registers are read as '0'.

#### 23.14 Error Detection

The CAN protocol provides sophisticated error detection mechanisms. The following errors can be detected.

#### 23.14.1 CRC ERROR

With the Cyclic Redundancy Check (CRC), the transmitter calculates special check bits for the bit sequence, from the start of a frame until the end of the data field. This CRC sequence is transmitted in the CRC field. The receiving node also calculates the CRC sequence using the same formula and performs a comparison to the received sequence. If a mismatch is detected, a CRC error has occurred and an error frame is generated. The message is repeated.

#### 23.14.2 ACKNOWLEDGE ERROR

In the Acknowledge field of a message, the transmitter checks if the Acknowledge slot (which was sent out as a recessive bit) contains a dominant bit. If not, no other node has received the frame correctly. An Acknowledge error has occurred, an error frame is generated and the message will have to be repeated.

#### 23.14.3 FORM ERROR

If a node detects a dominant bit in one of the four segments, including End-of-Frame, interframe space, Acknowledge delimiter or CRC delimiter, then a form error has occurred and an error frame is generated. The message is repeated.

#### 23.14.4 BIT ERROR

A bit error occurs if a transmitter sends a dominant bit and detects a recessive bit, or if it sends a recessive bit and detects a dominant bit, when monitoring the actual bus level and comparing it to the just transmitted bit. In the case where the transmitter sends a recessive bit and a dominant bit is detected during the arbitration field and the Acknowledge slot, no bit error is generated because normal arbitration is occurring.

#### 23.14.5 STUFF BIT ERROR

If, between the Start-of-Frame and the CRC delimiter, six consecutive bits with the same polarity are detected, the bit stuffing rule has been violated. A stuff bit error occurs and an error frame is generated. The message is repeated.

#### 23.14.6 ERROR STATES

Detected errors are made public to all other nodes via error frames. The transmission of the erroneous message is aborted and the frame is repeated as soon as possible. Furthermore, each CAN node is in one of the three error states: "error-active", "error-passive" or "bus-off", according to the value of the internal error counters. The error-active state is the usual state where the bus node can transmit messages and activate error frames (made of dominant bits) without any restrictions. In the error-passive state, messages and passive error frames (made of recessive bits) may be transmitted. The bus-off state makes it temporarily impossible for the station to participate in the bus communication. During this state, messages can neither be received nor transmitted.

#### 23.14.7 ERROR MODES AND ERROR COUNTERS

The PIC18F2682/2685/4682/4685 devices contain two error counters: the Receive Error Counter (RXERRCNT) and the Transmit Error Counter (TXERRCNT). The values of both counters can be read by the MCU. These counters are incremented or decremented in accordance with the CAN bus specification.

The PIC18F2682/2685/4682/4685 devices are erroractive if both error counters are below the error-passive limit of 128. They are error-passive if at least one of the error counters equals or exceeds 128. They go to busoff if the transmit error counter equals or exceeds the bus-off limit of 256. The devices remain in this state until the bus-off recovery sequence is received. The bus-off recovery sequence consists of 128 occurrences of 11 consecutive recessive bits (see Figure 23-8). Note that the CAN module, after going bus-off, will recover back to error-active without any intervention by the MCU if the bus remains Idle for 128 x 11 bit times. If this is not desired, the error Interrupt Service Routine should address this. The current Error mode of the CAN module can be read by the MCU via the COMSTAT register.

Additionally, there is an Error State Warning flag bit, EWARN, which is set if at least one of the error counters equals or exceeds the error warning limit of 96. EWARN is reset if both error counters are less than the error warning limit.

#### REGISTER 24-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| U-0                                                                        | U-0                                                           | U-0                                                                                                                                                                                           | R/P-1         | R/P-1        | R/P-1                 | R/P-1                 | R/P-1                 |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|-----------------------|-----------------------|-----------------------|--|

| _                                                                          | _                                                             | _                                                                                                                                                                                             | BORV1         | BORV0        | BOREN1 <sup>(1)</sup> | BOREN0 <sup>(1)</sup> | PWRTEN <sup>(1)</sup> |  |

| bit 7                                                                      |                                                               |                                                                                                                                                                                               |               | •            |                       |                       | bit 0                 |  |

|                                                                            |                                                               |                                                                                                                                                                                               |               |              |                       |                       |                       |  |

| Legend:                                                                    |                                                               |                                                                                                                                                                                               |               |              |                       |                       |                       |  |

| R = Readabl                                                                | e bit                                                         | P = Program                                                                                                                                                                                   | nable bit     | U = Unimpler | mented bit, read      | as '0'                |                       |  |

| -n = Value when device is unprogrammed u = Unchanged from programmed state |                                                               |                                                                                                                                                                                               |               |              |                       |                       |                       |  |

|                                                                            |                                                               |                                                                                                                                                                                               |               |              |                       |                       |                       |  |

| bit 7-5                                                                    | t 7-5 Unimplemented: Read as '0'                              |                                                                                                                                                                                               |               |              |                       |                       |                       |  |

| bit 4-3                                                                    | 4-3 BORV1:BORV0: Brown-out Reset Voltage bits                 |                                                                                                                                                                                               |               |              |                       |                       |                       |  |

| 11 = Minimum setting                                                       |                                                               |                                                                                                                                                                                               |               |              |                       |                       |                       |  |

|                                                                            | •                                                             |                                                                                                                                                                                               |               |              |                       |                       |                       |  |

|                                                                            | •                                                             |                                                                                                                                                                                               |               |              |                       |                       |                       |  |