# E·XFL

# XMOS - XS1-L6A-64-LQ64-C4 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | XCore                                                        |

| Core Size                  | 32-Bit 6-Core                                                |

| Speed                      | 400MIPS                                                      |

| Connectivity               | Configurable                                                 |

| Peripherals                | -                                                            |

| Number of I/O              | 36                                                           |

| Program Memory Size        | 64KB (16K x 32)                                              |

| Program Memory Type        | SRAM                                                         |

| EEPROM Size                | <u>.</u>                                                     |

| RAM Size                   | -                                                            |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                 |

| Data Converters            | -                                                            |

| Oscillator Type            | External                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 64-LQFP Exposed Pad                                          |

| Supplier Device Package    | 64-LQFP (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-l6a-64-lq64-c4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

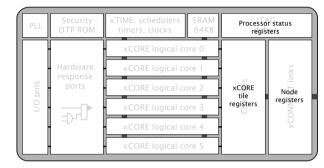

- Channels and channel ends Tasks running on logical cores communicate using channels formed between two channel ends. Data can be passed synchronously or asynchronously between the channel ends assigned to the communicating tasks. Section 5.5

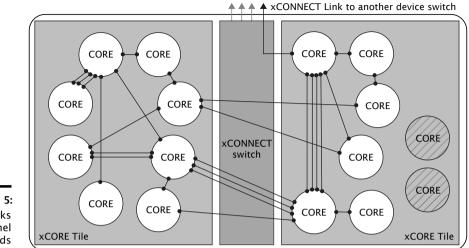

- xCONNECT Switch and Links Between tiles, channel communications are implemented over a high performance network of xCONNECT Links and routed through a hardware xCONNECT Switch. Section 5.6

- ▶ **Ports** The I/O pins are connected to the processing cores by Hardware Response ports. The port logic can drive its pins high and low, or it can sample the value on its pins optionally waiting for a particular condition. Section 5.3

- Clock blocks xCORE devices include a set of programmable clock blocks that can be used to govern the rate at which ports execute. Section 5.4

- Memory Each xCORE Tile integrates a bank of SRAM for instructions and data, and a block of one-time programmable (OTP) memory that can be configured for system wide security features. Section 8

- PLL The PLL is used to create a high-speed processor clock given a low speed external oscillator. Section 6

- JTAG The JTAG module can be used for loading programs, boundary scan testing, in-circuit source-level debugging and programming the OTP memory. Section 9

#### 1.1 Software

Devices are programmed using C, C++ or xC (C with multicore extensions). XMOS provides tested and proven software libraries, which allow you to quickly add interface and processor functionality such as USB, Ethernet, PWM, graphics driver, and audio EQ to your applications.

#### 1.2 xTIMEcomposer Studio

The xTIMEcomposer Studio development environment provides all the tools you need to write and debug your programs, profile your application, and write images into flash memory or OTP memory on the device. Because xCORE devices operate deterministically, they can be simulated like hardware within xTIMEcomposer: uniquely in the embedded world, xTIMEcomposer Studio therefore includes a static timing analyzer, cycle-accurate simulator, and high-speed in-circuit instrumentation.

xTIMEcomposer can be driven from either a graphical development environment, or the command line. The tools are supported on Windows, Linux and MacOS X and available at no cost from xmos.com/downloads. Information on using the tools is provided in the xTIMEcomposer User Guide, X3766.

$-X \Lambda ()S$

# 3 Pin Configuration

-XMOS

| Signal | Function                                                                         | Туре | Properties                       |

|--------|----------------------------------------------------------------------------------|------|----------------------------------|

| X0D11  | 1D <sup>0</sup>                                                                  | 1/0  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D12  | 1E <sup>0</sup>                                                                  | 1/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D13  | XLB <sup>4</sup> <sub>out</sub> 1F <sup>0</sup>                                  | 1/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D14  | $XLB_{out}^3$ 4C <sup>0</sup> 8B <sup>0</sup> 16A <sup>8</sup> 32A <sup>28</sup> | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D15  | $XLB_{out}^2$ 4C <sup>1</sup> 8B <sup>1</sup> 16A <sup>9</sup> 32A <sup>29</sup> | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D16  | $XLB_{out}^{1}$ 4D <sup>0</sup> 8B <sup>2</sup> 16A <sup>10</sup>                | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D17  | $XLB_{out}^{0}$ 4D <sup>1</sup> 8B <sup>3</sup> 16A <sup>11</sup>                | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D18  | $XLB_{in}^{0}$ 4D <sup>2</sup> 8B <sup>4</sup> 16A <sup>12</sup>                 | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D19  | $XLB_{in}^{1}$ 4D <sup>3</sup> 8B <sup>5</sup> 16A <sup>13</sup>                 | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D20  | $XLB_{in}^2$ $4C^2$ $8B^6$ $16A^{14}$ $32A^{30}$                                 | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D21  | $XLB_{in}^3$ 4C <sup>3</sup> 8B <sup>7</sup> 16A <sup>15</sup> 32A <sup>31</sup> | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D22  | $XLB_{in}^4$ 1G <sup>0</sup>                                                     | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D23  | 1H <sup>0</sup>                                                                  | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D24  | 110                                                                              | I/0  | PDs                              |

| X0D25  | 1J <sup>0</sup>                                                                  | I/0  | PDs                              |

| X0D26  | <b>4E<sup>0</sup></b> 8C <sup>0</sup> 16B <sup>0</sup>                           | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D27  | 4E 8C 16B                                                                        | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D32  | $4E^2 8C^6 16B^6$                                                                | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D33  | 4E <sup>3</sup> 8C <sup>7</sup> 16B <sup>7</sup>                                 | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D34  | 1K <sup>0</sup>                                                                  | I/0  | PDs                              |

| X0D35  | 1L <sup>0</sup>                                                                  | I/0  | PDs                              |

| X0D36  | 1M <sup>0</sup> 8D <sup>0</sup> 16B <sup>8</sup>                                 | I/O  | PDs                              |

| X0D37  | 1N <sup>0</sup> 8D <sup>1</sup> 16B <sup>9</sup>                                 | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D38  | 10 <sup>0</sup> 8D <sup>2</sup> 16B <sup>10</sup>                                | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D39  | 1P <sup>0</sup> 8D <sup>3</sup> 16B <sup>11</sup>                                | I/0  | PD <sub>S</sub> , R <sub>U</sub> |

-XMOS<sup>®</sup>-

Figure 5: Switch, links and channel ends

Information on the supported routing topologies that can be used to connect multiple devices together can be found in the XS1-L Link Performance and Design Guide, X2999.

# 6 PLL

The PLL creates a high-speed clock that is used for the switch, tile, and reference clock.

The PLL multiplication value is selected through the two MODE pins, and can be changed by software to speed up the tile or use less power. The MODE pins are set as shown in Figure 6:

|                | Oscillator | МС | DDE | Tile           | PLL Ratio | PLL | PLL settings |   |  |  |

|----------------|------------|----|-----|----------------|-----------|-----|--------------|---|--|--|

|                | Frequency  | 1  | 0   | Frequency      |           | OD  | F            | R |  |  |

| Figure 6:      | 5-13 MHz   | 0  | 0   | 130-399.75 MHz | 30.75     | 1   | 122          | 0 |  |  |

| PLL multiplier | 13-20 MHz  | 1  | 1   | 260-400.00 MHz | 20        | 2   | 119          | 0 |  |  |

| values and     | 20-48 MHz  | 1  | 0   | 167-400.00 MHz | 8.33      | 2   | 49           | 0 |  |  |

| MODE pins      | 48-100 MHz | 0  | 1   | 196-400.00 MHz | 4         | 2   | 23           | 0 |  |  |

Figure 6 also lists the values of OD, F and R, which are the registers that define the ratio of the tile frequency to the oscillator frequency:

-XMOS°

$$F_{core} = F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \times \frac{1}{OD+1}$$

- 1. Allocate channel-end 0.

- 2. Input a word on channel-end 0. It will use this word as a channel to acknowledge the boot. Provide the null-channel-end 0x0000FF02 if no acknowledgment is required.

- 3. Input the boot image specified above, including the CRC.

- 4. Input an END control token.

- 5. Output an END control token to the channel-end received in step 2.

- 6. Free channel-end 0.

- 7. Jump to the loaded code.

#### 7.3 Boot from OTP

If an xCORE tile is set to use secure boot (see Figure 7), the boot image is read from address 0 of the OTP memory in the tile's security module.

This feature can be used to implement a secure bootloader which loads an encrypted image from external flash, decrypts and CRC checks it with the processor, and discontinues the boot process if the decryption or CRC check fails. XMOS provides a default secure bootloader that can be written to the OTP along with secret decryption keys.

Each tile has its own individual OTP memory, and hence some tiles can be booted from OTP while others are booted from SPI or the channel interface. This enables systems to be partially programmed, dedicating one or more tiles to perform a particular function, leaving the other tiles user-programmable.

#### 7.4 Security register

The security register enables security features on the xCORE tile. The features shown in Figure 10 provide a strong level of protection and are sufficient for providing strong IP security.

### 8 Memory

#### 8.1 OTP

The xCORE Tile integrates 8 KB one-time programmable (OTP) memory along with a security register that configures system wide security features. The OTP holds data in four sectors each containing 512 rows of 32 bits which can be used to implement secure bootloaders and store encryption keys. Data for the security register is loaded from the OTP on power up. All additional data in OTP is copied from the OTP to SRAM and executed first on the processor.

The OTP memory is programmed using three special I/O ports: the OTP address port is a 16-bit port with resource ID 0x100200, the OTP data is written via a 32-bit

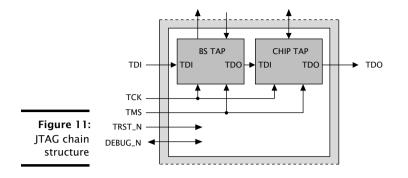

The JTAG chain structure is illustrated in Figure 11. Directly after reset, two TAP controllers are present in the JTAG chain: the boundary scan TAP and the chip TAP. The boundary scan TAP is a standard 1149.1 compliant TAP that can be used for boundary scan of the I/O pins. The chip TAP provides access into the xCORE Tile, switch and OTP for loading code and debugging.

The TRST\_N pin must be asserted low during and after power up for 100 ns. If JTAG is not required, the TRST\_N pin can be tied to ground to hold the JTAG module in reset.

The DEBUG\_N pin is used to synchronize the debugging of multiple xCORE Tiles. This pin can operate in both output and input mode. In output mode and when configured to do so, DEBUG\_N is driven low by the device when the processor hits a debug break point. Prior to this point the pin will be tri-stated. In input mode and when configured to do so, driving this pin low will put the xCORE Tile into debug mode. Software can set the behavior of the xCORE Tile based on this pin. This pin should have an external pull up of  $4K7-47K\Omega$  or left not connected in single core applications.

The JTAG device identification register can be read by using the IDCODE instruction. Its contents are specified in Figure 12.

Figure 12: IDCODE return value

| Bit3 | 31   |      |                |   | Device Identification Register Bit0 |   |     |   |   |   |                         |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|------|------|------|----------------|---|-------------------------------------|---|-----|---|---|---|-------------------------|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|      | Vers | sion | on Part Number |   |                                     |   |     |   |   |   | Manufacturer Identity 1 |     |   |   |   |   |   | 1 |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 0    | 0    | 0    | 0              | 0 | 0                                   | 0 | 0   | 0 | 0 | 0 | 0                       | 0   | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

|      | (    | )    |                |   | 0 0                                 |   | 0 2 |   |   |   |                         | 6 3 |   |   |   |   | 3 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

The JTAG usercode register can be read by using the USERCODE instruction. Its contents are specified in Figure 13. The OTP User ID field is read from bits [22:31] of the security register , *see* §8.1 (all zero on unprogrammed devices).

| Figure 13:   |

|--------------|

| USERCODE     |

| return value |

| <b>.</b>  | Bit | Bit31 |             |   |   |   |   |   |        |     |   | Usercode Register |   |                  |   |   |   |   |   |   |   |   | BitO |   |   |   |   |   |   |   |   |   |

|-----------|-----|-------|-------------|---|---|---|---|---|--------|-----|---|-------------------|---|------------------|---|---|---|---|---|---|---|---|------|---|---|---|---|---|---|---|---|---|

| 13:       |     |       | OTP User ID |   |   |   |   |   | Unused |     |   |                   |   | Silicon Revision |   |   |   |   |   |   |   |   |      |   |   |   |   |   |   |   |   |   |

| DE<br>lue | 0   | 0     | 0           | 0 | 0 | 0 | 0 | 0 | 0      | 0   | 0 | 0                 | 0 | 0                | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ue        |     |       | )           |   |   | ( | ) |   |        | . ( | ) |                   |   |                  | 2 |   |   | 8 | 3 |   |   | ( | )    |   |   | ( | ) |   |   | ( | ) |   |

XS1-L6A-64-LQ64

# 10 Board Integration

The device has the following power supply pins:

- ▶ VDD pins for the xCORE Tile

- VDDIO pins for the I/O lines

- PLL\_AVDD pins for the PLL

Several pins of each type are provided to minimize the effect of inductance within the package, all of which must be connected. The power supplies must be brought up monotonically and input voltages must not exceed specification at any time.

The VDD supply must ramp from 0V to its final value within 10 ms to ensure correct startup.

The VDDIO supply must ramp to its final value before VDD reaches 0.4 V.

The PLL\_AVDD supply should be separated from the other noisier supplies on the board. The PLL requires a very clean power supply, and a low pass filter (for example, a  $4.7 \Omega$  resistor and 100 nF multi-layer ceramic capacitor) is recommended on this pin.

The following ground pins are provided:

- PLL\_AGND for PLL\_AVDD

- ► GND for all other supplies

All ground pins must be connected directly to the board ground.

The VDD and VDDIO supplies should be decoupled close to the chip by several 100 nF low inductance multi-layer ceramic capacitors between the supplies and GND (for example,  $4\times100$ nF 0402 low inductance MLCCs per supply rail). The ground side of the decoupling capacitors should have as short a path back to the GND pins as possible. A bulk decoupling capacitor of at least 10 uF should be placed on each of these supplies.

RST\_N is an active-low asynchronous-assertion global reset signal. Following a reset, the PLL re-establishes lock after which the device boots up according to the boot mode (*see* §7). RST\_N and must be asserted low during and after power up for 100 ns.

#### 10.1 Land patterns and solder stencils

The land pattern recommendations in this document are based on a RoHS compliant process and derived, where possible, from the nominal *Generic Requirements for Surface Mount Design and Land Pattern Standards* IPC-7351B specifications. This standard aims to achieve desired targets of heel, toe and side fillets for solderjoints.

-XMOS-

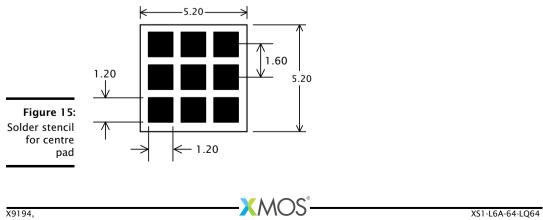

Solder paste and ground via recommendations are based on our engineering and development kit board production. They have been found to work and optimized as appropriate to achieve a high yield. The size, type and number of vias used in the center pad affects how much solder wicks down the vias during reflow. This in turn, along with solder paster coverage, affects the final assembled package height. These factors should be taken into account during design and manufacturing of the PCB.

The following land patterns and solder paste contains recommendations. Final land pattern and solder paste decisions are the responsibility of the customer. These should be tuned during manufacture to suit the manufacturing process.

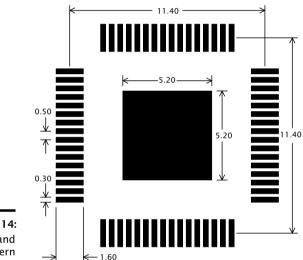

The package is a 64 pin Low profile Quad Flat Pack package with exposed heat slug on a 0.5mm pitch. An example land pattern is shown in Figure 14.

Figure 14: Example land pattern

> For the 64 pin LQFP package, a 3x3 array of squares for solder paste is recommended as shown in Figure 15. This gives a paste level of 48%.

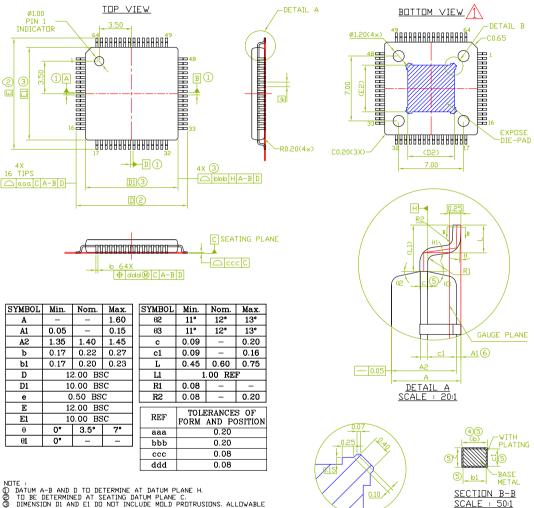

#### **Package Information** 12

- ITE : DATUM A-B AND D TO DETERMINE AT DATUM PLANE H. TO BE DETERMINED AT SEATING DATUM PLANE C. DIMENSION DI AND EI DO NDT INCLUDE MOLD PROTRUSIONS. ALLOWABLE PROTRUSION IS 0.25mm PER SIDE. DI AND EI ARE MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH. DIMENSION SHALL NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM 6 DIMENSION BY MORE THAN 0.08mm, DAMBAR CANNOT BE LOCATED DN THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD IS 0.07mm FOR 0.4mm AND 0.5mm PITCH PACKAGE. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE BETWEEN 0.10mm AND 0.25mm FROM THE LEAD TIP. AI IS THE DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY. PACKAGE DIMENSIONS REFERENCE TO JEDEC MS-026 Rev.D, except D2 and E2 ④

- ര

- 6 7

LF Ref# Symbol Min Nom Max 5.03 5.13 D2 4.93 L - 16 - 090064.93 5.03 5.13 E2

<u>B</u> /1

: 20:1

DETAIL SCALE

# Appendices

# A Configuration of the XS1

The device is configured through three banks of registers, as shown in Figure 27.

Figure 27: Registers

> The following communication sequences specify how to access those registers. Any messages transmitted contain the most significant 24 bits of the channel-end to which a response is to be sent. This comprises the node-identifier and the channel number within the node. if no response is required on a write operation, supply 24-bits with the last 8-bits set, which suppresses the reply message. Any multi-byte data is sent most significant byte first.

#### A.1 Accessing a processor status register

The processor status registers are accessed directly from the processor instruction set. The instructions GETPS and SETPS read and write a word. The register number should be translated into a processor-status resource identifier by shifting the register number left 8 places, and ORing it with 0x0C. Alternatively, the functions getps(reg) and setps(reg,value) can be used from XC.

#### A.2 Accessing an xCORE Tile configuration register

xCORE Tile configuration registers can be accessed through the interconnect using the functions write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tile  $\rightarrow$  ref, ...), where tileref is the name of the xCORE Tile, e.g. tile[1]. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the xCORE tile configuration registers. The destination of the channel-end should be set to 0xnnnnC20C where nnnnn is the tile-identifier.

A write message comprises the following:

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

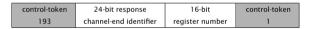

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to the read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.3 Accessing node configuration

Node configuration registers can be accessed through the interconnect using the functions write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...), where device is the name of the node. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the node configuration registers. The destination of the channel-end should be set to 0xnnnnC30C where nnnn is the node-identifier.

A write message comprises the following:

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

The response to a read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

$-X \wedge () >$

#### B.1 RAM base address: 0x00

This register contains the base address of the RAM. It is initialized to 0x00010000.

**0x00**: RAM base address

| 00: | Bits | Perm | Init | Description                                |

|-----|------|------|------|--------------------------------------------|

| ase | 31:2 | RW   |      | Most significant 16 bits of all addresses. |

| ess | 1:0  | RO   | -    | Reserved                                   |

#### B.2 Vector base address: 0x01

Base address of event vectors in each resource. On an interrupt or event, the 16 most significant bits of the destination address are provided by this register; the least significant 16 bits come from the event vector.

0x01: Vector base address

| -<br> : | Bits  | Perm | Init | Description                                                    |

|---------|-------|------|------|----------------------------------------------------------------|

| e       | 31:16 | RW   |      | The most significant bits for all event and interrupt vectors. |

| S       | 15:0  | RO   | -    | Reserved                                                       |

### B.3 xCORE Tile control: 0x02

Register to control features in the xCORE tile

| Bits | Perm | Init | Description                                                                                                                                                                                                                                             |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:6 | RO   | -    | Reserved                                                                                                                                                                                                                                                |

| 5    | RW   | 0    | Set to 1 to select the dynamic mode for the clock divider when<br>the clock divider is enabled. In dynamic mode the clock divider is<br>only activated when all active logical cores are paused. In static<br>mode the clock divider is always enabled. |

| 4    | RW   | 0    | Set to 1 to enable the clock divider. This slows down the xCORE tile clock in order to use less power.                                                                                                                                                  |

| 3:0  | RO   | -    | Reserved                                                                                                                                                                                                                                                |

0x02: xCORE Tile control

# B.4 xCORE Tile boot status: 0x03

This read-only register describes the boot status of the xCORE tile.

-XMOS

| Bits  | Perm | Init | Description                                                                                                                                                                                                                                       |  |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                                          |  |

| 17:16 | DRW  |      | If the debug interrupt was caused by a hardware breakpoint<br>or hardware watchpoint, this field contains the number of the<br>breakpoint or watchpoint. If multiple breakpoints or watch-<br>points trigger at once, the lowest number is taken. |  |

| 15:8  | DRW  |      | If the debug interrupt was caused by a logical core, this field contains the number of that core. Otherwise this field is 0.                                                                                                                      |  |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                                          |  |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt<br>1: Host initiated a debug interrupt through JTAG<br>2: Program executed a DCALL instruction<br>3: Instruction breakpoint<br>4: Data watch point<br>5: Resource watch point                          |  |

**0x15:** Debug interrupt type

### B.17 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

0x16 Debug interrupt data

| <b>0x16:</b><br>Debug | Bits | Perm | Init | Description |

|-----------------------|------|------|------|-------------|

| ot data               | 31:0 | DRW  |      | Value.      |

#### B.18 Debug core control: 0x18

This register enables the debugger to temporarily disable logical cores. When returning from the debug interrupts, the cores set in this register will not execute. This enables single stepping to be implemented.

**0x18:** Debug core control

| Bits | Perm | Init | Description                                                                                                                                                   |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO   | -    | Reserved                                                                                                                                                      |

| 7:0  | DRW  |      | 1-hot vector defining which logical cores are stopped when not<br>in debug mode. Every bit which is set prevents the respective<br>logical core from running. |

-XMOS

0x50 .. 0x53: Data watchpoint address 1

| Data<br>Ipoint | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ess 1          | 31:0 | DRW  |      | Value.      |

#### B.23 Data watchpoint address 2: 0x60 ... 0x63

This set of registers contains the second address for the four data watchpoints.

0x60 .. 0x63: Data watchpoint address 2

| ata<br>Dint | Bits | Perm | Init | Description |

|-------------|------|------|------|-------------|

| s 2         | 31:0 | DRW  |      | Value.      |

#### B.24 Data breakpoint control register: 0x70 .. 0x73

This set of registers controls each of the four data watchpoints.

|             | Bits  | Perm | Init | Description                                                                                                                                                                                                                                                                                       |  |

|-------------|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             | 31:24 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                          |  |

|             | 23:16 | DRW  | 0    | A bit for each logical core in the tile allowing the breakpoint to be enabled individually for each logical core.                                                                                                                                                                                 |  |

|             | 15:3  | RO   | -    | Reserved                                                                                                                                                                                                                                                                                          |  |

|             | 2     | DRW  | 0    | Set to 1 to enable breakpoints to be triggered on loads. Breakpoints always trigger on stores.                                                                                                                                                                                                    |  |

| a<br>t<br>l | 1     | DRW  | 0    | By default, data watchpoints trigger if memory in the range [Address1Address2] is accessed (the range is inclusive of Address1 and Address2). If set to 1, data watchpoints trigger if memory outside the range (Address2Address1) is accessed (the range is exclusive of Address2 and Address1). |  |

| r           | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                                                                                                                                     |  |

0x70 .. 0x73: Data breakpoint control register

#### B.25 Resources breakpoint mask: 0x80 .. 0x83

This set of registers contains the mask for the four resource watchpoints.

-XMOS

35

# C Tile Configuration

The xCORE Tile control registers can be accessed using configuration reads and writes (use write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tileref, ...) for reads and writes).

| Number    | Perm | Description                                    |  |  |

|-----------|------|------------------------------------------------|--|--|

| 0x00      | RO   | Device identification                          |  |  |

| 0x01      | RO   | xCORE Tile description 1                       |  |  |

| 0x02      | RO   | xCORE Tile description 2                       |  |  |

| 0x04      | CRW  | Control PSwitch permissions to debug registers |  |  |

| 0x05      | CRW  | Cause debug interrupts                         |  |  |

| 0x06      | RW   | xCORE Tile clock divider                       |  |  |

| 0x07      | RO   | Security configuration                         |  |  |

| 0x100x13  | RO   | PLink status                                   |  |  |

| 0x200x27  | CRW  | Debug scratch                                  |  |  |

| 0x40      | RO   | PC of logical core 0                           |  |  |

| 0x41      | RO   | PC of logical core 1                           |  |  |

| 0x42      | RO   | PC of logical core 2                           |  |  |

| 0x43      | RO   | PC of logical core 3                           |  |  |

| 0x44      | RO   | PC of logical core 4                           |  |  |

| 0x45      | RO   | PC of logical core 5                           |  |  |

| 0x60      | RO   | SR of logical core 0                           |  |  |

| 0x61      | RO   | SR of logical core 1                           |  |  |

| 0x62      | RO   | SR of logical core 2                           |  |  |

| 0x63      | RO   | SR of logical core 3                           |  |  |

| 0x64      | RO   | SR of logical core 4                           |  |  |

| 0x65      | RO   | SR of logical core 5                           |  |  |

| 0x80 0x9F | RO   | Chanend status                                 |  |  |

-XMOS

Figure 29:

# D Node Configuration

The digital node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...) for reads and writes).

| Number    | Perm | Description                           |  |

|-----------|------|---------------------------------------|--|

| 0x00      | RO   | Device identification                 |  |

| 0x01      | RO   | System switch description             |  |

| 0x04      | RW   | Switch configuration                  |  |

| 0x05      | RW   | Switch node identifier                |  |

| 0x06      | RW   | PLL settings                          |  |

| 0x07      | RW   | System switch clock divider           |  |

| 0x08      | RW   | Reference clock                       |  |

| 0x0C      | RW   | Directions 0-7                        |  |

| 0x0D      | RW   | Directions 8-15                       |  |

| 0x10      | RW   | DEBUG_N configuration                 |  |

| 0x1F      | RO   | Debug source                          |  |

| 0x20 0x27 | RW   | Link status, direction, and network   |  |

| 0x40 0x43 | RW   | PLink status and network              |  |

| 0x80 0x87 | RW   | Link configuration and initialization |  |

| 0xA0 0xA7 | RW   | Static link configuration             |  |

Figure 30: Summary

# D.1 Device identification: 0x00

This register contains version and revision identifiers and the mode-pins as sampled at boot-time.

|                | Bits  | Perm | Init | Description                                    |

|----------------|-------|------|------|------------------------------------------------|

|                | 31:24 | RO   | 0x00 | Chip identifier.                               |

| 0x00:          | 23:16 | RO   |      | Sampled values of pins MODE0, MODE1, on reset. |

| Device         | 15:8  | RO   |      | SSwitch revision.                              |

| identification | 7:0   | RO   |      | SSwitch version.                               |

# D.2 System switch description: 0x01

This register specifies the number of processors and links that are connected to this switch.

-XMOS

|                        | Bits  | Perm | Init | Description                                        |

|------------------------|-------|------|------|----------------------------------------------------|

|                        | 31:24 | RO   | -    | Reserved                                           |

| <b>0x01:</b><br>System | 23:16 | RO   |      | Number of links on the switch.                     |

| switch                 | 15:8  | RO   |      | Number of cores that are connected to this switch. |

| description            | 7:0   | RO   |      | Number of links per processor.                     |

#### D.3 Switch configuration: 0x04

This register enables the setting of two security modes (that disable updates to the PLL or any other registers) and the header-mode.

| Bits | Perm | Init | Description                                                                                        |  |

|------|------|------|----------------------------------------------------------------------------------------------------|--|

| 31   | RO   | 0    | Set to 1 to disable any write access to the configuration registers in this switch.                |  |

| 30:9 | RO   | -    | Reserved                                                                                           |  |

| 8    | RO   | 0    | Set to 1 to disable updates to the PLL configuration register.                                     |  |

| 7:1  | RO   | -    | Reserved                                                                                           |  |

| 0    | RO   | 0    | Header mode. Set to 1 to enable 1-byte headers. This must be performed on all nodes in the system. |  |

**0x04:** Switch configuration

### D.4 Switch node identifier: 0x05

This register contains the node identifier.

0x05 Switch node identifier

|               | Bits  | Perm | Init | Description                                                                                                                            |

|---------------|-------|------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| -             | 31:16 | RO   | -    | Reserved                                                                                                                               |

| 5:<br>e<br>er | 15:0  | RW   | 0    | The unique 16-bit ID of this node. This ID is matched most-<br>significant-bit first with incoming messages for routing pur-<br>poses. |

### D.5 PLL settings: 0x06

An on-chip PLL multiplies the input clock up to a higher frequency clock, used to clock the I/O, processor, and switch, see Oscillator. Note: a write to this register will cause the tile to be reset.

-XMOS-

45

| Bits  | Perm | Init | Description                                                                            |

|-------|------|------|----------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                               |

| 25:23 | RW   |      | OD: Output divider value<br>The initial value depends on pins MODE0 and MODE1.         |

| 22:21 | RO   | -    | Reserved                                                                               |

| 20:8  | RW   |      | F: Feedback multiplication ratio<br>The initial value depends on pins MODE0 and MODE1. |

| 7     | RO   | -    | Reserved                                                                               |

| 6:0   | RW   |      | R: Oscilator input divider value<br>The initial value depends on pins MODE0 and MODE1. |

0x06: PLL settings

### D.6 System switch clock divider: 0x07

Sets the ratio of the PLL clock and the switch clock.

**0x07** System switch clock divider

| 07:        | Bits  | Perm | Init | Description                                                                                            |

|------------|-------|------|------|--------------------------------------------------------------------------------------------------------|

| em         | 31:16 | RO   | -    | Reserved                                                                                               |

| ock<br>der | 15:0  | RW   | 0    | Switch clock divider. The PLL clock will be divided by this value plus one to derive the switch clock. |

### D.7 Reference clock: 0x08

Sets the ratio of the PLL clock and the reference clock used by the node.

**0x08:** Reference clock

| Bits  | Perm | Init | Description                                                                                                                       |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                                                          |

| 15:0  | RW   | 3    | Architecture reference clock divider. The PLL clock will be divided by this value plus one to derive the 100 MHz reference clock. |

# D.8 Directions 0-7: 0x0C

This register contains eight directions, for packets with a mismatch in bits 7..0 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

#### D.13 PLink status and network: 0x40 .. 0x43

These registers contain status information and the network number that each processor-link belongs to.

| Bits  | Perm | Init | Description                                                                                                                                                                              |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                 |

| 25:24 | RO   |      | If this link is currently routing data into the switch, this field<br>specifies the type of link that the data is routed to:<br>0: plink<br>1: external link<br>2: internal control link |

| 23:16 | RO   | 0    | If the link is routing data into the switch, this field specifies the destination link number to which all tokens are sent.                                                              |

| 15:6  | RO   | -    | Reserved                                                                                                                                                                                 |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, set for quality of service.                                                                                                           |

| 3     | RO   | -    | Reserved                                                                                                                                                                                 |

| 2     | RO   | 0    | Set to 1 if the current packet is junk and being thrown away. A packet is considered junk if, for example, it is not routable.                                                           |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                                                                                           |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch.                                                                           |

0x40 .. 0x43: PLink status and network

### D.14 Link configuration and initialization: 0x80 .. 0x87

-XMOS<sup>®</sup>

These registers contain configuration and debugging information specific to external links. The link speed and width can be set, the link can be initialized, and the link status can be monitored. The registers control links C, D, A, B, G, H, E, and F in that order. Pins MODE0 and MODE1 are set to the correct value for the chosen oscillator frequency. The MODE settings are shown in the Oscillator section, Section 6. If you have a choice between two values, choose the value with the highest multiplier ratio since that will boot faster.

#### H.5 USB ULPI Mode

This section can be skipped if you do not have an external USB PHY.

- □ If using ULPI, the ULPI signals are connected to specific ports as shown in Section E.

- □ If using ULPI, the ports that are used internally are not connected, see Section E. (Note that this limitation only applies when the ULPI is enabled, they can still be used before or after the ULPI is being used.)

#### H.6 Boot

- □ The device is connected to a SPI flash for booting, connected to X0D0, X0D01, X0D10, and X0D11 (Section 7). If not, you must boot the device through OTP or JTAG.

- □ The device that is connected to flash has both MODE2 and MODE3 connected to pin 3 on the xSYS Header (MSEL). If no debug adapter connection is supported (not recommended) MODE2 and MODE3 are to be left NC (Section 7).

- ☐ The SPI flash that you have chosen is supported by **xflash**, or you have created a specification file for it.

#### H.7 JTAG, XScope, and debugging

- $\Box$  You have decided as to whether you need an XSYS header or not (Section G)

- □ If you included an XSYS header, you connected pin 3 to any MODE2/MODE3 pin that would otherwise be NC (Section G).

- ☐ If you have not included an XSYS header, you have devised a method to program the SPI-flash or OTP (Section G).

#### H.8 GPIO

You have not mapped both inputs and outputs to the same multi-bit port.