#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                         |                                                                       |

|---------------------------------|-----------------------------------------------------------------------|

| Product Status                  | Obsolete                                                              |

| Core Processor                  | PowerPC G4                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 400MHz                                                                |

| Co-Processors/DSP               | -                                                                     |

| RAM Controllers                 | -                                                                     |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | -                                                                     |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 360-BCBGA, FCCBGA                                                     |

| Supplier Device Package         | 360-CBGA (25x25)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc7410vu400le |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- The MPC7410 is implemented in a next generation process technology for core frequency improvement.

- The MPC7410 floating-point unit has been improved to make latency equal for double- and single-precision operations involving multiplication.

- The completion queue has been extended to eight slots.

- There are no other significant changes to scalar pipelines, decode/dispatch/completion mechanisms, or the branch unit. The MPC750 four-stage pipeline model is unchanged (fetch, decode/dispatch, execute, complete/writeback).

Some comments on the MPC7410 with respect to the MPC7400:

- The MPC7410 adds configurable direct-mapped SRAM capability to the L2 cache interface.

- The MPC7410 adds 32-bit interface support to the L2 cache interface. The MPC7410 implements a 19th L2 address pin (L2ASPARE on the MPC7400) in order to support additional address range.

- The MPC7410 removes support for 3.3-V I/O on the L2 cache interface.

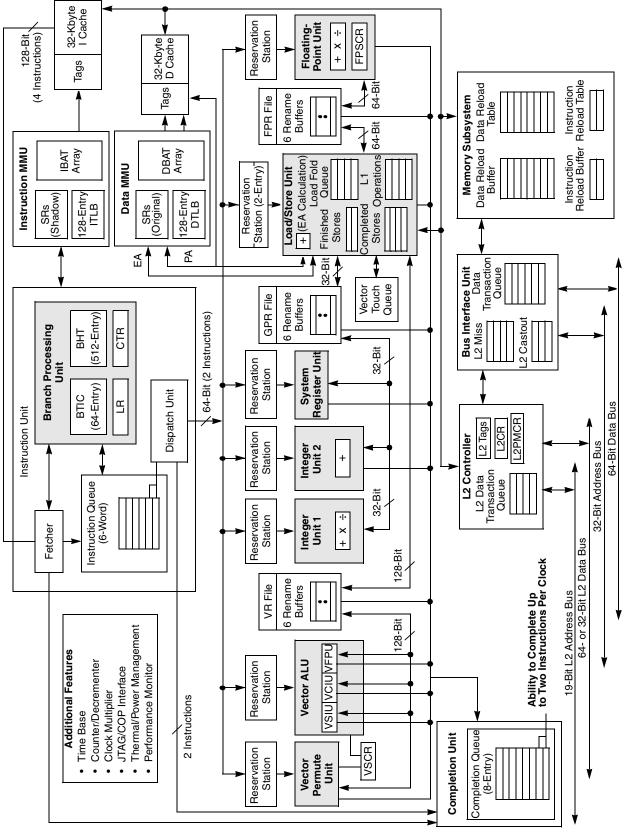

Figure 1 shows a block diagram of the MPC7410.

# 2 Features

This section summarizes features of the MPC7410 implementation of the PowerPC architecture. Major features of the MPC7410 are as follows:

- Branch processing unit

- Four instructions fetched per clock

- One branch processed per cycle (plus resolving two speculations)

- Up to one speculative stream in execution, one additional speculative stream in fetch

- 512-entry branch history table (BHT) for dynamic prediction

- 64-entry, four-way set-associative branch target instruction cache (BTIC) for eliminating branch delay slots

- Dispatch unit

- Full hardware detection of dependencies (resolved in the execution units)

- Dispatch two instructions to eight independent units (system, branch, load/store, fixed-point unit 1, fixed-point unit 2, floating-point, AltiVec permute, AltiVec ALU)

- Serialization control (predispatch, postdispatch, execution serialization)

Figure 1. MPC7410 Block Diagram

Features

- Decode

- Register file access

- Forwarding control

- Partial instruction decode

- Completion

- Eight-entry completion buffer

- Instruction tracking and peak completion of two instructions per cycle

- Completion of instructions in program order while supporting out-of-order instruction execution, completion serialization, and all instruction flow changes

- Fixed point units (FXUs) that share 32 GPRs for integer operands

- Fixed point unit 1 (FXU1)—multiply, divide, shift, rotate, arithmetic, logical

- Fixed point unit 2 (FXU2)—shift, rotate, arithmetic, logical

- Single-cycle arithmetic, shifts, rotates, logical

- Multiply and divide support (multi-cycle)

- Early out multiply

- Three-stage floating-point unit and a 32-entry FPR file

- Support for IEEE Std 754<sup>™</sup> single- and double-precision floating-point arithmetic

- Three-cycle latency, one-cycle throughput (single- or double-precision)

- Hardware support for divide

- Hardware support for denormalized numbers

- Time deterministic non-IEEE mode

- System unit

- Executes CR logical instructions and miscellaneous system instructions

- Special register transfer instructions

- AltiVec unit

- Full 128-bit data paths

- Two dispatchable units: vector permute unit and vector ALU unit.

- Contains its own 32-entry, 128-bit vector register file (VRF) with 6 renames

- The vector ALU unit is further subdivided into the vector simple integer unit (VSIU), the vector complex integer unit (VCIU), and the vector floating-point unit (VFPU).

- Fully pipelined

- Load/store unit

- One-cycle load or store cache access (byte, half word, word, double word)

- Two-cycle load latency with 1-cycle throughput

- Effective address generation

- Hits under misses (multiple outstanding misses)

- Single-cycle unaligned access within double-word boundary

- Alignment, zero padding, sign extend for integer register file

- Floating-point internal format conversion (alignment, normalization)

- Sequencing for load/store multiples and string operations

- Store gathering

- Executes the cache and TLB instructions

- Big- and little-endian byte addressing supported

- Misaligned little-endian supported

- Supports FXU, FPU, and AltiVec load/store traffic

- Complete support for all four architecture AltiVec DST streams

- Level 1 (L1) cache structure

- 32 Kbyte, 32-byte line, eight-way set-associative instruction cache (iL1)

- 32 Kbyte, 32-byte line, eight-way set-associative data cache (dL1)

- Single-cycle cache access

- Pseudo least-recently-used (LRU) replacement

- Data cache supports AltiVec LRU and transient instructions algorithm

- Copy-back or write-through data cache (on a page-per-page basis)

- Supports all PowerPC memory coherency modes

- Nonblocking instruction and data cache

- Separate copy of data cache tags for efficient snooping

- No snooping of instruction cache except for ICBI instruction

- Level 2 (L2) cache interface

- Internal L2 cache controller and tags; external data SRAMs

- 512-Kbyte, 1-Mbyte, and 2-Mbyte two-way set-associative L2 cache support

- Copy-back or write-through data cache (on a page basis, or for all L2)

- 32-byte (512-Kbyte), 64-byte (1-Mbyte), or 128-byte (2-Mbyte) sectored line size

- Supports pipelined (register-register) synchronous BurstRAMs and pipelined (register-register) late write synchronous BurstRAMs

- Supports direct-mapped mode for 256 Kbytes, 512 Kbytes, 1 Mbyte, or 2 Mbytes of SRAM (either all, half, or none of L2 SRAM must be configured as direct-mapped)

- Core-to-L2 frequency divisors of  $\div 1$ ,  $\div 1.5$ ,  $\div 2$ ,  $\div 2.5$ ,  $\div 3$ ,  $\div 3.5$ , and  $\div 4$  supported

- 64-bit data bus which also supports 32-bit bus mode

- Selectable interface voltages of 1.8 and 2.5 V

- Memory management unit

- 128-entry, two-way set-associative instruction TLB

- 128-entry, two-way set-associative data TLB

- Hardware reload for TLBs

- Four instruction BATs and four data BATs

- Virtual memory support for up to 4 hexabytes  $(2^{52})$  of virtual memory

- Real memory support for up to 4 gigabytes  $(2^{32})$  of physical memory

- Snooped and invalidated for TLBI instructions

- Efficient data flow

- All data buses between VRF, load/store unit, dL1, iL1, L2, and the bus are 128 bits wide

- dL1 is fully pipelined to provide 128 bits/cycle to/from the VRF

Features

- L2 is fully pipelined to provide 128 bits per L2 clock cycle to the L1s.

- Up to eight outstanding, out-of-order, cache misses between dL1 and L2/bus

- Up to seven outstanding, out-of-order transactions on the bus

- Load folding to fold new dL1 misses into older, outstanding load and store misses to the same line

- Store miss merging for multiple store misses to the same line. Only coherency action taken (that is, address only) for store misses merged to all 32 bytes of a cache line (no data tenure needed).

- Two-entry finished store queue and four-entry completed store queue between load/store unit and dL1

- Separate additional queues for efficient buffering of outbound data (castouts, write throughs, and so on) from dL1 and L2

- Bus interface

- MPX bus extension to 60x processor interface

- Mode-compatible with 60x processor interface

- 32-bit address bus

- 64-bit data bus

- Bus-to-core frequency multipliers of 2x, 2.5x, 3x, 3.5x, 4x, 4.5x, 5x, 5.5x, 6x, 6.5x, 7x, 7.5x, 8x, 9x supported

- Selectable interface voltages of 1.8, 2.5, and 3.3 V

- Power management

- Low-power design with thermal requirements very similar to MPC740 and MPC750

- Low-voltage processor core

- Selectable interface voltages can reduce power in output buffers

- Three static power saving modes: doze, nap, and sleep

- Dynamic power management

- Testability

- LSSD scan design

- IEEE Std 1149.1<sup>™</sup> JTAG interface

- Array built-in self test (ABIST)—factory test only

- Redundancy on L1 data arrays and L2 tag arrays

- Reliability and serviceability

- Parity checking on 60x and L2 cache buses

#### **Electrical and Thermal Characteristics**

| Characteristic               |                                             | Symbol             | Recommended<br>Value      | Unit | Notes |

|------------------------------|---------------------------------------------|--------------------|---------------------------|------|-------|

| Core supply voltage          |                                             | V <sub>DD</sub>    | 1.8 V ± 100 mV            | V    | —     |

| PLL supply voltage           |                                             | AV <sub>DD</sub>   | 1.8 V ± 100 mV            | V    | —     |

| L2 DLL supply voltage        |                                             | L2AV <sub>DD</sub> | 1.8 V ± 100 mV            | V    | —     |

| Processor bus supply voltage | BVSEL = 0                                   | OV <sub>DD</sub>   | 1.8 V ± 100 mV            | V    | —     |

|                              | BVSEL = HRESET                              | OV <sub>DD</sub>   | 2.5 V ± 100 mV            | V    | —     |

|                              | BVSEL = ¬ <del>HRESET</del> or<br>BVSEL = 1 | OV <sub>DD</sub>   | 3.3 V ± 165 mV            | V    | 2, 3  |

| L2 bus supply voltage        | L2VSEL = 0                                  | L2OV <sub>DD</sub> | 1.8 V ± 100 mV            | V    | —     |

|                              | L2VSEL = HRESET or<br>L2VSEL = 1            | L2OV <sub>DD</sub> | 2.5 V ± 100 mV            | V    |       |

| Input voltage                | Processor bus and JTAG signals              | V <sub>in</sub>    | GND to OV <sub>DD</sub>   | V    | —     |

|                              | L2 bus                                      | V <sub>in</sub>    | GND to L2OV <sub>DD</sub> | V    | —     |

| Die-junction temperature     | •                                           | Тј                 | 0 to 105                  | °C   | —     |

# Table 3. Recommended Operating Conditions <sup>1</sup>

#### Notes:

1. These are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

2. Mxx7410xxnnnLE (Rev. 1.4) and later only. Previous revisions do not support 3.3 V OV<sub>DD</sub> and have a recommended OV<sub>DD</sub> value of 2.5 V ± 100 mV for BVSEL = 1.

3. Mxx7410xxnnnLE (Rev. 1.4) and later only. Previous revisions do not support BVSEL =  $\neg$ HRESET.

Table 4 provides the package thermal characteristics for the MPC7410.

**Table 4. Package Thermal Characteristics**

|                                                                                     |                   | Va              | lue             |      | Notes |

|-------------------------------------------------------------------------------------|-------------------|-----------------|-----------------|------|-------|

| Characteristic                                                                      | Symbol            | MPC7410<br>CBGA | MPC7410<br>HCTE | Unit |       |

| Junction-to-ambient thermal resistance, natural convection, four-layer (2s2p) board | R <sub>θJMA</sub> | 18              | 20              | °C/W | 1, 2  |

| Junction-to-ambient thermal resistance, 1m/sec airflow, four-layer (2s2p) board     | R <sub>θJMA</sub> | 14              | 16              | °C/W | 1, 2  |

| Junction-to-ambient thermal resistance, 2m/sec airflow, four-layer (2s2p) board     | R <sub>θJMA</sub> | 13              | 15              | °C/W | 1, 2  |

| Junction-to-board thermal resistance                                                | $R_{	hetaJB}$     | 9               | 11              | °C/W | 3     |

#### **Electrical and Thermal Characteristics**

### Table 5. DC Electrical Specifications (continued)

At recommended operating conditions (see Table 3)

| Characteristic                                | Nominal<br>Bus<br>Voltage <sup>1</sup> | Symbol           | Min                         | Мах  | Unit | Notes   |

|-----------------------------------------------|----------------------------------------|------------------|-----------------------------|------|------|---------|

| High-Z (off-state) leakage current,           | 1.8                                    | I <sub>TSI</sub> | —                           | 20   | μA   | 2, 3,   |

| $V_{in} = L2OV_{DD}/OV_{DD}$                  | 2.5                                    | I <sub>TSI</sub> | —                           | 35   |      | 5, 7    |

|                                               | 3.3                                    | I <sub>TSI</sub> | —                           | 70   |      |         |

| Output high voltage, I <sub>OH</sub> = -5 mA  | 1.8                                    | V <sub>OH</sub>  | (L2)OV <sub>DD</sub> - 0.45 | _    | V    | 8       |

|                                               | 2.5                                    | V <sub>OH</sub>  | 1.7                         | _    |      |         |

|                                               | 3.3                                    | V <sub>OH</sub>  | 2.4                         | _    |      |         |

| Output low voltage, I <sub>OL</sub> = 5 mA    | 1.8                                    | V <sub>OL</sub>  | —                           | 0.45 | V    | 8       |

|                                               | 2.5                                    | V <sub>OL</sub>  | _                           | 0.4  |      |         |

|                                               | 3.3                                    | V <sub>OL</sub>  | —                           | 0.4  |      |         |

| Capacitance, V <sub>in</sub> = 0 V, f = 1 MHz |                                        | C <sub>in</sub>  | —                           | 6.0  | pF   | 3, 4, 7 |

#### Notes:

- 1. Nominal voltages; see Table 3 for recommended operating conditions.

- 2. For processor bus signals, the reference is OV<sub>DD</sub> while L2OV<sub>DD</sub> is the reference for the L2 bus signals.

- 3. Excludes factory test signals.

- 4. Capacitance is periodically sampled rather than 100% tested.

- 5. The leakage is measured for nominal OV<sub>DD</sub> and L2OV<sub>DD</sub>, or both OV<sub>DD</sub> and L2OV<sub>DD</sub> must vary in the same direction (for example, both OV<sub>DD</sub> and L2OV<sub>DD</sub> vary by either +5% or -5%).

- 6. Measured at max OV<sub>DD</sub>/L2OV<sub>DD</sub>.

- 7. Excludes IEEE 1149.1 boundary scan (JTAG) signals.

- 8. For JTAG support: all signals controlled by BVSEL and L2VSEL will see V<sub>IL</sub>/V<sub>IH</sub>/V<sub>OL</sub>/V<sub>OH</sub>/CV<sub>IH</sub>/CV<sub>IL</sub> DC limits of 1.8 V mode while either the EXTEST or CLAMP instruction is loaded into the IEEE 1149.1 instruction register by the UpdateIR TAP state until a different instruction is loaded into the instruction register by either another UpdateIR or a Test-Logic-Reset TAP state. If only TSRT is asserted to the part, and then a SAMPLE instruction is executed, there is no way to control or predict what the DC voltage limits are. If HRESET is asserted before executing a SAMPLE instruction, the DC voltage limits will be controlled by the BVSEL/L2VSEL settings during HRESET. Anytime HRESET is not asserted (that is, just asserting TRST), the voltage mode is not known until either EXTEST or CLAMP is executed, at which time the voltage level will be at the DC limits of 1.8 V.

# 4.2.2 Processor Bus AC Specifications

Table 8 provides the processor bus AC timing specifications for the MPC7410 as defined in Figure 4 and Figure 5. Timing specifications for the L2 bus are provided in Section 4.2.3, "L2 Clock AC Specifications."

# Table 8. Processor Bus AC Timing Specifications <sup>1</sup>

At recommended operating conditions (see Table 3)

| Parameter St                                                                                    |                                                               | 400, 450, 500 MHz |                   | Unit                | Notes   |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------|-------------------|---------------------|---------|

| Farameter                                                                                       | Symbol <sup>2</sup>                                           | Min               | Мах               | Onic                | NOICES  |

| Input setup                                                                                     | t <sub>IVKH</sub>                                             | 1.0               | —                 | ns                  | 4       |

| Input hold                                                                                      | t <sub>IXKH</sub>                                             | 0                 | —                 | ns                  | 4       |

| Output valid times:<br>ARTRY, SHD0, SHD1<br>All other outputs                                   | <sup>t</sup> кнтsv<br><sup>t</sup> кнаrv<br><sup>t</sup> кноv |                   | 3.0<br>2.3<br>3.0 | ns                  | 5, 6    |

| Output hold times:<br>ARTRY, SHD0, SHD1<br>All other outputs                                    | <sup>t</sup> кнтsx<br><sup>t</sup> кнаrx<br><sup>t</sup> кнох | 0.5<br>0.5<br>0.5 | <br>              | ns                  | 5       |

| SYSCLK to output enable                                                                         | t <sub>KHOE</sub>                                             | 0.5               | —                 | ns                  | 9       |

| SYSCLK to output high impedance (all except ABB/AMON(0),<br>ARTRY/SHD, DBB/DMON(0), SHD0, SHD1) | t <sub>KHOZ</sub>                                             | —                 | 3.5               | ns                  |         |

| SYSCLK to ABB/AMON(0), DBB/DMON(0) high impedance after precharge                               | t <sub>KHABPZ</sub>                                           | _                 | 1                 | t <sub>SYSCLK</sub> | 3, 7, 9 |

| Maximum delay to ARTRY, SHD0, SHD1 precharge                                                    | t <sub>KHARP</sub>                                            |                   | 1                 | t <sub>SYSCLK</sub> | 3, 8, 9 |

#### **Electrical and Thermal Characteristics**

## Table 8. Processor Bus AC Timing Specifications <sup>1</sup> (continued)

At recommended operating conditions (see Table 3)

| Parameter                                                  | Symbol <sup>2</sup> | 400, 450, 500 MHz |     | Unit                | Notes   |

|------------------------------------------------------------|---------------------|-------------------|-----|---------------------|---------|

| i arameter                                                 | Symbol              | Min               | Мах | Onit                | Notes   |

| SYSCLK to ARTRY, SHD0, SHD1 high impedance after precharge | t <sub>KHARPZ</sub> | —                 | 2   | t <sub>SYSCLK</sub> | 3, 8, 9 |

#### Notes:

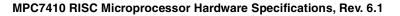

- All input specifications are measured from the midpoint of the signal in question to the midpoint of the rising edge of the input SYSCLK. All output specifications are measured from the midpoint of the rising edge of SYSCLK to the midpoint of the signal in question. All output timings assume a purely resistive 50-Ω load (see Figure 4). Input and output timings are measured at the pin; time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbology used for timing specifications herein follows the pattern of t<sub>(signal)(state)(reference)(state)</sub> for inputs and t<sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>IVKH</sub> symbolizes the time input signals (I) reach the valid state (V) relative to the SYSCLK reference (K) going to the high (H) state or input setup time. And t<sub>KHOV</sub> symbolizes the time from SYSCLK(K) going high (H) until outputs (O) are valid (V) or output valid time. Input hold time can be read as the time that the input signal (I) went invalid (X) with respect to the rising clock edge (KH)— note the position of the reference and its state for inputs—and output hold time can be read as the time from the rising edge (KH) until the output went invalid (OX).

- 3. t<sub>SYSCLK</sub> is the period of the external clock (SYSCLK) in ns. The numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in ns) of the parameter in question.

- 4. Includes mode select signals: BVSEL, EMODE, L2VSEL. See Figure 5 for mode select timing with respect to HRESET.

- 5. All other output signals are composed of the following— A[0:31], AP[0:3], TT[0:4], TS, TBST, TSIZ[0:2], GBL, WT, CI, DH[0:31], DL[0:31], DP[0:7], BR, CKSTP\_OUT, DRDY, HIT, QREQ, RSRV.

- 6. Output valid time is measured from 2.4 to 0.8 V which may be longer than the time required to discharge from V<sub>DD</sub> to 0.8 V.

- 7. According to the 60x bus protocol, ABB and DBB are driven only by the currently active bus master. They are asserted low then precharged high before returning to high-Z as shown in Figure 6. The nominal precharge width for ABB or DBB is 0.5 × t<sub>SYSCLK</sub>, that is, less than the minimum t<sub>SYSCLK</sub> period, to ensure that another master asserting ABB, or DBB on the following clock will not contend with the precharge. Output valid and output hold timing is tested for the signal asserted. Output valid time is tested for precharge. The high-Z behavior is guaranteed by design.

- 8. According to the 60x bus protocol, ARTRY can be driven by multiple bus masters through the clock period immediately following AACK. Bus contention is not an issue since any master asserting ARTRY will be driving it low. Any master asserting it low in the first clock following AACK will then go to high-Z for one clock before precharging it high during the second cycle after the assertion of AACK. The nominal precharge width for ARTRY is 1.0 t<sub>SYSCLK</sub>; that is, it should be high-Z as shown in Figure 6 before the first opportunity for another master to assert ARTRY. Output valid and output hold timing are tested for the signal asserted. Output valid time is tested for precharge. The high-Z behavior is guaranteed by design.

- 9. Guaranteed by design and not tested.

Figure 4 provides the AC test load for the MPC7410.

Figure 4. AC Test Load

**Electrical and Thermal Characteristics**

# 4.2.4 L2 Bus AC Specifications

Table 10 provides the L2 bus interface AC timing specifications for the MPC7410 as defined in Figure 8 and Figure 9 for the loading conditions described in Figure 10.

### Table 10. L2 Bus Interface AC Timing Specifications

At recommended operating conditions (see Table 3)

| Parameter                                                                                                                                                                        | Symbol                                  | 400, 450,                | 400, 450, 500 MHz        |        | Notes |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------|--------------------------|--------|-------|

| Farameter                                                                                                                                                                        | Symbol                                  | Min                      | Max                      | - Unit | Notes |

| L2SYNC_IN rise and fall time                                                                                                                                                     | $t_{\mbox{L2CR}}$ and $t_{\mbox{L2CF}}$ |                          | 1.0                      | ns     | 1     |

| Setup times: Data and parity                                                                                                                                                     | t <sub>DVL2CH</sub>                     | 1.5                      | —                        | ns     | 2     |

| Input hold times: Data and parity                                                                                                                                                | t <sub>DXL2CH</sub>                     |                          | 0.0                      | ns     | 2     |

| Valid times:<br>All outputs when L2CR[14–15] = 00<br>All outputs when L2CR[14–15] = 01<br>All outputs when L2CR[14–15] = 10<br>All outputs when L2CR[14–15] = 11                 | t <sub>l2CHOV</sub>                     | <br><br>                 | 2.5<br>2.5<br>2.9<br>3.5 | ns     | 3, 4  |

| Output hold times<br>All outputs when L2CR[14–15] = 00<br>All outputs when L2CR[14–15] = 01<br>All outputs when L2CR[14–15] = 10<br>All outputs when L2CR[14–15] = 11            | t <sub>L2CHOX</sub>                     | 0.4<br>0.8<br>1.2<br>1.6 | <br>                     | ns     | 3     |

| L2SYNC_IN to high impedance:<br>All outputs when L2CR[14–15] = 00<br>All outputs when L2CR[14–15] = 01<br>All outputs when L2CR[14–15] = 10<br>All outputs when L2CR[14–15] = 11 | t <sub>L2CHOZ</sub>                     | <br>                     | 2.0<br>2.5<br>3.0<br>3.5 | ns     | —     |

Notes:

1. Rise and fall times for the L2SYNC\_IN input are measured from 20% to 80% of L2OV\_DD.

2. All input specifications are measured from the midpoint of the signal in question to the midpoint voltage of the rising edge of the input L2SYNC\_IN (see Figure 8). Input timings are measured at the pins.

3. All output specifications are measured from the midpoint voltage of the rising edge of L2SYNC\_IN to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive  $50-\Omega$  load (see Figure 10).

4. The outputs are valid for both single-ended and differential L2CLK modes. For pipelined registered synchronous BurstRAMs, L2CR[14–15] = 00 is recommended. For pipelined late write synchronous BurstRAMs, L2CR[14–15] = 10 is recommended.

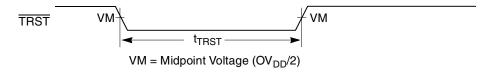

Figure 13 provides the  $\overline{\text{TRST}}$  timing diagram.

Figure 13. TRST Timing Diagram

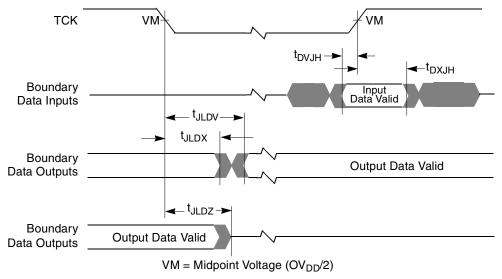

Figure 14 provides the boundary-scan timing diagram.

Figure 14. Boundary-Scan Timing Diagram

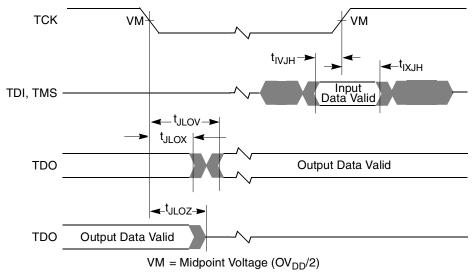

Figure 15 provides the test access port timing diagram.

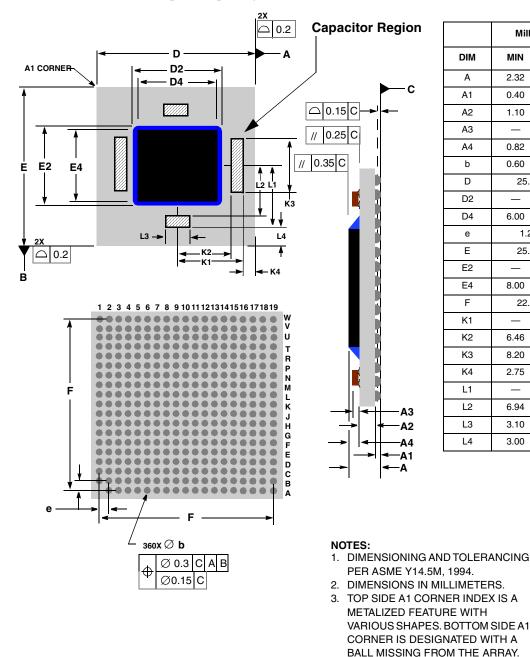

Millimeters

\_\_\_\_

MAX

2.80

0.60

1.30

0.60

0.90

0.90

12.50

9.00

14.30 11.00

9.75

8.60

\_

9.50

\_

3.30

\_

25.00 BSC

1.27 BSC

25.00 BSC

22.86 BSC

\_

\_

### Mechanical Dimensions for the MPC7410, 360 HCTE\_CBGA 7.4 (Lead Free C5 Spheres)

Figure 18 provides the mechanical dimensions and bottom surface nomenclature of the MPC7410, 360 HCTE\_CBGA (lead-free C5 spheres) package.

System Design Information

# 8.4 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level through a resistor. Unused active low inputs should be tied to  $OV_{DD}$ . Unused active high inputs should be connected to GND. All NC (no connect) signals must remain unconnected.

Power and ground connections must be made to all external  $V_{DD}$ ,  $OV_{DD}$ ,  $L2OV_{DD}$ , and GND pins of the MPC7410. Note that power must be supplied to  $L2OV_{DD}$  even if the L2 interface of the MPC7410 will not be used; the remainder of the L2 interface may be left unterminated.

# 8.5 Output Buffer DC Impedance

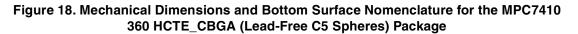

The MPC7410 60x and L2 I/O drivers are characterized over process, voltage, and temperature. To measure  $Z_0$ , an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 23).

The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held low, SW2 is closed (SW1 is open), and  $R_N$  is trimmed until the voltage at the pad equals (L2)OV<sub>DD</sub>/2.  $R_N$  then becomes the resistance of the pull-down devices. When data is held high, SW1 is closed (SW2 is open), and  $R_P$  is trimmed until the voltage at the pad equals (L2)OV<sub>DD</sub>/2.  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

Figure 23 describes the driver impedance measurement circuit described above.

Figure 23. Driver Impedance Measurement Circuit

Alternately, the following is another method to determine the output impedance of the MPC7410. A voltage source,  $V_{force}$ , is connected to the output of the MPC7410, as in Figure 24. Data is held low, the voltage source is set to a value that is equal to (L2)OV<sub>DD</sub>/2, and the current sourced by  $V_{force}$  is measured. The voltage drop across the pull-down device, which is equal to (L2)OV<sub>DD</sub>/2, is divided by the measured current to determine the output impedance of the pull-down device,  $R_N$ . Similarly, the impedance of the pull-up device is determined by dividing the voltage drop of the pull-up, (L2)OV<sub>DD</sub>/2, by the current sank by the pull-up when the data is high and  $V_{force}$  is equal to (L2)OV<sub>DD</sub>/2. This method can be employed with either empirical data from a test setup or with data from simulation models, such as IBIS.

#### **System Design Information**

The COP interface has a standard header for connection to the target system, based on the 0.025" square-post 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

There is no standardized way to number the COP header shown in Figure 25; consequently, many different pin numbers have been observed from emulator vendors. Some are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom, while still others number the pins counter clockwise from pin 1 (as with an IC). Regardless of the numbering, the signal placement recommended in Figure 25 is common to all known emulators.

The  $\overline{QACK}$  signal shown in Figure 25 is usually connected to the PCI bridge chip in a system and is an input to the MPC7410 informing it that it can go into the quiescent state. Under normal operation this occurs during a low-power mode selection. In order for COP to work, the MPC7410 must see this signal asserted (pulled down). While shown on the COP header, not all emulator products drive this signal. If the product does not, a pull-down resistor can be populated to assert this signal. Additionally, some emulator products implement open-drain type outputs and can only drive  $\overline{QACK}$  asserted; for these tools, a pull-up resistor can be implemented to ensure this signal is negated when it is not being driven by the tool. Note that the pull-up and pull-down resistors on the  $\overline{QACK}$  signal are mutually exclusive and it is never necessary to populate both in a system. To preserve correct power-down operation,  $\overline{QACK}$  should be merged via logic so that it also can be driven by the PCI bridge.

# 8.8 Thermal Management Information

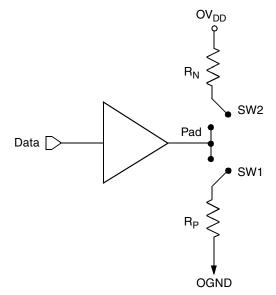

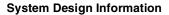

This section provides thermal management information for the MPC7410 for air-cooled applications. Proper thermal control design is primarily dependent on the system-level design—the heat sink, airflow, and thermal interface material. To reduce the die-junction temperature, heat sinks may be attached to the package by several methods such as spring clip to holes in the printed circuit board or with screws and springs to the printed circuit board; see Figure 26 for the BGA package and Figure 27 for the LGA package. This spring force should not exceed 5.5 pounds of force. Note that care should be taken to avoid focused forces being applied to die corners and/or edges when mounting heat sinks.

Figure 26. BGA Package Exploded Cross-Sectional View with Heat Sink Clip to PCB Option

#### Printed-Circuit Board

### Figure 27. LGA Package Exploded Cross-Sectional View with Heat Sink Clip to PCB Option

The board designer can choose between several types of heat sinks to place on the MPC7410. There are several commercially-available heat sinks for the MPC7410 from the following vendors:

| Aavid Thermalloy<br>70 Commercial Street, Suite 200<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                | 603-224-9988 |

|------------------------------------------------------------------------------------------------------------------------------|--------------|

| Alpha Novatech<br>473 Sapena Ct. #12<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                             | 408-567-8082 |

| The Bergquist Company<br>18930 West 78th St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com                   | 800-347-4572 |

| International Electronic Research Corporation (IERC)<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com | 818-842-7277 |

| Wakefield Engineering<br>33 Bridge St.<br>Pelham, NH 03076<br>Internet: www.wakefield.com                                    | 603-635-2800 |

Ultimately, the final selection of an appropriate heat sink depends on many factors, such as thermal performance at a given air velocity, spatial volume, mass, attachment method, assembly, and cost.

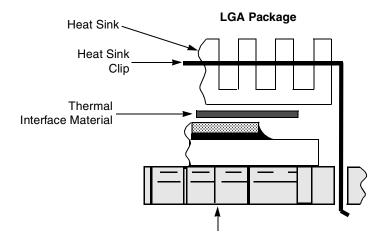

Figure 29 describes the thermal performance of selected thermal interface materials.

The board designer can choose between several types of thermal interface. Heat sink adhesive materials should be selected based on high conductivity, yet adequate mechanical strength to meet equipment shock/vibration requirements. There are several commercially-available thermal interfaces and adhesive materials provided by the following vendors:

| Chomerics, Inc.                  | 781-935-4850 |

|----------------------------------|--------------|

| 77 Dragon Court                  |              |

| Woburn, MA 01888-4014            |              |

| Internet: www.chomerics.com      |              |

| Dow-Corning Corporation          | 800-248-2481 |

| Dow-Corning Electronic Materials |              |

| 2200 W. Salzburg Rd.             |              |

| Midland, MI 48686-0997           |              |

| Internet: www.dow.com            |              |

| Shin-Etsu MicroSi, Inc.          | 888-642-7674 |

| 10028 S. 51st St.                |              |

| Phoenix, AZ 85044                |              |

| Internet: www.microsi.com        |              |

#### **System Design Information**

888-246-9050

Thermagon Inc. 4707 Detroit Ave. Cleveland, OH 44102 Internet: www.thermagon.com

# 8.8.3 Heat Sink Selection Example

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$$T_i = T_a + T_r + (\theta_{ic} + \theta_{int} + \theta_{sa}) \times P_d$$

where:

T<sub>i</sub> is the die-junction temperature

T<sub>a</sub> is the inlet cabinet ambient temperature

$T_r$  is the air temperature rise within the computer cabinet

$\theta_{ic}$  is the junction-to-case thermal resistance

$\theta_{int}$  is the adhesive or interface material thermal resistance

$\theta_{sa}$  is the heat sink base-to-ambient thermal resistance

P<sub>d</sub> is the power dissipated by the device

During operation the die-junction temperatures  $(T_j)$  should be maintained less than the value specified in Table 3. The temperature of the air cooling the component greatly depends upon the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature  $(T_a)$  may range from 30° to 40°C. The air temperature rise within a cabinet  $(T_r)$  may be in the range of 5° to 10°C. The thermal resistance of the thermal interface material ( $\theta_{int}$ ) is typically about 1°C/W. Assuming a T<sub>a</sub> of 30°C, a T<sub>r</sub> of 5°C, a CBGA package  $\theta_{jc} = 0.03$ , and a power consumption (P<sub>d</sub>) of 5.0 W, the following expression for T<sub>j</sub> is obtained:

Die-junction temperature:  $T_i = 30^{\circ}C + 5^{\circ}C + (0.03^{\circ}C/W + 1.0^{\circ}C/W + \theta_{sa}) \times 5.0 W$

For a Thermalloy heat sink #2328B, the heat sink-to-ambient thermal resistance ( $\theta_{sa}$ ) versus airflow velocity is shown in Figure 30.

Assuming an air velocity of 0.5 m/s, we have an effective R<sub>sa</sub> of 7°C/W, thus

$T_i = 30^{\circ}C + 5^{\circ}C + (0.03^{\circ}C/W + 1.0^{\circ}C/W + 7^{\circ}C/W) \times 5.0 W,$

resulting in a die-junction temperature of approximately 75°C which is well within the maximum operating temperature of the component.

Other heat sinks offered by Aavid Thermalloy, Alpha Novatech, The Bergquist Company, IERC, and Wakefield Engineering offer different heat sink-to-ambient thermal resistances, and may or may not need airflow.

# **10 Ordering Information**

7440

Ordering information for the parts fully covered by this specification document is provided in Section 10.1, "Part Numbers Addressed by This Specification." Section 10.2, "Part Numbers Not Fully Addressed by This Document," lists the part numbers which do not fully conform to the specifications of this document. These special part numbers require an additional document called a part number specification.

# **10.1 Part Numbers Addressed by This Specification**

Table 17 provides the Freescale part numbering nomenclature for the MPC7410 Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| Mxx             | 7410               | XX                                                 | nnn                                 | X                                | X                                                                                                        |

|-----------------|--------------------|----------------------------------------------------|-------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------|

| Product<br>Code | Part<br>Identifier | Package <sup>1</sup>                               | Processor<br>Frequency <sup>2</sup> | Application<br>Modifier          | Revision Level                                                                                           |

| MPC             | 7410               | RX = CBGA<br>HX = HCTE_CBGA<br>VS = HCTE_LGA       | 400<br>450<br>500                   | L: 1.8 V ± 100 mV<br>0° to 105°C | C: 1.2; PVR = 800C 1102<br>D: 1.3; PVR = 800C 1103<br>E: 1.4; PVR = 800C 1104<br>E: 1.4; PVR = 800C 1104 |

| MC              |                    | VU = HCTE_CBGA<br>(Lead Free C5<br>Solder Spheres) | 400<br>500                          |                                  |                                                                                                          |

## Table 17. Part Numbering Nomenclature

#### Notes:

1. See Section 7, "Package Description," for more information on available package types and Table 4 for more information on thermal characteristics.

Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

**Ordering Information**

# **10.2 Part Numbers Not Fully Addressed by This Document**

Parts with application modifiers or revision levels not fully addressed in this specification document are described in separate part number specifications which supplement and supersede this document, as described in the following tables.

| Table 18. Part Numbers A | Addressed by MPC74 | 10RXnnnPx Series P | art Number Specifications |

|--------------------------|--------------------|--------------------|---------------------------|

|--------------------------|--------------------|--------------------|---------------------------|

| MPC             | 7410               | RX        | nnn                                 | Р                              | X                                                                                                                    |

|-----------------|--------------------|-----------|-------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Product<br>Code | Part<br>Identifier | Package   | Processor<br>Frequency <sup>1</sup> | Application<br>Modifier        | Revision Level                                                                                                       |

| MPC             | 7410               | RX = CBGA | 450<br>500<br>550                   | P: 2.0 V ± 50 mV<br>0° to 65°C | C: 1.2; PVR = 800C 1102 <sup>1</sup><br>D: 1.3; PVR = 800C 1103 <sup>2</sup><br>E: 1.4; PVR = 800C 1104 <sup>3</sup> |

**Notes:** Document order numbers:

1. MPC7410PCPNS.

2. MPC7410PDPNS.

3. MPC7410PEPNS.

## Table 19. Part Numbers Addressed by MPC7410 RISC Microprocessor HardwareSpecifications Addendum for the MPC7410xxnnnNE Series

| Мхх             | 7410               | xx                                                 | nnn                                 | Ν                       | E                       |

|-----------------|--------------------|----------------------------------------------------|-------------------------------------|-------------------------|-------------------------|

| Product<br>Code | Part<br>Identifier | Package                                            | Processor<br>Frequency <sup>1</sup> | Application<br>Modifier | Revision Level          |

| MPC             | 7410               | RX = CBGA                                          | 400<br>450<br>500                   | N: 1.5 V ± 50 mV        | E: 1.4; PVR = 800C 1104 |

|                 |                    | HX = HCTE_CBGA<br>VS = HCTE_LGA                    | 400<br>450                          |                         |                         |

| MC              |                    | VU = HCTE_CBGA<br>(Lead Free C5 Solder<br>Spheres) |                                     |                         |                         |

Note: Document order number: MPC7410ECS02AD

## Table 20. Part Numbers Addressed by MPC7410TRXnnnNE Part Number Specification

| MPC             | 7410               | Т                     | RX        | nnn                                 | Ν                       | E                       |

|-----------------|--------------------|-----------------------|-----------|-------------------------------------|-------------------------|-------------------------|

| Product<br>Code | Part<br>Identifier | Process<br>Descriptor | Package   | Processor<br>Frequency <sup>1</sup> | Application<br>Modifier | Revision Level          |

| MPC             | 7410               | T: -40° to 105°C      | RX = CBGA | 400<br>450                          | N: 1.5 V ±50 mV         | E: 1.4; PVR = 800C 1104 |

Note: Document order number: MPC7410TRXNEPNS.

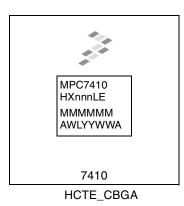

# **10.3 Part Marking**

Parts are marked as the example shown in Figure 31.

### Notes:

MMMMMM is the 6-digit mask number.

AWLYYWWA is the traceability code.

CCCCC is the country of assembly. This space is left blank if parts are assembled in the United States.

Figure 31. Part Marking for HCTE\_CBGA Device