Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 8032                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | LVR, POR, PWM, WDT                                                     |

| Number of I/O              | 37                                                                     |

| Program Memory Size        | 160KB (160K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | - ·                                                                    |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                            |

| Data Converters            | A/D 4x8b                                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 52-TQFP                                                                |

| Supplier Device Package    |                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/upsd3233b-40t6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

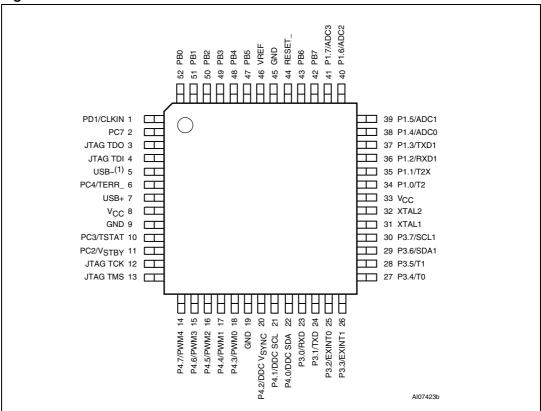

Figure 2. TQFP52 connections

1. Pull-up resistor required on pin 5 (2 k $\Omega$  for 3 V devices, 7.5 k $\Omega$  for 5 V devices) for all 52-pin devices, with or without USB function.

| Masaasis          | Onevetien                            | Addressing modes       |            |              |      |  |  |

|-------------------|--------------------------------------|------------------------|------------|--------------|------|--|--|

| Mnemonic          | Operation                            | Dir.                   | Ind.       | Reg.         | Imm. |  |  |

| INC               | A = A + 1                            |                        | Accumu     | lator only   |      |  |  |

| INC <byte></byte> | <byte> = <byte> + 1</byte></byte>    | X X X                  |            |              |      |  |  |

| INC DPTR          | DPTR = DPTR + 1                      | Data Pointer only      |            |              |      |  |  |

| DEC               | A = A - 1                            |                        | Accumu     | lator only   |      |  |  |

| DEC <byte></byte> | <byte> = <byte> - 1</byte></byte>    | Х                      | Х          | Х            |      |  |  |

| MUL AB            | B:A = B x A                          |                        | Accumulato | r and B only | /    |  |  |

| DIV AB            | A = Int[ A / B ]<br>B = Mod[ A / B ] | Accumulator and B only |            |              |      |  |  |

| DA A              | Decimal Adjust                       | Accumulator only       |            |              |      |  |  |

Table 4. Arithmetic instructions (continued)

## 2.11 Logical instructions

*Table 5* lists logical instructions for UPSD323xx devices. The instructions that perform Boolean operations (AND, OR, Exclusive OR, NOT) on bytes perform the operation on a bit-by-bit basis. That is, if the Accumulator contains 00110101B and byte contains 01010011B, then:

ANL A, <byte>

will leave the Accumulator holding 00010001B.

The addressing modes that can be used to access the <byte> operand are listed in Table 5.

The ANL A, <byte> instruction may take any of the forms:

ANL A,7FH(direct addressing)

ANL A, @R1 (indirect addressing)

ANL A,R6 (register addressing)

ANL A,#53H (immediate constant)

Note: Boolean operations can be performed on any byte in the internal Data Memory space without going through the Accumulator. The XRL <byte>, #data instruction, for example, offers a quick and easy way to invert port bits, as in:

XRL P1, #0FFH.

If the operation is in response to an interrupt, not using the Accumulator saves the time and effort to push it onto the stack in the service routine.

The Rotate instructions (RL A, RLC A, etc.) shift the Accumulator 1 bit to the left or right. For a left rotation, the MSB rolls into the LSB position. For a right rotation, the LSB rolls into the MSB position.

The SWAP A instruction interchanges the high and low nibbles within the Accumulator. This is a useful operation in BCD manipulations. For example, if the Accumulator contains a

| 머고          | Den Neme |      |      |      | Bit Regist | er Name |      |                   |        | set<br>ue      | 0                            |

|-------------|----------|------|------|------|------------|---------|------|-------------------|--------|----------------|------------------------------|

| SFR<br>Addr | Reg Name | 7    | 6    | 5    | 4          | 3       | 2    | 1                 | 0      | Reset<br>Value | Comments                     |

| A1          | PWMCON   | PWML | PWMP | PWME | CFG4       | CFG3    | CFG2 | CFG1              | CFG0   | 00             | PWM Control<br>Polarity      |

| A2          | PWM0     |      |      |      |            |         |      |                   |        | 00             | PWM0<br>Output Duty<br>Cycle |

| A3          | PWM1     |      |      |      |            |         |      |                   |        | 00             | PWM1<br>Output Duty<br>Cycle |

| A4          | PWM2     |      |      |      |            |         |      |                   |        | 00             | PWM2<br>Output Duty<br>Cycle |

| A5          | PWM3     |      |      |      |            |         |      |                   |        | 00             | PWM3<br>Output Duty<br>Cycle |

| A6          | WDRST    |      |      |      |            |         |      |                   |        | 00             | Watch Dog<br>Reset           |

| A7          | IEA      | EDDC |      |      | ES2        |         |      | El <sup>2</sup> C | EUSB   | 00             | Interrupt<br>Enable (2nd)    |

| A8          | IE       | EA   | -    | ET2  | ES         | ET1     | EX1  | ET0               | EX0    | 00             | Interrupt<br>Enable          |

| A9          |          |      |      |      |            |         |      |                   |        |                |                              |

| AA          | PWM4P    |      |      |      |            |         |      |                   |        | 00             | PWM 4<br>Period              |

| AB          | PWM4W    |      |      |      |            |         |      |                   |        | 00             | PWM 4 Pulse<br>Width         |

| AE          | WDKEY    |      |      |      |            |         |      |                   |        | 00             | Watch Dog<br>Key Register    |

| B0          | P3       |      |      |      |            |         |      |                   |        | FF             | Port 3                       |

| B1          | PSCL0L   |      |      |      |            |         |      |                   |        | 00             | Prescaler 0<br>Low (8-bit)   |

| B2          | PSCL0H   |      |      |      |            |         |      |                   |        | 00             | Prescaler 0<br>High (8-bit)  |

| В3          | PSCL1L   |      |      |      |            |         |      |                   |        | 00             | Prescaler 1<br>Low (8-bit)   |

| B4          | PSCL1H   |      |      |      |            |         |      |                   |        | 00             | Prescaler 1<br>High (8-bit)  |

| B7          | IPA      | PDDC |      |      | PS2        |         |      | PI2C              | PUSB   | 00             | Interrupt<br>Priority (2nd)  |

| B8          | IP       |      |      | PT2  | PS         | PT1     | PX1  | PT0               | PX0    | 00             | Interrupt<br>Priority        |

| C0          | P4       |      |      |      |            |         |      |                   |        | FF             | New Port 4                   |

| C8          | T2CON    | TF2  | EXF2 | RCLK | TCLK       | EXEN2   | TR2  | C/T2              | CP/RL2 | 00             | Timer 2<br>Control           |

### Table 16. List of all SFRs (continued)

| ሮ ታ         |             |     |        |           | Bit Regist | er Name    |            |            |      | set<br>ue      | Comments                            |

|-------------|-------------|-----|--------|-----------|------------|------------|------------|------------|------|----------------|-------------------------------------|

| SFR<br>Addr | Reg Name    | 7   | 6      | 5         | 4          | 3          | 2          | 1          | 0    | Reset<br>Value | Comments                            |

| C9          | T2MOD       |     |        |           |            |            |            |            | DCEN | 00             | Timer 2<br>mode                     |

| CA          | RCAP2L      |     |        |           |            |            |            |            |      | 00             | Timer 2<br>Reload low               |

| СВ          | RCAP2H      |     |        |           |            |            |            |            |      | 00             | Timer 2<br>Reload High              |

| СС          | TL2         |     |        |           |            |            |            |            |      | 00             | Timer 2 Low<br>byte                 |

| CD          | TH2         |     |        |           |            |            |            |            |      | 00             | Timer 2 High<br>byte                |

| D0          | PSW         | CY  | AC     | FO        | RS1        | RS0        | ov         |            | Р    | 00             | Program<br>Status Word              |

| D1          | S1SETU<br>P |     |        |           |            |            |            |            |      | 00             | DDC I <sup>2</sup> C<br>(S1) Setup  |

| D2          | S2SETUP     |     |        |           |            |            |            |            |      | 00             | I <sup>2</sup> C (S2)<br>Setup      |

| D4          | RAMBUF      |     |        |           |            |            |            |            |      | хх             | DDC Ram<br>Buffer                   |

| D5          | DDCDAT      |     |        |           |            |            |            |            |      | 00             | DDC Data<br>xmit<br>register        |

| D6          | DDCADR      |     |        |           |            |            |            |            |      | 00             | Addr<br>pointer<br>register         |

| D7          | DDCCON      | —   | EX_DAT | SWEN<br>B | DDC_A<br>X | DDCIN<br>T | DDC1E<br>N | SWHIN<br>T | MO   | 00             | DDC<br>Control<br>Register          |

| D8          | S1CON       | CR2 | ENI1   | STA       | STO        | ADDR       | AA         | CR1        | CR0  | 00             | DDC I <sup>2</sup> C<br>Control Reg |

| D9          | S1STA       | GC  | Stop   | Intr      | TX-Md      | Bbusy      | Blost      | ACK_R      | SLV  | 00             | DDC I <sup>2</sup> C<br>Status      |

| DA          | S1DAT       |     |        |           |            |            |            |            |      | 00             | Data Hold<br>Register               |

| DB          | S1ADR       |     |        |           |            |            |            |            |      | 00             | DDC I <sup>2</sup> C<br>address     |

| DC          | S2CON       | CR2 | EN1    | STA       | STO        | ADDR       | AA         | CR1        | CR0  | 00             | I <sup>2</sup> C Bus<br>Control Reg |

| DD          | S2STA       | GC  | Stop   | Intr      | TX-Md      | Bbusy      | Blost      | ACK_R      | SLV  | 00             | I <sup>2</sup> C Bus<br>Status      |

| DE          | S2DAT       |     |        |           |            |            |            |            |      | 00             | Data Hold<br>Register               |

| DF          | S2ADR       |     |        |           |            |            |            |            |      | 00             | I <sup>2</sup> C address            |

| E0          | ACC         |     |        |           |            |            |            |            |      | 00             | Accumulator                         |

### Table 16. List of all SFRs (continued)

| CSIOP          | Deviatory as a                |                  |               | Bi                   | t regist              | er nam                | е                     |               |               | Reset | 0                                              |

|----------------|-------------------------------|------------------|---------------|----------------------|-----------------------|-----------------------|-----------------------|---------------|---------------|-------|------------------------------------------------|

| addr<br>offset | Register name                 | 7                | 6             | 5                    | 4                     | 3                     | 2                     | 1             | 0             | value | Comments                                       |

| C0             | Primary Flash<br>Protection   | Sec7_<br>Prot    | Sec6_<br>Prot | Sec5_<br>Prot        | Sec4_<br>Prot         | Sec3_<br>Prot         | Sec2_<br>Prot         | Sec1_<br>Prot | Sec0_<br>Prot |       | Bit = 1 sector<br>is protected                 |

| C2             | Secondary Flash<br>Protection | Security<br>_Bit | *             | *                    | *                     | Sec3_<br>Prot         | Sec2_<br>Prot         | Sec1_<br>Prot | Sec0_<br>Prot |       | Security Bit =<br>1 device is<br>secured       |

| B0             | PMMR0                         | *                | *             | PLD<br>Mcells<br>clk | PLD<br>array-<br>clk  | PLD<br>Turbo          | *                     | APD<br>enable | *             | 00    | Control PLD<br>power<br>consumption            |

| B4             | PMMR2                         | *                |               | PLD<br>array<br>Ale  | PLD<br>array<br>Cntl2 | PLD<br>array<br>Cntl1 | PLD<br>array<br>Cntl0 | *             | *             | 00    | Blocking<br>inputs to PLD<br>array             |

| E0             | Page                          |                  |               |                      |                       |                       |                       |               |               | 00    | Page Register                                  |

| E2             | VM                            | Periph-<br>mode  | *             | *                    | FL_<br>data           | Boot_<br>data         | FL_<br>code           | Boot_<br>code | SR_<br>code   |       | Configure<br>8032 Program<br>and Data<br>Space |

Table 17. PSD module register address offset (continued)

(Register address = CSIOP address + address offset; where CSIOP address is defined by user in PSDsoft)

\* indicates bit is not used and must be set to '0'.

| Bit | Symbol | Function                          |

|-----|--------|-----------------------------------|

| 7   | EDDC   | Enable DDC Interrupt              |

| 6   | —      | Not used                          |

| 5   | —      | Not used                          |

| 4   | ES2    | Enable 2nd USART Interrupt        |

| 3   | —      | Not used                          |

| 2   | —      | Not used                          |

| 1   | EI2C   | Enable I <sup>2</sup> C Interrupt |

| 0   | EUSB   | Enable USB Interrupt              |

Table 21. Description of the IEA bits

### Table 22. Description of the IP bits

| Bit | Symbol | Function                                 |  |  |  |  |

|-----|--------|------------------------------------------|--|--|--|--|

| 7   | —      | Reserved                                 |  |  |  |  |

| 6   | —      | Reserved                                 |  |  |  |  |

| 5   | PT2    | Timer 2 Interrupt priority level         |  |  |  |  |

| 4   | PS     | USART Interrupt priority level           |  |  |  |  |

| 3   | PT1    | Timer 1 Interrupt priority level         |  |  |  |  |

| 2   | PX1    | External Interrupt (Int1) priority level |  |  |  |  |

| 1   | PT0    | Timer 0 Interrupt priority level         |  |  |  |  |

| 0   | PX0    | External Interrupt (Int0) priority level |  |  |  |  |

### Table 23.Description of the IPA bits

| Bit | Symbol | Function                                  |

|-----|--------|-------------------------------------------|

| 7   | PDDC   | DDC Interrupt priority level              |

| 6   | —      | Not used                                  |

| 5   | —      | Not used                                  |

| 4   | PS2    | 2nd USART Interrupt priority level        |

| 3   | —      | Not used                                  |

| 2   | —      | Not used                                  |

| 1   | PI2C   | I <sup>2</sup> C Interrupt priority level |

| 0   | PUSB   | USB Interrupt priority level              |

| Table J4. | Becchipti             |                                                                                                                                                                              |  |  |  |  |  |  |

|-----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit       | Symbol                | Function                                                                                                                                                                     |  |  |  |  |  |  |

| 7         | GC                    | General Call Flag                                                                                                                                                            |  |  |  |  |  |  |

| 6         | STOP                  | Stop Flag. This bit is set when a STOP condition is received                                                                                                                 |  |  |  |  |  |  |

| 5         | INTR <sup>(1,2)</sup> | Interrupt Flag. This bit is set when an I <sup>2</sup> C Interrupt condition is requested                                                                                    |  |  |  |  |  |  |

| 4         | TX_MODE               | Transmission mode Flag.<br>This bit is set when the I <sup>2</sup> C is a transmitter; otherwise this bit is reset                                                           |  |  |  |  |  |  |

| 3         | BBUSY                 | Bus Busy Flag.<br>This bit is set when the bus is being used by another master; otherwise,<br>this bit is reset                                                              |  |  |  |  |  |  |

| 2         | BLOST                 | Bus Lost Flag.<br>This bit is set when the master loses the bus contention; otherwise this bit<br>is reset                                                                   |  |  |  |  |  |  |

| 1         | /ACK_REP              | Acknowledge Response Flag.<br>This bit is set when the receiver transmits the not acknowledge signal<br>This bit is reset when the receiver transmits the acknowledge signal |  |  |  |  |  |  |

| 0         | SLV                   | Slave mode Flag.<br>This bit is set when the I <sup>2</sup> C plays role in the Slave mode; otherwise this bit<br>is reset                                                   |  |  |  |  |  |  |

Table 54. Description of the SxSTA bits

1. Interrupt Flag bit (INTR, SxSTA Bit 5) is cleared by Hardware as reading SxSTA register.

2. I<sup>2</sup>C interrupt flag (INTR) can occur in below case. (except DDC2B mode at SWENB=0)

#### Table 55.Data shift register (SxDAT: S1DAT, S2DAT)

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| SxDAT7 | SxDAT6 | SxDAT5 | SxDAT4 | SxDAT3 | SxDAT2 | SxDAT1 | SxDAT0 |

# 15.3 Address register (SxADR: S1ADR, S2ADR)

This 8-bit register may be loaded with the 7-bit slave address to which the controller will respond when programmed as a slave receive/transmitter.

The Start/Stop Hold Time Detection and System Clock registers (*Table 57* and *Table 58*) are included in the  $I^2C$  unit to specify the start/stop detection time to work with the large range of MCU frequency values supported. For example, with a system clock of 40MHz.

| Table 56. | Address | register | (SxADR) | ) |

|-----------|---------|----------|---------|---|

|-----------|---------|----------|---------|---|

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0 |

|------|------|------|------|------|------|------|---|

| SLA6 | SLA5 | SLA4 | SLA3 | SLA2 | SLA1 | SLA0 | — |

1. SLA6 to SLA0: Own slave address.

| Table 66. | Description of the DISTA bits (continued) |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-----------|-------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit       | Symbol                                    | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 4         | TXD0F                                     | R/W | Endpoint0 Data Transmit Flag.<br>This bit is set after the data stored in Endpoint 0 transmit<br>buffers has been sent and an ACK handshake packet from the<br>host is received. Once the next set of data is ready in the<br>transmit buffers, software must clear this flag. To enable the<br>next data packet transmission, TX0E must also be set. If<br>TXD0F Bit is not cleared, a NAK handshake will be returned in<br>the next IN transactions. RESET clears this bit.                                                                                  |  |

| 3         | RXD0F                                     | R/W | Endpoint0 Data Receive Flag.<br>This bit is set after the USB module has received a data<br>packet and responded with ACK handshake packet. Software<br>must clear this flag after all of the received data has been<br>read. Software must also set RX0E Bit to one to enable the<br>next data packet reception. If RXD0F Bit is not cleared, a NAK<br>handshake will be returned in the next OUT transaction.<br>RESET clears this bit.                                                                                                                      |  |

| 2         | TXD1F                                     | R/W | Endpoint1 / Endpoint2 Data Transmit Flag.<br>This bit is shared by Endpoints 1 and Endpoints 2. It is set<br>after the data stored in the shared Endpoint 1/ Endpoint 2<br>transmit buffer has been sent and an ACK handshake packet<br>from the host is received. Once the next set of data is ready in<br>the transmit buffers, software must clear this flag. To enable<br>the next data packet transmission, TX1E must also be set. If<br>TXD1F Bit is not cleared, a NAK handshake will be returned in<br>the next IN transaction. RESET clears this bit. |  |

| 1         | EOPF                                      | R/W | End of Packet Flag.<br>This bit is set when a valid End of Packet sequence is<br>detected on the D+ and D-line. Software must clear this flag.<br>RESET clears this bit.                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 0         | RESUMF                                    | R/W | Resume Flag.<br>This bit is set when USB bus activity is detected while the<br>SUSPND Bit is set.<br>Software must clear this flag. RESET clears this bit.                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Table 68. | Description of the UISTA bits | (continued) |

|-----------|-------------------------------|-------------|

|           |                               | (           |

| Table 69. | USB Endpoint0 transmit control register (UCON0: 0EAh) |

|-----------|-------------------------------------------------------|

|           |                                                       |

|       |        |      |      | •       | •       | ,       |         |

|-------|--------|------|------|---------|---------|---------|---------|

| 7     | 6      | 5    | 4    | 3       | 2       | 1       | 0       |

| TSEQ0 | STALL0 | TX0E | RX0E | TP0SIZ3 | TP0SIZ2 | TP0SIZ1 | TP0SIZ0 |

| Functional Block          | JTAG programming | Device programmer | IAP |

|---------------------------|------------------|-------------------|-----|

| Primary Flash memory      | Yes              | Yes               | Yes |

| Secondary Flash memory    | Yes              | Yes               | Yes |

| PLD array (DPLD and CPLD) | Yes              | Yes               | No  |

| PSD module configuration  | Yes              | Yes               | No  |

Table 83.

Methods of programming different functional blocks of the PSD module

# 19 Development system

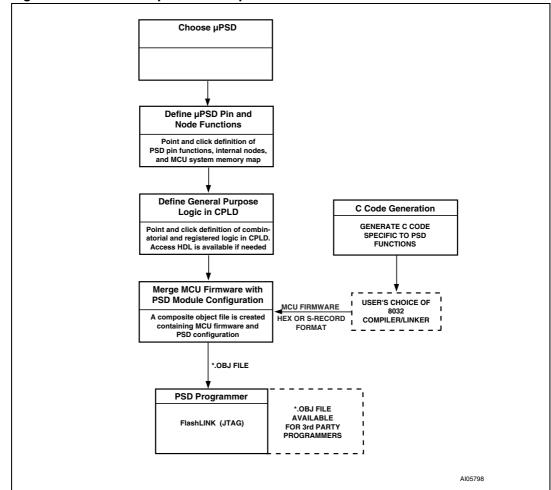

UPSD323xx devices are supported by PSDsoft, a Windows-based software development tool (Windows-95, Windows-98, Windows-NT). A PSD module design is quickly and easily produced in a point and click environment. The designer does not need to enter Hardware Description Language (HDL) equations, unless desired, to define PSD module pin functions and memory map information. The general design flow is shown in *Figure 50*. PSDsoft is available from our web site (the address is given on the back page of this data sheet) or other distribution channels.

PSDsoft directly supports a low cost device programmer from ST: FlashLINK (JTAG). The programmer may be purchased through your local distributor/representative. UPSD323xx devices are also supported by third party device programmers. See our web site for the current list.

Figure 50. PSDsoft express development tool

It is suggested (as with all Flash memories) to read the location again after the embedded programming algorithm has completed, to compare the byte that was written to Flash memory with the byte that was intended to be written.

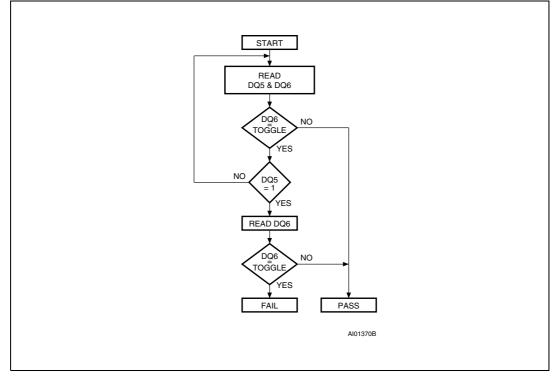

When using the Data Toggle method after an Erase cycle, *Figure 52* still applies. the Toggle Flag bit (DQ6) toggles until the Erase cycle is complete. A 1 on the Error Flag bit (DQ5) indicates a time-out condition on the Erase cycle; a '0' indicates no error. The MCU can read any location within the sector being erased to get the Toggle Flag bit (DQ6) and the Error Flag bit (DQ5).

PSDsoft Express generates ANSI C code functions which implement these Data Toggling algorithms.

### 22.6.3 Unlock Bypass

The Unlock Bypass instructions allow the system to program bytes to the Flash memories faster than using the standard Program instruction. The Unlock Bypass mode is entered by first initiating two Unlock cycles. This is followed by a third WRITE cycle containing the Unlock Bypass code, 20h (as shown in *Table 85*).

The Flash memory then enters the Unlock Bypass mode. A two-cycle Unlock Bypass Program instruction is all that is required to program in this mode. The first cycle in this instruction contains the Unlock Bypass Program code, A0h. The second cycle contains the program address and data. Additional data is programmed in the same manner. These instructions dispense with the initial two Unlock cycles required in the standard Program instruction, resulting in faster total Flash memory programming.

During the Unlock Bypass mode, only the Unlock Bypass Program and Unlock Bypass Reset Flash instructions are valid.

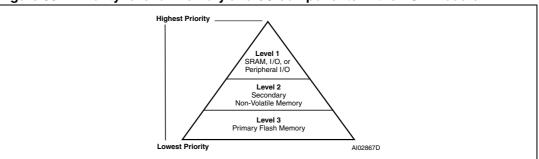

#### Figure 53. Priority level of memory and I/O components in the PSD module

### Table 89.VM register

| Bit 7<br>PIO_EN               | Bit 6       | Bit 5       | Bit 4<br>Primary<br>FL_Data                  | Bit 3<br>Secondary<br>Data                          | Bit 2<br>Primary<br>FL_Cod<br>e                   | Bit 1<br>Secondary<br>Code                                   | Bit 0<br>SRAM_Co<br>de                     |

|-------------------------------|-------------|-------------|----------------------------------------------|-----------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------|--------------------------------------------|

| 0 =<br>disable<br>PIO<br>mode | not<br>used | not<br>used | 0 = RD<br>can't<br>access<br>Flash<br>memory | 0 = RD can't<br>access<br>Secondary<br>Flash memory | 0 =<br>PSEN<br>can't<br>access<br>Flash<br>memory | 0 = <u>PSEN</u> can't<br>access<br>Secondary<br>Flash memory | 0 = <u>PSEN</u><br>can't<br>access<br>SRAM |

| 1=<br>enable<br>PIO<br>mode   | not<br>used | not<br>used | 1 = RD<br>access<br>Flash<br>memory          | 1 = RD access<br>Secondary<br>Flash memory          | 1 =<br>PSEN<br>access<br>Flash<br>memory          | 1 = <u>PSEN</u><br>access<br>Secondary<br>Flash memory       | 1 = <del>PSEN</del><br>access<br>SRAM      |

### 22.10.3 Separate Space mode

Program space is separated from Data space. For example, Program Select Enable ( $\overrightarrow{PSEN}$ ) is used to access the program code from the primary Flash memory, while READ Strobe ( $\overrightarrow{RD}$ ) is used to access data from the secondary Flash memory, SRAM and I/O Port blocks. This configuration requires the VM Register to be set to 0Ch (see *Figure 54*).

### 22.10.4 Combined Space modes

The Program and Data spaces are combined into one memory space that allows the primary Flash memory, secondary Flash memory, and SRAM to be accessed by either Program Select Enable ( $\overrightarrow{PSEN}$ ) or READ Strobe ( $\overrightarrow{RD}$ ). For example, to configure the primary Flash memory in Combined space, Bits b2 and b4 of the VM Register are set to '1' (see *Figure 55*).

flop. The flip-flop is clocked on the rising edge of CLKIN (PD1). The preset and clear are active High inputs. Each clear input can use up to two product terms.

| Output<br>Macrocell | Port<br>Assignment<br>(1,2) | Native Product<br>Terms | Max. Borrowed<br>Product Terms | Data Bit for<br>Loading or Reading |

|---------------------|-----------------------------|-------------------------|--------------------------------|------------------------------------|

| McellAB0            | Port A0, B0                 | 3                       | 6                              | D0                                 |

| McellAB1            | Port A1, B1                 | 3                       | 6                              | D1                                 |

| McellAB2            | Port A2, B2                 | 3                       | 6                              | D2                                 |

| McellAB3            | Port A3, B3                 | 3                       | 6                              | D3                                 |

| McellAB4            | Port A4, B4                 | 3                       | 6                              | D4                                 |

| McellAB5            | Port A5, B5                 | 3                       | 6                              | D5                                 |

| McellAB6            | Port A6, B6                 | 3                       | 6                              | D6                                 |

| McellAB7            | Port A7, B7                 | 3                       | 6                              | D7                                 |

| McellBC0            | Port B0                     | 4                       | 5                              | D0                                 |

| McellBC1            | Port B1                     | 4                       | 5                              | D1                                 |

| McellBC2            | Port B2, C2                 | 4                       | 5                              | D2                                 |

| McellBC3            | Port B3, C3                 | 4                       | 5                              | D3                                 |

| McellBC4            | Port B4, C4                 | 4                       | 6                              | D4                                 |

| McellBC5            | Port B5                     | 4                       | 6                              | D5                                 |

| McellBC6            | Port B6                     | 4                       | 6                              | D6                                 |

| McellBC7            | Port B7, C7                 | 4                       | 6                              | D7                                 |

Table 92. Output macrocell port and data bit assignments

1. McellAB0-McellAB7 can only be assigned to Port B in the 52-pin package

2. Port PC0, PC1, PC5, and PC6 are assigned to JTAG pins and are not available as Macrocell outputs.

# 23.5 Product term allocator

The CPLD has a Product Term Allocator. PSDsoft uses the Product Term Allocator to borrow and place product terms from one macrocell to another. The following list summarizes how product terms are allocated:

- McellAB0-McellAB7 all have three native product terms and may borrow up to six more

- McellBC0-McellBC3 all have four native product terms and may borrow up to five more

- McellBC4-McellBC7 all have four native product terms and may borrow up to six more.

Each macrocell may only borrow product terms from certain other macrocells. Product terms already in use by one macrocell are not available for another macrocell.

If an equation requires more product terms than are available to it, then "external" product terms are required, which consume other Output Macrocells (OMC). If external product terms are used, extra delay is added for the equation that required the extra product terms.

This is called product term expansion. PSDsoft Express performs this expansion as needed.

are not set, writing to the macrocell loads data to the macrocell flip-flops. See *Section 23: PLDs*.

### 24.9.4 OMC mask register

Each OMC Mask Register Bit corresponds to an Output Macrocell (OMC) flip-flop. When the OMC Mask Register Bit is set to a '1,' loading data into the Output Macrocell (OMC) flip-flop is blocked. The default value is '0' or unblocked.

### 24.9.5 Input macrocells (IMC)

The Input Macrocells (IMC) can be used to latch or store external inputs. The outputs of the Input Macrocells (IMC) are routed to the PLD input bus, and can be read by the MCU. See *Section 23: PLDs*.

### 24.9.6 Enable out

The Enable Out register can be read by the MCU. It contains the output enable values for a given port. A '1' indicates the driver is in output mode. A '0' indicates the driver is in tri-state and the pin is in input mode.

| Drive<br>Register | Bit 7             | Bit 6             | Bit 5             | Bit 4             | Bit 3             | Bit 2        | Bit 1        | Bit 0             |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------|--------------|-------------------|

| Port A            | Open              | Open              | Open              | Open              | Slew              | Slew         | Slew         | Slew              |

|                   | Drain             | Drain             | Drain             | Drain             | Rate              | Rate         | Rate         | Rate              |

| Port B            | Open              | Open              | Open              | Open              | Slew              | Slew         | Slew         | Slew              |

|                   | Drain             | Drain             | Drain             | Drain             | Rate              | Rate         | Rate         | Rate              |

| Port C            | Open              | Open              | Open              | Open              | Open              | Open         | Open         | Open              |

|                   | Drain             | Drain             | Drain             | Drain             | Drain             | Drain        | Drain        | Drain             |

| Port D            | NA <sup>(1)</sup> | Slew<br>Rate | Slew<br>Rate | NA <sup>(1)</sup> |

Table 100. Drive register pin assignment

1. NA = Not Applicable.

#### Table 101. Port data registers

| Register Name    | Port    | MCU Access                                                           |

|------------------|---------|----------------------------------------------------------------------|

| Data In          | A,B,C,D | READ – input on pin                                                  |

| Data Out         | A,B,C,D | WRITE/READ                                                           |

| Output Macrocell | A,B,C   | READ – outputs of macrocells<br>WRITE – loading macrocells flip-flop |

| Mask Macrocell   | A,B,C   | WRITE/READ – prevents loading into a given<br>macrocell              |

| Input Macrocell  | A,B,C   | READ – outputs of the Input Macrocells                               |

| Enable Out       | A,B,C   | READ – the output enable control of the port driver                  |

The PSD module has a Turbo Bit in PMMR0. This bit can be set to turn the Turbo mode off (the default is with Turbo mode turned on). While Turbo mode is off, the PLDs can achieve standby current when no PLD inputs are changing (zero DC current). Even when inputs do change, significant power can be saved at lower frequencies (AC current), compared to when Turbo mode is on. When the Turbo mode is on, there is a significant DC current component and the AC component is higher.

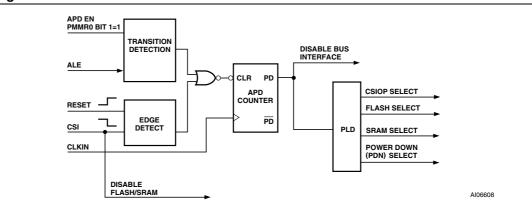

### Automatic Power-down (APD) Unit and Power-down mode

The APD Unit, shown in *Figure 67*, puts the PSD module into Power-down mode by monitoring the activity of Address Strobe (ALE). If the APD Unit is enabled, as soon as activity on Address Strobe (ALE) stops, a four-bit counter starts counting. If Address Strobe (ALE/AS, PD0) remains inactive for fifteen clock periods of CLKIN (PD1), Power-down (PDN) goes High, and the PSD module enters Power-down mode, as discussed next.

#### Power-down mode

By default, if you enable the APD Unit, Power-down mode is automatically enabled. The device enters Power-down mode if Address Strobe (ALE) remains inactive for fifteen periods of CLKIN (PD1).

The following should be kept in mind when the PSD module is in Power-down mode:

- If Address Strobe (ALE) starts pulsing again, the PSD module returns to normal Operating mode. The PSD module also returns to normal Operating mode if either PSD Chip Select Input (CSI, PD2) is Low or the RESET input is High.

- The MCU address/data bus is blocked from all memory and PLDs.

- Various signals can be blocked (prior to Power-down mode) from entering the PLDs by setting the appropriate bits in the PMMR registers. The blocked signals include MCU control signals and the common CLKIN (PD1).

Note:

- Blocking CLKIN (PD1) from the PLDs does not block CLKIN (PD1) from the APD Unit.

- All memories enter Standby mode and are drawing standby current. However, the PLD and I/O ports blocks do *not* go into Standby mode because you don't want to have to wait for the logic and I/O to "wake-up" before their outputs can change. See *Table 102* for Power-down mode effects on PSD module ports.

- Typical standby current is of the order of microamperes. These standby current values assume that there are no transitions on any PLD input.

| Symbol                           | Parameter <sup>(1)</sup>              | 24 MHz<br>oscillator |      | Variable<br>1/t <sub>CLCL</sub> = 8 | Unit                                                                                                                                                               |    |

|----------------------------------|---------------------------------------|----------------------|------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                  |                                       | Min.                 | Max. | Min.                                | <b>bscillator</b><br><b>to 24 MHz</b><br><b>Max.</b><br>4 t <sub>CLCL</sub> – 87<br>3 t <sub>CLCL</sub> – 65<br>t <sub>CLCL</sub> – 10<br>5 t <sub>CLCL</sub> – 60 |    |

| t <sub>LHLL</sub>                | ALE pulse width                       | 43                   |      | 2 t <sub>CLCL</sub> – 40            |                                                                                                                                                                    | ns |

| t <sub>AVLL</sub>                | Address set-up to ALE                 | 17                   |      | t <sub>CLCL</sub> – 25              |                                                                                                                                                                    | ns |

| t <sub>LLAX</sub>                | Address hold after ALE                | 17                   |      | t <sub>CLCL</sub> – 25              |                                                                                                                                                                    | ns |

| t <sub>LLIV</sub>                | ALE Low to valid instruction in       |                      | 80   |                                     | 4 t <sub>CLCL</sub> – 87                                                                                                                                           | ns |

| t <sub>LLPL</sub>                | ALE to PSEN                           | 22                   |      | t <sub>CLCL</sub> – 20              |                                                                                                                                                                    | ns |

| t <sub>PLPH</sub>                | PSEN pulse width                      | 95                   |      | 3 t <sub>CLCL</sub> – 30            |                                                                                                                                                                    | ns |

| t <sub>PLIV</sub>                | PSEN to valid instruction in          |                      | 60   |                                     | 3 t <sub>CLCL</sub> – 65                                                                                                                                           | ns |

| t <sub>PXIX</sub>                | Input instruction hold after<br>PSEN  | 0                    |      | 0                                   |                                                                                                                                                                    | ns |

| t <sub>PXIZ</sub> <sup>(2)</sup> | Input instruction float after<br>PSEN |                      | 32   |                                     | t <sub>CLCL</sub> – 10                                                                                                                                             | ns |

| t <sub>PXAV</sub> <sup>(2)</sup> | Address valid after PSEN              | 37                   |      | t <sub>CLCL</sub> – 5               |                                                                                                                                                                    | ns |

| t <sub>AVIV</sub>                | Address to valid instruction in       |                      | 148  |                                     | 5 t <sub>CLCL</sub> – 60                                                                                                                                           | ns |

| t <sub>AZPL</sub>                | Address float to PSEN                 | -10                  |      | -10                                 |                                                                                                                                                                    | ns |

Table 121. External program memory AC characteristics (with the 3 V MCU module)

Conditions (in addition to those in *Table 114*, V<sub>CC</sub> = 3.0 to 3.6 V): V<sub>SS</sub> = 0 V; C<sub>L</sub> for Port 0, ALE and PSEN output is 100 pF, for 5 V devices, and 50 pF for 3 V devices; C<sub>L</sub> for other outputs is 80 pF, for 5 V devices, and 50 pF for 3 V devices)

2. Interfacing the UPSD323xx devices to devices with float times up to 35 ns is permissible. This limited bus contention does not cause any damage to Port 0 drivers.

| Table 122. | External clock drive | (with the 5 V MCU module) |

|------------|----------------------|---------------------------|

|------------|----------------------|---------------------------|

| Symbol             | Parameter <sup>(1)</sup> | 40 MHz c | oscillator | Variable (<br>1/t <sub>CLCL</sub> = 24 | Unit                                     |    |

|--------------------|--------------------------|----------|------------|----------------------------------------|------------------------------------------|----|

|                    |                          | Min.     | Max.       | Min.                                   | Max.                                     |    |

| t <sub>RLRH</sub>  | Oscillator period        |          |            | 25                                     | 41.7                                     | ns |

| t <sub>WLWH</sub>  | High time                |          |            | 10                                     | t <sub>CLCL</sub> –<br>t <sub>CLCX</sub> | ns |

| t <sub>LLAX2</sub> | Low time                 |          |            | 10                                     | t <sub>CLCL</sub> –<br>t <sub>CLCX</sub> | ns |

| t <sub>RHDX</sub>  | Rise time                |          |            |                                        | 10                                       | ns |

| t <sub>RHDX</sub>  | Fall time                |          |            |                                        | 10                                       | ns |

1. Conditions (in addition to those in *Table 113*,  $V_{CC}$  = 4.5 to 5.5 V):  $V_{SS}$  = 0 V;  $C_L$  for Port 0, ALE and PSEN output is 100 pF;  $C_L$  for other outputs is 80 pF

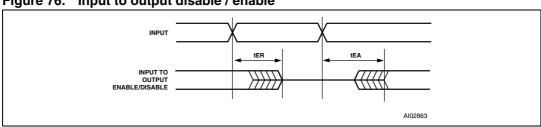

### Figure 76. Input to output disable / enable

### Table 127. CPLD combinatorial timing (5 V devices)

| Symbol                         | Parameter                                            | Conditions       | Min. | Max. | PT<br>aloc | Turbo<br>off | Slew<br>rate <sup>(1)</sup> | Unit |

|--------------------------------|------------------------------------------------------|------------------|------|------|------------|--------------|-----------------------------|------|

| t <sub>PD</sub> <sup>(2)</sup> | CPLD input pin/feedback to CPLD combinatorial output |                  |      | 20   | + 2        | + 10         | - 2                         | ns   |

| t <sub>EA</sub>                | CPLD input to CPLD output enable                     |                  |      | 21   |            | + 10         | -2                          | ns   |

| t <sub>ER</sub>                | CPLD input to CPLD output disable                    |                  |      | 21   |            | + 10         | -2                          | ns   |

| t <sub>ARP</sub>               | CPLD register clear or<br>preset delay               |                  |      | 21   |            | + 10         | -2                          | ns   |

| t <sub>ARPW</sub>              | CPLD register clear or<br>preset pulse width         |                  | 10   |      |            | + 10         |                             | ns   |

| t <sub>ARD</sub>               | CPLD array delay                                     | Any<br>macrocell |      | 11   | + 2        |              |                             | ns   |

1. Fast Slew Rate output available on PA3-PA0, PB3-PB0, and PD2-PD1. Decrement times by given amount

$t_{PD}$  for MCU address and control signals refers to delay from pins on Port 0, Port 2,  $\overline{RD}$   $\overline{WR}$ ,  $\overline{PSEN}$  and ALE to CPLD combinatorial output (80-pin package only) 2.

### Table 128. CPLD combinatorial timing (3 V devices)

| Symbol                         | Parameter                                               | Conditions       | Min. | Max. | PT<br>aloc | Turbo<br>off | Slew<br>rate <sup>(1)</sup> | Unit |

|--------------------------------|---------------------------------------------------------|------------------|------|------|------------|--------------|-----------------------------|------|

| t <sub>PD</sub> <sup>(2)</sup> | CPLD input pin/feedback to<br>CPLD combinatorial output |                  |      | 40   | + 4        | + 20         | - 6                         | ns   |

| t <sub>EA</sub>                | CPLD input to CPLD output enable                        |                  |      | 43   |            | + 20         | - 6                         | ns   |

| t <sub>ER</sub>                | CPLD input to CPLD output disable                       |                  |      | 43   |            | + 20         | - 6                         | ns   |

| t <sub>ARP</sub>               | CPLD register clear or<br>preset delay                  |                  |      | 40   |            | + 20         | - 6                         | ns   |

| t <sub>ARPW</sub>              | CPLD register clear or<br>preset pulse width            |                  | 25   |      |            | + 20         |                             | ns   |

| t <sub>ARD</sub>               | CPLD array delay                                        | Any<br>macrocell |      | 25   | + 4        |              |                             | ns   |

1. Fast Slew Rate output available on PA3-PA0, PB3-PB0, and PD2-PD1. Decrement times by given amount

$t_{PD}$  for MCU address and control signals refers to delay from pins on Port 0, Port 2,  $\overline{RD}$   $\overline{WR}$ ,  $\overline{PSEN}$  and ALE to CPLD combinatorial output (80-pin package only) 2.

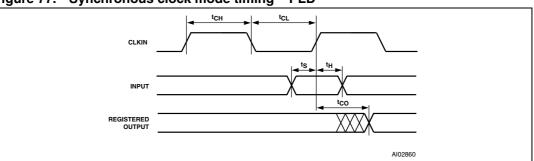

### Figure 77. Synchronous clock mode timing – PLD

| Table 129. | CPLD macrocell synchronous clock mode timing (5 V devices) |

|------------|------------------------------------------------------------|

|------------|------------------------------------------------------------|

| Symbol           | Parameter                                               | Conditions                              | Min. | Max. | PT<br>Aloc | Turbo<br>Off | Slew<br>rate <sup>(1)</sup> | Unit |

|------------------|---------------------------------------------------------|-----------------------------------------|------|------|------------|--------------|-----------------------------|------|

|                  | Maximum frequency<br>external feedback                  | 1/(t <sub>S</sub> +t <sub>CO</sub> )    |      | 40.0 |            |              |                             | MHz  |

| f <sub>MAX</sub> | Maximum frequency internal feedback (f <sub>CNT</sub> ) | 1/(t <sub>S</sub> +t <sub>CO</sub> -10) |      | 66.6 |            |              |                             | MHz  |

|                  | Maximum frequency pipelined data                        | 1/(t <sub>CH</sub> +t <sub>CL</sub> )   |      | 83.3 |            |              |                             | MHz  |

| t <sub>S</sub>   | Input setup time                                        |                                         | 12   |      | + 2        | + 10         |                             | ns   |

| t <sub>H</sub>   | Input hold time                                         |                                         | 0    |      |            |              |                             | ns   |

| t <sub>CH</sub>  | Clock high time                                         | Clock input                             | 6    |      |            |              |                             | ns   |

| t <sub>CL</sub>  | Clock low time                                          | Clock input                             | 6    |      |            |              |                             | ns   |

| t <sub>CO</sub>  | Clock to output delay                                   | Clock input                             |      | 13   |            |              | - 2                         | ns   |

| t <sub>ARD</sub> | CPLD array delay                                        | Any macrocell                           |      | 11   | + 2        |              |                             | ns   |

| t <sub>MIN</sub> | Minimum clock period <sup>(2)</sup>                     | t <sub>CH</sub> +t <sub>CL</sub>        | 12   |      |            |              |                             | ns   |

1. Fast Slew Rate output available on PA3-PA0, PB3-PB0, and PD2-PD1. Decrement times by given amount.

2. CLKIN (PD1)  $t_{CLCL} = t_{CH} + t_{CL}$ .

| Symbol             | Parameter                                                         | Min.    | Тур. | Max. | Unit   |

|--------------------|-------------------------------------------------------------------|---------|------|------|--------|

|                    | Flash Program                                                     |         | 8.5  |      | S      |

|                    | Flash Bulk Erase <sup>(1)</sup> (pre-programmed)                  |         | 3    | 30   | s      |

|                    | Flash Bulk Erase (not pre-programmed)                             |         | 5    |      | S      |

| t <sub>WHQV3</sub> | Sector Erase (pre-programmed)                                     |         | 1    | 30   | s      |

| t <sub>WHQV2</sub> | Sector Erase (not pre-programmed)                                 |         | 2.2  |      | S      |

| t <sub>WHQV1</sub> | Byte Program                                                      |         | 14   | 150  | μs     |

|                    | Program / Erase Cycles (per Sector)                               | 100,000 |      |      | cycles |

| t <sub>WHWLO</sub> | Sector Erase Time-Out                                             |         | 100  |      | μs     |

| t <sub>Q7VQV</sub> | DQ7 Valid to Output (DQ7-DQ0) Valid (Data Polling) <sup>(2)</sup> |         |      | 30   | ns     |

Table 135.

Program, Write and Erase times (5 V devices)

1. Programmed to all zero before erase.

2. The polling status, DQ7, is valid  $t_{Q7VQV}$  time units before the data byte, DQ0-DQ7, is valid for reading.

Table 136.

Program, Write and Erase times (3 V devices)

| Symbol             | Parameter                                                         | Min.    | Тур. | Max. | Unit   |

|--------------------|-------------------------------------------------------------------|---------|------|------|--------|

|                    | Flash Program                                                     |         | 8.5  |      | S      |

|                    | Flash Bulk Erase <sup>(1)</sup> (pre-programmed)                  |         | 3    | 30   | S      |

|                    | Flash Bulk Erase (not pre-programmed)                             |         | 5    |      | S      |

| t <sub>WHQV3</sub> | Sector Erase (pre-programmed)                                     |         | 1    | 30   | S      |

| t <sub>WHQV2</sub> | Sector Erase (not pre-programmed)                                 |         | 2.2  |      | S      |

| t <sub>WHQV1</sub> | Byte Program                                                      |         | 14   | 150  | μs     |

|                    | Program / Erase Cycles (per Sector)                               | 100,000 |      |      | cycles |

| t <sub>WHWLO</sub> | Sector Erase Time-Out                                             |         | 100  |      | μs     |

| t <sub>Q7VQV</sub> | DQ7 Valid to Output (DQ7-DQ0) Valid (Data Polling) <sup>(2)</sup> |         |      | 30   | ns     |

1. Programmed to all zero before erase.

2. The polling status, DQ7, is valid  $t_{Q7VQV}$  time units before the data byte, DQ0-DQ7, is valid for reading.

# 34 Part numbering

| Table 148. Ordering inf                                     | ormatio | n sch | eme |   |   |   |     |    |   |   |   |

|-------------------------------------------------------------|---------|-------|-----|---|---|---|-----|----|---|---|---|

| Example:                                                    | UPSD    | 3     | 2   | 3 | 4 | В | V – | 24 | U | 6 | Т |

| Device type                                                 |         |       |     |   |   |   |     |    |   |   |   |

| UPSD = Microcontroller PSD                                  |         |       |     |   |   |   |     |    |   |   |   |

|                                                             |         |       |     |   |   |   |     |    |   |   |   |

| Family                                                      |         |       |     |   |   |   |     |    |   |   |   |

| 3 = 8032 core                                               |         |       |     |   |   |   |     |    |   |   |   |

|                                                             |         |       |     |   |   |   |     |    |   |   |   |

| PLD size                                                    |         |       |     |   |   |   |     |    |   |   |   |

| 2 = 16 Macrocells                                           |         |       |     |   |   |   |     |    |   |   |   |

| SRAM Size                                                   |         |       |     |   |   |   |     |    |   |   |   |

| 3 = 8 Kbytes                                                |         |       |     |   |   |   |     |    |   |   |   |

|                                                             |         |       |     |   |   |   |     |    |   |   |   |

| Main Flash memory size                                      |         |       |     |   |   |   |     |    |   |   |   |

| 2 = 64 Kbytes                                               |         |       |     |   |   |   |     |    |   |   |   |

| 3 = 128 Kbytes                                              |         |       |     |   |   |   |     |    |   |   |   |

| 4 = 256 Kbytes                                              |         |       |     |   |   |   |     |    |   |   |   |

|                                                             |         |       |     |   |   |   |     |    |   |   |   |

| IP mix                                                      |         |       |     |   |   |   |     |    |   |   |   |

| A = USB, $I^2C$ , PWM, DDC, ADC, (2) UARTs                  |         |       |     |   |   |   |     |    |   |   |   |

| Supervisor (Reset Out, Reset In, LVD, WD)                   |         |       |     |   |   |   |     |    |   |   |   |

| $B = I^2C$ , PWM, DDC, ADC, (2) UARTs                       |         |       |     |   |   |   |     |    |   |   |   |

| Supervisor (Reset Out, Reset In, LVD, WD)                   |         |       |     |   |   |   |     |    |   |   |   |

| On evention welter as                                       |         |       |     |   |   |   |     |    |   |   |   |

| Operating voltage<br>blank = V <sub>CC</sub> = 4.5 to 5.5 V |         |       |     |   |   |   |     |    |   |   |   |

|                                                             |         |       |     |   |   |   |     |    |   |   |   |

| $V = V_{CC} = 3.0$ to 3.6 V                                 |         |       |     |   |   |   |     |    |   |   |   |

| Speed                                                       |         |       |     |   |   |   |     |    |   |   |   |

| Speed<br>-24 = 24 MHz                                       |         |       |     |   |   |   |     |    |   |   |   |

| -40 = 40  MHz                                               |         |       |     |   |   |   |     |    |   |   |   |

|                                                             |         |       |     |   |   |   |     |    |   |   |   |

| Package                                                     |         |       |     |   |   |   |     |    |   |   |   |

| T = 52-pin LQFP                                             |         |       |     |   |   |   |     |    |   |   |   |

| U = 80-pin LQFP                                             |         |       |     |   |   |   |     |    |   |   |   |

|                                                             |         |       |     |   |   |   |     |    |   |   |   |

| Temperature range                                           |         |       |     |   |   |   |     |    |   |   |   |

| 1 = 0 to 70°C                                               |         |       |     |   |   |   |     |    |   |   |   |

| $6 = -40$ to $85^{\circ}$ C                                 |         |       |     |   |   |   |     |    |   |   |   |

| <b>.</b>                                                    |         |       |     |   |   |   |     |    |   |   |   |

| Shipping options                                            |         |       |     |   |   |   |     |    |   |   |   |

F = ECOPACK<sup>®</sup> Package, Tape & Reel Packing

For other options, or for more information on any aspect of this device, please contact the ST Sales Office nearest you.