Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 8032                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 24MHz                                                                   |

| Connectivity               | I²C, UART/USART                                                         |

| Peripherals                | LVR, POR, PWM, WDT                                                      |

| Number of I/O              | 46                                                                      |

| Program Memory Size        | 160KB (160K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                               |

| Data Converters            | A/D 4x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-LQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/upsd3233bv-24u6 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 26.1   | Warm RESET 150                                                                            |

|----|--------|-------------------------------------------------------------------------------------------|

|    | 26.2   | I/O pin, register and PLD status at RESET 150                                             |

|    | 26.3   | Reset of Flash Memory Erase and Program Cycles 150                                        |

| 27 | Prog   | amming in-circuit using the JTAG serial interface                                         |

|    | 27.1   | Standard JTAG Signals 152                                                                 |

|    | 27.2   | JTAG extensions 152                                                                       |

|    | 27.3   | Security and Flash memory protection 153                                                  |

| 28 | Initia | delivery state                                                                            |

| 29 | AC/D   | C parameters 155                                                                          |

| 30 | Maxi   | num ratings                                                                               |

| 31 | EMC    | characteristics                                                                           |

|    | 31.1   | Functional EMS (electromagnetic susceptibility) 159                                       |

|    |        | 31.1.1 ESD                                                                                |

|    |        | 31.1.2 FTB                                                                                |

|    | 31.2   | Designing hardened software to avoid noise problems 159                                   |

|    |        | 31.2.1 Software recommendations                                                           |

|    |        | 31.2.2 Prequalification trials                                                            |

|    | 31.3   | Absolute maximum ratings (electrical sensitivity) 160                                     |

|    |        | 31.3.1 Electro-static discharge (ESD)                                                     |

|    |        | 31.3.2         Latch-up         160           21.2.2         Duramia latah un         160 |

|    |        | 31.3.3 Dynamic latch-up                                                                   |

| 32 | DC a   | nd AC parameters                                                                          |

| 33 | Pack   | age mechanical information 185                                                            |

| 34 | Part   | numbering                                                                                 |

| 35 | Revis  | ion history                                                                               |

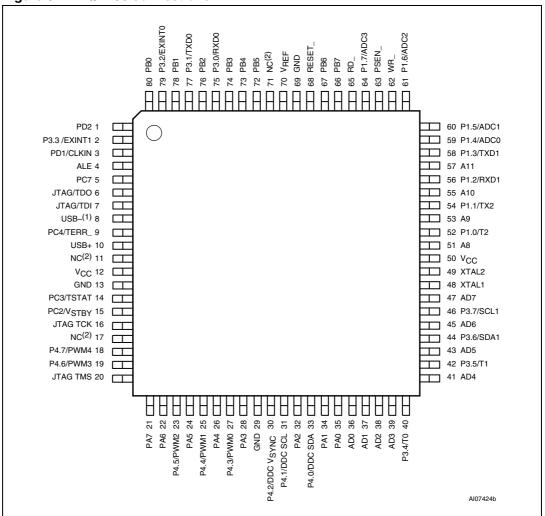

Figure 3. TQFP80 connections

1. Pull-up resistor required on pin 8 (2 k $\Omega$  for 3 V devices, 7.5 k $\Omega$  for 5 V devices) for all 82-pin devices, with or without USB function.

2. NC = Not Connected

Table 2. 80-pin package pin description

| Port | Signal | Pin | In/ | Function                                            | l         |

|------|--------|-----|-----|-----------------------------------------------------|-----------|

| pin  | name   | no. | out | Basic                                               | Alternate |

|      | AD0    | 36  | I/O | External Bus: Multiplexed<br>Address/Data bus A1/D1 |           |

|      | AD1    | 37  | I/O | Multiplexed Address/Data bus A0/D0                  |           |

|      | AD2    | 38  | I/O | Multiplexed Address/Data bus A2/D2                  |           |

|      | AD3    | 39  | I/O | Multiplexed Address/Data bus A3/D3                  |           |

|      | AD4    | 41  | I/O | Multiplexed Address/Data bus A4/D4                  |           |

|      | AD5    | 43  | I/O | Multiplexed Address/Data bus A5/D5                  |           |

|      | AD6    | 45  | I/O | Multiplexed Address/Data bus A6/D6                  |           |

| Port | Signal      | Pin | ln/ | F                    | unction                                  |

|------|-------------|-----|-----|----------------------|------------------------------------------|

| pin  | name        | no. | out | Basic                | Alternate                                |

|      | JTAG<br>TMS | 20  | I   | JTAG pin             |                                          |

|      | JTAG<br>TCK | 16  | I   | JTAG pin             |                                          |

| PC3  | TSTAT       | 14  | I/O | General I/O port pin | PLD macrocell outputs                    |

| PC4  | TERR_       | 9   | I/O | General I/O port pin | PLD inputs JTAG pins are dedicated       |

|      | JTAG<br>TDI | 7   | I   | JTAG pin             | pins                                     |

|      | JTAG<br>TDO | 6   | 0   | JTAG pin             |                                          |

| PC7  |             | 5   | I/O | General I/O port pin |                                          |

| PD1  | CLKIN       | 3   | I/O | General I/O port pin | PLD I/O<br>Clock input to PLD and<br>APD |

| PD2  |             | 1   | I/O | General I/O port pin | PLD I/O<br>Chip select to PSD module     |

| Vcc  |             | 12  |     |                      |                                          |

| Vcc  |             | 50  |     |                      |                                          |

| GND  |             | 13  |     |                      |                                          |

| GND  |             | 29  |     |                      |                                          |

| GND  |             | 69  |     |                      |                                          |

|      | USB+        | 10  |     |                      |                                          |

| NC   |             | 11  |     |                      |                                          |

| NC   |             | 17  |     |                      |                                          |

| NC   |             | 71  |     |                      |                                          |

Table 2.

80-pin package pin description (continued)

# 1.1 52-pin package I/O port

The 52-pin package members of the UPSD323xx devices have the same port pins as those of the 80-pin package except:

- Port 0 (P0.0-P0.7, external address/data bus AD0-AD7)

- Port 2 (P2.0-P2.3, external address bus A8-A11)

- Port A (PA0-PA7)

- Port D (PD2)

- Bus control signal (RD,WR,PSEN,ALE)

- Pin 5 requires a pull-up resistor (2 kΩ for 3 V devices, 7.5 kΩ for 5 V devices) for all devices, with or without USB function.

## 2 Architecture overview

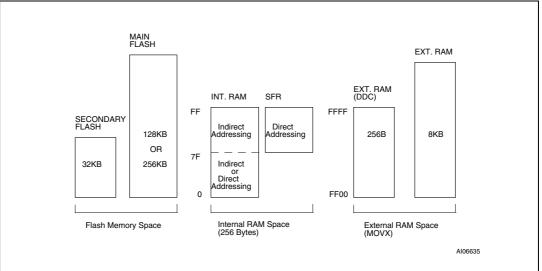

### 2.1 Memory organization

The UPSD323xx devices' standard 8032 Core has separate 64-Kbyte address spaces for Program memory and Data Memory. Program memory is where the 8032 executes instructions from. Data memory is used to hold data variables. Flash memory can be mapped in either program or data space. The Flash memory consists of two Flash memory blocks: the main Flash memory (1 or 2 Mbit) and the Secondary Flash memory (256 Kbit). Except during flash memory programming or update, Flash memory can only be read, not written to. A Page Register is used to access memory beyond the 64-Kbyte address space. Refer to the PSD module for details on mapping of the Flash memory.

The 8032 core has two types of data memory (internal and external) that can be read and written. The internal SRAM consists of 256 bytes, and includes the stack area.

The SFR (Special Function Registers) occupies the upper 128 bytes of the internal SRAM, the registers can be accessed by Direct addressing only. There are two separate blocks of external SRAM inside the UPSD325X devices: one 256-byte block is assigned for DDC data storage. Another 8 Kbytes resides in the PSD module that can be mapped to any address space defined by the user.

Figure 4. Memory map and address space

## 2.2 Registers

The 8032 has several registers; these are the Program Counter (PC), Accumulator (A), B Register (B), the Stack Pointer (SP), the Program Status Word (PSW), General purpose registers (R0 to R7), and DPTR (Data Pointer register).

#### Figure 5. 8032 MCU registers

| A<br>B<br>SP<br>PCH PCL<br>PSW<br>R0-R7<br>DPTR(DPH) DPTR(DPL) | Accumulator         B Register         Stack Pointer         Program Counter         Program Status Word         General Purpose         Register (Bank0-3)         Data Pointer Register |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                | Al06636                                                                                                                                                                                   |

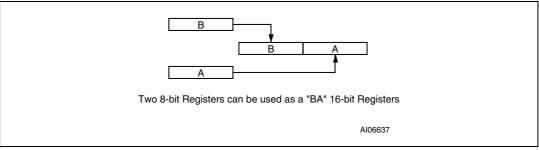

### 2.2.1 Accumulator

The Accumulator is the 8-bit general purpose register, used for data operation such as transfer, temporary saving, and conditional tests. The Accumulator can be used as a 16-bit register with B Register as shown below.

Figure 6. Configuration of BA 16-bit registers

### 2.2.2 B register

The B Register is the 8-bit general purpose register, used for an arithmetic operation such as multiply, division with Accumulator.

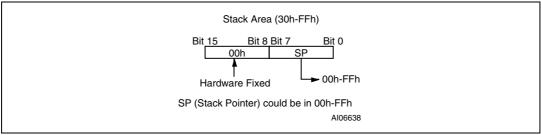

### 2.2.3 Stack pointer

The Stack Pointer Register is 8 bits wide. It is incremented before data is stored during PUSH and CALL executions. While the stack may reside anywhere in on-chip RAM, the Stack Pointer is initialized to 07h after reset. This causes the stack to begin at location 08h.

#### Figure 7. Stack pointer

# 4 MCU module description

This section provides a detail description of the MCU module system functions and Peripherals, including:

- Special function registers

- Timers/counter

- Interrupts

- PWM

- Supervisory function (LVD and Watchdog)

- USART

- Power-saving modes

- I<sup>2</sup>C Bus

- On-chip oscillator

- ADC

- I/O Ports

- USB

## 4.1 Special function registers

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in *Table 15*.

Note: In the SFRs not all of the addresses are occupied. Unoccupied addresses are not implemented on the chip. READ accesses to these addresses will in general return random data, and WRITE accesses will have no effect. User software should write '0s' to these unimplemented locations.

|                      |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B <sup>(1)</sup>     |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | F7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UISTA <sup>(1)</sup> | UIEN                                                                                                                                                                                                                              | UCON0                                                                                                                                                                                                                                                                                                                                            | UCON1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | UCON2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | USTA                                                                                                                                                                                                                  | UADR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | UDR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ACC <sup>(1)</sup>   | USCL                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       | UDT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | UDT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | E7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| S1CON <sup>(1)</sup> | S1STA                                                                                                                                                                                                                             | S1DAT                                                                                                                                                                                                                                                                                                                                            | S1ADR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S2CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | S2STA                                                                                                                                                                                                                 | S2DAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | S2ADR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PSW <sup>(1)</sup>   | S1SETUP                                                                                                                                                                                                                           | S2SETUP                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RAMBUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DDCDAT                                                                                                                                                                                                                | DDCADR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DDCCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| T2CON <sup>(1)</sup> | T2MOD                                                                                                                                                                                                                             | RCAP2L                                                                                                                                                                                                                                                                                                                                           | RCAP2H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TH2                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P4 <sup>(1)</sup>    |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IP <sup>(1)</sup>    |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P3 <sup>(1)</sup>    | PSCL0L                                                                                                                                                                                                                            | PSCL0H                                                                                                                                                                                                                                                                                                                                           | PSCL1L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PSCL1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IPA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | B7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IE <sup>(1)</sup>    |                                                                                                                                                                                                                                   | PWM4P                                                                                                                                                                                                                                                                                                                                            | PWM4W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       | WDKEY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | AF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P2 <sup>(1)</sup>    | PWMCON                                                                                                                                                                                                                            | PWM0                                                                                                                                                                                                                                                                                                                                             | PWM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PWM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PWM3                                                                                                                                                                                                                  | WDRST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IEA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SCON                 | SBUF                                                                                                                                                                                                                              | SCON2                                                                                                                                                                                                                                                                                                                                            | SBUF2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P1 <sup>(1)</sup>    | P1SFS                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                  | P3SFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P4SFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ASCL                                                                                                                                                                                                                  | ADAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ACON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                      | UISTA <sup>(1)</sup><br>ACC <sup>(1)</sup><br>S1CON <sup>(1)</sup><br>PSW <sup>(1)</sup><br>T2CON <sup>(1)</sup><br>P4 <sup>(1)</sup><br>IP <sup>(1)</sup><br>P3 <sup>(1)</sup><br>IE <sup>(1)</sup><br>P2 <sup>(1)</sup><br>SCON | UISTA <sup>(1)</sup> UIEN           ACC <sup>(1)</sup> USCL           S1CON <sup>(1)</sup> S1STA           PSW <sup>(1)</sup> S1SETUP           T2CON <sup>(1)</sup> T2MOD           P4 <sup>(1)</sup> T2MOD           P4 <sup>(1)</sup> T2MOD           IP <sup>(1)</sup> PSCLOL           IE <sup>(1)</sup> PSCLOL           SCON         SBUF | Image: Constraint of the system         Image: Constraint of the system           UISTA <sup>(1)</sup> UIEN         UCON0           ACC <sup>(1)</sup> USCL         S1DAT           S1CON <sup>(1)</sup> S1SETUP         S2SETUP           PSW <sup>(1)</sup> T2MOD         RCAP2L           P4 <sup>(1)</sup> T2MOD         RCAP2L           IP <sup>(1)</sup> PSCL0L         PSCL0H           IS <sup>(1)</sup> PSCL0L         PSCL0H           IE <sup>(1)</sup> PWMCON         PWM4P           P2 <sup>(1)</sup> SBUF         SCON2 | UISTA <sup>(1)</sup> UIEN         UCON0         UCON1           ACC <sup>(1)</sup> USCL              S1CON <sup>(1)</sup> S1STA         S1DAT         S1ADR           PSW <sup>(1)</sup> S1SETUP         S2SETUP            T2CON <sup>(1)</sup> T2MOD         RCAP2L         RCAP2H           P4 <sup>(1)</sup> T2MOD         RCAP2L         PCAP2H           IP <sup>(1)</sup> PSCL0L         PSCL0H         PSCL1L           IE <sup>(1)</sup> PSCL0L         PWM4P         PWM4W           P2 <sup>(1)</sup> PWMCON         PWM0         PWM1           SCON         SBUF         SCON2         SBUF2 | UISTA <sup>(1)</sup> UIEN         UCON0         UCON1         UCON2           ACC <sup>(1)</sup> USCL                                                                                                               < | $I_{1}$ < | $I_{1}$ $I_{1}$ $I_{1}$ $I_{1}$ $I_{1}$ $I_{1}$ $I_{1}$ UISTA <sup>(1)</sup> UIEN         UCON0         UCON1         UCON2         USTA         UADR           ACC <sup>(1)</sup> USCL          I         S1         UDT1         UDT1           S1CON <sup>(1)</sup> S1STA         S1DAT         S1ADR         S2CON         S2STA         S2DAT           PSW <sup>(1)</sup> S1SETUP         S2SETUP         RAMBUF         DDCDAT         DDCADR           T2CON <sup>(1)</sup> T2MOD         RCAP2L         RCAP2H         TL2         TH2         DCAT           P4 <sup>(1)</sup> T2MOD         RCAP2L         RCAP2H         TL2         TH2         I           P4 <sup>(1)</sup> T2MOD         RCAP2H         PSCL         I         I         I           P3 <sup>(1)</sup> PSCL0L         PSCL0H         PSCL1L         PSCL1H         I         I           IE <sup>(1)</sup> PSCL0L         PSCL0H         PSCL1L         PSCL1H         I         I           IE <sup>(1)</sup> PWMCON         PWM4P         PWM4W         I         I         WDRST           P2 <sup>(1)</sup> PWMCON         PWM0 | -1 $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ $-1$ <t< td=""></t<> |

| Table 15. | SFR | memory | map |

|-----------|-----|--------|-----|

|-----------|-----|--------|-----|

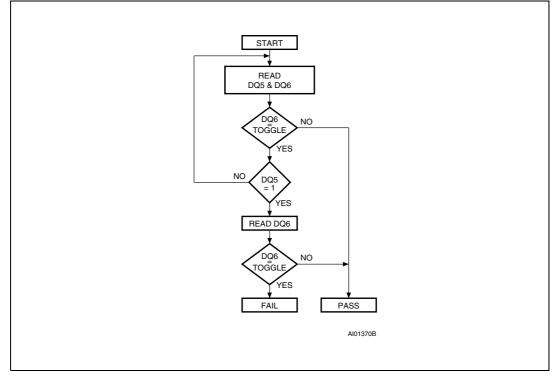

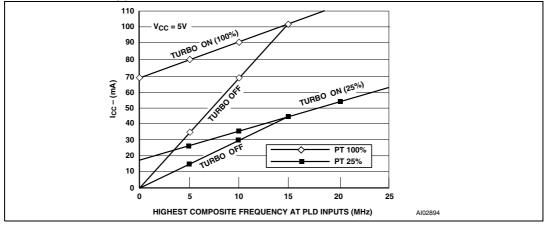

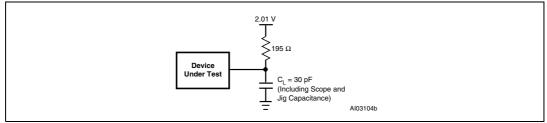

| CSIOP          | Deviator                    |   |   | В | it regist | ter nam | e |   |   | Reset<br>value | Comments                     |