Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 30 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, LVD, POR, PWM, WDT             |

| Number of I/O              | 68                                                                              |

| Program Memory Size        | 66KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 1K x 8                                                                          |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-TQFP                                                                         |

| Supplier Device Package    | 80-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f5013t-30i-ptg |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

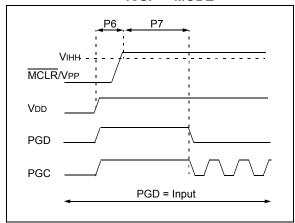

#### 5.2 Entering Enhanced ICSP Mode

The Enhanced ICSP mode is entered by holding PGC and PGD high, and then raising MCLR/VPP to VIHH (high voltage), as illustrated in Figure 5-2. In this mode, the code memory, data EEPROM and Configuration bits can be efficiently programmed using the programming executive commands that are serially transferred using PGC and PGD.

#### FIGURE 5-2: ENTERING ENHANCED ICSP™ MODE

- Note 1: The sequence that places the device into Enhanced ICSP mode places all unused I/Os in the high-impedance state.

- 2: Before entering Enhanced ICSP mode, clock switching must be disabled using ICSP, by programming the FCKSM<1:0> bits in the FOSC Configuration register to '11' or '10'.

- **3:** When in Enhanced ICSP mode, the SPI output pin (SDO1) will toggle while the device is being programmed.

#### 5.3 Chip Erase

Before a chip can be programmed, it must be erased. The Bulk Erase command (ERASEB) is used to perform this task. Executing this command with the MS command field set to 0x3 erases all code memory, data EEPROM and code-protect Configuration bits. The Chip Erase process sets all bits in these three memory regions to '1'.

Since non-code-protect Configuration bits cannot be erased, they must be manually set to '1' using multiple PROGC commands. One PROGC command must be sent for each Configuration register (see Section 5.7 "Configuration Bits Programming").

If Advanced Security features are enabled, then individual Segment Erase operations would need to be performed, depending on which segment needs to be programmed at a given stage of system programming. The user should have the flexibility to select specific segments for programming.

| Note: | The Device ID registers cannot be erased.  |

|-------|--------------------------------------------|

|       | These registers remain intact after a Chip |

|       | Erase is performed.                        |

#### 5.4 Blank Check

The term "Blank Check" means to verify that the device has been successfully erased and has no programmed memory cells. A blank or erased memory cell reads as '1'. The following memories must be blank checked:

- · All implemented code memory

- · All implemented data EEPROM

- · All Configuration bits (for their default value)

The Device ID registers (0xFF0000:0xFF0002) can be ignored by the Blank Check since this region stores device information that cannot be erased. Additionally, all unimplemented memory space should be ignored from the Blank Check.

The QBLANK command is used for the Blank Check. It determines if the code memory and data EEPROM are erased by testing these memory regions. A 'BLANK' or 'NOT BLANK' response is returned. The READD command is used to read the Configuration registers. If it is determined that the device is not blank, it must be erased (see Section 5.3 "Chip Erase") before attempting to program the chip.

#### 5.5 Code Memory Programming

#### 5.5.1 OVERVIEW

The Flash code memory array consists of 512 rows of thirty-two, 24-bit instructions. Each panel stores 16K instruction words, and each dsPIC30F device has either 1, 2 or 3 memory panels (see Table 5-2).

| Device        | Code Size<br>(24-bit<br>Words) | Number<br>of<br>Rows | Number<br>of<br>Panels |

|---------------|--------------------------------|----------------------|------------------------|

| dsPIC30F2010  | 4K                             | 128                  | 1                      |

| dsPIC30F2011  | 4K                             | 128                  | 1                      |

| dsPIC30F2012  | 4K                             | 128                  | 1                      |

| dsPIC30F3010  | 8K                             | 256                  | 1                      |

| dsPIC30F3011  | 8K                             | 256                  | 1                      |

| dsPIC30F3012  | 8K                             | 256                  | 1                      |

| dsPIC30F3013  | 8K                             | 256                  | 1                      |

| dsPIC30F3014  | 8K                             | 256                  | 1                      |

| dsPIC30F4011  | 16K                            | 512                  | 1                      |

| dsPIC30F4012  | 16K                            | 512                  | 1                      |

| dsPIC30F4013  | 16K                            | 512                  | 1                      |

| dsPIC30F5011  | 22K                            | 704                  | 2                      |

| dsPIC30F5013  | 22K                            | 704                  | 2                      |

| dsPIC30F5015  | 22K                            | 704                  | 2                      |

| dsPIC30F5016  | 22K                            | 704                  | 2                      |

| dsPIC30F6010  | 48K                            | 1536                 | 3                      |

| dsPIC30F6010A | 48K                            | 1536                 | 3                      |

| dsPIC30F6011  | 44K                            | 1408                 | 3                      |

| dsPIC30F6011A | 44K                            | 1408                 | 3                      |

| dsPIC30F6012  | 48K                            | 1536                 | 3                      |

| dsPIC30F6012A | 48K                            | 1536                 | 3                      |

| dsPIC30F6013  | 44K                            | 1408                 | 3                      |

| dsPIC30F6013A | 44K                            | 1408                 | 3                      |

| dsPIC30F6014  | 48K                            | 1536                 | 3                      |

| dsPIC30F6014A | 48K                            | 1536                 | 3                      |

| dsPIC30F6015  | 48K                            | 1536                 | 3                      |

TABLE 5-2: DEVICE CODE MEMORY SIZE

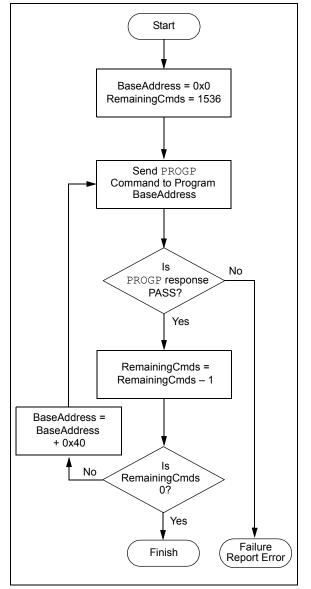

#### 5.5.2 PROGRAMMING METHODOLOGY

Code memory is programmed with the PROGP command. PROGP programs one row of code memory to the memory address specified in the command. The number of PROGP commands required to program a device depends on the number of rows that must be programmed in the device.

A flowchart for programming of code memory is illustrated in Figure 5-3. In this example, all 48K instruction words of a dsPIC30F6014A device are programmed. First, the number of commands to send (called 'RemainingCmds' in the flowchart) is set to 1536 and the destination address (called 'BaseAddress') is set to '0'. Next, one row in the device is programmed with a PROGP command. Each PROGP command contains data for one row of code memory of the dsPIC30F6014A. After the first command is processed successfully, 'RemainingCmds' is decremented by 1 and compared to 0. Since there are more PROGP commands to send, 'BaseAddress' is incremented by 0x40 to point to the next row of memory.

On the second PROGP command, the second row of each memory panel is programmed. This process is repeated until the entire device is programmed. No special handling must be performed when a panel boundary is crossed.

#### FLOWCHART FOR PROGRAMMING dsPIC30F6014A CODE MEMORY

#### 5.5.3 PROGRAMMING VERIFICATION

Once code memory is programmed, the contents of memory can be verified to ensure that programming was successful. Verification requires code memory to be read back and compared against the copy held in the programmer's buffer.

The READP command can be used to read back all the programmed code memory.

Alternatively, you can have the programmer perform the verification once the entire device is programmed using a checksum computation, as described in Section 6.8 "Checksum Computation".

#### 5.6 Data EEPROM Programming

#### 5.6.1 OVERVIEW

The panel architecture for the data EEPROM memory array consists of 128 rows of sixteen 16-bit data words. Each panel stores 2K words. All devices have either one or no memory panels. Devices with data EEPROM provide either 512 words, 1024 words or 2048 words of memory on the one panel (see Table 5-3).

TABLE 5-3:DATA EEPROM SIZE

| TABLE 5-5. DATA LEFRON SIZE |                             |                   |  |  |

|-----------------------------|-----------------------------|-------------------|--|--|

| Device                      | Data EEPROM<br>Size (Words) | Number of<br>Rows |  |  |

| dsPIC30F2010                | 512                         | 32                |  |  |

| dsPIC30F2011                | 0                           | 0                 |  |  |

| dsPIC30F2012                | 0                           | 0                 |  |  |

| dsPIC30F3010                | 512                         | 32                |  |  |

| dsPIC30F3011                | 512                         | 32                |  |  |

| dsPIC30F3012                | 512                         | 32                |  |  |

| dsPIC30F3013                | 512                         | 32                |  |  |

| dsPIC30F3014                | 512                         | 32                |  |  |

| dsPIC30F4011                | 512                         | 32                |  |  |

| dsPIC30F4012                | 512                         | 32                |  |  |

| dsPIC30F4013                | 512                         | 32                |  |  |

| dsPIC30F5011                | 512                         | 32                |  |  |

| dsPIC30F5013                | 512                         | 32                |  |  |

| dsPIC30F5015                | 512                         | 32                |  |  |

| dsPIC30F5016                | 512                         | 32                |  |  |

| dsPIC30F6010                | 2048                        | 128               |  |  |

| dsPIC30F6010A               | 2048                        | 128               |  |  |

| dsPIC30F6011                | 1024                        | 64                |  |  |

| dsPIC30F6011A               | 1024                        | 64                |  |  |

| dsPIC30F6012                | 2048                        | 128               |  |  |

| dsPIC30F6012A               | 2048                        | 128               |  |  |

| dsPIC30F6013                | 1024                        | 64                |  |  |

| dsPIC30F6013A               | 1024                        | 64                |  |  |

| dsPIC30F6014                | 2048                        | 128               |  |  |

| dsPIC30F6014A               | 2048                        | 128               |  |  |

| dsPIC30F6015                | 2048                        | 128               |  |  |

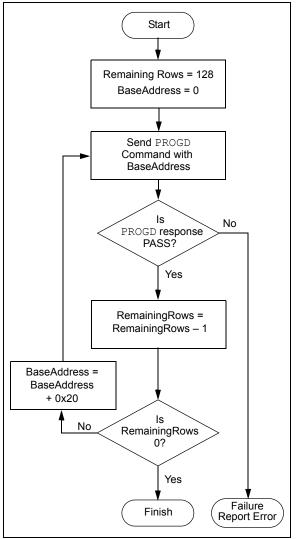

#### 5.6.2 PROGRAMMING METHODOLOGY

The programming executive uses the PROGD command to program the data EEPROM. Figure 5-4 illustrates the flowchart of the process. Firstly, the number of rows to program (RemainingRows) is based on the device size, and the destination address (DestAddress) is set to '0'. In this example, 128 rows (2048 words) of data EEPROM will be programmed.

The first PROGD command programs the first row of data EEPROM. Once the command completes successfully, 'RemainingRows' is decremented by 1 and compared with 0. Since there are 127 more rows to program, 'BaseAddress' is incremented by 0x20 to point to the next row of data EEPROM. This process is then repeated until all 128 rows of data EEPROM are programmed.

FIGURE 5-4:

#### FLOWCHART FOR PROGRAMMING dsPIC30F6014A DATA EEPROM

#### TABLE 5-6: FOSC CONFIGURATION BITS DESCRIPTION FOR dsPIC30F2011/2012, dsPIC30F3010/3011/3012/3013/3014, dsPIC30F4013, dsPIC30F5015/5016, dsPIC30F6010A/6011A/6012A/6013A/6014A AND dsPIC30F6015

|     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OSC | <b>Clock Switching Mode</b><br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| OSC | Oscillator Source Selection on POR<br>111 = Primary Oscillator<br>110 = Reserved<br>101 = Reserved<br>100 = Reserved<br>011 = Reserved<br>010 = Internal Low-Power RC Oscillator<br>001 = Internal Fast RC Oscillator (no PLL)<br>000 = Low-Power 32 kHz Oscillator (Timer1 Oscillator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| DSC | Primary Oscillator Mode (when FOS<2:0> = 111b)<br>11xxx = Reserved (do not use)<br>10111 = HS/3 w/PLL 16X – HS/3 crystal oscillator with 16X PLL<br>(10 MHz-25 MHz crystal)<br>10101 = HS/3 w/PLL 8X – HS/3 crystal oscillator with 8X PLL<br>(10 MHz-25 MHz crystal)<br>10101 = HS/3 w/PLL 4X – HS/3 crystal oscillator with 4X PLL<br>(10 MHz-25 MHz crystal)<br>10100 = Reserved (do not use)<br>10011 = HS/2 w/PLL 16X – HS/2 crystal oscillator with 16X PLL<br>(10 MHz-25 MHz crystal)<br>10010 = HS/2 w/PLL 8X – HS/2 crystal oscillator with 8X PLL<br>(10 MHz-25 MHz crystal)<br>10001 = HS/2 w/PLL 8X – HS/2 crystal oscillator with 8X PLL<br>(10 MHz-25 MHz crystal)<br>10001 = HS/2 w/PLL 4X – HS/2 crystal oscillator with 4X PLL<br>(10 MHz-25 MHz crystal)<br>10000 = Reserved (do not use)<br>01111 = ECIO w/PLL 16x – External clock with 16x PLL. OSC2 pin is I/O<br>01101 = ECIO w/PLL 16x – External clock with 8x PLL. OSC2 pin is I/O<br>01101 = ECIO w/PLL 4x – External clock with 4x PLL. OSC2 pin is I/O<br>01101 = ECIO w/PLL 4x – External clock with 4x PLL. OSC2 pin is I/O<br>01101 = ECIO w/PLL 8x – Internal fast RC oscillator with 8x PLL. OSC2 pin is I/O<br>01010 = Reserved (do not use)<br>01011 = Reserved (do not use)<br>01011 = XT w/PLL 16X – XT crystal oscillator with 16X PLL<br>0110 = XT w/PLL 4X – XT crystal oscillator with 8X PLL<br>0110 = XT w/PLL 4X – XT crystal oscillator with 8X PLL<br>0110 = XT w/PLL 4X – XT crystal oscillator with 8X PLL<br>0110 = TRC w/PLL 4X – Internal fast RC oscillator with 8x PLL. OSC2 pin is I/O<br>0111 = FRC w/PLL 4X – XT crystal oscillator with 8X PLL<br>0100 = Reserved (do not use)<br>00011 = FRC w/PLL 4X – Internal fast RC oscillator with 8x PLL. OSC2 pin is I/O<br>00010 = Reserved (do not use)<br>00011 = FRC w/PLL 4X – Internal fast RC oscillator with 4x PLL. OSC2 pin is I/O<br>00010 = Reserved (do not use) |  |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Bit Field | Register | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EBS       | FBS      | Boot Segment Data EEPROM Code Protection (only present in dsPIC30F5011/<br>5013/6010A/6011A/6012A/6013A/6014A/6015)<br>1 = No Data EEPROM is reserved for Boot Segment<br>0 = 128 bytes of Data EEPROM are reserved for Boot Segment in dsPIC30F5011/<br>5013, and 256 bytes in dsPIC30F6010A/6011A/6012A/6013A/6014A/6015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BSS<2:0>  | FBS      | Boot Segment Program Memory Code Protection (only present in<br>dsPIC30F5011/5013/6010A/6011A/6012A/6013A/6014A/6015)         111 = No Boot Segment         110 = Standard security; Small-sized Boot Program Flash<br>[Boot Segment starts after BS and ends at 0x0003FF]         101 = Standard security; Medium-sized Boot Program Flash<br>[Boot Segment starts after BS and ends at 0x0007FF]         100 = Standard security; Large-sized Boot Program Flash<br>[Boot Segment starts after BS and ends at 0x0007FF]         100 = Standard security; Large-sized Boot Program Flash<br>[Boot Segment starts after BS and ends at 0x001FF]         011 = No Boot Segment         010 = High security; Small-sized Boot Program Flash<br>[Boot Segment starts after BS and ends at 0x0003FF]         011 = High security; Medium-sized Boot Program Flash<br>[Boot Segment starts after BS and ends at 0x0003FF]         001 = High security; Medium-sized Boot Program Flash<br>[Boot Segment starts after BS and ends at 0x0007FF]         001 = High security; Large-sized Boot Program Flash<br>[Boot Segment starts after BS and ends at 0x0007FF]         000 = High security; Large-sized Boot Program Flash<br>[Boot Segment starts after BS and ends at 0x0007FF]         000 = High security; Large-sized Boot Program Flash<br>[Boot Segment starts after BS and ends at 0x0007FF] |

| BWRP      | FBS      | Boot Segment Program Memory Write Protection (only present in<br>dsPIC30F5011/5013/6010A/6011A/6012A/6013A/6014A/6015)<br>1 = Boot Segment program memory is not write-protected<br>0 = Boot Segment program memory is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RSS<1:0>  | FSS      | Secure Segment Data RAM Code Protection (only present in dsPIC30F5011/         5013/6010A/6011A/6012A/6013A/6014A/6015)         11 = No Data RAM is reserved for Secure Segment         10 = Small-sized Secure RAM         [(256 - N) bytes of RAM are reserved for Secure Segment]         01 = Medium-sized Secure RAM         [(768 - N) bytes of RAM are reserved for Secure Segment in dsPIC30F5011/         5013, and (2048 - N) bytes in dsPIC30F6010A/6011A/6012A/6013A/6014A/         6015]         00 = Large-sized Secure RAM         [(1024 - N) bytes of RAM are reserved for Secure Segment in dsPIC30F5011/         5013, and (4096 - N) bytes in dsPIC30F6010A/6011A/6012A/6013A/6014A/         6015]         where N = Number of bytes of RAM reserved for Boot Sector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ESS<1:0>  | FSS      | <ul> <li>Secure Segment Data EEPROM Code Protection (only present in dsPIC30F5011/5013/6010A/6011A/6012A/6013A/6014A/6015)</li> <li>11 = No Data EEPROM is reserved for Secure Segment</li> <li>10 = Small-sized Secure Data EEPROM <ul> <li>[(128 – N) bytes of Data EEPROM are reserved for Secure Segment in dsPIC30F5011/5013, and (256 – N) bytes in dsPIC30F6010A/6011A/6012A/6013A/6014A/6015]</li> </ul> </li> <li>01 = Medium-sized Secure Data EEPROM <ul> <li>[(256 – N) bytes of Data EEPROM are reserved for Secure Segment in dsPIC30F5011/5013, and (512 – N) bytes in dsPIC30F6010A/6011A/6012A/6013A/6014A/6015]</li> </ul> </li> <li>01 = Large-sized Secure Data EEPROM <ul> <li>[(512 – N) bytes of Data EEPROM</li> <li>[(512 – N) bytes of Data EEPROM are reserved for Secure Segment in dsPIC30F5011/5013, (1024 – N) bytes in dsPIC30F6011A/6013A, and (2048 – N) bytes in dsPIC30F6010A/6012A/6014A/6015]</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### TABLE 5-7: CONFIGURATION BITS DESCRIPTION (CONTINUED)

| TABLE 5-7: | CONFIGURATION BITS DESCRIPTION (CONTINUED) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit Field  | Register                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| SSS<2:0>   | FSS                                        | <ul> <li>Secure Segment Program Memory Code Protection (only present in dsPIC30F5011/5013/6010A/6011A/6012A/6013A/6014A/6015)</li> <li>111 = No Secure Segment</li> <li>110 = Standard security; Small-sized Secure Program Flash [Secure Segment starts after BS and ends at 0x001FFF]</li> <li>101 = Standard security; Medium-sized Secure Program Flash [Secure Segment starts after BS and ends at 0x003FFF]</li> <li>100 = Standard security; Large-sized Secure Program Flash [Secure Segment starts after BS and ends at 0x007FFF]</li> <li>011 = No Secure Segment</li> <li>010 = High security; Small-sized Secure Program Flash [Secure Segment starts after BS and ends at 0x007FFF]</li> <li>011 = No Secure Segment</li> <li>010 = High security; Medium-sized Secure Program Flash [Secure Segment starts after BS and ends at 0x001FFF]</li> <li>001 = High security; Medium-sized Secure Program Flash [Secure Segment starts after BS and ends at 0x003FFF]</li> <li>001 = High security; Medium-sized Secure Program Flash [Secure Segment starts after BS and ends at 0x003FFF]</li> <li>001 = High security; Medium-sized Secure Program Flash [Secure Segment starts after BS and ends at 0x003FFF]</li> <li>001 = High security; Large-sized Secure Program Flash [Secure Segment starts after BS and ends at 0x003FFF]</li> </ul> |  |  |

| SWRP       | FSS                                        | Secure Segment Program Memory Write Protection (only present in<br>dsPIC30F5011/5013/6010A/6011A/6012A/6013A/6014A/6015)<br>1 = Secure Segment program memory is not write-protected<br>0 = Secure program memory is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| GSS<1:0>   | FGS                                        | General Segment Program Memory Code Protection (only present in<br>dsPIC30F5011/5013/6010A/6011A/6012A/6013A/6014A/6015)<br>11 = Code protection is disabled<br>10 = Standard security code protection is enabled<br>0x = High security code protection is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| GCP        | FGS                                        | General Segment Program Memory Code Protection (present in all devices<br>except dsPIC30F5011/5013/6010A/6011A/6012A/6013A/6014A/6015)<br>1 = General Segment program memory is not code-protected<br>0 = General Segment program memory is code-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| GWRP       | FGS                                        | General Segment Program Memory Write Protection<br>1 = General Segment program memory is not write-protected<br>0 = General Segment program memory is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| BKBUG      | FICD                                       | <b>Debugger/Emulator Enable</b><br>1 = Device will reset into Operational mode<br>0 = Device will reset into Debug/Emulation mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| COE        | FICD                                       | Debugger/Emulator Enable<br>1 = Device will reset into Operational mode<br>0 = Device will reset into Clip-on Emulation mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| ICS<1:0>   | FICD                                       | ICD Communication Channel Select<br>11 = Communicate on PGC/EMUC and PGD/EMUD<br>10 = Communicate on EMUC1 and EMUD1<br>01 = Communicate on EMUC2 and EMUD2<br>00 = Communicate on EMUC3 and EMUD3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| RESERVED   | FBS, FSS, FGS                              | Reserved (read as '1', write as '1')                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| —          | All                                        | Unimplemented (read as '0', write as '0')                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

#### TABLE 5-7: CONFIGURATION BITS DESCRIPTION (CONTINUED)

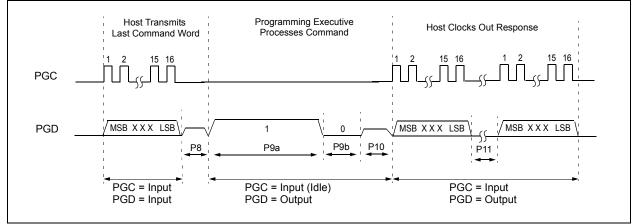

clocked out. The programmer can begin to clock out the response 20  $\mu$ sec after PGD is brought low, and it must provide the necessary amount of clock pulses to receive the entire response from the programming executive.

Once the entire response is clocked out, the programmer should terminate the clock on PGC until it is time to send another command to the programming executive. This protocol is illustrated in Figure 7-2.

### 7.3 SPI Rate

In Enhanced ICSP mode, the dsPIC30F operates from the fast internal RC oscillator, which has a nominal frequency of 7.37 MHz. This oscillator frequency yields an effective system clock frequency of 1.84 MHz. Since the SPI module operates in Slave mode, the programmer must limit the SPI clock rate to a frequency no greater than 1 MHz.

| Note: | If the programmer provides the SPI with a<br>clock faster than 1 MHz, the behavior of |  |  |  |

|-------|---------------------------------------------------------------------------------------|--|--|--|

|       | the programming executive will be unpredictable.                                      |  |  |  |

### 7.4 Time Outs

The programming executive uses no Watchdog Timer or time out for transmitting responses to the programmer. If the programmer does not follow the flow control mechanism using PGC, as described in Section 7.2 "Communication Interface and Protocol", it is possible that the programming executive will behave unexpectedly while trying to send a response to the programmer. Since the programming executive has no time out, it is imperative that the programmer correctly follow the described communication protocol.

As a safety measure, the programmer should use the command time outs identified in Table 8-1. If the command time out expires, the programmer should reset the programming executive and start programming the device again.

#### FIGURE 7-2: PROGRAMMING EXECUTIVE – PROGRAMMER COMMUNICATION PROTOCOL

# dsPIC30F Flash Programming Specification

#### 8.5.7 ERASEB COMMAND

| 15 12  | 11       | 2 | 0 |

|--------|----------|---|---|

| Opcode | Length   |   |   |

|        | Reserved | M | S |

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Opcode   | 0x7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Length   | 0x2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Reserved | 0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MS       | Select memory to erase:<br>0x0 = All Code in General Segment<br>0x1 = All Data EEPROM in General Segment $0x2 = All Code and Data EEPROM inGeneral Segment, interrupt vectors andFGS Configuration register0x3 = Full Chip Erase0x4 = All Code and Data EEPROM inBoot, Secure and General Segments,and FBS, FSS and FGS Configurationregisters0x5 = All Code and Data EEPROM inSecure and General Segments, andFSS and FGS Configuration registers0x6 = All Data EEPROM in$ Boot<br>Segment<br>0x7 = All Data EEPROM in Secure<br>Segment |

The ERASEB command performs a Bulk Erase. The MS field selects the memory to be bulk erased, with options for erasing Code and/or Data EEPROM in individual memory segments.

When Full Chip Erase is selected, the following memory regions are erased:

- All code memory (even if code-protected)

- All data EEPROM

- All code-protect Configuration registers

Only the executive code memory, Unit ID, device ID and Configuration registers that are not code-protected remain intact after a Chip Erase.

#### Expected Response (2 words):

0x1700 0x0002

> Note: A Full Chip Erase cannot be performed in low-voltage programming systems (VDD less than 4.5 volts). ERASED and ERASEP must be used to erase code memory, executive memory and data memory. Alternatively, individual Segment Erase operations may be performed.

#### 8.5.8 ERASED COMMAND

| 15       | 12  | 11 | 8 | 7        | 0 |

|----------|-----|----|---|----------|---|

| Орс      | ode |    |   | Length   |   |

| Num_Rows |     |    |   | Addr_MSB |   |

| Addr_LS  |     |    |   |          |   |

| Field    | Description                          |

|----------|--------------------------------------|

| Opcode   | 0x8                                  |

| Length   | 0x3                                  |

| Num_Rows | Number of rows to erase (max of 128) |

| Addr_MSB | MSB of 24-bit base address           |

| Addr_LS  | LS 16 bits of 24-bit base address    |

The ERASED command erases the specified number of rows of data EEPROM from the specified base address. The specified base address must be a multiple of 0x20. Since the data EEPROM is mapped to program space, a 24-bit base address must be specified.

After the erase is performed, all targeted bytes of data EEPROM will contain 0xFF.

Expected Response (2 words): 0x1800 0x0002

Note: The ERASED command cannot be used to erase the Configuration registers or device ID. Code-protect Configuration registers can only be erased with the ERASEB command, while the device ID is read-only. Table 11-4 shows the ICSP programming process for bulk-erasing program memory. This process includes the ICSP command code, which must be transmitted (for each instruction) to the Least Significant bit first using the PGC and PGD pins (see Figure 11-2).

If an individual Segment Erase operation is required, the NVMCON value must be replaced by the value for the corresponding Segment Erase operation.

| Note: | Program memory must be erased before |

|-------|--------------------------------------|

|       | writing any data to program memory.  |

# TABLE 11-4:SERIAL INSTRUCTION EXECUTION FOR BULK ERASING PROGRAM MEMORY<br/>(ONLY IN NORMAL-VOLTAGE SYSTEMS)

| 08A<br>80A                                                    | GOTO 0x100<br>GOTO 0x100<br>NOP<br>the FBS Configuration register. <sup>(1)</sup><br>MOV #0x4008, W10<br>MOV W10, NVMCON |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 00<br>000<br>DN to program<br>08A<br>00A<br><b>TBLPAG and</b> | GOTO 0×100<br>NOP<br>the FBS Configuration register. <sup>(1)</sup><br>MOV #0×4008, W10                                  |

| DN to program                                                 | NOP<br>the FBS Configuration register. <sup>(1)</sup><br>MOV #0x4008, W10                                                |

| DN to program                                                 | the FBS Configuration register. <sup>(1)</sup>                                                                           |

| BA<br>BOA<br>CHANNE TBLPAG and                                | MOV #0x4008, W10                                                                                                         |

| BOA<br>TBLPAG and                                             |                                                                                                                          |

| e TBLPAG and                                                  | MOV W10, NVMCON                                                                                                          |

|                                                               |                                                                                                                          |

| '80                                                           | write pointer (W7) for TBLWT instruction for Configuration register. <sup>(1)</sup>                                      |

|                                                               | MOV #0xF8, W0                                                                                                            |

| .90                                                           | MOV W0, TBLPAG                                                                                                           |

| 67                                                            | MOV #0x6, W7                                                                                                             |

| onfiguration Re                                               | egister data to W6. <sup>(1)</sup>                                                                                       |

| 300                                                           | CLR W6                                                                                                                   |

| 000                                                           | NOP                                                                                                                      |

| onfiguration Re                                               | egister write latch. Advance W7 to point to next Configuration register. <sup>(1)</sup>                                  |

| 386                                                           | TBLWTL W6, [W7++]                                                                                                        |

| NVMCON for p                                                  | programming the Configuration register. <sup>(1)</sup>                                                                   |

| 58                                                            | MOV #0x55, W8                                                                                                            |

| A9                                                            | MOV #0xAA, W9                                                                                                            |

| 338                                                           | MOV W8, NVMKEY                                                                                                           |

| 339                                                           | MOV W9, NVMKEY                                                                                                           |

| orogramming c                                                 | ycle. <sup>(1)</sup>                                                                                                     |

| 61                                                            | BSET NVMCON, #WR                                                                                                         |

| 000                                                           | NOP                                                                                                                      |

| 000                                                           | NOP                                                                                                                      |

|                                                               | Externally time 2 ms                                                                                                     |

| 000                                                           | NOP                                                                                                                      |

| 000                                                           | NOP                                                                                                                      |

| 61                                                            | BCLR NVMCON, #WR                                                                                                         |

| 000                                                           | NOP                                                                                                                      |

| 000                                                           | NOP                                                                                                                      |

| os 5-7 one time                                               | e to program 0x0000 to RESERVED2 Configuration register. <sup>(1)</sup>                                                  |

| VICON to erase                                                | e all Program Memory.                                                                                                    |

| 'FA                                                           | MOV #0x407F, W10                                                                                                         |

| 30A                                                           | MOV W10, NVMCON                                                                                                          |

| O<br>OS<br>M                                                  | 5-7 one time<br>CON to erase                                                                                             |

**Note 1:** Steps 2-8 are only required for the dsPIC30F5011/5013 devices. These steps may be skipped for all other devices in the dsPIC30F family.

#### 11.6 Erasing Program Memory in Low-Voltage Systems

The procedure for erasing program memory (all code memory and data memory) in low-voltage systems (with VDD between 2.5 volts and 4.5 volts) is quite different than the procedure for erasing program memory in normal-voltage systems. Instead of using a Bulk Erase operation, each region of memory must be individually erased by row. Namely, all of the code memory, executive memory and data memory must be erased one row at a time. This procedure is detailed in Table 11-5.

Due to security restrictions, the FBS, FSS and FGS register cannot be erased in low-voltage systems. Once any bits in the FGS register are programmed to '0', they can only be set back to '1' by performing a Bulk Erase in a normal-voltage system. Alternatively, a Segment Erase operation can be performed instead of a Bulk Erase.

Normal-voltage systems can also be used to erase program memory as shown in Table 11-5. However, since this method is more time-consuming and does not clear the code-protect bits, it is not recommended.

Note: Program memory must be erased before writing any data to program memory.

# TABLE 11-5:SERIAL INSTRUCTION EXECUTION FOR ERASING PROGRAM MEMORY<br/>(EITHER IN LOW-VOLTAGE OR NORMAL-VOLTAGE SYSTEMS)

| Command<br>(Binary)                  | Data<br>(Hexadecimal)                          | Description                                                                                                                       |

|--------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Step 1: Exit th                      | e Reset vector.                                |                                                                                                                                   |

| 0000                                 | 040100                                         | GOTO 0x100                                                                                                                        |

| 0000                                 | 040100<br>000000                               | GOTO 0x100<br>NOP                                                                                                                 |

|                                      |                                                | /MADRU to erase code memory and initialize W7 for row address updates.                                                            |

| 0000                                 | EB0300<br>883B16                               | CLR W6<br>MOV W6, NVMADR                                                                                                          |

| 0000<br>0000                         | 883B26<br>200407                               | MOV W6, NVMADRU<br>MOV #0x40, W7                                                                                                  |

| Step 3: Set N                        | VMCON to erase 1 r                             | ow of code memory.                                                                                                                |

| 0000<br>0000                         | 24071A<br>883B0A                               | MOV #0x4071, W10<br>MOV W10, NVMCON                                                                                               |

| Step 4: Unloc                        | k the NVMCON to e                              | rase 1 row of code memory.                                                                                                        |

| 0000<br>0000<br>0000<br>0000         | 200558<br>883B38<br>200AA9<br>883B39           | MOV #0x55, W8<br>MOV W8, NVMKEY<br>MOV #0xAA, W9<br>MOV W9, NVMKEY                                                                |

| Step 5: Initiate                     | e the erase cycle.                             |                                                                                                                                   |

| 0000<br>0000<br>0000<br>             | A8E761<br>000000<br>000000<br>-                | BSET NVMCON, #WR<br>NOP<br>NOP<br>Externally time 'P13a' ms (see Section 13.0 "AC/DC Characteristics and<br>Timing Requirements") |

| 0000<br>0000<br>0000<br>0000<br>0000 | 000000<br>000000<br>A9E761<br>000000<br>000000 | NOP<br>NOP<br>BCLR NVMCON, #WR<br>NOP<br>NOP                                                                                      |

# TABLE 11-5:SERIAL INSTRUCTION EXECUTION FOR ERASING PROGRAM MEMORY<br/>(EITHER IN LOW-VOLTAGE OR NORMAL-VOLTAGE SYSTEMS) (CONTINUED)

| Command<br>(Binary) | Data<br>(Hexadecimal) | Description                                                            |

|---------------------|-----------------------|------------------------------------------------------------------------|

| Step 18: Un         | lock the NVMCON to    | erase 1 row of data memory.                                            |

| 0000                | 200558                | MOV #0x55, W8                                                          |

| 0000                | 883B38                | MOV W8, NVMKEY                                                         |

| 0000                | 200AA9                | MOV #0xAA, W9                                                          |

| 0000                | 883B39                | MOV W9, NVMKEY                                                         |

| Step 19: Init       | iate the erase cycle. |                                                                        |

| 0000                | A8E761                | BSET NVMCON, #WR                                                       |

| 0000                | 000000                | NOP                                                                    |

| 0000                | 000000                | NOP                                                                    |

| _                   | -                     | Externally time 'P13a' ms (see Section 13.0 "AC/DC Characteristics and |

|                     |                       | Timing Requirements")                                                  |

| 0000                | 000000                | NOP                                                                    |

| 0000                | 000000                | NOP                                                                    |

| 0000                | A9E761                | BCLR NVMCON, #WR                                                       |

| 0000                | 000000                | NOP                                                                    |

| 0000                | 000000                | NOP                                                                    |

| Step 20: Up         | date the row address  | stored in NVMADR.                                                      |

| 0000                | 430307                | ADD W6, W7, W6                                                         |

| 0000                | 883B16                | MOV W6, NVMADR                                                         |

| Step 21: Re         | set device internal P | С.                                                                     |

| 0000                | 040100                | GOTO 0x100                                                             |

| 0000                | 000000                | NOP                                                                    |

| Step 22: Re         | peat Steps 17-21 unt  | il all rows of data memory are erased.                                 |

### 11.7 Writing Configuration Memory

The FOSC, FWDT, FBORPOR and FICD registers are not erasable. It is recommended that all Configuration registers be set to a default value after erasing program memory. The FWDT, FBORPOR and FICD registers can be set to a default all '1's value by programming 0xFFFF to each register. Since these registers contain unimplemented bits that read as '0' the default values shown in Table 11-6 will be read instead of 0xFFFF. The recommended default FOSC value is 0xC100, which selects the FRC clock oscillator setting.

The FGS, FBS and FSS Configuration registers are special since they enable code protection for the device. For security purposes, once any bit in these registers is programmed to '0' (to enable some code protection feature), it can only be set back to '1' by performing a Bulk Erase or Segment Erase as described in **Section 11.5 "Erasing Program Memory in Normal-Voltage Systems**". Programming these bits from a '0' to '1' is not possible, but they may be programmed from a '1' to a '0' to enable code protection.

Table 11-7 shows the ICSP programming details for clearing the Configuration registers. In Step 1, the Reset vector is exited. In Step 2, the write pointer (W7) is loaded with 0x0000, which is the original destination address (in TBLPAG 0xF8 of program memory). In Step 3, the NVMCON is set to program one Configura-