Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 30 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 52                                                                             |

| Program Memory Size        | 132KB (44K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 2K x 8                                                                         |

| RAM Size                   | 6K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6011t-30i-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.5.3 PROGRAMMING VERIFICATION

Once code memory is programmed, the contents of memory can be verified to ensure that programming was successful. Verification requires code memory to be read back and compared against the copy held in the programmer's buffer.

The READP command can be used to read back all the programmed code memory.

Alternatively, you can have the programmer perform the verification once the entire device is programmed using a checksum computation, as described in Section 6.8 "Checksum Computation".

### 5.6 Data EEPROM Programming

#### 5.6.1 OVERVIEW

The panel architecture for the data EEPROM memory array consists of 128 rows of sixteen 16-bit data words. Each panel stores 2K words. All devices have either one or no memory panels. Devices with data EEPROM provide either 512 words, 1024 words or 2048 words of memory on the one panel (see Table 5-3).

TABLE 5-3:DATA EEPROM SIZE

| TABLE J-J. DATA LEFICON JIZE |                             |                   |  |  |

|------------------------------|-----------------------------|-------------------|--|--|

| Device                       | Data EEPROM<br>Size (Words) | Number of<br>Rows |  |  |

| dsPIC30F2010                 | 512                         | 32                |  |  |

| dsPIC30F2011                 | 0                           | 0                 |  |  |

| dsPIC30F2012                 | 0                           | 0                 |  |  |

| dsPIC30F3010                 | 512                         | 32                |  |  |

| dsPIC30F3011                 | 512                         | 32                |  |  |

| dsPIC30F3012                 | 512                         | 32                |  |  |

| dsPIC30F3013                 | 512                         | 32                |  |  |

| dsPIC30F3014                 | 512                         | 32                |  |  |

| dsPIC30F4011                 | 512                         | 32                |  |  |

| dsPIC30F4012                 | 512                         | 32                |  |  |

| dsPIC30F4013                 | 512                         | 32                |  |  |

| dsPIC30F5011                 | 512                         | 32                |  |  |

| dsPIC30F5013                 | 512                         | 32                |  |  |

| dsPIC30F5015                 | 512                         | 32                |  |  |

| dsPIC30F5016                 | 512                         | 32                |  |  |

| dsPIC30F6010                 | 2048                        | 128               |  |  |

| dsPIC30F6010A                | 2048                        | 128               |  |  |

| dsPIC30F6011                 | 1024                        | 64                |  |  |

| dsPIC30F6011A                | 1024                        | 64                |  |  |

| dsPIC30F6012                 | 2048                        | 128               |  |  |

| dsPIC30F6012A                | 2048                        | 128               |  |  |

| dsPIC30F6013                 | 1024                        | 64                |  |  |

| dsPIC30F6013A                | 1024                        | 64                |  |  |

| dsPIC30F6014                 | 2048                        | 128               |  |  |

| dsPIC30F6014A                | 2048                        | 128               |  |  |

| dsPIC30F6015                 | 2048                        | 128               |  |  |

#### 5.6.2 PROGRAMMING METHODOLOGY

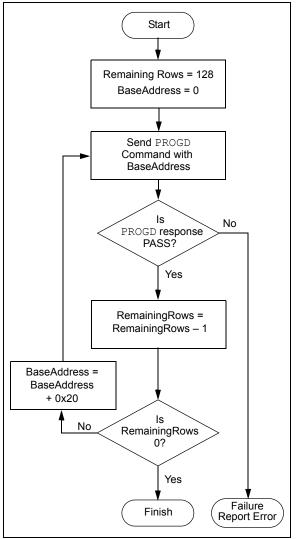

The programming executive uses the PROGD command to program the data EEPROM. Figure 5-4 illustrates the flowchart of the process. Firstly, the number of rows to program (RemainingRows) is based on the device size, and the destination address (DestAddress) is set to '0'. In this example, 128 rows (2048 words) of data EEPROM will be programmed.

The first PROGD command programs the first row of data EEPROM. Once the command completes successfully, 'RemainingRows' is decremented by 1 and compared with 0. Since there are 127 more rows to program, 'BaseAddress' is incremented by 0x20 to point to the next row of data EEPROM. This process is then repeated until all 128 rows of data EEPROM are programmed.

FIGURE 5-4:

#### FLOWCHART FOR PROGRAMMING dsPIC30F6014A DATA EEPROM

# TABLE 5-5:FOSC CONFIGURATION BITS DESCRIPTION FOR dsPIC30F4011/4012 AND<br/>dsPIC30F5011/5013

| Bit Field  | Register | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCKSM<1:0> | FOSC     | Clock Switching Mode<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FOS<1:0>   | FOSC     | Oscillator Source Selection on POR<br>11 = Primary Oscillator<br>10 = Internal Low-Power RC Oscillator<br>01 = Internal Fast RC Oscillator<br>00 = Low-Power 32 kHz Oscillator (Timer1 Oscillator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FPR<3:0>   | FOSC     | <ul> <li>Primary Oscillator Mode</li> <li>1111 = ECIO w/PLL 16X – External Clock mode with 16X PLL. OSC2 pin is I/O</li> <li>1101 = ECIO w/PLL 8X – External Clock mode with 8X PLL. OSC2 pin is I/O</li> <li>1011 = ECIO w/PLL 4X – External Clock mode with 4X PLL. OSC2 pin is I/O</li> <li>100 = ECIO – External Clock mode. OSC2 pin is I/O</li> <li>1011 = EC – External Clock mode. OSC2 pin is system clock output (Fosc/4)</li> <li>1010 = FRC w/PLL 8x – Internal fast RC oscillator with 8x PLL. OSC2 pin is I/O</li> <li>1001 = ERC – External RC Oscillator mode. OSC2 pin is system clock output (Fosc/4)</li> <li>1000 = ERCIO – External RC Oscillator mode. OSC2 pin is system clock output (Fosc/4)</li> <li>1000 = ERCIO – External RC Oscillator mode. OSC2 pin is I/O</li> <li>0111 = XT w/PLL 16X – XT Crystal Oscillator mode with 16X PLL</li> <li>0101 = XT w/PLL 4X – XT Crystal Oscillator mode with 4X PLL</li> <li>0101 = XT w/PLL 4X – T Crystal Oscillator mode with 4X PLL</li> <li>0101 = T K w/PLL 16x – Internal fast RC oscillator with 16x PLL</li> <li>0111 = ST w/PLL 4X – XT Crystal Oscillator mode with 4X PLL</li> <li>0101 = KT w/PLL 16x – Internal fast RC oscillator with 16x PLL. OSC2 pin is I/O</li> <li>0011 = FRC w/PLL 16x – Internal fast RC oscillator with 16x PLL. OSC2 pin is I/O</li> <li>0010 = HS – HS Crystal Oscillator mode (10 MHz-25 MHz crystal)</li> <li>0011 = FRC w/PLL 4x – Internal fast RC oscillator with 4x PLL. OSC2 pin is I/O</li> <li>0011 = FRC w/PLL 4x – Internal fast RC oscillator with 4x PLL. OSC2 pin is I/O</li> <li>0011 = FRC w/PLL 4x – Internal fast RC oscillator with 4x PLL. OSC2 pin is I/O</li> <li>0011 = FRC w/PLL 4x – Internal fast RC oscillator with 4x PLL. OSC2 pin is I/O</li> <li>0011 = FRC w/PLL 4x – Internal fast RC oscillator with 4x PLL. OSC2 pin is I/O</li> <li>0011 = FRC w/PLL 4x – Internal fast RC oscillator with 4x PLL. OSC2 pin is I/O</li> </ul> |

#### TABLE 5-6: FOSC CONFIGURATION BITS DESCRIPTION FOR dsPIC30F2011/2012, dsPIC30F3010/3011/3012/3013/3014, dsPIC30F4013, dsPIC30F5015/5016, dsPIC30F6010A/6011A/6012A/6013A/6014A AND dsPIC30F6015

|     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OSC | Clock Switching Mode<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| OSC | Oscillator Source Selection on POR<br>111 = Primary Oscillator<br>110 = Reserved<br>101 = Reserved<br>100 = Reserved<br>011 = Reserved<br>010 = Internal Low-Power RC Oscillator<br>001 = Internal Fast RC Oscillator (no PLL)<br>000 = Low-Power 32 kHz Oscillator (Timer1 Oscillator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| DSC | Primary Oscillator Mode (when FOS<2:0> = 111b)<br>11xxx = Reserved (do not use)<br>10111 = HS/3 w/PLL 16X – HS/3 crystal oscillator with 16X PLL<br>(10 MHz-25 MHz crystal)<br>10101 = HS/3 w/PLL 8X – HS/3 crystal oscillator with 8X PLL<br>(10 MHz-25 MHz crystal)<br>10101 = HS/3 w/PLL 4X – HS/3 crystal oscillator with 4X PLL<br>(10 MHz-25 MHz crystal)<br>10100 = Reserved (do not use)<br>10011 = HS/2 w/PLL 16X – HS/2 crystal oscillator with 16X PLL<br>(10 MHz-25 MHz crystal)<br>10010 = HS/2 w/PLL 8X – HS/2 crystal oscillator with 8X PLL<br>(10 MHz-25 MHz crystal)<br>10001 = HS/2 w/PLL 8X – HS/2 crystal oscillator with 8X PLL<br>(10 MHz-25 MHz crystal)<br>10001 = HS/2 w/PLL 4X – HS/2 crystal oscillator with 4X PLL<br>(10 MHz-25 MHz crystal)<br>10000 = Reserved (do not use)<br>01111 = ECIO w/PLL 16x – External clock with 16x PLL. OSC2 pin is I/O<br>01101 = ECIO w/PLL 16x – External clock with 8x PLL. OSC2 pin is I/O<br>01101 = ECIO w/PLL 4x – External clock with 4x PLL. OSC2 pin is I/O<br>01101 = ECIO w/PLL 4x – External clock with 4x PLL. OSC2 pin is I/O<br>01101 = ECIO w/PLL 8x – Internal fast RC oscillator with 8x PLL. OSC2 pin is I/O<br>01010 = Reserved (do not use)<br>01011 = Reserved (do not use)<br>01011 = XT w/PLL 16X – XT crystal oscillator with 16X PLL<br>0110 = XT w/PLL 4X – XT crystal oscillator with 8X PLL<br>0110 = XT w/PLL 4X – XT crystal oscillator with 8X PLL<br>0110 = XT w/PLL 4X – XT crystal oscillator with 8X PLL<br>0110 = TRC w/PLL 4X – Internal fast RC oscillator with 8x PLL. OSC2 pin is I/O<br>0111 = FRC w/PLL 4X – XT crystal oscillator with 8X PLL<br>0100 = Reserved (do not use)<br>00011 = FRC w/PLL 4X – Internal fast RC oscillator with 8x PLL. OSC2 pin is I/O<br>00010 = Reserved (do not use)<br>00011 = FRC w/PLL 4X – Internal fast RC oscillator with 4x PLL. OSC2 pin is I/O<br>00010 = Reserved (do not use) |  |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

#### 6.0 OTHER PROGRAMMING **FEATURES**

#### 6.1 Erasing Memory

Memory is erased by using an ERASEB, ERASED or ERASEP command, as detailed in Section 8.5 "Command Descriptions". Code memory can be erased by row using ERASEP. Data EEPROM can be erased by row using ERASED. When memory is erased, the affected memory locations are set to '1's.

ERASEB provides several Bulk Erase options. Performing a Chip Erase with the ERASEB command clears all code memory, data EEPROM and code protection registers. Alternatively, ERASEB can be used to selectively erase either all code memory or data EEPROM. Erase options are summarized in Table 6-1.

| Command   | Affected Region                                                                       |  |

|-----------|---------------------------------------------------------------------------------------|--|

| ERASEB    | Entire chip <sup>(1)</sup> or all code memory or all data EEPROM, or erase by segment |  |

| ERASED    | Specified rows of data EEPROM                                                         |  |

| ERASEP(2) | Specified rows of code memory                                                         |  |

**TABLE 6-1: ERASE OPTIONS**

The system operation Configuration Note 1: registers and device ID registers are not erasable.

> 2: ERASEP cannot be used to erase codeprotect Configuration bits. These bits must be erased using ERASEB.

#### 6.2 Modifying Memory

Instead of bulk-erasing the device before programming, it is possible that you may want to modify only a section of an already programmed device. In this situation, Chip Erase is not a realistic option.

Instead, you can erase selective rows of code memory and data EEPROM using ERASEP and ERASED, respectively. You can then reprogram the modified rows with the PROGP and PROGD command pairs. In these cases, when code memory is programmed, single-panel programming must be specified in the PROGP command.

For modification of Advanced Code Protection bits for a particular segment, the entire chip must first be erased with the ERASEB command. Alternatively, on devices that support Advanced Security, individual segments (code and/or data EEPROM) may be erased, by suitably changing the MS (Memory Select) field in the ERASEB command. The code-protect Configuration bits can then be reprogrammed using the PROGC command.

Note: If read or write code protection is enabled for a segment, no modifications can be made to that segment until code protection is disabled. Code protection can only be disabled by performing a Chip Erase or by performing a Segment Erase operation for the required segment.

#### 6.3 Reading Memory

The READD command reads the data EEPROM, Configuration bits and device ID of the device. This command only returns 16-bit data and operates on 16-bit registers. READD can be used to return the entire contents of data EEPROM.

The READP command reads the code memory of the device. This command only returns 24-bit data packed as described in Section 8.3 "Packed Data Format". READP can be used to read up to 32K instruction words of code memory.

| Note: |                                         |

|-------|-----------------------------------------|

|       | location causes the programming         |

|       | executive to reset. All READD and READP |

|       | commands must specify only valid        |

|       | memory locations.                       |

#### 6.4 Programming Executive Software Version

At times, it may be necessary to determine the version of programming executive stored in executive memory. The QVER command performs this function. See Section 8.5.11 "QVER Command" for more details about this command.

#### Data EEPROM Information in the 6.5 **Hexadecimal File**

To allow portability of code, the programmer must read the data EEPROM information from the hexadecimal file. If data EEPROM information is not present, a simple warning message should be issued by the programmer. Similarly, when saving a hexadecimal file, all data EEPROM information must be included. An option to not include the data EEPROM information can be provided.

Microchip Technology Inc. believes that this feature is important for the benefit of the end customer.

#### 8.5 Command Descriptions

All commands that are supported by the programming executive are described in Section 8.5.1 "SCHECK Command" through Section 8.5.11 "QVER Command".

#### 8.5.1 SCHECK COMMAND

| 15 | 12     | 11 0   | ) |

|----|--------|--------|---|

|    | Opcode | Length |   |

| Field  | Description |

|--------|-------------|

| Opcode | 0x0         |

| Length | 0x1         |

The SCHECK command instructs the programming executive to do nothing, but generate a response. This command is used as a "sanity check" to verify that the programming executive is operational.

#### Expected Response (2 words):

0x1000 0x0002

Note: This instruction is not required for programming, but is provided for development purposes only.

#### 8.5.2 READD COMMAND

| 15      | 12        | 11 | 8 | 7        | 0 |

|---------|-----------|----|---|----------|---|

| Орс     | ode       |    |   | Length   |   |

| Reser   | ved0      | N  |   |          |   |

|         | Reserved1 |    |   | Addr_MSB |   |

| Addr_LS |           |    |   |          |   |

| Field     | Description                                  |

|-----------|----------------------------------------------|

| Opcode    | 0x1                                          |

| Length    | 0x4                                          |

| Reserved0 | 0x0                                          |

| N         | Number of 16-bit words to read (max of 2048) |

| Reserved1 | 0x0                                          |

| Addr_MSB  | MSB of 24-bit source address                 |

| Addr_LS   | LS 16 bits of 24-bit source address          |

The READD command instructs the programming executive to read N 16-bit words of memory starting from the 24-bit address specified by Addr\_MSB and Addr\_LS. This command can only be used to read 16-bit data. It can be used to read data EEPROM, Configuration registers and the device ID.

#### Expected Response (2+N words):

0x1100 N + 2 Data word 1

Data word N

Note: Reading unimplemented memory will cause the programming executive to reset.

## dsPIC30F Flash Programming Specification

#### 8.5.3 READP COMMAND

| 15                | 12      | 11 | 8 | 7      | 0 |

|-------------------|---------|----|---|--------|---|

| Орс               | ode     |    |   | Length |   |

|                   |         |    | Ν |        |   |

| Reserved Addr_MSB |         |    |   |        |   |

|                   | Addr_LS |    |   |        |   |

| Field    | Description                                          |

|----------|------------------------------------------------------|

| Opcode   | 0x2                                                  |

| Length   | 0x4                                                  |

| Ν        | Number of 24-bit instructions to read (max of 32768) |

| Reserved | 0x0                                                  |

| Addr_MSB | MSB of 24-bit source address                         |

| Addr_LS  | LS 16 bits of 24-bit source address                  |

The READP command instructs the programming executive to read N 24-bit words of code memory starting from the 24-bit address specified by Addr\_MSB and Addr\_LS. This command can only be used to read 24-bit data. All data returned in response to this command uses the packed data format described in Section 8.3 "Packed Data Format".

#### Expected Response (2 + 3 \* N/2 words for N even): 0x1200

2 + 3 \* N/2 Least significant program memory word 1

Least significant data word N

## Expected Response (4 + 3 \* (N - 1)/2 words for N odd):

0x12004 + 3 \* (N - 1)/2 Least significant program memory word 1

MSB of program memory word N (zero padded)

Note: Reading unimplemented memory will cause the programming executive to reset.

#### 8.5.4 PROGD COMMAND

| 15   | 12   | 2 11 8 7 0 |       |    |          |  |

|------|------|------------|-------|----|----------|--|

| Орс  | ode  |            |       | L  | ength    |  |

|      | Rese | rved       |       |    | Addr_MSB |  |

|      |      |            | Addr_ | LS |          |  |

| D_1  |      |            |       |    |          |  |

| D_2  |      |            |       |    |          |  |

|      |      |            |       |    |          |  |

| D_16 |      |            |       |    |          |  |

| Field    | Description                              |

|----------|------------------------------------------|

| Opcode   | 0x4                                      |

| Length   | 0x13                                     |

| Reserved | 0x0                                      |

| Addr_MSB | MSB of 24-bit destination address        |

| Addr_LS  | LS 16 bits of 24-bit destination address |

| D_1      | 16-bit data word 1                       |

| D_2      | 16-bit data word 2                       |

|          | 16-bit data words 3 through 15           |

| D_16     | 16-bit data word 16                      |

The PROGD command instructs the programming executive to program one row of data EEPROM. The data to be programmed is specified by the 16 data words (D\_1, D\_2,..., D\_16) and is programmed to the destination address specified by Addr\_MSB and Addr\_LSB. The destination address should be a multiple of 0x20.

Once the row of data EEPROM has been programmed, the programming executive verifies the programmed data against the data in the command.

#### Expected Response (2 words):

0x1400 0x0002

**Note:** Refer to Table 5-3 for data EEPROM size information.

#### 8.5.5 PROGP COMMAND

| 15  | 12   | 12 11 8 7 0 |  |    |          |  |

|-----|------|-------------|--|----|----------|--|

| Орс | ode  |             |  | L  | ength    |  |

|     | Rese | rved        |  |    | Addr_MSB |  |

|     |      |             |  | LS |          |  |

|     | D_1  |             |  |    |          |  |

| D_2 |      |             |  |    |          |  |

|     |      |             |  |    |          |  |

| D_N |      |             |  |    |          |  |

| Field    | Description                              |

|----------|------------------------------------------|

| Opcode   | 0x5                                      |

| Length   | 0x33                                     |

| Reserved | 0x0                                      |

| Addr_MSB | MSB of 24-bit destination address        |

| Addr_LS  | LS 16 bits of 24-bit destination address |

| D_1      | 16-bit data word 1                       |

| D_2      | 16-bit data word 2                       |

|          | 16-bit data word 3 through 47            |

| D_48     | 16-bit data word 48                      |

The PROGP command instructs the programming executive to program one row of code memory (32 instruction words) to the specified memory address. Programming begins with the row address specified in the command. The destination address should be a multiple of 0x40.

The data to program to memory, located in command words D\_1 through D\_48, must be arranged using the packed instruction word format shown in Figure 8-2.

After all data has been programmed to code memory, the programming executive verifies the programmed data against the data in the command.

Expected Response (2 words): 0x1500 0x0002

**Note:** Refer to Table 5-2 for code memory size information.

#### 8.5.6 PROGC COMMAND

| 15      | 12       | 11 | 8 | 7 |          | 0 |

|---------|----------|----|---|---|----------|---|

| Opcode  |          |    |   | L | ength    |   |

|         | Reserved |    |   |   | Addr_MSB |   |

| Addr_LS |          |    |   |   |          |   |

|         | Data     |    |   |   |          |   |

| Field    | Description                              |

|----------|------------------------------------------|

| Opcode   | 0x6                                      |

| Length   | 0x4                                      |

| Reserved | 0x0                                      |

| Addr_MSB | MSB of 24-bit destination address        |

| Addr_LS  | LS 16 bits of 24-bit destination address |

| Data     | Data to program                          |

The PROGC command programs data to the specified Configuration register and verifies the programming. Configuration registers are 16 bits wide, and this command allows one Configuration register to be programmed.

Expected Response (2 words): 0x1600 0x0002

Note: This command can only be used for programming Configuration registers.

## dsPIC30F Flash Programming Specification

#### 8.5.7 ERASEB COMMAND

| 15 12  | 11       | 2 | 0 |

|--------|----------|---|---|

| Opcode | Length   |   |   |

|        | Reserved | M | S |

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Opcode   | 0x7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Length   | 0x2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Reserved | 0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MS       | Select memory to erase:<br>0x0 = All Code in General Segment<br>0x1 = All Data EEPROM in General Segment $0x2 = All Code and Data EEPROM inGeneral Segment, interrupt vectors andFGS Configuration register0x3 = Full Chip Erase0x4 = All Code and Data EEPROM inBoot, Secure and General Segments,and FBS, FSS and FGS Configurationregisters0x5 = All Code and Data EEPROM inSecure and General Segments, andFSS and FGS Configuration registers0x6 = All Data EEPROM in$ Boot<br>Segment<br>0x7 = All Data EEPROM in Secure<br>Segment |

The ERASEB command performs a Bulk Erase. The MS field selects the memory to be bulk erased, with options for erasing Code and/or Data EEPROM in individual memory segments.

When Full Chip Erase is selected, the following memory regions are erased:

- All code memory (even if code-protected)

- All data EEPROM

- All code-protect Configuration registers

Only the executive code memory, Unit ID, device ID and Configuration registers that are not code-protected remain intact after a Chip Erase.

#### Expected Response (2 words):

0x1700 0x0002

> Note: A Full Chip Erase cannot be performed in low-voltage programming systems (VDD less than 4.5 volts). ERASED and ERASEP must be used to erase code memory, executive memory and data memory. Alternatively, individual Segment Erase operations may be performed.

#### 8.5.8 ERASED COMMAND

| 15       | 12 | 11 | 8        | 7      | 0 |

|----------|----|----|----------|--------|---|

| Opcode   |    |    |          | Length |   |

| Num_Rows |    |    | Addr_MSB |        |   |

|          |    |    | Addr_    | LS     |   |

| Field    | Description                          |

|----------|--------------------------------------|

| Opcode   | 0x8                                  |

| Length   | 0x3                                  |

| Num_Rows | Number of rows to erase (max of 128) |

| Addr_MSB | MSB of 24-bit base address           |

| Addr_LS  | LS 16 bits of 24-bit base address    |

The ERASED command erases the specified number of rows of data EEPROM from the specified base address. The specified base address must be a multiple of 0x20. Since the data EEPROM is mapped to program space, a 24-bit base address must be specified.

After the erase is performed, all targeted bytes of data EEPROM will contain 0xFF.

Expected Response (2 words): 0x1800 0x0002

Note: The ERASED command cannot be used to erase the Configuration registers or device ID. Code-protect Configuration registers can only be erased with the ERASEB command, while the device ID is read-only.

#### 9.2.3 QE\_Code FIELD

The QE\_Code is a byte in the first word of the response. This byte is used to return data for query commands, and error codes for all other commands.

When the programming executive processes one of the two query commands (QBLANK or QVER), the returned opcode is always PASS and the QE\_Code holds the query response data. The format of the QE\_Code for both queries is shown in Table 9-3.

TABLE 9-3: QE\_Code FOR QUERIES

| Query  | QE_Code                                                                                                |

|--------|--------------------------------------------------------------------------------------------------------|

| QBLANK | 0x0F = Code memory and data EEPROM<br>are NOT blank<br>0xF0 = Code memory and data EEPROM<br>are blank |

| QVER   | 0xMN, where programming executive<br>software version = M.N<br>(i.e., 0x32 means software version 3.2) |

When the programming executive processes any command other than a Query, the QE\_Code represents an error code. Supported error codes are shown in Table 9-4. If a command is successfully processed, the returned QE\_Code is set to 0x0, which indicates that there was no error in the command processing. If the verify of the programming for the PROGD, PROGP or PROGC command fails, the QE\_Code is set to 0x1. For all other programming executive errors, the QE\_Code is 0x2.

#### TABLE 9-4: QE\_Code FOR NON-QUERY COMMANDS

| QE_Code | Description   |

|---------|---------------|

| 0x0     | No error      |

| 0x1     | Verify failed |

| 0x2     | Other error   |

#### 9.2.4 RESPONSE LENGTH

The response length indicates the length of the programming executive's response in 16-bit words. This field includes the 2 words of the response header.

With the exception of the response for the READD and READP commands, the length of each response is only 2 words.

The response to the READD command is N + 2 words, where N is the number of words specified in the READD command.

The response to the READP command uses the packed instruction word format described in **Section 8.3 "Packed Data Format"**. When reading an odd number of program memory words (N odd), the response to the READP command is  $(3 \cdot (N + 1)/2 + 2)$  words. When reading an even number of program memory words (N even), the response to the READP command is  $(3 \cdot N/2 + 2)$  words.

## 11.0 ICSP™ MODE

#### 11.1 ICSP Mode

ICSP mode is a special programming protocol that allows you to read and write to the dsPIC30F programming executive. The ICSP mode is the second (and slower) method used to program the device. This mode also has the ability to read the contents of executive memory to determine whether the programming executive is present. This capability is accomplished by applying control codes and instructions serially to the device using pins PGC and PGD.

In ICSP mode, the system clock is taken from the PGC pin, regardless of the device's oscillator Configuration bits. All instructions are first shifted serially into an internal buffer, then loaded into the Instruction register and executed. No program fetching occurs from internal memory. Instructions are fed in 24 bits at a time. PGD is used to shift data in and PGC is used as both the serial shift clock and the CPU execution clock.

Data is transmitted on the rising edge and latched on the falling edge of PGC. For all data transmissions, the Least Significant bit (LSb) is transmitted first.

Note 1: During ICSP operation, the operating frequency of PGC must not exceed 5 MHz.

2: Because ICSP is slower, it is recommended that only Enhanced ICSP (E-ICSP) mode be used for device programming, as described in Section 5.1 "Overview of the Programming Process".

#### 11.2 ICSP Operation

Upon entry into ICSP mode, the CPU is idle. Execution of the CPU is governed by an internal state machine. A 4-bit control code is clocked in using PGC and PGD, and this control code is used to command the CPU (see Table 11-1).

The SIX control code is used to send instructions to the CPU for execution, while the REGOUT control code is used to read data out of the device via the VISI register. The operation details of ICSP mode are provided in Section 11.2.1 "SIX Serial Instruction Execution" and Section 11.2.2 "REGOUT Serial Instruction Execution".

## TABLE 11-1:CPU CONTROL CODES IN<br/>ICSP™ MODE

| 4-bit<br>Control<br>Code | Mnemonic | Description                              |

|--------------------------|----------|------------------------------------------|

| d0000b                   | SIX      | Shift in 24-bit instruction and execute. |

| 0001b                    | REGOUT   | Shift out the VISI register.             |

| 0010b-1111b              | N/A      | Reserved.                                |

#### 11.2.1 SIX SERIAL INSTRUCTION EXECUTION

The SIX control code allows execution of dsPIC30F assembly instructions. When the SIX code is received, the CPU is suspended for 24 clock cycles as the instruction is then clocked into the internal buffer. Once the instruction is shifted in, the state machine allows it to be executed over the next four clock cycles. While the received instruction is executed, the state machine simultaneously shifts in the next 4-bit command (see Figure 11-2).

- Note 1: Coming out of the ICSP entry sequence, the first 4-bit control code is always forced to SIX and a forced NOP instruction is executed by the CPU. Five additional PGC clocks are needed on startup, thereby resulting in a 9-bit SIX command instead of the normal 4-bit SIX command. After the forced SIX is clocked in, ICSP operation resumes as normal (the next 24 clock cycles load the first instruction word to the CPU). See Figure 11-1 for details.

- 2: TBLRDH, TBLRDL, TBLWTH and TBLWTL instructions must be followed by a NOP instruction.

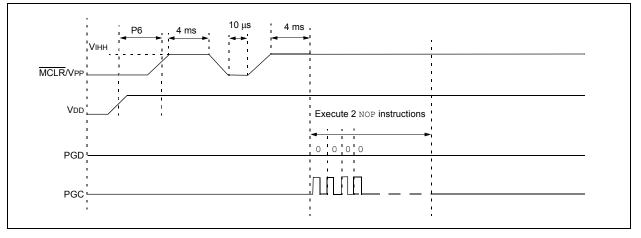

#### 11.3 Entering ICSP Mode

The ICSP mode is entered by holding PGC and PGD low, raising  $\overline{\text{MCLR}/\text{VPP}}$  to VIHH (high voltage), and then performing additional steps as illustrated in Figure 11-4.

- Note 1: The sequence that places the device into ICSP mode places all unused I/O pins to the high-impedance state.

- **2:** Once ICSP mode is entered, the PC is set to 0x0 (the Reset vector).

- 3: Before leaving the Reset vector, execute two GOTO instructions, followed by a single NOP instruction must be executed.

FIGURE 11-4: ENTERING ICSP™ MODE

#### 11.4 Flash Memory Programming in ICSP Mode

Programming in ICSP mode is described in Section 11.4.1 "Programming Operations" through Section 11.4.3 "Starting and Stopping a Programming Cycle". Step-by-step procedures are described in Section 11.5 "Erasing Program Memory in Normal-Voltage Systems" through Section 11.13 "Reading the Application ID Word". All programming operations must use serial execution, as described in Section 11.2 "ICSP Operation".

#### 11.4.1 PROGRAMMING OPERATIONS

Flash memory write and erase operations are controlled by the NVMCON register. Programming is performed by setting NVMCON to select the type of erase operation (Table 11-2) or write operation (Table 11-3), writing a key sequence to enable the programming and initiating the programming by setting the WR control bit, NVMCON<15>.

In ICSP mode, all programming operations are externally timed. An external 2 ms delay must be used between setting the WR control bit and clearing the WR control bit to complete the programming operation.

#### TABLE 11-2: NVMCON ERASE OPERATIONS

| NVMCON<br>Value | Erase Operation                                                                                    |  |

|-----------------|----------------------------------------------------------------------------------------------------|--|

| 0x407F          | Erase all code memory, data memory (does not erase UNIT ID).                                       |  |

| 0x4075          | Erase 1 row (16 words) of data<br>EEPROM.                                                          |  |

| 0x4074          | Erase 1 word of data EEPROM.                                                                       |  |

| 0x4072          | Erase all executive memory.                                                                        |  |

| 0x4071          | Erase 1 row (32 instruction words) from 1 panel of code memory.                                    |  |

| 0x406E          | Erase Boot Secure and General<br>Segments, then erase FBS, FSS and<br>FGS configuration registers. |  |

| 0x4066          | Erase all Data EEPROM allocated to<br>Boot Segment.                                                |  |

| 0x405E          | Erase Secure and General Segments,<br>then erase FSS and FGS configuration<br>registers.           |  |

| 0x4056          | Erase all Data EEPROM allocated to Secure Segment.                                                 |  |

| 0x404E          | Erase General Segment, then erase FGS configuration register.                                      |  |

| 0x4046          | Erase all Data EEPROM allocated to General Segment.                                                |  |

## TABLE 11-3: NVMCON WRITE OPERATIONS

| NVMCON<br>Value | Write Operation                                                    |  |

|-----------------|--------------------------------------------------------------------|--|

| 0x4008          | Write 1 word to configuration                                      |  |

|                 | memory.                                                            |  |

| 0x4005          | Write 1 row (16 words) to data memory.                             |  |

| 0x4004          | Write 1 word to data memory.                                       |  |

| 0x4001          | Write 1 row (32 instruction words) into 1 panel of program memory. |  |

#### 11.4.2 UNLOCKING NVMCON FOR PROGRAMMING

Writes to the WR bit (NVMCON<15>) are locked to prevent accidental programming from taking place. Writing a key sequence to the NVMKEY register unlocks the WR bit and allows it to be written to. The unlock sequence is performed as follows:

| MOV   | #0x55, W8                                                                                 |

|-------|-------------------------------------------------------------------------------------------|

| MOV   | W8, NVMKEY                                                                                |

| MOV   | #OxAA, W9                                                                                 |

| MOV   | W9, NVMKEY                                                                                |

| Note: | Any working register, or working register pair, can be used to write the unlock sequence. |

#### 11.4.3 STARTING AND STOPPING A PROGRAMMING CYCLE

Once the unlock key sequence has been written to the NVMKEY register, the WR bit (NVMCON<15>) is used to start and stop an erase or write cycle. Setting the WR bit initiates the programming cycle. Clearing the WR bit terminates the programming cycle.

All erase and write cycles must be externally timed. An external delay must be used between setting and clearing the WR bit. Starting and stopping a programming cycle is performed as follows:

| BSET                                            | NVMCON, | #WR |

|-------------------------------------------------|---------|-----|

| <wait< td=""><td>2 ms&gt;</td><td></td></wait<> | 2 ms>   |     |

| BCLR                                            | NVMCON, | #WR |

### 11.5 Erasing Program Memory in Normal-Voltage Systems

The procedure for erasing program memory (all code memory, data memory, executive memory and codeprotect bits) consists of setting NVMCON to 0x407F, unlocking NVMCON for erasing and then executing the programming cycle. This method of bulk erasing program memory only works for systems where VDD is between 4.5 volts and 5.5 volts. The method for erasing program memory for systems with a lower VDD (3.0 volts-4.5 volts) is described in Section 6.1 "Erasing Memory".

### 11.9 Writing Data EEPROM

The procedure for writing data EEPROM is very similar to the procedure for writing code memory, except that fewer words are programmed in each operation. When writing data EEPROM, one row of data EEPROM is programmed at a time. Each row consists of sixteen 16-bit data words. Since fewer words are programmed during each operation, only working registers W0:W3 are used as temporary holding registers for the data to be programmed.

Table 11-9 shows the ICSP programming details for writing data EEPROM. Note that a different NVMCON value is required to write to data EEPROM, and that the TBLPAG register is hard-coded to 0x7F (the upper byte address of all locations of data EEPROM).

|             | OFRIAL INOTRUCTION EVECUTION FOR WRITING RATA FERROM |

|-------------|------------------------------------------------------|

| TABLE 11-9: | SERIAL INSTRUCTION EXECUTION FOR WRITING DATA EEPROM |

| Command<br>(Binary) | Data<br>(Hexadecimal)  | Description                                                 |

|---------------------|------------------------|-------------------------------------------------------------|

| Step 1: Exit th     | e Reset vector.        |                                                             |

| 0000                | 040100                 | GOTO 0x100                                                  |

| 0000                | 040100                 | GOTO 0x100                                                  |

| 0000                | 000000                 | NOP                                                         |

| Step 2: Set the     | e NVMCON to write      | 16 data words.                                              |

| 0000                | 24005A                 | MOV #0x4005, W10                                            |

| 0000                | 883B0A                 | MOV W10, NVMCON                                             |

| Step 3: Initializ   | ze the write pointer   | W7) for TBLWT instruction.                                  |

| 0000                | 2007F0                 | MOV #0x7F, WO                                               |

| 0000                | 880190                 | MOV W0, TBLPAG                                              |

| 0000                | 2xxxx7                 | MOV # <destinationaddress15:0>, W7</destinationaddress15:0> |

| Step 4: Load \      | W0:W3 with the nex     | 4 data words to program.                                    |

| 0000                | 2xxxx0                 | MOV # <wordo>, WO</wordo>                                   |

| 0000                | 2xxxx1                 | MOV # <word1>, W1</word1>                                   |

| 0000                | 2xxxx2                 | MOV # <word2>, W2</word2>                                   |

| 0000                | 2xxxx3                 | MOV # <word3>, W3</word3>                                   |

| Step 5: Set the     | e read pointer (W6)    | and load the (next set of) write latches.                   |

| 0000                | EB0300                 | CLR W6                                                      |

| 0000                | 000000                 | NOP                                                         |

| 0000                | BB1BB6                 | TBLWTL [W6++], [W7++]                                       |

| 0000                | 000000                 | NOP                                                         |

| 0000                | 000000                 | NOP                                                         |

| 0000                | BB1BB6                 | TBLWTL [W6++], [W7++]                                       |

| 0000                | 000000                 | NOP                                                         |

| 0000                | 000000                 | NOP                                                         |

| 0000                | BB1BB6                 | TBLWTL [W6++], [W7++]                                       |

| 0000                | 000000                 | NOP                                                         |

| 0000                | 000000                 | NOP                                                         |

| 0000                | BB1BB6                 | TBLWTL [W6++], [W7++]                                       |

| 0000                | 000000                 | NOP                                                         |

| 0000                | 000000                 | NOP                                                         |

| Step 6: Repea       | at steps 4-5 four time | es to load the write latches for 16 data words.             |

|                     |                        |                                                             |

| Comman<br>(Binary) |                        | Description                                                            |  |  |

|--------------------|------------------------|------------------------------------------------------------------------|--|--|

| Step 7: Un         | lock the NVMCON for    | writing.                                                               |  |  |

| 0000               | 200558                 | MOV #0x55, W8                                                          |  |  |

| 0000               | 883B38                 | MOV W8, NVMKEY                                                         |  |  |

| 0000               | 200AA9                 | MOV #0xAA, W9                                                          |  |  |

| 0000               | 883B39                 | MOV W9, NVMKEY                                                         |  |  |

| Step 8: Init       | iate the write cycle.  |                                                                        |  |  |

| 0000               | A8E761                 | BSET NVMCON, #WR                                                       |  |  |

| 0000               | 000000                 | NOP                                                                    |  |  |

| 0000               | 000000                 | NOP                                                                    |  |  |

| _                  | -                      | Externally time 'P12a' ms (see Section 13.0 "AC/DC Characteristics and |  |  |

|                    |                        | Timing Requirements")                                                  |  |  |

| 0000               | 000000                 | NOP                                                                    |  |  |

| 0000               | 000000                 | NOP                                                                    |  |  |

| 0000               | A9E761                 | BCLR NVMCON, #WR                                                       |  |  |

| 0000               | 000000                 | NOP                                                                    |  |  |

| 0000               | 000000                 | NOP                                                                    |  |  |

| Step 9: Re         | set device internal PC |                                                                        |  |  |

| 0000               | 040100                 | GOTO 0x100                                                             |  |  |

| 0000               | 000000                 | NOP                                                                    |  |  |

#### TABLE 11-9: SERIAL INSTRUCTION EXECUTION FOR WRITING DATA EEPROM (CONTINUED)

| Command<br>(Binary) | Data<br>(Hexadecimal)                 | Description                                             |  |  |

|---------------------|---------------------------------------|---------------------------------------------------------|--|--|

| Step 4: Outpu       | t W0:W5 using th                      | ne VISI register and REGOUT command.                    |  |  |

| 0000                | 883C20                                | MOV W0, VISI                                            |  |  |

| 0000                | 000000                                | NOP                                                     |  |  |

| 0001                | -                                     | Clock out contents of VISI register                     |  |  |

| 0000                | 883C21                                | MOV W1, VISI                                            |  |  |

| 0000                | 000000                                | NOP                                                     |  |  |

| 0001                | -                                     | Clock out contents of VISI register                     |  |  |

| 0000                | 883C22                                | MOV W2, VISI                                            |  |  |

| 0000                | 000000                                | NOP                                                     |  |  |

| 0001                | -                                     | Clock out contents of VISI register                     |  |  |

| 0000                | 883C23                                | MOV W3, VISI                                            |  |  |

| 0000                | 000000                                | NOP                                                     |  |  |

| 0001                | -                                     | Clock out contents of VISI register                     |  |  |

| 0000                | 883C24                                | MOV W4, VISI                                            |  |  |

| 0000                | 000000                                | NOP                                                     |  |  |

| 0001                | -                                     | Clock out contents of VISI register                     |  |  |

| 0000                | 883C25                                | MOV W5, VISI                                            |  |  |

| 0000                | 000000                                | NOP                                                     |  |  |

| 0001                | -                                     | Clock out contents of VISI register                     |  |  |

| Step 5: Reset       | Step 5: Reset the device internal PC. |                                                         |  |  |

| 0000                | 040100                                | GOTO 0x100                                              |  |  |

| 0000                | 000000                                | NOP                                                     |  |  |

| Step 6: Repea       | at Steps 3-5 until                    | all 736 instruction words of executive memory are read. |  |  |

## TABLE 12-2: READING EXECUTIVE MEMORY (CONTINUED)

| AC/DC CHARACTERISTICS |       | Standard Operating Conditions<br>(unless otherwise stated)<br>Operating Temperature: 25° C is recommended |     |     |       |                       |

|-----------------------|-------|-----------------------------------------------------------------------------------------------------------|-----|-----|-------|-----------------------|

| Param.<br>No. Sym     |       | Characteristic                                                                                            | Min | Мах | Units | Conditions            |

| P9b                   | TDLY5 | Delay between PGD ↓by programming<br>executive to PGD released by<br>programming executive                | 15  | _   | μs    | —                     |

| P10                   | TDLY6 | Delay between PGD released by programming executive to first PGC ↑ of response                            | 5   | _   | μs    | _                     |

| P11                   | TDLY7 | Delay between clocking out response words                                                                 | 10  | —   | μs    | -                     |

| P12a                  | TPROG | Row Programming cycle time                                                                                | 1   | 4   | ms    | ICSP mode             |

| P12b                  | TPROG | Row Programming cycle time                                                                                | 0.8 | 2.6 | ms    | Enhanced<br>ICSP mode |

| P13a                  | Tera  | Bulk/Row Erase cycle time                                                                                 | 1   | 4   | ms    | ICSP mode             |

| P13b                  | Tera  | Bulk/Row Erase cycle time                                                                                 | 0.8 | 2.6 | ms    | Enhanced<br>ICSP mode |

## TABLE 13-1: AC/DC CHARACTERISTICS (CONTINUED)

## APPENDIX A: DEVICE-SPECIFIC INFORMATION

## A.1 Checksum Computation

The checksum computation is described in **Section 6.8 "Checksum Computation"**. Table A-1 shows how this 16-bit computation can be made for each dsPIC30F device. Computations for read code protection are shown both enabled and disabled. The checksum values assume that the Configuration registers are also erased. However, when code protection is enabled, the value of the FGS register is assumed to be 0x5.

### A.2 dsPIC30F5011 and dsPIC30F5013

#### A.2.1 ICSP PROGRAMMING

The dsPIC30F5011 and dsPIC30F5013 processors require that the FBS and FSS registers be programmed with 0x0000 before the device is chip erased. The steps to perform this action are shown in Table 11-4.

#### A.2.2 ENHANCED ICSP PROGRAMMING

The dsPIC30F5011 and dsPIC30F5013 processors require that the FBS and FSS registers be programmed with 0x0000 using the PROGC command before the ERASEB command is used to erase the chip.

| Device       | Read Code<br>Protection | Checksum Computation | Erased<br>Value | Value with<br>0xAAAAAA at 0x0<br>and Last<br>Code Address |

|--------------|-------------------------|----------------------|-----------------|-----------------------------------------------------------|

| dsPIC30F2010 | Disabled                | CFGB+SUM(0:001FFF)   | 0xD406          | 0xD208                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F2011 | Disabled                | CFGB+SUM(0:001FFF)   | 0xD406          | 0xD208                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F2012 | Disabled                | CFGB+SUM(0:001FFF)   | 0xD406          | 0xD208                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F3010 | Disabled                | CFGB+SUM(0:003FFF)   | 0xA406          | 0xA208                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F3011 | Disabled                | CFGB+SUM(0:003FFF)   | 0xA406          | 0xA208                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F3012 | Disabled                | CFGB+SUM(0:003FFF)   | 0xA406          | 0xA208                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F3013 | Disabled                | CFGB+SUM(0:003FFF)   | 0xA406          | 0xA208                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F3014 | Disabled                | CFGB+SUM(0:003FFF)   | 0xA406          | 0xA208                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F4011 | Disabled                | CFGB+SUM(0:007FFF)   | 0x4406          | 0x4208                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F4012 | Disabled                | CFGB+SUM(0:007FFF)   | 0x4406          | 0x4208                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F4013 | Disabled                | CFGB+SUM(0:007FFF)   | 0x4406          | 0x4208                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F5011 | Disabled                | CFGB+SUM(0:00AFFF)   | 0xFC06          | 0xFA08                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F5013 | Disabled                | CFGB+SUM(0:00AFFF)   | 0xFC06          | 0xFA08                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

| dsPIC30F5015 | Disabled                | CFGB+SUM(0:00AFFF)   | 0xFC06          | 0xFA08                                                    |

|              | Enabled                 | CFGB                 | 0x0404          | 0x0404                                                    |

#### TABLE A-1: CHECKSUM COMPUTATION

Item Description:

**SUM(a:b)** = Byte sum of locations a to b inclusive (all 3 bytes of code memory)

CFGB = Configuration Block (masked) = Byte sum of ((FOSC&0xC10F) + (FWDT&0x803F) + (FBORPOR&0x87B3) + (FBS&0x310F) + (FSS&0x330F) + (FGS&0x0007) + (FICD&0xC003))