Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | SCI, SPI                                                   |

| Peripherals                | LVD, POR, PWM                                              |

| Number of I/O              | 33                                                         |

| Program Memory Size        | 16KB (16K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 512 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 8x8b                                                   |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 44-QFP                                                     |

| Supplier Device Package    | 44-QFP (10x10)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908gp16cfbe |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table of Contents

| 14.3.1   | External Pin Reset                           | 0 |

|----------|----------------------------------------------|---|

| 14.3.2   | Active Resets from Internal Sources          | 1 |

| 14.3.2.1 | Power-On Reset                               | 1 |

| 14.3.2.2 | Computer Operating Properly (COP) Reset      | 2 |

| 14.3.2.3 | Illegal Opcode Reset                         | 2 |

| 14.3.2.4 | Illegal Address Reset                        | 3 |

| 14.3.2.5 | Low-Voltage Inhibit (LVI) Reset 163          | 3 |

| 14.3.2.6 | Monitor Mode Entry Module Reset (MODRST) 163 | 3 |

| 14.4 SII | M Counter                                    | 3 |

| 14.4.1   | SIM Counter During Power-On Reset            | 3 |

| 14.4.2   | SIM Counter During Stop Mode Recovery 163    | 3 |

| 14.4.3   | SIM Counter and Reset States 163             | 3 |

| 14.5 Ex  | ception Control                              | 4 |

| 14.5.1   | Interrupts                                   | 4 |

| 14.5.1.1 | Hardware Interrupts                          | 6 |

| 14.5.1.2 | SWI Instruction                              | 6 |

| 14.5.1.3 | Interrupt Status Registers                   | 7 |

| 14.5.2   | Reset                                        | 8 |

| 14.5.3   | Break Interrupts                             | 8 |

| 14.5.4   | Status Flag Protection in Break Mode 169     | 9 |

| 14.6 Lo  | w-Power Modes                                | 9 |

| 14.6.1   | Wait Mode                                    | 9 |

| 14.6.2   | Stop Mode                                    | 0 |

| 14.7 SII | M Registers                                  | 1 |

| 14.7.1   | SIM Break Status Register                    |   |

| 14.7.2   | SIM Reset Status Register                    | 2 |

| 14.7.3   | SIM Break Flag Control Register 173          | 3 |

# Chapter 15 Serial Peripheral Interface Module (SPI)

| 15.1   | Introduction                          |

|--------|---------------------------------------|

| 15.2   | Features                              |

| 15.3   | Pin Name Conventions                  |

| 15.4   | Functional Description                |

| 15.4.1 | Master Mode                           |

| 15.4.2 | Slave Mode                            |

| 15.5   | Transmission Formats                  |

| 15.5.1 | Clock Phase and Polarity Controls 178 |

| 15.5.2 | Transmission Format When CPHA = 0 179 |

| 15.5.3 | Transmission Format When CPHA = 1 180 |

| 15.5.4 | Transmission Initiation Latency 180   |

| 15.6   | Queuing Transmission Data 181         |

| 15.7   | Error Conditions                      |

| 15.7.1 | Overflow Error                        |

| 15.7.2 | Mode Fault Error                      |

| 15.8   | Interrupts                            |

| 15.9   | Resetting the SPI 187                 |

#### Input/Output (I/O) Section

| Addr.                                      | Register Name                              |                 | Bit 7   | 6          | 5       | 4           | 3          | 2       | 1        | Bit 0   |

|--------------------------------------------|--------------------------------------------|-----------------|---------|------------|---------|-------------|------------|---------|----------|---------|

| \$0000                                     | Port A Data Register                       | Read:<br>Write: | PTA7    | PTA6       | PTA5    | PTA4        | PTA3       | PTA2    | PTA1     | PTA0    |

|                                            | (PTA)                                      | Reset:          |         |            |         | Unaffecte   | d by reset |         |          |         |

| \$0001                                     | Port B Data Register<br>(PTB)              | Read:<br>Write: | PTB7    | PTB6       | PTB5    | PTB4        | PTB3       | PTB2    | PTB1     | PTB0    |

|                                            | (гто)                                      | Reset:          |         |            |         | Unaffecte   | d by reset |         |          |         |

| \$0002                                     | Port C Data Register<br>(PTC)              | Read:<br>Write: | 0       | PTC6       | PTC5    | PTC4        | PTC3       | PTC2    | PTC1     | PTC0    |

|                                            | (1.10)                                     | Reset:          |         |            | 1       | Unaffecte   | d by reset |         |          |         |

| \$0003                                     | Port D Data Register<br>(PTD)              | Read:<br>Write: | PTD7    | PTD6       | PTD5    | PTD4        | PTD3       | PTD2    | PTD1     | PTD0    |

|                                            | (110)                                      | Reset:          |         |            | 1       | Unaffecte   | d by reset |         |          |         |

| \$0004                                     | Data Direction Register A<br>(DDRA)        | Read:<br>Write: | DDRA7   | DDRA6      | DDRA5   | DDRA4       | DDRA3      | DDRA2   | DDRA1    | DDRA0   |

|                                            | (DDIA)                                     | Reset:          | 0       | 0          | 0       | 0           | 0          | 0       | 0        | 0       |

| \$0005                                     | Data Direction Register B<br>(DDRB)        | Read:<br>Write: | DDRB7   | DDRB6      | DDRB5   | DDRB4       | DDRB3      | DDRB2   | DDRB1    | DDRB0   |

|                                            | (02112)                                    | Reset:          | 0       | 0          | 0       | 0           | 0          | 0       | 0        | 0       |

| \$0006 Data Direction Register C<br>(DDRC) | Read:<br>Write:                            | 0               | DDRC6   | DDRC5      | DDRC4   | DDRC3       | DDRC2      | DDRC1   | DDRC0    |         |

|                                            | Reset:                                     | 0               | 0       | 0          | 0       | 0           | 0          | 0       | 0        |         |

| \$0007                                     | \$0007 Data Direction Register D<br>(DDRD) | Read:<br>Write: | DDRD7   | DDRD6      | DDRD5   | DDRD4       | DDRD3      | DDRD2   | DDRD1    | DDRD0   |

|                                            | (6616)                                     | Reset:          | 0       | 0          | 0       | 0           | 0          | 0       | 0        | 0       |

|                                            | Port E Data Register                       | Read:           | 0       | 0          | 0       | 0           | 0          | 0       | PTE1     | PTE0    |

| \$0008                                     | (PTE)                                      | Write:          |         |            |         | Lineffecte  | d by we at |         |          |         |

|                                            |                                            | Reset:<br>Read: |         |            |         | Unanecte    | d by reset |         |          |         |

| \$0009                                     | Unimplemented                              | Write:          |         |            |         |             |            |         |          |         |

|                                            | F                                          | Reset:          | 0       | 0          | 0       | 0           | 0          | 0       | 0        | 0       |

|                                            |                                            | Read:           |         |            |         |             |            |         |          |         |

| \$000A                                     | Unimplemented                              | Write:          |         |            |         |             |            |         |          |         |

|                                            |                                            | Reset:          | 0       | 0          | 0       | 0           | 0          | 0       | 0        | 0       |

| #000D                                      | l la faca la consta d                      | Read:           |         |            |         |             |            |         |          |         |

| \$000B                                     | Unimplemented                              | Write:          | 0       | 0          | 0       | 0           | 0          | 0       | 0        | 0       |

|                                            |                                            | Read:           | 0       | 0          | 0       | 0           | 0          | 0       |          |         |

| \$000C                                     | Data Direction Register E                  | Write:          |         | Ŭ          | Ŭ       | Ŭ           | Ŭ          | •       | DDRE1    | DDRE0   |

|                                            | (DDRE)                                     | Reset:          | 0       | 0          | 0       | 0           | 0          | 0       | 0        | 0       |

| \$000D                                     | Port A Input Pullup Enable<br>Register     | Read:<br>Write: | PTAPUE7 | PTAPUE6    | PTAPUE5 | PTAPUE4     | PTAPUE3    | PTAPUE2 | PTAPUE1  | PTAPUE0 |

|                                            | (PTAPUE)                                   | Reset:          | 0       | 0          | 0       | 0           | 0          | 0       | 0        | 0       |

|                                            |                                            |                 |         | = Unimplem | ented   | R = Reserve | d          | U = Una | affected |         |

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 6)

#### NOTE

A security feature prevents viewing of the FLASH contents.<sup>(1)</sup>

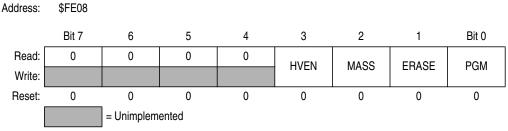

## 2.6.2 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

### HVEN — High-Voltage Enable Bit

This read/write bit enables the charge pump to drive high voltages for program and erase operations in the array. HVEN can only be set if either PGM = 1 or ERASE = 1 and the proper sequence for program or erase is followed.

1 = High voltage enabled to array and charge pump on

0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

Setting this read/write bit configures the 32Kbyte FLASH array for mass erase operation.

1 = MASS erase operation selected

0 = PAGE erase operation selected

#### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

1 = Erase operation selected

0 = Erase operation unselected

#### PGM — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

1 = Program operation selected

0 = Program operation unselected

## 2.6.3 FLASH Page Erase Operation

Use this step-by-step procedure to erase a page (128 bytes) of FLASH memory.

- 1. Set the ERASE bit, and clear the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the page address range of the block to be erased.

- 4. Wait for a time,  $t_{nvs}$  (min. 10 µs)

- 5. Set the HVEN bit.

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### FLASH Memory

During the programming cycle, make sure that all addresses being written to fit within one of the ranges specified above. Attempts to program addresses in different row ranges in one programming cycle will fail. Use this step-by-step procedure to program a row of FLASH memory (Figure 2-4 is a flowchart representation).

#### NOTE

Only bytes which are currently \$FF may be programmed.

- 1. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 2. Read from the FLASH block protect register.

- 3. Write any data to any FLASH address within the row address range desired.

- 4. Wait for a time,  $t_{nvs}$  (min. 10 µs).

- 5. Set the HVEN bit.

- 6. Wait for a time,  $t_{pqs}$  (min. 5  $\mu$ s).

- 7. Write data to the FLASH address to be programmed. (See note.)

- 8. Wait for a time,  $t_{PROG}$  (min. 30 µs).

- 9. Repeat step 7 and 8 until all the bytes within the row are programmed.

- 10. Clear the PGM bit. (See note.)

- 11. Wait for a time,  $t_{nvh}$  (min. 5  $\mu$ s).

- 12. Clear the HVEN bit.

- 13. After time, t<sub>RCV</sub> (typical 1 µs), the memory can be accessed in read mode again.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

Programming and erasing of FLASH locations can not be performed by code being executed from the same FLASH array.

#### NOTE

While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Care must be taken within the FLASH array memory space such as the COP control register (COPCTL) at \$FFFF.

#### NOTE

It is highly recommended that interrupts be disabled during program/ erase operations.

#### NOTE

Do not exceed  $t_{PROG}$  maximum or  $t_{HV}$  maximum.  $t_{HV}$  is defined as the cumulative high voltage programming time to the same row before next erase.  $t_{HV}$  must satisfy this condition:

$t_{NVS} + t_{NVH} + t_{PGS} + (t_{PROG} \times 64) \le t_{HV}$  maximum

Refer to 19.17 Memory Characteristics.

#### NOTE

The time between programming the FLASH address change (step 7 to step 7), or the time between the last FLASH programmed to clearing the

#### Low-Power Modes

## 3.3.2 Stop Mode

The break module is inactive in stop mode. The STOP instruction does not affect break module register states.

# 3.4 Central Processor Unit (CPU)

## 3.4.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

## 3.4.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

# 3.5 Clock Generator Module (CGM)

### 3.5.1 Wait Mode

The CGM remains active in wait mode. Before entering wait mode, software can disengage and turn off the PLL by clearing the BCS and PLLON bits in the PLL control register (PCTL). Less power-sensitive applications can disengage the PLL without turning it off. Applications that require the PLL to wake the MCU from wait mode also can deselect the PLL output without turning off the PLL.

### 3.5.2 Stop Mode

If the OSCSTOPEN bit in the CONFIG register is cleared (default), then the STOP instruction disables the CGM (oscillator and phase-locked loop) and holds low all CGM outputs (CGMXCLK, CGMOUT, and CGMINT).

If the OSCSTOPEN bit in the CONFIG register is set, then the phase locked loop is shut off but the oscillator will continue to operate in stop mode.

# 3.6 Computer Operating Properly Module (COP)

#### 3.6.1 Wait Mode

The COP remains active in wait mode. To prevent a COP reset during wait mode, periodically clear the COP counter in a CPU interrupt routine.

Low-Power Modes

# 3.10 Serial Communications Interface Module (SCI)

## 3.10.1 Wait Mode

The SCI module remains active in wait mode. Any enabled CPU interrupt request from the SCI module can bring the MCU out of wait mode.

If SCI module functions are not required during wait mode, reduce power consumption by disabling the module before executing the WAIT instruction.

## 3.10.2 Stop Mode

The SCI module is inactive in stop mode. The STOP instruction does not affect SCI register states. SCI module operation resumes after the MCU exits stop mode.

Because the internal clock is inactive during stop mode, entering stop mode during an SCI transmission or reception results in invalid data.

# 3.11 Serial Peripheral Interface Module (SPI)

## 3.11.1 Wait Mode

The SPI module remains active in wait mode. Any enabled CPU interrupt request from the SPI module can bring the MCU out of wait mode.

If SPI module functions are not required during wait mode, reduce power consumption by disabling the SPI module before executing the WAIT instruction.

### 3.11.2 Stop Mode

The SPI module is inactive in stop mode. The STOP instruction does not affect SPI register states. SPI operation resumes after an external interrupt. If stop mode is exited by reset, any transfer in progress is aborted, and the SPI is reset.

# 3.12 Timer Interface Module (TIM1 and TIM2)

### 3.12.1 Wait Mode

The TIM remains active in wait mode. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

## 3.12.2 Stop Mode

The TIM is inactive in stop mode. The STOP instruction does not affect register states or the state of the TIM counter. TIM operation resumes when the MCU exits stop mode after an external interrupt.

Analog-to-Digital Converter (ADC)

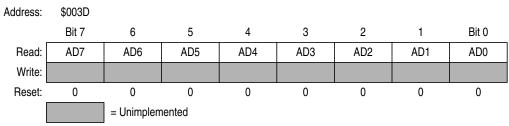

## 4.7.2 ADC Data Register

One 8-bit result register, ADC data register (ADR), is provided. This register is updated each time an ADC conversion completes.

Figure 4-3. ADC Data Register (ADR)

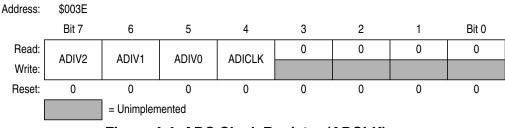

## 4.7.3 ADC Clock Register

The ADC clock register (ADCLK) selects the clock frequency for the ADC.

Figure 4-4. ADC Clock Register (ADCLK)

### ADIV2–ADIV0 — ADC Clock Prescaler Bits

ADIV2–ADIV0 form a 3-bit field which selects the divide ratio used by the ADC to generate the internal ADC clock. Table 4-2 shows the available clock configurations. The ADC clock should be set to approximately 1 MHz.

| ADIV2 | ADIV1 | ADIV0 | ADC Clock Rate       |

|-------|-------|-------|----------------------|

| 0     | 0     | 0     | ADC input clock ÷ 1  |

| 0     | 0     | 1     | ADC input clock ÷ 2  |

| 0     | 1     | 0     | ADC input clock ÷ 4  |

| 0     | 1     | 1     | ADC input clock ÷ 8  |

| 1     | Х     | Х     | ADC input clock ÷ 16 |

Table 4-2. ADC Clock Divide Ratio

X = don't care

#### Z — Zero Flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00.

- 1 = Zero result

- 0 = Non-zero result

### C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.

1 = Carry out of bit 7

0 = No carry out of bit 7

# 8.4 Arithmetic/Logic Unit (ALU)

The ALU performs the arithmetic and logic operations defined by the instruction set.

Refer to the *CPU08 Reference Manual* (document order number CPU08RM/AD) for a description of the instructions and addressing modes and more detail about the architecture of the CPU.

## 8.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

### 8.5.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

### 8.5.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

# 8.6 CPU During Break Interrupts

If a break module is present on the MCU, the CPU starts a break interrupt by:

- · Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC:\$FFFD or with \$FEFC:\$FEFD in monitor mode

The break interrupt begins after completion of the CPU instruction in progress. If the break address register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the MCU to normal operation if the break interrupt has been deasserted.

# Chapter 12 Input/Output (I/O) Ports

# 12.1 Introduction

Thirty-three (33) bidirectional input-output (I/O) pins form five parallel ports. All I/O pins are programmable as inputs or outputs. All individual bits within port A, port C, and port D are software configurable with pullup devices if configured as input port bits. The pullup devices are automatically and dynamically disabled when a port bit is switched to output mode.

Input pins and I/O port pins that are not used in the application must be terminated. This prevents excess current caused by floating inputs, and enhances immunity during noise or transient events. Termination methods include:

- 1. Configuring unused pins as outputs and driving high or low;

- 2. Configuring unused pins as inputs and enabling internal pull-ups;

- 3. Configuring unused pins as inputs and using external pull-up or pull-down resistors.

Never connect unused pins directly to  $V_{DD}$  or  $V_{SS}$ .

Since some general-purpose I/O pins are not available on all packages, these pins must be terminated as well. Either method 1 or 2 above are appropriate.

| Addr.  | Register Name                 |                 | Bit 7                     | 6                                                                                                                                                                                                                                                | 5     | 4         | 3          | 2    | 1    | Bit 0 |  |  |

|--------|-------------------------------|-----------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|------------|------|------|-------|--|--|

| \$0000 | Port A Data Register<br>(PTA) | Read:<br>Write: | PTA7                      | PTA6                                                                                                                                                                                                                                             | PTA5  | PTA4      | PTA3       | PTA2 | PTA1 | PTA0  |  |  |

|        | ( )                           | Reset:          |                           | PTA6    PTA5    PTA4    PTA3      Unaffected by reset    Unaffected by reset      PTB6    PTB5    PTB4    PTB3      Unaffected by reset    Unaffected by reset      PTC6    PTC5    PTC4    PTC3      Unaffected by reset    Unaffected by reset |       |           |            |      |      |       |  |  |

| \$0001 | Port B Data Register<br>(PTB) | Read:<br>Write: | PTB7                      | PTB6                                                                                                                                                                                                                                             | PTB5  | PTB4      | PTB3       | PTB2 | PTB1 | PTB0  |  |  |

|        | ( )                           | Reset:          | eset: Unaffected by reset |                                                                                                                                                                                                                                                  |       |           |            |      |      |       |  |  |

| \$0002 | Port C Data Register          | Read:<br>Write: | 0                         | PTC6                                                                                                                                                                                                                                             | PTC5  | PTC4      | PTC3       | PTC2 | PTC1 | PTC0  |  |  |

|        | (PTC)                         | Reset:          |                           |                                                                                                                                                                                                                                                  |       | Unaffecte | d by reset |      |      |       |  |  |

| \$0003 | Port D Data Register<br>(PTD) | Read:<br>Write: | PTD7                      | PTD6                                                                                                                                                                                                                                             | PTD5  | PTD4      | PTD3       | PTD2 | PTD1 | PTD0  |  |  |

|        | ( )                           | Reset:          |                           |                                                                                                                                                                                                                                                  |       | Unaffecte | d by reset |      |      |       |  |  |

|        |                               |                 |                           | = Unimplem                                                                                                                                                                                                                                       | ented |           |            |      |      |       |  |  |

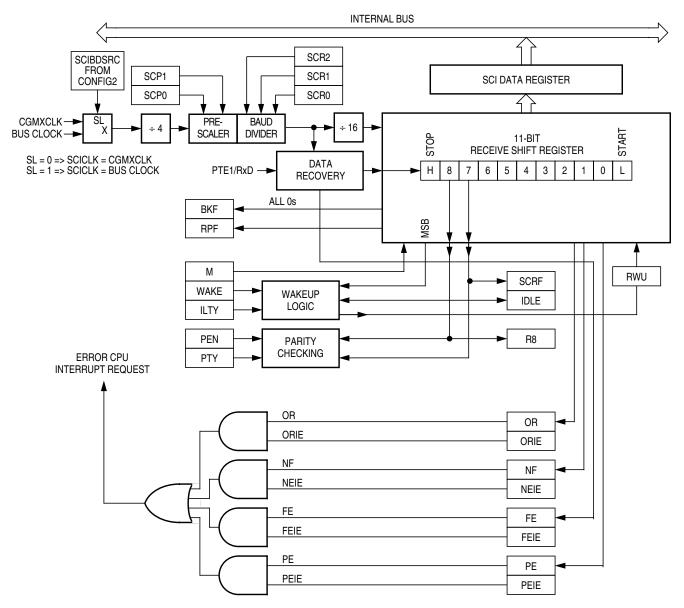

Serial Communications Interface Module (SCI)

Figure 13-5. SCI Receiver Block Diagram

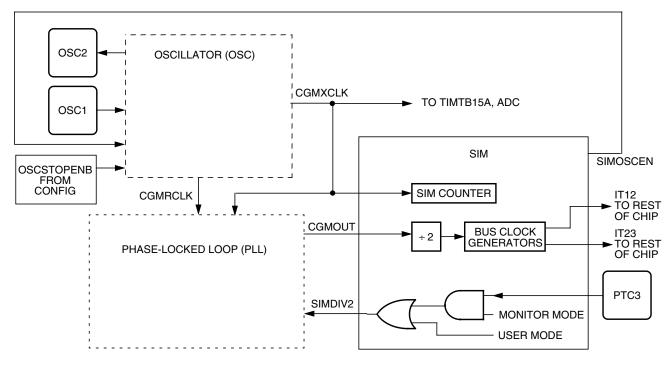

**SIM Bus Clock Control and Generation**

| Addr.                                     | Register Name                              |                 | Bit 7           | 6    | 5    | 4          | 3    | 2   | 1    | Bit 0 |

|-------------------------------------------|--------------------------------------------|-----------------|-----------------|------|------|------------|------|-----|------|-------|

| \$FE03                                    | SIM Break Flag Control<br>Register (SBFCR) | Read:<br>Write: | BCFE            | R    | R    | R          | R    | R   | R    | R     |

|                                           |                                            | Reset:          | 0               |      | -    |            |      |     |      |       |

|                                           |                                            | Read:           | IF6             | IF5  | IF4  | IF3        | IF2  | IF1 | 0    | 0     |

| \$FE04 Interrupt Status Register 1 (INT1) | Write:                                     | R               | R               | R    | R    | R          | R    | R   | R    |       |

|                                           | (                                          | Reset:          | 0               | 0    | 0    | 0          | 0    | 0   | 0    | 0     |

|                                           |                                            | Read:           | IF14            | IF13 | IF12 | IF11       | IF10 | IF9 | IF8  | IF7   |

| \$FE05                                    | Interrupt Status Register 2<br>(INT2)      | Write:          | R               | R    | R    | R          | R    | R   | R    | R     |

|                                           | (                                          | Reset:          | 0               | 0    | 0    | 0          | 0    | 0   | 0    | 0     |

|                                           |                                            | Read:           | 0               | 0    | 0    | 0          | 0    | 0   | IF16 | IF15  |

| \$FE06                                    | Interrupt Status Register 3<br>(INT3)      | Write:          | R               | R    | R    | R          | R    | R   | R    | R     |

|                                           | (1110)                                     | Reset:          | 0               | 0    | 0    | 0          | 0    | 0   | 0    | 0     |

|                                           |                                            | [               | = Unimplemented |      | R    | = Reserved |      |     |      |       |

Figure 14-2. SIM I/O Register Summary (Continued)

# 14.2 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, CGMOUT, as shown in Figure 14-3. This clock can come from either an external oscillator or from the on-chip PLL. (See Chapter 5 Clock Generator Module (CGM).)

Figure 14-3. CGM Clock Signals

System Integration Module (SIM)

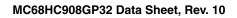

## 14.7.1 SIM Break Status Register

The SIM break status register (SBSR) contains a flag to indicate that a break caused an exit from wait mode.

Note: Writing a logic 0 clears SBSW.

### Figure 14-20. SIM Break Status Register (SBSR)

### SBSW — SIM Break Stop/Wait

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it.

1 = Wait mode was exited by break interrupt.

0 = Wait mode was not exited by break interrupt.

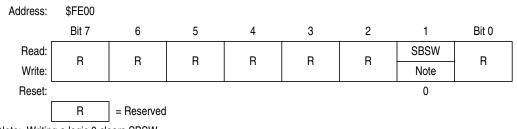

## 14.7.2 SIM Reset Status Register

The SRSR register contains flags that show the source of the last reset. The status register will automatically clear after reading SRSR. A power-on reset sets the POR bit and clears all other bits in the register. All other reset sources set the individual flag bits but do not clear the register. More than one reset source can be flagged at any time depending on the conditions at the time of the internal or external reset. For example, the POR and LVI bit can both be set if the power supply has a slow rise time.

Figure 14-21. SIM Reset Status Register (SRSR)

### POR — Power-On Reset Bit

- 1 = Last reset caused by POR circuit

- 0 = Read of SRSR

#### PIN — External Reset Bit

- 1 = Last reset caused by external reset pin ( $\overline{RST}$ )

- 0 = POR or read of SRSR

### COP — Computer Operating Properly Reset Bit

- 1 = Last reset caused by COP counter

- 0 = POR or read of SRSR

Serial Peripheral Interface Module (SPI)

# **15.4 Functional Description**

Figure 15-1 summarizes the SPI I/O registers and Figure 15-2 shows the structure of the SPI module.

| Addr.                                             | Register Name                              |                 | Bit 7           | 6    | 5      | 4                   | 3      | 2      | 1    | Bit 0 |

|---------------------------------------------------|--------------------------------------------|-----------------|-----------------|------|--------|---------------------|--------|--------|------|-------|

| \$0010                                            | \$0010 SPI Control Register (SPCR)         | Read:<br>Write: | SPRIE           | R    | SPMSTR | CPOL                | CPHA   | SPWOM  | SPE  | SPTIE |

|                                                   | Reset:                                     | 0               | 0               | 1    | 0      | 1                   | 0      | 0      | 0    |       |

| \$0011 SPI Status and Control<br>Bogister (SPSCP) | Read:                                      | SPRF            | ERRIE           | OVRF | MODF   | SPTE                | MODFEN | SPR1   | SPR0 |       |

|                                                   | SPI Status and Control<br>Register (SPSCR) | Write:          |                 |      |        |                     |        | WODFEN | SPRI | SPRU  |

|                                                   |                                            | Reset:          | 0               | 0    | 0      | 0                   | 1      | 0      | 0    | 0     |

|                                                   |                                            | Read:           | R7              | R6   | R5     | R4                  | R3     | R2     | R1   | R0    |

| \$0012                                            | SPI Data Register<br>(SPDR)                | Write:          | T7              | T6   | T5     | T4                  | Т3     | T2     | T1   | Т0    |

|                                                   |                                            | Reset:          |                 | •    |        | Unaffected by reset |        |        |      |       |

|                                                   |                                            | [               | = Unimplemented |      |        | R                   | = Res  | erved  |      |       |

Figure 15-1. SPI I/O Register Summary

The SPI module allows full-duplex, synchronous, serial communication between the MCU and peripheral devices, including other MCUs. Software can poll the SPI status flags or SPI operation can be interrupt-driven.

If a port bit is configured for input, then an internal pullup device may be enabled for that port bit. (See 12.4.3 Port C Input Pullup Enable Register.)

The following paragraphs describe the operation of the SPI module.

### 15.4.1 Master Mode

The SPI operates in master mode when the SPI master bit, SPMSTR, is set.

NOTE

Configure the SPI modules as master or slave before enabling them. Enable the master SPI before enabling the slave SPI. Disable the slave SPI before disabling the master SPI. (See 15.13.1 SPI Control Register.)

Only a master SPI module can initiate transmissions. Software begins the transmission from a master SPI module by writing to the transmit data register. If the shift register is empty, the byte immediately transfers to the shift register, setting the SPI transmitter empty bit, SPTE. The byte begins shifting out on the MOSI pin under the control of the serial clock. (See Figure 15-3.)

The SPR1 and SPR0 bits control the baud rate generator and determine the speed of the shift register. (See 15.13.2 SPI Status and Control Register.) Through the SPSCK pin, the baud rate generator of the master also controls the shift register of the slave peripheral.

As the byte shifts out on the MOSI pin of the master, another byte shifts in from the slave on the master's MISO pin. The transmission ends when the receiver full bit, SPRF, becomes set. At the same time that SPRF becomes set, the byte from the slave transfers to the receive data register. In normal operation, SPRF signals the end of a transmission. Software clears SPRF by reading the SPI status and control register with SPRF set and then reading the SPI data register. Writing to the SPI data register clears the SPTE bit.

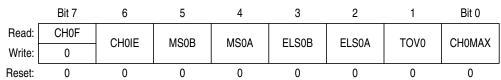

# 17.5 Interrupts

The following TIM sources can generate interrupt requests:

- TIM overflow flag (TOF) The TOF bit is set when the TIM counter reaches the modulo value programmed in the TIM counter modulo registers. The TIM overflow interrupt enable bit, TOIE, enables TIM overflow CPU interrupt requests. TOF and TOIE are in the TIM status and control register.

- TIM channel flags (CH1F:CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. Channel x TIM CPU interrupt requests are controlled by the channel x interrupt enable bit, CHxIE. Channel x TIM CPU interrupt requests are enabled when CHxIE = 1. CHxF and CHxIE are in the TIM channel x status and control register.

# **17.6 Low-Power Modes**

The WAIT and STOP instructions put the MCU in low power- consumption standby modes.

### 17.6.1 Wait Mode

The TIM remains active after the execution of a WAIT instruction. In wait mode, the TIM registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

## 17.6.2 Stop Mode

The TIM is inactive after the execution of a STOP instruction. The STOP instruction does not affect register conditions or the state of the TIM counter. TIM operation resumes when the MCU exits stop mode after an external interrupt.

# 17.7 TIM During Break Interrupts

A break interrupt stops the TIM counter.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear status bits during the break state. See 14.7.3 SIM Break Flag Control Register.

To allow software to clear status bits during a break interrupt, write a logic 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a 2-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at logic 0. After the break, doing the second step clears the status bit.

#### **TOIE** — **TIM** Overflow Interrupt Enable Bit

This read/write bit enables TIM overflow interrupts when the TOF bit becomes set. Reset clears the TOIE bit.

1 = TIM overflow interrupts enabled

0 = TIM overflow interrupts disabled

#### TSTOP — TIM Stop Bit

This read/write bit stops the TIM counter. Counting resumes when TSTOP is cleared. Reset sets the TSTOP bit, stopping the TIM counter until software clears the TSTOP bit.

- 1 = TIM counter stopped

- 0 = TIM counter active

#### NOTE

Do not set the TSTOP bit before entering wait mode if the TIM is required to exit wait mode.

#### TRST — TIM Reset Bit

Setting this write-only bit resets the TIM counter and the TIM prescaler. Setting TRST has no effect on any other registers. Counting resumes from \$0000. TRST is cleared automatically after the TIM counter is reset and always reads as logic 0. Reset clears the TRST bit.

1 = Prescaler and TIM counter cleared

0 = No effect

#### NOTE

Setting the TSTOP and TRST bits simultaneously stops the TIM counter at a value of \$0000.

#### PS[2:0] — Prescaler Select Bits

These read/write bits select one of the seven prescaler outputs as the input to the TIM counter as Table 17-2 shows. Reset clears the PS[2:0] bits.

| PS2 | PS1 | PS0 | TIM Clock Source        |

|-----|-----|-----|-------------------------|

| 0   | 0   | 0   | Internal bus clock ÷ 1  |

| 0   | 0   | 1   | Internal bus clock ÷ 2  |

| 0   | 1   | 0   | Internal bus clock ÷ 4  |

| 0   | 1   | 1   | Internal bus clock ÷ 8  |

| 1   | 0   | 0   | Internal bus clock ÷ 16 |

| 1   | 0   | 1   | Internal bus clock ÷ 32 |

| 1   | 1   | 0   | Internal bus clock ÷ 64 |

| 1   | 1   | 1   | Not available           |

#### Table 17-2. Prescaler Selection

#### 17.9.2 TIM Counter Registers

The two read-only TIM counter registers contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

## 17.9.4 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Address: T1SC0, \$0025 and T2SC0, \$0030

Figure 17-9. TIM Channel 0 Status and Control Register (TSC0)

|        | Bit 7 | 6          | 5               | 4      | 3     | 2     | 1    | Bit 0  |  |  |  |

|--------|-------|------------|-----------------|--------|-------|-------|------|--------|--|--|--|

| Read:  | CH1F  | CH1IE      | 0               | MS1A   | ELS1B | ELS1A | TOV1 | CH1MAX |  |  |  |

| Write: | 0     | OTTIL      |                 | INISTA | ELGID |       |      |        |  |  |  |

| Reset: | 0     | 0          | 0               | 0      | 0     | 0     | 0    | 0      |  |  |  |

|        |       | = Unimplem | - Unimplemented |        |       |       |      |        |  |  |  |

Figure 17-10. TIM Channel 1 Status and Control Register (TSC1)

#### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM counter registers matches the value in the TIM channel x registers.

When TIM CPU interrupt requests are enabled (CHxIE = 1), clear CHxF by reading TIM channel x status and control register with CHxF set and then writing a logic 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing logic 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a logic 1 to CHxF has no effect.

1 = Input capture or output compare on channel x

0 = No input capture or output compare on channel x

#### CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM CPU interrupt service requests on channel x. Reset clears the CHxIE bit.

1 = Channel x CPU interrupt requests enabled

0 = Channel x CPU interrupt requests disabled

#### **Development Support**

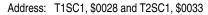

## Figure 18-1. Break Module Block Diagram

| Addr.        | Register Name                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 7 | 6            | 5     | 4     | 3          | 2     | 1                           | Bit 0 |

|--------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|-------|-------|------------|-------|-----------------------------|-------|

| \$FE00       | SIM Break Status Register<br>(SBSR)                         | Read:<br>Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R     | R            | R     | R     | R          | R     | SBSW<br>Note <sup>(1)</sup> | R     |

|              | See page 218.                                               | Reset:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       | •            |       | •     |            |       | 0                           |       |

| \$FE02       | Reserved                                                    | Read:<br>Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R     | R            | R     | R     | R          | R     | R                           | R     |

|              |                                                             | Reset:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     | 0            | 0     | 0     | 0          | 0     | 0                           | 0     |

| \$FE03       | SIM Break Flag Control<br>Register (SBFCR)<br>See page 219. | Read:<br>Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BCFE  | R            | R     | R     | R          | R     | R                           | R     |

|              |                                                             | Reset:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     |              |       |       |            |       |                             |       |

| \$FE09       | Break Address High<br>Register (BRKH)                       | Read:<br>Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit15 | Bit14        | Bit13 | Bit12 | Bit11      | Bit10 | Bit9                        | Bit8  |

|              | See page 218.                                               | R (Status Register<br>(SBSR)RRRSee page 218.Reset:See page 218.Reset:ReservedRead:RReservedWrite:RReset:00reak Flag Control<br>Register (SBFCR)Read:BCFERegister (SBFCR)Write:BCFESee page 219.Read:Register (BRKH)<br>See page 218.Read:Bit15Bit14Bit15Bit14Bit7Bit 6Bit 7Bit 6Bit 7Bit 6Bit 8Reset:See page 218.Reset:Reset:0Rest:0Bit 9Reset:See page 218.Reset:Reset:0Bit 6Bit 5See page 218.Reset:Reset:0Bit 6Bit 5See page 218.Reset:Reset:0Bit 6Bit 5See page 218.Reset:Reset:0Bit 6Bit 5Reset:0O0Reset:0O0Reset:0O0Reset:0O0Reset:0Reset:0Reset:0Reset:0Reset:0Reset:0Reset:0Reset:0Reset:0Reset:0Reset:0 <t< td=""><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td></t<> | 0     | 0            | 0     | 0     | 0          | 0     |                             |       |

| \$FE0A       | Break Address Low<br>Register (BRKL)                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1                       | Bit 0 |

|              | See page 218.                                               | Reset:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     | 0            | 0     | 0     | 0          | 0     | 0                           | 0     |

|              | Break Status and Control                                    | Read:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PDVE  | PDKA         | 0     | 0     | 0          | 0     | 0                           | 0     |

| \$FE0B       | Register (BRKSCR)                                           | Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DAKE  |              |       |       |            |       |                             |       |

|              | See page 218.                                               | Reset:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0     | 0            | 0     | 0     | 0          | 0     | 0                           | 0     |

| 1. Writing a | a 0 clears SBSW.                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | ] = Unimplem | ented | R     | = Reserved |       |                             |       |

Figure 18-2. Break I/O Register Summary

# **19.6 3.0-V DC Electrical Characteristics**

| Characteristic <sup>(1)</sup>                                      | Symbol           | Min                                            | Тур <sup>(2)</sup> | Мах                | Unit     |

|--------------------------------------------------------------------|------------------|------------------------------------------------|--------------------|--------------------|----------|

| Output high voltage<br>(I <sub>Load</sub> = -0.6 mA) all I/O pins  | V <sub>OH</sub>  | V <sub>DD</sub> – 0.3                          |                    |                    |          |

| $(I_{Load} = -4.0 \text{ mA})$ all I/O pins                        | V <sub>OH</sub>  | V <sub>DD</sub> – 0.3<br>V <sub>DD</sub> – 1.0 | _                  |                    | V<br>V   |

| $(I_{Load} = -4.0 \text{ mA})$ pins PTC0–PTC4 only                 | V <sub>OH</sub>  | $V_{DD} = 1.0$<br>$V_{DD} = 0.5$               |                    |                    | v        |

| Maximum combined I <sub>OH</sub> for port C, port E,               | I <sub>OH1</sub> |                                                | _                  | 30                 | mA       |

| port PTD0–PTD3                                                     | _                |                                                |                    |                    |          |

| Maximum combined I <sub>OH</sub> for port PTD4–PTD7,               | I <sub>OH2</sub> | —                                              | _                  | 30                 | mA       |

| port A, port B                                                     |                  |                                                | _                  | 60                 | mA       |

| Maximum total I <sub>OH</sub> for all port pins                    | Іонт             |                                                |                    |                    |          |

| Output low voltage                                                 |                  |                                                |                    |                    |          |

| (I <sub>Load</sub> = 0.5 mA) all I/O pins                          | V <sub>OL</sub>  | _                                              | _                  | 0.3                | v        |

| (I <sub>Load</sub> = 6.0 mA) all I/O pins                          | V <sub>OL</sub>  | _                                              | _                  | 1.0                | v        |

| (I <sub>Load</sub> = 10.0 mA) pins PTC0–PTC4 only                  | V <sub>OL</sub>  | —                                              | —                  | 0.8                | V        |

| Maximum combined I <sub>OL</sub> for port C, port E,               | I <sub>OL1</sub> | —                                              | —                  | 30                 | mA       |

| port PTD0–PTD3                                                     | .                |                                                |                    | 30                 | mA       |

| Maximum combined I <sub>OL</sub> for port PTD4–PTD7,               | I <sub>OL2</sub> | _                                              |                    | 50                 |          |

| port A, port B                                                     | IOLT             | —                                              | _                  | 60                 | mA       |

| Maximum total I <sub>OL</sub> for all port pins                    |                  |                                                |                    |                    |          |

| Input high voltage<br>All ports, IRQ, RST, OSC1                    | V <sub>IH</sub>  | $0.7 	imes V_{DD}$                             | —                  | V <sub>DD</sub>    | V        |

| Input low voltage<br>All ports, IRQ, RST, OSC1                     | VIL              | V <sub>SS</sub>                                | —                  | $0.3 	imes V_{DD}$ | v        |

| V <sub>DD</sub> supply current                                     |                  |                                                |                    |                    |          |

| Run <sup>(3)</sup>                                                 |                  |                                                | 4 5                | 0                  | m 4      |

| Wait <sup>(4)</sup>                                                |                  |                                                | 4.5<br>1.65        | 8<br>4             | mA<br>mA |

|                                                                    |                  |                                                |                    |                    |          |

| Stop <sup>(5)</sup>                                                | I <sub>DD</sub>  |                                                |                    |                    |          |

| 25 °C                                                              | -00              | —                                              | 2                  | —                  | μA       |

| 25 °C with TBM enabled <sup>(6)</sup>                              |                  | _                                              | 12<br>200          |                    | μΑ<br>μΑ |

| 25 °C with LVI and TBM enabled <sup>(6)</sup>                      |                  |                                                | 30                 |                    | μΑ<br>μΑ |

| -40 °C to 85 °C with TBM enabled <sup>(6)</sup>                    |                  | _                                              | 300                | _                  | μA       |

| -40 °C to 85 °C with LVI and TBM enabled <sup>(6)</sup>            |                  |                                                |                    |                    |          |

| DC injection current <sup>(7) (8) (9) (10)</sup>                   |                  |                                                |                    |                    |          |

| Single pin limit                                                   |                  |                                                |                    |                    |          |

| $V_{in} > V_{DD}$                                                  | .                | 0                                              | —                  | 2                  |          |

| V <sub>in</sub> < V <sub>SS</sub>                                  | I <sub>IC</sub>  | 0                                              | -                  | -0.2               | mA       |

| Total MCU limit, includes sum of all stressed pins $V_{1} > V_{2}$ |                  | 0                                              | _                  | 25                 |          |

| $V_{in} > V_{DD}$<br>$V_{in} < V_{SS}$                             |                  | 0                                              | _                  | -5                 |          |

| I/O ports Hi-Z leakage current <sup>(11)</sup>                     | IIL              |                                                |                    | ±10                | μA       |

|                                                                    |                  |                                                |                    |                    |          |

| Input current                                                      | lIn              |                                                | _                  | ±1                 | μΑ       |

Contined on next page

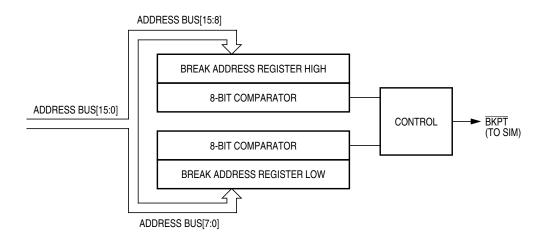

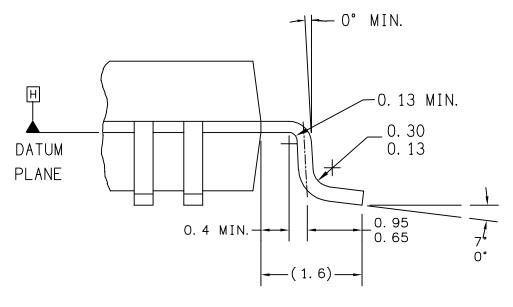

DETAIL "A"

SECTION B-B VIEW ROTATED 90°

DETAIL "C"

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA   | LOUTLINE      | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-------------|---------------|------------------|-------------|

| TITLE:<br>44LD QFP,<br>10X10X2.0 PKG, 0.8 PITCH         | DOCUMENT NO | : 98ASB42839B | REV: B           |             |

|                                                         | РІТСН       | CASE NUMBER   | : 824A-01        | 06 APR 2005 |

|                                                         |             | STANDARD: NC  | N-JEDEC          |             |

NOTES:

- 1. DIMENSIONS AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DATUMPLANE -H- IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUMS A-B AND -D- TO BE DETERMINED AT DATUM PLANE -H-.

- 5 This dimension to be determined at seating plane -C-.

- 6. THIS DIMENSION DO NOT INCLUDE MOLD PROTRUSION, ALLOWABLE PROTRUSION IS 0.25 PER SIDE, DIMENSIONS A AND B DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE -H-.

- THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSTION, ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT.

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. | L OUTLINE    | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--------------|------------------|-------------|

| TITLE:                                                  | DOCUMENT NO  | ): 98ASB42839B   | REV: B      |

| 44LD QFP,<br>10X10X2.0 PKG, 0.8 PITCH                   | CASE NUMBER  | R: 824A-01       | 06 APR 2005 |

| 10//10//2. 0 11/0, 0. 0 1 11011                         | STANDARD: NO | DN-JEDEC         |             |