Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                    |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 33                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x8b                                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-QFP                                                                 |

| Supplier Device Package    | 44-QFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gp32cfber |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC68HC908GP32

Data Sheet

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2001, 2006, 2008. All rights reserved.

General Description

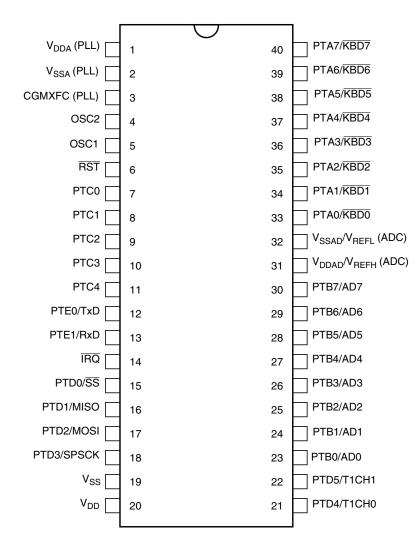

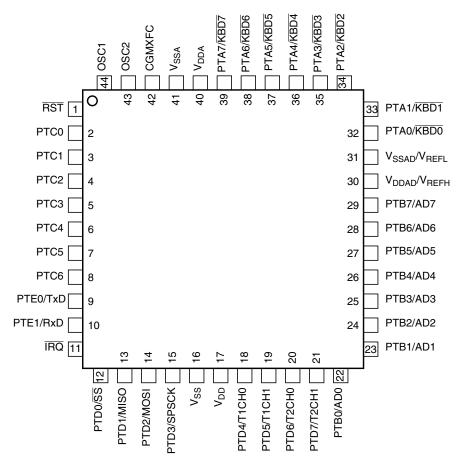

# **1.4 Pin Assignments**

| Pins Not Available<br>on 40-Pin Package | Internal<br>Connection |

|-----------------------------------------|------------------------|

| PTC5                                    | Connected to ground    |

| PTC6                                    | Connected to ground    |

| PTD6/T2CH0                              | Unconnected            |

| PTD7/T2CH1                              | Unconnected            |

#### Figure 1-2. 40-Pin PDIP Pin Assignments

**General Description**

Figure 1-4. 44-Pin QFP Pin Assignments

# **1.5 Pin Functions**

Descriptions of the pin functions are provided here.

### 1.5.1 Power Supply Pins ( $V_{DD}$ and $V_{SS}$ )

V<sub>DD</sub> and V<sub>SS</sub> are the power supply and ground pins. The MCU operates from a single power supply.

Fast signal transitions on MCU pins place high, short-duration current demands on the power supply. To prevent noise problems, take special care to provide power supply bypassing at the MCU as Figure 1-5 shows. Place the C1 bypass capacitor as close to the MCU as possible. Use a high-frequency-response ceramic capacitor for C1. C2 is an optional bulk current bypass capacitor for use in applications that require the port pins to source high current levels.

#### Low-Power Modes

### 3.3.2 Stop Mode

The break module is inactive in stop mode. The STOP instruction does not affect break module register states.

# 3.4 Central Processor Unit (CPU)

### 3.4.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

### 3.4.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

### 3.5 Clock Generator Module (CGM)

#### 3.5.1 Wait Mode

The CGM remains active in wait mode. Before entering wait mode, software can disengage and turn off the PLL by clearing the BCS and PLLON bits in the PLL control register (PCTL). Less power-sensitive applications can disengage the PLL without turning it off. Applications that require the PLL to wake the MCU from wait mode also can deselect the PLL output without turning off the PLL.

#### 3.5.2 Stop Mode

If the OSCSTOPEN bit in the CONFIG register is cleared (default), then the STOP instruction disables the CGM (oscillator and phase-locked loop) and holds low all CGM outputs (CGMXCLK, CGMOUT, and CGMINT).

If the OSCSTOPEN bit in the CONFIG register is set, then the phase locked loop is shut off but the oscillator will continue to operate in stop mode.

### 3.6 Computer Operating Properly Module (COP)

#### 3.6.1 Wait Mode

The COP remains active in wait mode. To prevent a COP reset during wait mode, periodically clear the COP counter in a CPU interrupt routine.

# Chapter 4 Analog-to-Digital Converter (ADC)

## 4.1 Introduction

This section describes the 8-bit analog-to-digital converter (ADC).

## 4.2 Features

Features of the ADC module include:

- Eight channels with multiplexed input

- Linear successive approximation with monotonicity

- 8-bit resolution

- Single or continuous conversion

- Conversion complete flag or conversion complete interrupt

- Selectable ADC clock

# 4.3 Functional Description

The ADC provides eight pins for sampling external sources at pins PTB7/AD7–PTB0/AD0. An analog multiplexer allows the single ADC converter to select one of eight ADC channels as ADC voltage in  $(V_{ADIN})$ .  $V_{ADIN}$  is converted by the successive approximation register-based analog-to-digital converter. When the conversion is completed, ADC places the result in the ADC data register and sets a flag or generates an interrupt. (See Figure 4-1.)

### 4.3.1 ADC Port I/O Pins

PTB7/AD7–PTB0/AD0 are general-purpose I/O (input/output) pins that share with the ADC channels. The channel select bits define which ADC channel/port pin will be used as the input signal. The ADC overrides the port I/O logic by forcing that pin as input to the ADC. The remaining ADC channels/port pins are controlled by the port I/O logic and can be used as general-purpose I/O. Writes to the port register or DDR will not have any affect on the port pin that is selected by the ADC. Read of a port pin in use by the ADC will return a logic 0.

### 4.3.2 Voltage Conversion

When the input voltage to the ADC equals  $V_{REFH}$ , the ADC converts the signal to \$FF (full scale). If the input voltage equals  $V_{REFL}$ , the ADC converts it to \$00. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are a straight-line linear conversion.

#### NOTE

Inside the ADC module, the reference voltages  $V_{REFH}$  is connected to the ADC analog power,  $V_{DDAD}$ ; and  $V_{REFL}$  is connected to the ADC analog ground,  $V_{SSAD}$ . Therefore, the ADC input voltage should not exceed these analog supply voltages.

9. Calculate and verify the adequacy of the VCO programmed center-of-range frequency, f<sub>VRS</sub>. The center-of-range frequency is the midpoint between the minimum and maximum frequencies attainable by the PLL.

$$f_{VRS} = (L \times 2^E) f_{NOM}$$

For proper operation,

$$\left|f_{VRS} - f_{VCLK}\right| \le \frac{f_{NOM} \times 2^{E}}{2}$$

Verify the choice of P, R, N, E, and L by comparing f<sub>VCLK</sub> to f<sub>VRS</sub> and f<sub>VCLKDES</sub>. For proper operation, f<sub>VCLK</sub> must be within the application's tolerance of f<sub>VCLKDES</sub>, and f<sub>VRS</sub> must be as close as possible to f<sub>VCLK</sub>.

#### NOTE

Exceeding the recommended maximum bus frequency or VCO frequency can crash the MCU.

- 11. Program the PLL registers accordingly:

- a. In the PRE bits of the PLL control register (PCTL), program the binary equivalent of P.

- b. In the VPR bits of the PLL control register (PCTL), program the binary equivalent of E.

- C. In the PLL multiplier select register low (PMSL) and the PLL multiplier select register high (PMSH), program the binary equivalent of N.

- d. In the PLL VCO range select register (PMRS), program the binary coded equivalent of L.

- e. In the PLL reference divider select register (PMDS), program the binary coded equivalent of R.

NOTE

The values for P, E, N, L, and R can only be programmed when the PLL is off (PLLON = 0).

Table 5-1 provides numeric examples (numbers are in hexadecimal notation):

| f <sub>BUS</sub> | f <sub>RCLK</sub> | R | Ν   | Р | Е | L  |

|------------------|-------------------|---|-----|---|---|----|

| 2.0 MHz          | 32.768 kHz        | 1 | F5  | 0 | 0 | D1 |

| 2.4576 MHz       | 32.768 kHz        | 1 | 12C | 0 | 1 | 80 |

| 2.5 MHz          | 32.768 kHz        | 1 | 132 | 0 | 1 | 83 |

| 4.0 MHz          | 32.768 kHz        | 1 | 1E9 | 0 | 1 | D1 |

| 4.9152 MHz       | 32.768 kHz        | 1 | 258 | 0 | 2 | 80 |

| 5.0 MHz          | 32.768 kHz        | 1 | 263 | 0 | 2 | 82 |

| 7.3728 MHz       | 32.768 kHz        | 1 | 384 | 0 | 2 | C0 |

| 8.0 MHz          | 32.768 kHz        | 1 | 3D1 | 0 | 2 | D0 |

#### Table 5-1. Numeric Example

Clock Generator Module (CGM)

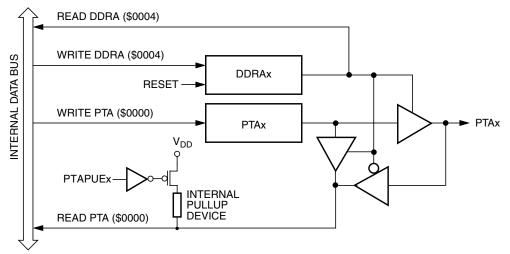

Figure 12-4 shows the port A I/O logic.

Figure 12-4. Port A I/O Circuit

When bit DDRAx is a logic 1, reading address \$0000 reads the PTAx data latch. When bit DDRAx is a logic 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 12-2 summarizes the operation of the port A pins.

| Table 12-2. Port A Pin Functions | rt A Pin Functions |

|----------------------------------|--------------------|

|----------------------------------|--------------------|

| PTAPUE Bit | DDRA Bit | PTA Bit          | I/O Pin Mode                          | Accesses to DDRA | Access    | es to PTA                |

|------------|----------|------------------|---------------------------------------|------------------|-----------|--------------------------|

| FTAFUE BIL |          |                  |                                       | Read/Write       | Read      | Write                    |

| 1          | 0        | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(4)</sup> | DDRA7-DDRA0      | Pin       | PTA7–PTA0 <sup>(3)</sup> |

| 0          | 0        | Х                | Input, Hi-Z <sup>(2)</sup>            | DDRA7-DDRA0      | Pin       | PTA7–PTA0 <sup>(3)</sup> |

| Х          | 1        | Х                | Output                                | DDRA7-DDRA0      | PTA7-PTA0 | PTA7-PTA0                |

NOTES:

1. X = Don't care

2. Hi-Z = High impedance

3. Writing affects data register, but does not affect input.

4. I/O pin pulled up to  $V_{DD}$  by internal pullup device

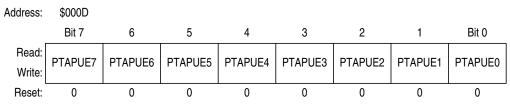

### 12.2.3 Port A Input Pullup Enable Register

The port A input pullup enable register (PTAPUE) contains a software configurable pullup device for each of the eight port A pins. Each bit is individually configurable and requires that the data direction register, DDRA, bit be configured as an input. Each pullup is automatically and dynamically disabled when a port bit's DDRA is configured for output mode.

Input/Output (I/O) Ports

#### PTAPUE7–PTAPUE0 — Port A Input Pullup Enable Bits

These writable bits are software programmable to enable pullup devices on an input port bit.

- 1 = Corresponding port A pin configured to have internal pullup

- 0 = Corresponding port A pin has internal pullup disconnected

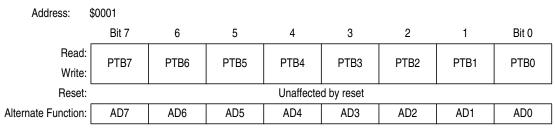

# 12.3 Port B

Port B is an 8-bit special-function port that shares all eight of its pins with the analog-to-digital converter (ADC) module.

### 12.3.1 Port B Data Register

The port B data register (PTB) contains a data latch for each of the eight port pins.

Figure 12-6. Port B Data Register (PTB)

#### PTB7-PTB0 — Port B Data Bits

These read/write bits are software-programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

#### AD7-AD0 — Analog-to-Digital Input Bits

AD7–AD0 are pins used for the input channels to the analog-to-digital converter module. The channel select bits in the ADC status and control register define which port B pin will be used as an ADC input and overrides any control from the port I/O logic by forcing that pin as the input to the analog circuitry.

#### NOTE

Care must be taken when reading port B while applying analog voltages to AD7–AD0 pins. If the appropriate ADC channel is not enabled, excessive current drain may occur if analog voltages are applied to the PTBx/ADx pin, while PTB is read as a digital input. Those ports not selected as analog input channels are considered digital I/O ports.

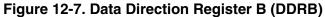

### 12.3.2 Data Direction Register B

Data direction register B (DDRB) determines whether each port B pin is an input or an output. Writing a logic 1 to a DDRB bit enables the output buffer for the corresponding port B pin; a logic 0 disables the output buffer.

| Address:        | \$0005 |       |       |       |       |       |       |       |

|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

|                 | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| Read:<br>Write: | DDRB7  | DDRB6 | DDRB5 | DDRB4 | DDRB3 | DDRB2 | DDRB1 | DDRB0 |

| Reset:          | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                 |        |       |       |       |       |       |       |       |

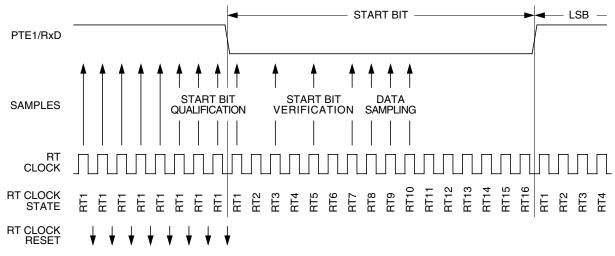

#### 13.4.3.3 Data Sampling

The receiver samples the PTE1/RxD pin at the RT clock rate. The RT clock is an internal signal with a frequency 16 times the baud rate. To adjust for baud rate mismatch, the RT clock is resynchronized at the following times (see Figure 13-6):

- After every start bit

- After the receiver detects a data bit change from logic 1 to logic 0 (after the majority of data bit samples at RT8, RT9, and RT10 returns a valid logic 1 and the majority of the next RT8, RT9, and RT10 samples returns a valid logic 0)

To locate the start bit, data recovery logic does an asynchronous search for a logic 0 preceded by three logic 1s. When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

Figure 13-6. Receiver Data Sampling

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7. Table 13-2 summarizes the results of the start bit verification samples.

| RT3, RT5, and RT7<br>Samples | Start Bit<br>Verification | Noise Flag |

|------------------------------|---------------------------|------------|

| 000                          | Yes                       | 0          |

| 001                          | Yes                       | 1          |

| 010                          | Yes                       | 1          |

| 011                          | No                        | 0          |

| 100                          | Yes                       | 1          |

| 101                          | No                        | 0          |

| 110                          | No                        | 0          |

| 111                          | No                        | 0          |

| Table <sup>-</sup> | 13-2. | Start | Bit | Verification |

|--------------------|-------|-------|-----|--------------|

|--------------------|-------|-------|-----|--------------|

Start bit verification is not successful if any two of the three verification samples are logic 1s. If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

### 15.12.4 SS (Slave Select)

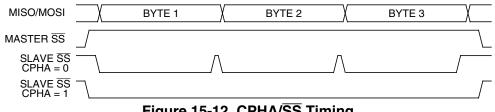

The SS pin has various functions depending on the current state of the SPI. For an SPI configured as a slave, the  $\overline{SS}$  is used to select a slave. For CPHA = 0, the  $\overline{SS}$  is used to define the start of a transmission. (See 15.5 Transmission Formats.) Since it is used to indicate the start of a transmission, the SS must be toggled high and low between each byte transmitted for the CPHA = 0 format. However, it can remain low between transmissions for the CPHA = 1 format. See Figure 15-12.

When an SPI is configured as a slave, the SS pin is always configured as an input. It cannot be used as a general-purpose I/O regardless of the state of the MODFEN control bit. However, the MODFEN bit can still prevent the state of the SS from creating a MODF error. (See 15.13.2 SPI Status and Control Register.)

#### NOTE

A logic 1 voltage on the  $\overline{SS}$  pin of a slave SPI puts the MISO pin in a high-impedance state. The slave SPI ignores all incoming SPSCK clocks, even if it was already in the middle of a transmission.

When an SPI is configured as a master, the SS input can be used in conjunction with the MODF flag to prevent multiple masters from driving MOSI and SPSCK. (See 15.7.2 Mode Fault Error.) For the state of the SS pin to set the MODF flag, the MODFEN bit in the SPSCK register must be set. If the MODFEN bit is low for an SPI master, the SS pin can be used as a general-purpose I/O under the control of the data direction register of the shared I/O port. With MODFEN high, it is an input-only pin to the SPI regardless of the state of the data direction register of the shared I/O port.

The CPU can always read the state of the  $\overline{SS}$  pin by configuring the appropriate pin as an input and reading the port data register. (See Table 15-3.)

| SPE | SPMSTR           | MODFEN | SPI Configuration   | Function of SS Pin                                  |

|-----|------------------|--------|---------------------|-----------------------------------------------------|

| 0   | X <sup>(1)</sup> | Х      | Not enabled         | General-purpose I/O; $\overline{SS}$ ignored by SPI |

| 1   | 0                | Х      | Slave               | Input-only to SPI                                   |

| 1   | 1                | 0      | Master without MODF | General-purpose I/O; SS ignored by SPI              |

| 1   | 1                | 1      | Master with MODF    | Input-only to SPI                                   |

Note 1. X = Don't care

#### 15.12.5 CGND (Clock Ground)

CGND is the ground return for the serial clock pin, SPSCK, and the ground for the port output buffers. It is internally connected to V<sub>SS</sub> as shown in Table 15-1.

#### TBR2:TBR0 — Timebase Rate Selection

These read/write bits are used to select the rate of timebase interrupts as shown in Table 16-1.

| TBR2 | TBR1 | TBR0 | Divider | Timebase Interrupt Rate |       |  |

|------|------|------|---------|-------------------------|-------|--|

| IDNZ | IDNI | IDRU | Dividei | Hz                      | ms    |  |

| 0    | 0    | 0    | 32768   | 1                       | 1000  |  |

| 0    | 0    | 1    | 8192    | 4                       | 250   |  |

| 0    | 1    | 0    | 2048    | 16                      | 62.5  |  |

| 0    | 1    | 1    | 128     | 256                     | ~ 3.9 |  |

| 1    | 0    | 0    | 64      | 512                     | ~2    |  |

| 1    | 0    | 1    | 32      | 1024                    | ~1    |  |

| 1    | 1    | 0    | 16      | 2048                    | ~0.5  |  |

| 1    | 1    | 1    | 8       | 4096                    | ~0.24 |  |

Table 16-1. Timebase Rate Selection for OSC1 = 32.768-kHz

#### NOTE

Do not change TBR2:TBR0 bits while the timebase is enabled (TBON = 1).

#### **TACK** — Timebase ACKnowledge

The TACK bit is a write-only bit and always reads as 0. Writing a logic 1 to this bit clears TBIF, the timebase interrupt flag bit. Writing a logic 0 to this bit has no effect.

1 = Clear timebase interrupt flag

0 = No effect

#### **TBIE** — Timebase Interrupt Enabled

This read/write bit enables the timebase interrupt when the TBIF bit becomes set. Reset clears the TBIE bit.

1 = Timebase interrupt enabled

0 = Timebase interrupt disabled

#### **TBON** — Timebase Enabled

This read/write bit enables the timebase. Timebase may be turned off to reduce power consumption when its function is not necessary. The counter can be initialized by clearing and then setting this bit. Reset clears the TBON bit.

1 = Timebase enabled

0 = Timebase disabled and the counter initialized to 0s

### 16.5 Interrupts

The timebase module can interrupt the CPU on a regular basis with a rate defined by TBR2:TBR0. When the timebase counter chain rolls over, the TBIF flag is set. If the TBIE bit is set, enabling the timebase interrupt, the counter chain overflow will generate a CPU interrupt request.

Interrupts must be acknowledged by writing a logic 1 to the TACK bit.

#### **Functional Description**

| Addr.               | Register Name                                            |                 | Bit 7                     | 6     | 5     | 4           | 3              | 2           | 1           | Bit 0    |  |

|---------------------|----------------------------------------------------------|-----------------|---------------------------|-------|-------|-------------|----------------|-------------|-------------|----------|--|

|                     | Timer 1 Status and Control                               | Read:           | TOF                       | тог   | TSTOP | 0           | 0              | PS2         | DO1         | DCO      |  |

| \$0020              | Register                                                 | Write:          | 0                         | TOIE  | 13105 | TRST        |                | F32         | PS1         | PS0      |  |

|                     | (T1SC)                                                   | Reset:          | 0                         | 0     | 1     | 0           | 0              | 0           | 0           | 0        |  |

|                     | Timer 1 Counter                                          | Read:           | Bit 15                    | 14    | 13    | 12          | 11             | 10          | 9           | Bit 8    |  |

| \$0021 Regist       | Register High                                            | Write:          |                           |       |       |             |                |             |             |          |  |

|                     | (T1CNTH)                                                 | Reset:          | 0                         | 0     | 0     | 0           | 0              | 0           | 0           | 0        |  |

|                     | Timer 1 Counter                                          | Read:           | Bit 7                     | 6     | 5     | 4           | 3              | 2           | 1           | Bit 0    |  |

| \$0022              | \$0022 Register Low                                      | Write:          |                           |       |       |             |                |             |             |          |  |

|                     | (T1CNTL)                                                 | Reset:          | 0                         | 0     | 0     | 0           | 0              | 0           | 0           | 0        |  |

|                     | Timer 1 Counter Modulo                                   | Read:           | Bit 15                    | 14    | 13    | 12          | 11             | 10          | 9           | Bit 8    |  |

| \$0023              | Register High                                            | Write:          | 2                         |       |       |             |                | 10          | Ĵ           | Dir o    |  |

|                     | (T1MODH)                                                 | Reset:          | 1                         | 1     | 1     | 1           | 1              | 1           | 1           | 1        |  |

| \$0024              | Timer 1 Counter Modulo<br>Register Low                   | Read:<br>Write: | Bit 7                     | 6     | 5     | 4           | 3              | 2           | 1           | Bit 0    |  |

| (T1                 | (T1MODL)                                                 | Reset:          | 1                         | 1     | 1     | 1           | 1              | 1           | 1           | 1        |  |

|                     | Timer 1 Channel 0 Status and<br>Control Register (T1SC0) | Read:           | CH0F                      | CHOIE | MS0B  | MS0A        | ELS0B          | ELS0A       | TOV0        | CHOMAX   |  |

| \$0025 <sup>I</sup> |                                                          | Write:          | 0                         |       | NIS0D | MOUA        | ELSOD          | ELSUA       | 1000        | CITOWAX  |  |

|                     |                                                          | Reset:          | 0                         | 0     | 0     | 0           | 0              | 0           | 0           | 0        |  |

| \$0026              | Timer 1 Channel 0<br>Register High                       | Read:<br>Write: | Bit 15                    | 14    | 13    | 12          | 11             | 10          | 9           | Bit 8    |  |

|                     | (T1CH0H)                                                 | Reset:          | Indeterminate after reset |       |       |             |                |             |             |          |  |

| \$0027              | Timer 1 Channel 0<br>Register Low                        | Read:<br>Write: | Bit 7                     | 6     | 5     | 4           | 3              | 2           | 1           | Bit 0    |  |

|                     | (T1CH0L)                                                 | Reset:          | Indeterminate after reset |       |       |             |                |             |             | 1]       |  |

|                     |                                                          | Read:           | CH1F                      |       | 0     | 14044       |                |             | TO)/4       | OLIMAAY  |  |

| \$0028              | Timer 1 Channel 1 Status and<br>Control Register (T1SC1) | Write:          | 0                         | CH1IE |       | MS1A        | ELS1B          | ELS1A       | TOV1        | CH1MAX   |  |

|                     |                                                          | Reset:          | 0                         | 0     | 0     | 0           | 0              | 0           | 0           | 0        |  |

| \$0029              | Timer 1 Channel 1<br>Register High                       | Read:<br>Write: | Bit 15                    | 14    | 13    | 12          | 11             | 10          | 9           | Bit 8    |  |

| φ00 <u></u> 20      | (T1CH1H)                                                 | Reset:          |                           |       |       | Indetermina | te after reset |             |             |          |  |

|                     | Timer 1 Channel 1                                        | Read:           |                           |       |       |             |                |             |             |          |  |

| \$002A              | Register Low                                             | Write:          | Bit 7                     | 6     | 5     | 4           | 3              | 2           | 1           | Bit 0    |  |

|                     | (T1CH1L)                                                 | Reset:          |                           | 1     | 1     | Indetermina | te after reset |             | 1           | <u> </u> |  |

|                     | Timer 2 Status and Control                               | Read:           | TOF                       | TOIT  |       | 0           | 0              | <b>D</b> 00 | <b>D</b> 24 | DOG      |  |

| \$002B              | Register                                                 | Write:          | 0                         | TOIE  | TSTOP | TRST        |                | PS2         | PS1         | PS0      |  |

|                     | (T2SC)                                                   | Reset:          | 0                         | 0     | 1     | 0           | 0              | 0           | 0           | 0        |  |

|                     | = Unimplemented                                          |                 |                           |       |       |             |                |             |             |          |  |

Figure 17-2. TIM I/O Register Summary (Sheet 1 of 2)

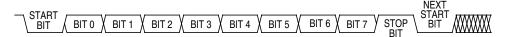

#### 18.3.1.4 Data Format

Communication with the monitor ROM is in standard non-return-to-zero (NRZ) mark/space data format. Transmit and receive baud rates must be identical.

Figure 18-12. Monitor Data Format

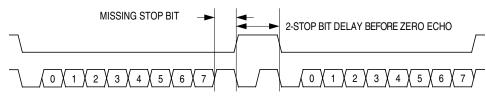

#### 18.3.1.5 Break Signal

A start bit (0) followed by nine 0 bits is a break signal. When the monitor receives a break signal, it drives the PTA0 pin high for the duration of two bits and then echoes back the break signal.

Figure 18-13. Break Transaction

#### 18.3.1.6 Baud Rate

The communication baud rate is controlled by the external clock and the state of the PTC3 pin (when  $\overline{IRQ}$  is set to  $V_{TST}$ ) upon entry into monitor mode. If monitor mode was entered with a blank reset vector and  $V_{DD}$  or  $V_{SS}$  on  $\overline{IRQ}$ , then the baud rate is independent of PTC3.

Table 18-1 lists external frequencies required to achieve a standard baud rate of 9600 bps. The effective baud rate is the bus frequency divided by 256.

#### 18.3.1.7 Commands

The monitor ROM firmware uses these commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

The monitor ROM firmware echoes each received byte back to the PTA0 pin for error checking. An 11-bit delay at the end of each command allows the host to send a break character to cancel the command. A delay of two bit times occurs before each echo and before READ, IREAD, or READSP data is returned. The data returned by a read command appears after the echo of the last byte of the command.

#### NOTE

Wait one bit time after each echo before sending the next byte.

# 19.7 5.0-V Control Timing

| Characteristic <sup>(1)</sup>                                                    | Symbol                              | Min      | Мах         | Unit             |

|----------------------------------------------------------------------------------|-------------------------------------|----------|-------------|------------------|

| Frequency of operation<br>Crystal option<br>External clock option <sup>(2)</sup> | f <sub>OSC</sub>                    | 32<br>dc | 100<br>32.8 | kHz<br>MHz       |

| Internal operating frequency                                                     | f <sub>OP</sub> (f <sub>BUS</sub> ) | _        | 8.2         | MHz              |

| Internal clock period (1/f <sub>OP</sub> )                                       | t <sub>CYC</sub>                    | 122      | —           | ns               |

| RST input pulse width low                                                        | t <sub>IRL</sub>                    | 100      | —           | ns               |

| IRQ interrupt pulse width low (edge-triggered)                                   | t <sub>ILIH</sub>                   | 100      | _           | ns               |

| IRQ interrupt pulse period                                                       | t <sub>ILIL</sub>                   | (3)      | —           | t <sub>CYC</sub> |

Notes:

1.  $V_{SS} = 0$  Vdc; timing shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD}$  unless otherwise noted. 2. No more than 10% duty cycle deviation from 50% 3. The minimum period,  $t_{ILIL}$  or  $t_{TLTL}$ , should not be less than the number of cycles it takes to execute the interrupt service routine plus t<sub>CYC</sub>.

**Electrical Specifications**

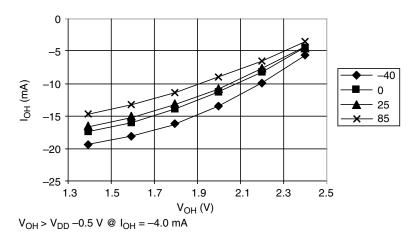

Figure 19-5. Typical High-Side Driver Characteristics – Port PTC4–PTC0 (V<sub>DD</sub> = 2.7 Vdc)

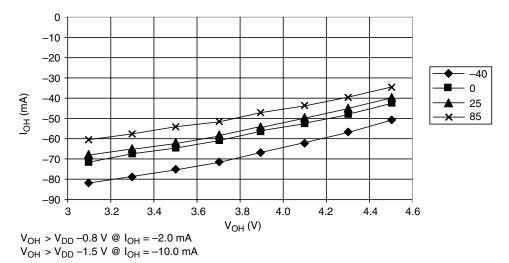

Figure 19-6. Typical High-Side Driver Characteristics – Ports PTB7–PTB0, PTC6–PTC5, PTD7–PTD0, and PTE1–PTE0 (V<sub>DD</sub> = 5.5 Vdc)

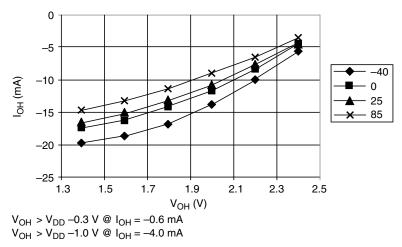

Figure 19-7. Typical High-Side Driver Characteristics – Ports PTB7–PTB0, PTC6–PTC5, PTD7–PTD0, and PTE1–PTE0 (V<sub>DD</sub> = 2.7 Vdc)

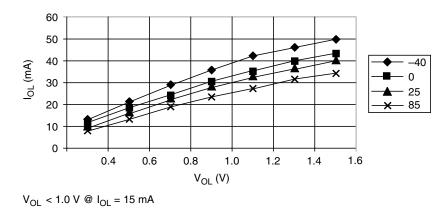

### **19.10 Output Low-Voltage Characteristics**

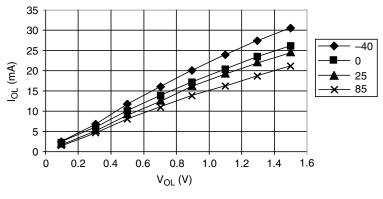

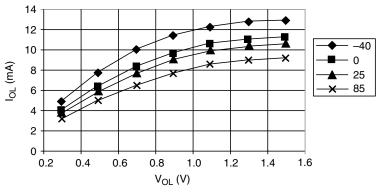

$V_{OL} < 0.4$  V @  $I_{OL} = 1.6$  mA  $V_{OL} < 1.5$  V @  $I_{OL} = 10.0$  mA

Figure 19-8. Typical Low-Side Driver Characteristics – Port PTA7–PTA0 (V<sub>DD</sub> = 5.5 Vdc)

Figure 19-9. Typical Low-Side Driver Characteristics – Port PTA7–PTA0 (V<sub>DD</sub> = 2.7 Vdc)

Figure 19-10. Typical Low-Side Driver Characteristics – Port PTC4–PTC0 (V<sub>DD</sub> = 4.5 Vdc)

**Electrical Specifications**

# **19.12 ADC Characteristics**

| Characteristic <sup>(1)</sup>                                                       | Symbol            | Min                          | Max                          | Unit                    | Comments                                                                                             |

|-------------------------------------------------------------------------------------|-------------------|------------------------------|------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|

| Supply voltage                                                                      | V <sub>DDAD</sub> | 2.7<br>(V <sub>DD</sub> min) | 5.5<br>(V <sub>DD</sub> max) | v                       | V <sub>DDAD</sub> should be tied to<br>the same potential as V <sub>DD</sub><br>via separate traces. |

| Input voltages                                                                      | V <sub>ADIN</sub> | 0                            | V <sub>DDAD</sub>            | V                       | V <sub>ADIN</sub> ≤ V <sub>REFH</sub>                                                                |

| Resolution                                                                          | B <sub>AD</sub>   | 8                            | 8                            | Bits                    |                                                                                                      |

| Absolute accuracy<br>( $V_{REFL} = 0 V$ ,<br>$V_{REFH} = V_{DDAD} = 5 V \pm 10\%$ ) | A <sub>AD</sub>   | _                            | ± 1                          | LSB                     | Includes quantization                                                                                |

| ADC internal clock                                                                  | f <sub>ADIC</sub> | 0.5                          | 1.048                        | MHz                     | t <sub>AIC</sub> = 1/f <sub>ADIC</sub> , tested only<br>at 1 MHz                                     |

| Conversion range                                                                    | R <sub>AD</sub>   | V <sub>REFL</sub>            | V <sub>REFH</sub>            | V                       | $V_{REFH} = V_{DDAD}$<br>$V_{REFL} = V_{SSAD}$                                                       |

| Power-up time                                                                       | t <sub>ADPU</sub> | 16                           |                              | t <sub>AIC</sub> cycles |                                                                                                      |

| Conversion time                                                                     | t <sub>ADC</sub>  | 16                           | 17                           | t <sub>AIC</sub> cycles |                                                                                                      |

| Sample time <sup>(2)</sup>                                                          | t <sub>ADS</sub>  | 5                            | _                            | t <sub>AIC</sub> cycles |                                                                                                      |

| Zero input reading <sup>(3)</sup>                                                   | Z <sub>ADI</sub>  | 00                           | 01                           | Hex                     | V <sub>IN</sub> = V <sub>REFL</sub>                                                                  |

| Full-scale reading <sup>(3)</sup>                                                   | F <sub>ADI</sub>  | FE                           | FF                           | Hex                     | V <sub>IN</sub> = V <sub>REFH</sub>                                                                  |

| Input capacitance                                                                   | C <sub>ADI</sub>  |                              | (20) 8                       | pF                      | Not tested                                                                                           |

| Input leakage <sup>(4)</sup><br>Port B                                              | _                 | —                            | ± 1                          | μΑ                      |                                                                                                      |

| Notes:                                                                              | •                 |                              | •                            | •                       | •                                                                                                    |

1.  $V_{DD} = 5.0 \text{ Vdc} \pm 10\%$ ,  $V_{SS} = 0 \text{ Vdc}$ ,  $V_{DDAD} = 5.0 \text{ Vdc} \pm 10\%$ ,  $V_{SSAD} = 0 \text{ Vdc}$ ,  $V_{REFH} = 5.0 \text{ Vdc} \pm 10\%$ ,  $V_{REFL} = 0$ 2. Source impedances greater than 10 k $\Omega$  adversely affect internal RC charging time during input sampling. 3. Zero-input/full-scale reading requires sufficient decoupling measures for accurate conversions.

4. The external system error caused by input leakage current is approximately equal to the product of R source and input current.

**Electrical Specifications**

# **19.16 Clock Generation Module Characteristics**

### 19.16.1 CGM Component Specifications

| Characteristic                            | Symbol            | Min | Тур    | Max | Unit |

|-------------------------------------------|-------------------|-----|--------|-----|------|

| Crystal reference frequency               | <sup>f</sup> XCLK | 30  | 32.768 | 100 | kHz  |

| Crystal load capacitance <sup>(1)</sup>   | CL                | _   | 12.5   | —   | pF   |

| Crystal fixed capacitance <sup>(2)</sup>  | C <sub>1</sub>    | _   | 15     | —   | pF   |

| Crystal tuning capacitance <sup>(2)</sup> | C <sub>2</sub>    | —   | 15     | —   | pF   |

| Feedback bias resistor                    | R <sub>B</sub>    | 1   | 10     | 22  | MΩ   |

| Series resistor <sup>(3)</sup>            | R <sub>S</sub>    | 100 | 330    | 470 | kΩ   |

Notes:

1. Crystal manufacturer value.

Capacitor on OSC1 pin. Does not include parasitic capacitance due to package, pin, and board.

Capacitor on OSC2 pin. Does not include parasitic capacitance due to package, pin, and board.

**Ordering Information**