Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                     |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 25MHz                                                                       |

| Connectivity               | SCI, SmartCard                                                              |

| Peripherals                | DMA, PWM, WDT                                                               |

| Number of I/O              | 70                                                                          |

| Program Memory Size        | 384KB (384K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 16K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                   |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-BFQFP                                                                   |

| Supplier Device Package    | 100-QFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df3028f25v |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                                                                                        | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21.1.4 A/D Conversion                                                                       | 658  | Conditions amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Characteristics<br>Table 21.8 A/D<br>Conversion<br>Characteristics                          |      | Conditions: $V_{CC} = 3.0 V$ to $3.6 V$ , $AV_{CC} = 3.0 V$ to $3.6 V$ , $V_{REF} = 3.0 V$ to<br>$AV_{CC}$ , $V_{SS} = AV_{SS} = 0 V$ , $T_a = -20^{\circ}C$ to $+75^{\circ}C$ (regular<br>specifications), $T_a = -40^{\circ}C$ to $+85^{\circ}C$ (wide-range<br>specifications)<br>Table amended                                                                                                                                                                                                                                                                      |

|                                                                                             |      | Permissible signal- $\phi \le 13 \text{ MHz} 5 \text{ k}\Omega$ source impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 21.1.5 D/A Conversion<br>Characterisitcs<br>Table 21.9 D/A<br>Conversion<br>Characteristics | 659  | Conditions amended<br>Conditions: $V_{CC} = 3.0 \text{ V}$ to $3.6 \text{ V}$ , $AV_{CC} = 3.0 \text{ V}$ to $3.6 \text{ V}$ , $V_{REF} = 3.0 \text{ V}$ to<br>$AV_{CC}$ , $V_{SS} = AV_{SS} = 0 \text{ V}$ , $T_a = -20^{\circ}\text{C}$ to $+75^{\circ}\text{C}$ (regular<br>specifications), $T_a = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ (wide-range<br>specifications)                                                                                                                                                                                     |

| 21.2.1 Absolute<br>Maximum Ratings<br>Table 21.10 Absolute                                  | 660  | Table and note amended         Operating temperature       T <sub>opr</sub> -20 to +75*2       °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Maximum Ratings                                                                             |      | Wide-range specifications: °C<br>-40 to +85 <sup>*2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                             |      | 2. The operating temperature range when programming and erasing the flash memory is: $T_a = 0$ to +75°C (regular specifications), $T_a = 0$ to +85°C (wide-range specifications).                                                                                                                                                                                                                                                                                                                                                                                       |

| 21.2.2 DC                                                                                   | 661, | Conditions amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Characteristics<br>Table 21.11 DC<br>Characteristics                                        | 662  | Conditions: $V_{CC} = 3.0 \text{ V}$ to $3.6 \text{ V}$ , $AV_{CC}^{*1} = 3.0 \text{ V}$ to $3.6 \text{ V}$ , $V_{REF}^{*1} = 3.0 \text{ V}$<br>to $AV_{CC}$ , $V_{SS} = AV_{SS}^{*1} = 0 \text{ V}$ , $T_a = -20^{\circ}\text{C}$ to $+75^{\circ}\text{C}$ (regular specifications), $T_a = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ (wide-range specifications)<br>[Programming/erasing conditions: $T_a = 0^{\circ}\text{C}$ to $+75^{\circ}\text{C}$ (regular specifications), $T_a = 0^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ (wide-range specifications)] |

|                                                                                             |      | Table amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                             |      | Input FWE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                             |      | capacitance NMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                             |      | All input pins<br>except NMI,<br>and FWE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 7.1.3    | Functional Overview                                       |     |

|------|----------|-----------------------------------------------------------|-----|

|      | 7.1.4    | Input/Output Pins                                         | 192 |

|      | 7.1.5    | Register Configuration                                    | 192 |

| 7.2  | Registe  | r Descriptions (1) (Short Address Mode)                   | 194 |

|      | 7.2.1    | Memory Address Registers (MAR)                            | 194 |

|      | 7.2.2    | I/O Address Registers (IOAR)                              | 195 |

|      | 7.2.3    | Execute Transfer Count Registers (ETCR)                   | 195 |

|      | 7.2.4    | Data Transfer Control Registers (DTCR)                    | 197 |

| 7.3  | Registe  | er Descriptions (2) (Full Address Mode)                   | 200 |

|      | 7.3.1    | Memory Address Registers (MAR)                            | 200 |

|      | 7.3.2    | I/O Address Registers (IOAR)                              | 200 |

|      | 7.3.3    | Execute Transfer Count Registers (ETCR)                   | 201 |

|      | 7.3.4    | Data Transfer Control Registers (DTCR)                    | 203 |

| 7.4  | Operati  | on                                                        | 209 |

|      | 7.4.1    | Overview                                                  | 209 |

|      | 7.4.2    | I/O Mode                                                  | 211 |

|      | 7.4.3    | Idle Mode                                                 | 213 |

|      | 7.4.4    | Repeat Mode                                               | 216 |

|      | 7.4.5    | Normal Mode                                               | 219 |

|      | 7.4.6    | Block Transfer Mode                                       | 222 |

|      | 7.4.7    | DMAC Activation                                           | 227 |

|      | 7.4.8    | DMAC Bus Cycle                                            | 229 |

|      | 7.4.9    | Multiple-Channel Operation                                | 235 |

|      | 7.4.10   | External Bus Requests, DRAM Interface, and DMAC           | 236 |

|      | 7.4.11   | NMI Interrupts and DMAC                                   | 237 |

|      | 7.4.12   | Aborting a DMAC Transfer                                  | 238 |

|      | 7.4.13   | Exiting Full Address Mode                                 | 239 |

|      | 7.4.14   | DMAC States in Reset State, Standby Modes, and Sleep Mode | 240 |

| 7.5  | Interrup | ots                                                       | 241 |

| 7.6  | Usage 1  | Notes                                                     | 242 |

|      | 7.6.1    | Note on Word Data Transfer                                | 242 |

|      | 7.6.2    | DMAC Self-Access                                          | 242 |

|      | 7.6.3    | Longword Access to Memory Address Registers               | 242 |

|      | 7.6.4    | Note on Full Address Mode Setup                           | 242 |

|      | 7.6.5    | Note on Activating DMAC by Internal Interrupts            | 243 |

|      | 7.6.6    | NMI Interrupts and Block Transfer Mode                    | 244 |

|      | 7.6.7    | Memory and I/O Address Register Values                    | 244 |

|      | 7.6.8    | Bus Cycle when Transfer is Aborted                        | 245 |

|      | 7.6.9    | Transfer Requests by A/D Converter                        | 245 |

| Sect | ion 8    | I/O Ports                                                 | 247 |

| 8.1  |          | ew                                                        |     |

| 8.2  |          |                                                           |     |

| 0.2  | 10111.   |                                                           | 200 |

### Renesas

Rev. 2.00, 09/03, page xxi of xxx

| Pin No.             | Pin Name                                              |                                                       |                                                       |                                                       |                                                       |                                                       |                                                     |

|---------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|

| FP-100B<br>TFP-100B | Mode 1                                                | Mode 2                                                | Mode 3                                                | Mode 4                                                | Mode 5                                                | Mode 6                                                | Mode 7                                              |

| 55                  | A <sub>18</sub>                                       | A <sub>18</sub>                                       | A <sub>18</sub>                                       | A <sub>18</sub>                                       | P5 <sub>2</sub> /A <sub>18</sub>                      | P52                                                   | P5 <sub>2</sub>                                     |

| 56                  | A <sub>19</sub>                                       | A <sub>19</sub>                                       | A <sub>19</sub>                                       | A <sub>19</sub>                                       | P5 <sub>3</sub> /A <sub>19</sub>                      | P5₃                                                   | P5₃                                                 |

| 57                  | V <sub>SS</sub>                                       | $V_{\text{SS}}$                                     |

| 58                  | P6 <sub>0</sub> /WAIT                                 | P60                                                   | P6 <sub>0</sub>                                     |

| 59                  | P6 <sub>1</sub> /BREQ                                 | P61                                                   | P61                                                 |

| 60                  | P6 <sub>2</sub> /BACK                                 | P62                                                   | P6 <sub>2</sub>                                     |

| 61                  | φ                                                     | φ                                                     | φ                                                     | φ                                                     | P6 <sub>7</sub> /φ                                    | P6 <sub>7</sub> /φ                                    | P67/\$                                              |

| 62                  | STBY                                                  | STBY                                                  | STBY                                                  | STBY                                                  | STBY                                                  | STBY                                                  | STBY                                                |

| 63                  | RES                                                   | RES                                                   | RES                                                   | RES                                                   | RES                                                   | RES                                                   | RES                                                 |

| 64                  | NMI                                                   | NMI                                                   | NMI                                                   | NMI                                                   | NMI                                                   | NMI                                                   | NMI                                                 |

| 65                  | V <sub>SS</sub>                                       | $V_{\text{SS}}$                                     |

| 66                  | EXTAL                                                 | EXTAL                                                 | EXTAL                                                 | EXTAL                                                 | EXTAL                                                 | EXTAL                                                 | EXTAL                                               |

| 67                  | XTAL                                                  | XTAL                                                  | XTAL                                                  | XTAL                                                  | XTAL                                                  | XTAL                                                  | XTAL                                                |

| 68                  | V <sub>cc</sub>                                       | $V_{\text{CC}}$                                     |

| 69                  | AS                                                    | AS                                                    | ĀS                                                    | ĀS                                                    | AS                                                    | P63                                                   | P6 <sub>3</sub>                                     |

| 70                  | RD                                                    | RD                                                    | RD                                                    | RD                                                    | RD                                                    | P64                                                   | P64                                                 |

| 71                  | HWR                                                   | HWR                                                   | HWR                                                   | HWR                                                   | HWR                                                   | P6₅                                                   | P6₅                                                 |

| 72                  | LWR                                                   | LWR                                                   | LWR                                                   | LWR                                                   | LWR                                                   | P6 <sub>6</sub>                                       | P6 <sub>6</sub>                                     |

| 73                  | MD <sub>0</sub>                                       | $MD_0$                                              |

| 74                  | $MD_1$                                                | MD <sub>1</sub>                                       | $MD_1$                                              |

| 75                  | $MD_2$                                                | MD <sub>2</sub>                                       | MD <sub>2</sub>                                       | MD <sub>2</sub>                                       | $MD_2$                                                | $MD_2$                                                | $MD_2$                                              |

| 76                  | AV <sub>CC</sub>                                      | $AV_{CC}$                                             | $AV_{CC}$                                           |

| 77                  | $V_{REF}$                                             | $V_{REF}$                                             | $V_{REF}$                                             | V <sub>REF</sub>                                      | $V_{REF}$                                             | $V_{REF}$                                             | $V_{REF}$                                           |

| 78                  | P7 <sub>0</sub> /AN <sub>0</sub>                      | P7 <sub>0</sub> /AN <sub>0</sub>                    |

| 79                  | P7 <sub>1</sub> /AN <sub>1</sub>                      | P7 <sub>1</sub> /AN <sub>1</sub>                    |

| 80                  | P7 <sub>2</sub> /AN <sub>2</sub>                      | P7 <sub>2</sub> /AN <sub>2</sub>                    |

| 81                  | P7 <sub>3</sub> /AN <sub>3</sub>                      | P7 <sub>3</sub> /AN <sub>3</sub>                    |

| 82                  | P7 <sub>4</sub> /AN <sub>4</sub>                      | P7₄/AN₄                                             |

| 83                  | P75/AN5                                               | P7 <sub>5</sub> /AN <sub>5</sub>                      | P7 <sub>5</sub> /AN <sub>5</sub>                      | P7 <sub>5</sub> /AN <sub>5</sub>                      | P75/AN5                                               | P75/AN5                                               | P7₅/AN                                              |

| 84                  | P7 <sub>6</sub> /AN <sub>6</sub> /<br>DA <sub>0</sub> | P7₀/AN₀<br>DA₀                                      |

| 85                  | P7 <sub>7</sub> /AN <sub>7</sub> /<br>DA <sub>1</sub> | P7 <sub>7</sub> /AN <sub>7</sub><br>DA <sub>1</sub> |

| 86                  | AV <sub>ss</sub>                                      | AV <sub>SS</sub>                                    |

| 87                  | P8₀/ĪRQ₀/<br>RFSH                                     | P8₀/ĪRQ₀/<br>RFSH                                     | P8 <sub>0</sub> /IRQ <sub>0</sub> /<br>RFSH           | P8 <sub>0</sub> /IRQ <sub>0</sub> /<br>RFSH           | P8₀/IRQ₀/<br>RFSH                                     | P8 <sub>0</sub> /IRQ <sub>0</sub>                     | P8 <sub>0</sub> /IRQ                                |

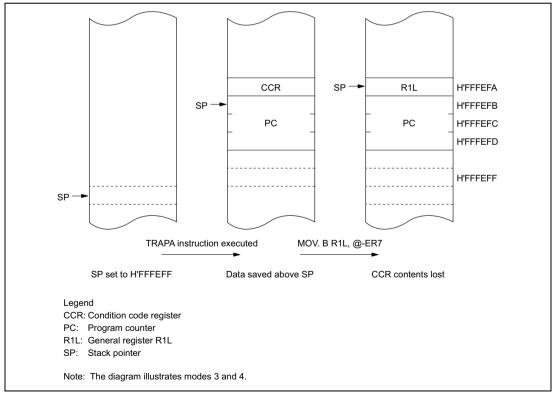

# 4.4 Trap Instruction

Trap instruction exception handling starts when a TRAPA instruction is executed. If the UE bit is set to 1 in the system control register (SYSCR), the exception handling sequence sets the I bit to 1 in CCR. If the UE bit is 0, the I and UI bits are both set to 1. The TRAPA instruction fetches a start address from a vector table entry corresponding to a vector number from 0 to 3, which is specified in the instruction code.

### 4.6 Notes on Stack Usage

When accessing word data or longword data, the H8/3028 Group regards the lowest address bit as 0. The stack should always be accessed by word access or longword access, and the value of the stack pointer (SP, ER7) should always be kept even.

Use the following instructions to save registers:

PUSH.W Rn (or MOV.W Rn, @–SP) PUSH.L ERn (or MOV.L ERn, @–SP)

Use the following instructions to restore registers:

| POP.W Rn  | (or MOV.W @SP+, Rn)  |

|-----------|----------------------|

| POP.L ERn | (or MOV.L @SP+, ERn) |

Setting SP to an odd value may lead to a malfunction. Figure 4.7 shows an example of what happens when the SP value is odd.

Figure 4.7 Operation when SP Value is Odd

Rev. 2.00, 09/03, page 79 of 890

| Bit 7<br>MXC1 | Bit 6<br>MXC0 | Description             |                     |                                    |

|---------------|---------------|-------------------------|---------------------|------------------------------------|

| 0             | 0             | Column address: 8 bits  |                     |                                    |

|               |               | Compared address:       |                     |                                    |

|               |               | Modes 1, 2              | 8-bit access space  | A <sub>19</sub> to A <sub>8</sub>  |

|               |               |                         | 16-bit access space | A <sub>19</sub> to A <sub>9</sub>  |

|               |               | Modes 3, 4, 5           | 8-bit access space  | A <sub>23</sub> to A <sub>8</sub>  |

|               |               |                         | 16-bit access space | A <sub>23</sub> to A <sub>9</sub>  |

|               | 1             | Column address: 9 bits  |                     |                                    |

|               |               | Compared address:       |                     |                                    |

|               |               | Modes 1, 2              | 8-bit access space  | $A_{19}$ to $A_9$                  |

|               |               |                         | 16-bit access space | A <sub>19</sub> to A <sub>10</sub> |

|               |               | Modes 3, 4, 5           | 8-bit access space  | A <sub>23</sub> to A <sub>9</sub>  |

|               |               |                         | 16-bit access space | A <sub>23</sub> to A <sub>10</sub> |

| 1             | 0             | Column address: 10 bits |                     |                                    |

|               |               | Compared address:       |                     |                                    |

|               |               | Modes 1, 2              | 8-bit access space  | A <sub>19</sub> to A <sub>10</sub> |

|               |               |                         | 16-bit access space | A <sub>19</sub> to A <sub>11</sub> |

|               |               | Modes 3, 4, 5           | 8-bit access space  | A <sub>23</sub> to A <sub>10</sub> |

|               |               |                         | 16-bit access space | A <sub>23</sub> to A <sub>11</sub> |

|               | 1             | Illegal setting         |                     |                                    |

Bit 5— $\overline{CAS}$  Output Pin Select (CSEL): Selects the  $\overline{UCAS}$  and  $\overline{LCAS}$  output pins when areas 2 to 5 are designated as DRAM space.

| Bit 5<br>CSEL | Description                                                                                                                       |                 |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0             | PB4 and PB5 selected as $\overline{\text{UCAS}}$ and $\overline{\text{LCAS}}$ output pins                                         | (Initial value) |

| 1             | $\overline{\text{HWR}}$ and $\overline{\text{LWR}}$ selected as $\overline{\text{UCAS}}$ and $\overline{\text{LCAS}}$ output pins |                 |

**Bit 4—Refresh Cycle Enable (RCYCE):** Enables or disables CAS-before-RAS refresh cycle insertion. When none of areas 2 to 5 has been designated as DRAM space, refresh cycles are not inserted regardless of the setting of this bit.

| Bit 4<br>RCYCE | Description                 |                 |

|----------------|-----------------------------|-----------------|

| 0              | Refresh cycles disabled     | (Initial value) |

| 1              | DRAM refresh cycles enabled |                 |

Rev. 2.00, 09/03, page 125 of 890

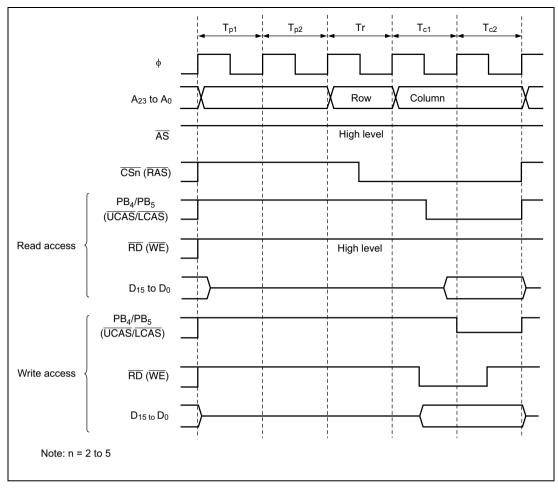

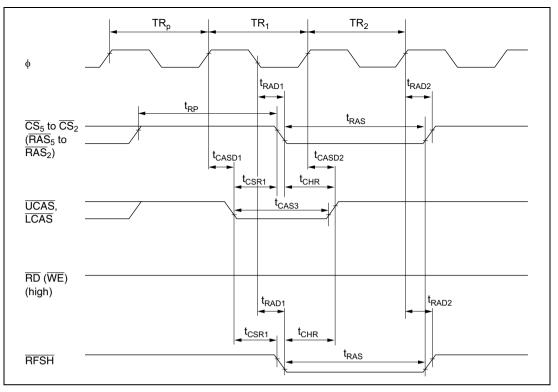

Figure 6.19 Timing with Two Precharge States (CSEL = 0 in DRCRB)

### 6.5.8 Wait Control

In a DRAM access cycle, wait states can be inserted (1) between the  $T_r$  state and  $T_{c1}$  state, and (2) between the  $T_{c1}$  state and  $T_{c2}$  state.

**Insertion of T**<sub>rw</sub> **Wait State between T**<sub>r</sub> and T<sub>c1</sub>: One T<sub>rw</sub> state can be inserted between T<sub>r</sub> and T<sub>c1</sub> by setting the RCW bit to 1 in DRCRB.

**Insertion of**  $T_w$  **Wait State(s) between**  $T_{c1}$  **and**  $T_{c2}$ **:** When the bit in ASTCR corresponding to an area designated as DRAM space is set to 1, from 0 to 3 wait states can be inserted between the  $T_{c1}$  state and  $T_{c2}$  state by means of settings in WCRH and WCRL.

Figure 6.20 shows an example of the timing for wait state insertion.

Rev. 2.00, 09/03, page 155 of 890

#### Table 8.20Port A Pin Functions (Modes 3, 4, and 5)

| Pin                                  | Pin Functions and Selection Method                    |                        |

|--------------------------------------|-------------------------------------------------------|------------------------|

| PA <sub>7</sub> /TP <sub>7</sub> /   | Modes 3 and 4: Always used as A <sub>20</sub> output. |                        |

| TIOCB <sub>2</sub> / A <sub>20</sub> | Pin function                                          | A <sub>20</sub> output |

#### Mode 5:

Bit PWM2 in TMDR, bits IOB2 to IOB0 in TIOR2, bit NDER7 in NDERA, bit A20E in BRCR, and bit PA<sub>7</sub>DDR select the pin function as follows.

| A20E                            | 1                         |                          |                           | 0                         |                           |

|---------------------------------|---------------------------|--------------------------|---------------------------|---------------------------|---------------------------|

| 16-bit timer channel 2 settings | (1) in table below        | (2)                      | in table be               | low                       | _                         |

| PA7DDR                          | —                         | 0                        | 1                         | 1                         | —                         |

| NDER7                           | —                         | _                        | 0                         | 1                         | —                         |

| Pin function                    | TIOCB <sub>2</sub> output | PA <sub>7</sub><br>input | PA <sub>7</sub><br>output | TP <sub>7</sub><br>output | A <sub>20</sub><br>output |

|                                 |                           | TI                       | OCB <sub>2</sub> inpu     | ıt*                       |                           |

Note: \* TIOCB<sub>2</sub> input when IOB2 = 1 and PWM2 = 0.

| 16-bit timer<br>channel 2 settings | (2) | (* | 1) | (2) |

|------------------------------------|-----|----|----|-----|

| IOB2                               |     | 0  |    | 1   |

| IOB1                               | 0   | 0  | 1  | —   |

| IOB0                               | 0   | 1  | _  | _   |

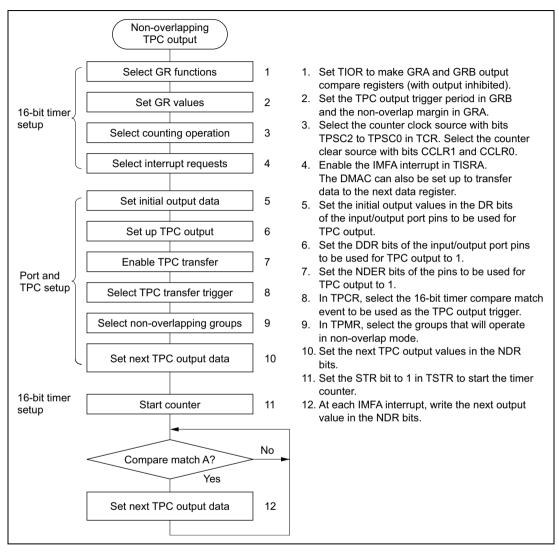

#### 11.3.4 Non-Overlapping TPC Output

**Sample Setup Procedure for Non-Overlapping TPC Output:** Figure 11.6 shows a sample procedure for setting up non-overlapping TPC output.

**Bit 5—Overrun Error (ORER):** Indicates that data reception ended abnormally due to an overrun error.

| Bit 5<br>ORER | Description                                                                                                                                                                 |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | Receiving is in progress or has ended normally <sup>*1</sup> (Initial value)                                                                                                |

|               | [Clearing conditions]                                                                                                                                                       |

|               | The chip is reset or enters standby mode                                                                                                                                    |

|               | <ul> <li>Read ORER when ORER = 1, then write 0 in ORER</li> </ul>                                                                                                           |

| 1             | A receive overrun error occurred <sup>*2</sup>                                                                                                                              |

|               | [Setting condition]                                                                                                                                                         |

|               | Reception of the next serial data ends when RDRF = 1                                                                                                                        |

| Notes: 1.     | Clearing the RE bit to 0 in SCR does not affect the ORER flag, which retains its previous value.                                                                            |

| 2.            | RDR continues to hold the receive data prior to the overrun error, so subsequent receive data is lost. Serial receiving cannot continue while the ORER flag is set to 1. In |

**Bit 4—Framing Error (FER)/Error Signal Status (ERS):** The function of this bit differs for the normal serial communication interface and for the smart card interface. Its function is switched with the SMIF bit in SCMR.

For serial communication interface (SMIF bit in SCMR cleared to 0): Indicates that data reception ended abnormally due to a framing error in asynchronous mode.

synchronous mode, serial transmitting is also disabled.

| Bit 4  |    |                                                                                                                                                                                                                                                                                              |                      |

|--------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| FER    |    | Description                                                                                                                                                                                                                                                                                  |                      |

| 0      |    | Receiving is in progress or has ended normally*1                                                                                                                                                                                                                                             | (Initial value)      |

|        |    | [Clearing conditions]                                                                                                                                                                                                                                                                        |                      |

|        |    | The chip is reset or enters standby mode                                                                                                                                                                                                                                                     |                      |

|        |    | • Read FER when FER = 1, then write 0 in FER                                                                                                                                                                                                                                                 |                      |

| 1      |    | A receive framing error occurred <sup>*2</sup>                                                                                                                                                                                                                                               |                      |

|        |    | [Setting condition]                                                                                                                                                                                                                                                                          |                      |

|        |    | The stop bit at the end of the receive data is checked and f                                                                                                                                                                                                                                 | ound to be 0         |

| Notes: | 1. | Clearing the RE bit to 0 in SCR does not affect the FER flag, which value.                                                                                                                                                                                                                   | retains its previous |

|        | 2. | When the stop bit length is 2 bits, only the first bit is checked. The s<br>not checked. When a framing error occurs the SCI transfers the red<br>but does not set the RDRF flag. Serial receiving cannot continue w<br>set to 1. In synchronous mode, serial transmitting is also disabled. | ceive data into RDR  |

### 14.3.6 Transmitting and Receiving Data

**Initialization:** Before transmitting or receiving data, the smart card interface must be initialized as described below. Initialization is also necessary when switching from transmit mode to receive mode, or vice versa.

- 1. Clear the TE and RE bits to 0 in the serial control register (SCR).

- 2. Clear error flags FER/ERS, PER, and ORER to 0 in the serial status register (SSR).

- 3. Set the parity bit  $(O/\overline{E})$  and baud rate generator select bits (CKS1 and CKS0) in the serial mode register (SMR). Clear the C/A, CHR, and MP bits to 0, and set the STOP and PE bits to 1.

- Set the SMIF, SDIR, and SINV bits in the smart card mode register (SCMR).

When the SMIF bit is set to 1, the TxD pin and RxD pin are both switched from port to SCI pin functions and go to the high-impedance state.

- 5. Set a value corresponding to the desired bit rate in the bit rate register (BRR).

- 6. Set the CKE0 bit in SCR. Clear the TIE, RIE, TE, RE, MPIE, TEIE, and CKE1 bits to 0. If the CKE0 bit is set to 1, the clock is output from the SCK pin.

- 7. Wait at least one bit interval, then set the TIE, RIE, TE, and RE bits in SCR. Do not set the TE bit and RE bit at the same time, except for self-diagnosis.

**Transmitting Serial Data:** As data transmission in smart card mode involves error signal sampling and retransmission processing, the processing procedure is different from that for the normal SCI. Figure 14.5 shows a sample transmission processing flowchart.

- 1. Perform smart card interface mode initialization as described in Initialization above.

- 2. Check that the FER/ERS error flag is cleared to 0 in SSR.

- 3. Repeat steps 2 and 3 until it can be confirmed that the TEND flag is set to 1 in SSR.

- 4. Write the transmit data in TDR, clear the TDRE flag to 0, and perform the transmit operation. The TEND flag is cleared to 0.

- 5. To continue transmitting data, go back to step 2.

- 6. To end transmission, clear the TE bit to 0.

The above processing may include interrupt handling DMA transfer.

If transmission ends and the TEND flag is set to 1 while the TIE bit is set to 1 and interrupt requests are enabled, a transmit-data-empty interrupt (TXI) will be requested. If an error occurs in transmission and the ERS flag is set to 1 while the RIE bit is set to 1 and interrupt requests are enabled, a transmit/receive-error interrupt (ERI) will be requested.

The timing of TEND flag setting depends on the GM bit in SMR (see figure 14.4).

If the TXI interrupt activates the DMAC, the number of bytes designated in the DMAC can be transmitted automatically, including automatic retransmission.

Rev. 2.00, 09/03, page 527 of 890

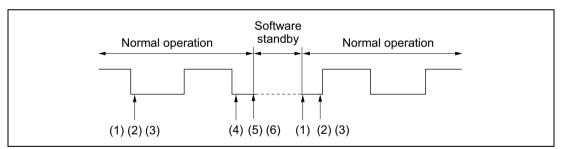

**Examples of Operation in GSM Mode:** When switching between smart card interface mode and software standby mode, use the following procedures to maintain the clock duty cycle.

- Switching from smart card interface mode to software standby mode

- 1. Set the P9<sub>4</sub> data register (DR) and data direction register (DDR) to the values for the fixed output state in software standby mode.

- 2. Write 0 in the TE and RE bits in the serial control register (SCR) to stop transmit/receive operations. At the same time, set the CKE1 bit to the value for the fixed output state in software standby mode.

- 3. Write 0 in the CKE0 bit in SCR to stop the clock.

- 4. Wait for one serial clock cycle. During this period, the duty cycle is preserved and clock output is fixed at the specified level.

- 5. Write H'00 in the serial mode register (SMR) and smart card mode register (SCMR).

- 6. Make the transition to the software standby state.

- Returning from software standby mode to smart card interface mode

- 1. Clear the software standby state.

- 2. Set the CKE1 bit in SCR to the value for the fixed output state at the start of software standby (the current  $P9_4$  pin state).

- 3. Set smart card interface mode and output the clock. Clock signal generation is started with the normal duty cycle.

Figure 14.10 Procedure for Stopping and Restarting the Clock

Use the following procedure to secure the clock duty cycle after powering on.

- 1. The initial state is port input and high impedance. Use pull-up or pull-down resistors to fix the potential.

- 2. Fix at the output specified by the CKE1 bit in SCR.

- 3. Set SMR and SCMR, and switch to smart card interface mode operation.

- 4. Set the CKE0 bit to 1 in SCR to start clock output.

Rev. 2.00, 09/03, page 534 of 890

# 15.5 Interrupts

The A/D converter generates an interrupt (ADI) at the end of A/D conversion. The ADI interrupt request can be enabled or disabled by the ADIE bit in ADCSR. The ADI interrupt request can be designated as a DMAC activation source. In this case, an interrupt request is not sent to the CPU.

# 15.6 Usage Notes

When using the A/D converter, note the following points:

- 1. Analog Input Voltage Range: During A/D conversion, the voltages input to the analog input pins should be in the range  $AV_{SS} \le AN_n \le V_{REF}$ .

- 2. Relationships of AV<sub>CC</sub> and AV<sub>SS</sub> to V<sub>CC</sub> and V<sub>SS</sub>: AV<sub>CC</sub>, AV<sub>SS</sub>, V<sub>CC</sub>, and V<sub>SS</sub> should be related as follows:  $AV_{SS} = V_{SS}$ . AV<sub>CC</sub> and AV<sub>SS</sub> must not be left open, even if the A/D converter is not used.

- 3.  $V_{REF}$  Programming Range: The reference voltage input at the  $V_{REF}$  pin should be in the range  $V_{REF} \le AV_{CC}$ .

- 4. Note on Board Design: In board layout, separate the digital circuits from the analog circuits as much as possible. Particularly avoid layouts in which the signal lines of digital circuits cross or closely approach the signal lines of analog circuits. Induction and other effects may cause the analog circuits to operate incorrectly, or may adversely affect the accuracy of A/D conversion. The analog input signals (AN<sub>0</sub> to AN<sub>7</sub>), analog reference voltage (V<sub>REF</sub>), and analog supply voltage (AV<sub>CC</sub>) must be separated from digital circuits by the analog ground (AV<sub>SS</sub>). The analog ground (AV<sub>SS</sub>) should be connected to a stable digital ground (V<sub>SS</sub>) at one point on the board.

- 5. Note on Noise: To prevent damage from surges and other abnormal voltages at the analog input pins ( $AN_0$  to  $AN_7$ ) and analog reference voltage pin ( $V_{REF}$ ), connect a protection circuit like the one in figure 15.7 between  $AV_{CC}$  and  $AV_{SS}$ . The bypass capacitors connected to  $AV_{CC}$  and  $V_{REF}$  and the filter capacitors connected to  $AN_0$  to  $AN_7$  must be connected to  $AV_{SS}$ . If filter capacitors like the ones in figure 15.7 are connected, the voltage values input to the analog input pins ( $AN_0$  to  $AN_7$ ) will be smoothed, which may give rise to error. Error can also occur if A/D conversion is frequently performed in scan mode so that the current that charges and discharges the capacitor in the sample-and-hold circuit of the A/D converter becomes greater than that input to the analog input pins via input impedance Rin. The circuit constants should therefore be selected carefully.

Figure 21.18 DRAM Bus Timing (CAS Before RAS Refresh)

|                    |              |     | ddre<br>ruc1 |      | -         |             |     |          | )    |  |                                                    |   |   |       |   |   | No.<br>Stat | · · · · |          |

|--------------------|--------------|-----|--------------|------|-----------|-------------|-----|----------|------|--|----------------------------------------------------|---|---|-------|---|---|-------------|---------|----------|

|                    |              | #xx | Rn           | @ERn | @(d, ERn) | @-ERn/@ERn+ | Фаа | @(d, PC) | @@aa |  |                                                    |   |   | ditio |   |   |             | Normal  | Advanced |

|                    | Operand Size | #   | ~            | -    | 0         | 9           | ø   | ø        | 0    |  | Operation                                          | I | н | N     | z | V | C<br>↑      | _       |          |

| BLD #xx:3, @ERd    | B<br>B       |     |              | 4    |           |             | 4   |          |      |  | $(\#xx:3 \text{ of } @ERd) \rightarrow C$          | _ | - | -     | - | - | \$          | 6       |          |

| BLD #xx:3, @aa:8   | В            |     | 2            |      |           |             | 4   |          |      |  | $(\#xx:3 \text{ of } @aa:8) \rightarrow C$         | _ | _ | _     | _ | _ | ↓<br>↓      | 2       |          |

| BILD #xx:3, Rd     | В            |     | 2            | 4    |           |             |     |          |      |  | ¬ (#xx:3 of Rd8) → C                               | _ | _ | -     | - | _ | · ·         | 6       |          |

| BILD #xx:3, @ERd   |              |     |              | 4    |           |             | 4   |          |      |  | $\neg (\#xx:3 \text{ of } @ERd) \rightarrow C$     | _ | - | -     | - | - | \$          |         |          |

| BILD #xx:3, @aa:8  | В            |     |              |      |           |             | 4   |          |      |  | ¬ (#xx:3 of @aa:8) → C                             | — | - | -     | - | - | \$          | 6       |          |

| BST #xx:3, Rd      | В            |     | 2            |      |           |             |     |          |      |  | $C \rightarrow (\#xx:3 \text{ of } Rd8)$           | - | - | -     | - | - | -           | 2       |          |

| BST #xx:3, @ERd    | В            |     |              | 4    |           |             | 4   |          |      |  | $C \rightarrow (\#xx:3 \text{ of } @ERd24)$        | — | - | -     | - | - | -           | 8       |          |

| BST #xx:3, @aa:8   | В            |     |              |      |           |             | 4   |          |      |  | $C \rightarrow (\#xx:3 \text{ of } @aa:8)$         | _ | — | -     | - | - | -           | 8       |          |

| BIST #xx:3, Rd     | В            |     | 2            |      |           |             |     |          |      |  | $\neg C \rightarrow (\#xx:3 \text{ of } Rd8)$      | - | - | -     | - | - | -           | 2       |          |

| BIST #xx:3, @ERd   | В            |     |              | 4    |           |             | _   |          |      |  | $\neg C \rightarrow (\#xx:3 \text{ of } @ERd24)$   | - | - | -     | - | - | -           | 8       |          |

| BIST #xx:3, @aa:8  | В            |     | 0            |      |           |             | 4   |          |      |  | $\neg C \rightarrow (\#xx:3 \text{ of } @aa:8)$    | _ | - | -     | - | - | -           | 8       |          |

| BAND #xx:3, Rd     | В            |     | 2            |      |           |             |     |          |      |  | $C \land (\#xx:3 \text{ of } Rd8) \rightarrow C$   | - | - | -     | - | - | \$          | 2       |          |

| BAND #xx:3, @ERd   | В            |     |              | 4    |           |             | _   |          |      |  | C∧(#xx:3 of @ERd24) → C                            | - | - | -     | - | - | \$          | 6       |          |

| BAND #xx:3, @aa:8  | В            |     |              |      |           |             | 4   |          |      |  | $C \land (\#xx:3 \text{ of } @aa:8) \rightarrow C$ | — | - | -     | - | - | \$          | 6       |          |

| BIAND #xx:3, Rd    | В            |     | 2            |      |           |             |     |          |      |  | $C \land \neg$ (#xx:3 of Rd8) $\rightarrow$ C      | — | — | -     | - | - | \$          | 2       |          |

| BIAND #xx:3, @ERd  | В            |     |              | 4    |           |             |     |          |      |  | C∧ ¬ (#xx:3 of @ERd24) → C                         | — | — | -     | - | - | \$          | 6       |          |

| BIAND #xx:3, @aa:8 | В            |     |              |      |           |             | 4   |          |      |  | C∧ ¬ (#xx:3 of @aa:8) → C                          | — | — | -     | - | - | \$          | 6       |          |

| BOR #xx:3, Rd      | В            |     | 2            |      |           |             |     |          |      |  | $C \lor (\#xx:3 \text{ of } Rd8) \rightarrow C$    | — | — | -     | - | - | \$          | 2       |          |

| BOR #xx:3, @ERd    | В            |     |              | 4    |           |             |     |          |      |  | $C \lor (\#xx:3 \text{ of } @ERd24) \rightarrow C$ | — | - | -     | - | - | \$          | 6       |          |

| BOR #xx:3, @aa:8   | В            |     |              |      |           |             | 4   |          |      |  | C∨(#xx:3 of @aa:8) → C                             | — | — | -     | - | - | \$          | 6       | ;        |

| BIOR #xx:3, Rd     | В            |     | 2            |      |           |             |     |          |      |  | C∨ ¬ (#xx:3 of Rd8) → C                            | — | — | -     | - | - | \$          | 2       | 2        |

| BIOR #xx:3, @ERd   | В            |     |              | 4    |           |             |     |          |      |  | C∨¬ (#xx:3 of @ERd24) → C                          | — | — | -     | - | - | \$          | 6       | ;        |

| BIOR #xx:3, @aa:8  | В            |     |              |      |           |             | 4   |          |      |  | C∨ ¬ (#xx:3 of @aa:8) → C                          | — | — | -     | - | - | \$          | 6       | \$       |

| BXOR #xx:3, Rd     | В            |     | 2            |      |           |             |     |          |      |  | C⊕(#xx:3 of Rd8) → C                               | - | - | -     | - | - | \$          | 2       | 2        |

| BXOR #xx:3, @ERd   | в            |     |              | 4    |           |             |     |          |      |  | C⊕(#xx:3 of @ERd24) → C                            | _ | — | -     | - | - | \$          | 6       | \$       |

| BXOR #xx:3, @aa:8  | в            |     |              |      |           |             | 4   |          |      |  | C⊕(#xx:3 of @aa:8) → C                             | _ | — | -     | - | - | \$          | 6       | \$       |

| BIXOR #xx:3, Rd    | в            |     | 2            |      |           |             |     |          |      |  | C⊕ ¬ (#xx:3 of Rd8) → C                            | - | - | -     | - | - | \$          | 2       | 2        |

| BIXOR #xx:3, @ERd  | в            |     |              | 4    |           |             |     |          |      |  | C⊕ ¬ (#xx:3 of @ERd24) → C                         | _ | _ | -     | - | - | \$          | 6       | \$       |

| BIXOR #xx:3, @aa:8 | В            |     |              |      |           |             | 4   |          |      |  | C⊕ ¬ (#xx:3 of @aa:8) → C                          | — | — | -     | — | - | \$          | 6       | \$       |

| Address          | Deviator         | Data         | Bit Names |         |       |       |       |       |       |       |                 |

|------------------|------------------|--------------|-----------|---------|-------|-------|-------|-------|-------|-------|-----------------|

| Address<br>(Low) | Register<br>Name | Bus<br>Width | Bit 7     | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | —Module<br>Name |

| H'EE0B0          | Reserved         | area (acc    | cess proh | ibited) |       |       |       |       |       |       |                 |

| H'EE0B1          |                  |              |           |         |       |       |       |       |       |       |                 |

| H'EE0B2          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0B3          |                  |              |           |         |       |       |       |       |       |       |                 |

| H'EE0B4          |                  |              |           |         |       |       |       |       |       |       |                 |

| H'EE0B5          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0B6          |                  |              |           |         |       |       |       |       |       |       |                 |

| H'EE0B7          |                  |              |           |         |       |       |       |       |       |       |                 |

| H'EE0B8          |                  |              |           |         |       |       |       |       |       |       |                 |

| H'EE0B9          |                  |              |           |         |       |       |       |       |       |       |                 |

| H'EE0BA          |                  |              |           |         |       |       |       |       |       |       |                 |

| H'EE0BB          |                  |              |           |         |       |       |       |       |       |       |                 |

| H'EE0BC          |                  |              |           |         |       |       |       |       |       |       |                 |

| H'EE0BD          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0BE          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0BF          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0C0          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0C1          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0C2          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0C3          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0C4          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0C5          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0C6          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0C7          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0C8          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0C9          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0CA          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0CB          |                  |              |           |         |       |       |       |       |       |       |                 |

| H'EE0CC          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0CD          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0CE          | _                |              |           |         |       |       |       |       |       |       |                 |

| H'EE0CF          |                  |              |           |         |       |       |       |       |       |       |                 |

| Address | Register | Data<br>Bus | Bit Names |       |       |       |       |       |       |       |                 |  |

|---------|----------|-------------|-----------|-------|-------|-------|-------|-------|-------|-------|-----------------|--|

| (Low)   | Name     |             | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | —Module<br>Name |  |

| H'FFE30 | _        |             | _         | _     | _     | _     | _     |       | _     | _     |                 |  |

| H'FFE31 | _        |             | _         | _     | _     | _     | _     | _     | _     |       |                 |  |

| H'FFE32 | _        |             | _         | _     | _     | _     | _     | _     | _     |       |                 |  |

| H'FFE33 | _        |             | _         | _     | _     | _     | _     | _     | _     |       |                 |  |

| H'FFE34 | _        |             | _         | _     | —     | —     | _     | _     | _     | _     |                 |  |

| H'FFE35 | _        |             | —         | _     | _     | —     | —     | —     | _     | _     |                 |  |

| H'FFE36 | _        |             | _         | _     | —     | —     | _     | —     | _     | _     |                 |  |

| H'FFE37 | _        |             | —         | _     | _     | —     | —     | —     | _     | _     |                 |  |

| H'FFE38 | _        |             | —         | _     | _     | _     | _     | _     | _     | _     |                 |  |

| H'FFE39 | _        |             | _         | _     | _     | _     | _     | _     | _     | _     |                 |  |

| H'FFE3A | _        |             | _         | _     | _     | _     | _     | _     | _     | _     |                 |  |

| H'FFE3B | _        |             | _         | _     | _     | _     | _     | _     | _     | _     |                 |  |

| H'FFE3C | —        |             | _         | —     | _     | _     | —     | _     | —     | —     |                 |  |

| H'FFE3D | _        |             | _         | _     |       | _     | —     |       | _     | _     |                 |  |

| H'FFE3E | _        |             | —         | —     | _     | _     | _     | _     | _     | —     |                 |  |

| H'FFE3F | _        |             | _         | _     | —     | _     | _     | _     | _     | _     |                 |  |

| H'FFE40 | _        |             | _         | _     | —     | —     | _     | _     | _     | _     |                 |  |

| H'FFE41 | _        |             | —         | _     | _     | —     | —     | —     | _     | _     |                 |  |

| H'FFE42 | _        |             | _         | _     |       | _     | —     |       | _     | _     |                 |  |

| H'FFE43 | _        |             | —         | _     | _     | —     | —     | —     | _     | _     |                 |  |

| H'FFE44 | _        |             | —         | _     | _     | —     | —     | —     | _     | _     |                 |  |

| H'FFE45 | _        |             | —         | _     | _     | —     | —     | —     | _     | _     |                 |  |

| H'FFE46 | _        |             | _         | _     |       | _     | —     |       | _     | _     |                 |  |

| H'FFE47 | _        |             | —         | _     | _     | —     | —     | —     | _     | _     |                 |  |

| H'FFE48 | _        |             | —         | _     |       | _     | —     |       | _     | _     |                 |  |

| H'FFE49 | _        |             | _         | _     | _     | _     | _     | _     | _     | _     |                 |  |

| H'FFE4A | _        |             | _         | _     | _     | _     | _     | _     | _     | _     |                 |  |

| H'FFE4B | _        |             | _         | —     | _     | _     | _     | _     | _     | _     |                 |  |

| H'FFE4C | _        |             | _         | _     |       | _     | —     |       | _     | _     |                 |  |

| H'FFE4D | _        |             | —         | _     | _     | _     | —     |       | _     | _     |                 |  |

| H'FFE4E | _        |             | _         | _     | _     | _     | _     | _     | _     | _     |                 |  |

| H'FFE4F | _        |             | _         | _     |       | _     | _     | _     | _     | _     |                 |  |

**IPRA**—Interrupt Priority Register A

**H'EE018**

**Interrupt Controller**

| Bit                         | 7        | 6        | 5        | 4            | 3             | 2             | 1        | 0        |

|-----------------------------|----------|----------|----------|--------------|---------------|---------------|----------|----------|

|                             | IPRA7    | IPRA6    | IPRA5    | IPRA4        | IPRA3         | IPRA2         | IPRA1    | IPRA0    |

| Initial value<br>Read/Write | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W     | 0<br>R/W      | 0<br>R/W      | 0<br>R/W | 0<br>R/W |

|                             |          |          | Р        | riority leve | l A7 to A0    |               |          |          |

|                             |          |          |          | 0 Priorit    | y level 0 (le | ow priority   | )        |          |

|                             |          |          |          | 1 Priorit    | y level 1 (h  | high priority | /)       |          |

· Interrupt sources controlled by each bit

|      | Bit                 | Bit 7 | Bit 6 | Bit 5         | Bit 4         | Bit 3                                       | Bit 2                        | Bit 1                        | Bit 0                        |

|------|---------------------|-------|-------|---------------|---------------|---------------------------------------------|------------------------------|------------------------------|------------------------------|

|      | ы                   | IPRA7 | IPRA6 | IPRA5         | IPRA4         | IPRA3                                       | IPRA2                        | IPRA1                        | IPRA0                        |

| IPRA | Interrupt<br>source | IRQ₀  | IRQ1  | IRQ2,<br>IRQ3 | IRQ4,<br>IRQ5 | WDT,<br>DRAM<br>interface,<br>A/D converter | 16-bit<br>timer<br>channel 0 | 16-bit<br>timer<br>channel 1 | 16-bit<br>timer<br>channel 2 |

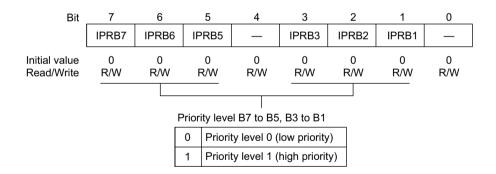

**IPRB**—Interrupt Priority Register B

H'EE019

**Interrupt Controller**

· Interrupt sources controlled by each bit

|      | Bit                 | Bit 7                              | Bit 6                              | Bit 5 | Bit 4 | Bit 3            | Bit 2            | Bit 1            | Bit 0 |

|------|---------------------|------------------------------------|------------------------------------|-------|-------|------------------|------------------|------------------|-------|

|      |                     | IPRB7                              | IPRB6                              | IPRB5 | _     | IPRB3            | IPRB2            | IPRB1            | _     |

| IPRB | Interrupt<br>source | 8-bit timer<br>channels<br>0 and 1 | 8-bit timer<br>channels<br>2 and 3 | DMAC  | _     | SCI<br>channel 0 | SCI<br>channel 1 | SCI<br>channel 2 | —     |

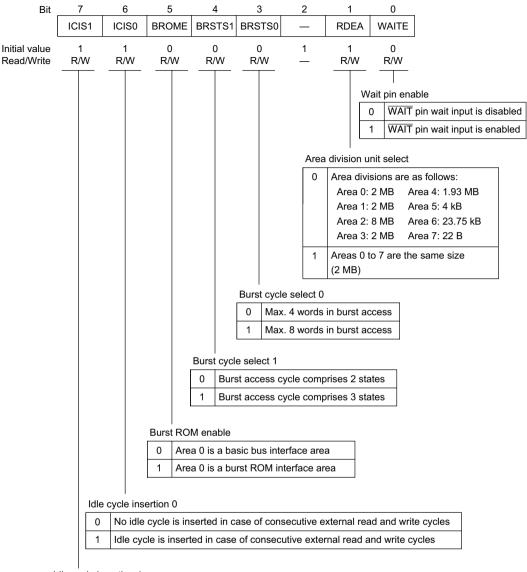

#### **BCR—Bus Control Register**

H'EE024

#### **Bus controller**

Idle cycle insertion 1

| 0 | No idle cycle is inserted in case of consecutive external read cycles for different areas |

|---|-------------------------------------------------------------------------------------------|

| 1 | Idle cycle is inserted in case of consecutive external read cycles for different areas    |

### Renesas

#### Rev. 2.00, 09/03, page 767 of 890

H'EE031

Flash Memory

- Notes: 1. Writes to FLMCR2 are prohibited.

- 2. This register is used only by the flash memory version and do not exist in the mask ROM version. In the mask ROM version reading these addresses always returns a value of 1, and it is not possible to write to them.

| EBR (EBR1)—Erase B                                 | lock Reg |           | H'E       | E032         | Flash    | Flash Memory |          |          |  |

|----------------------------------------------------|----------|-----------|-----------|--------------|----------|--------------|----------|----------|--|

| Bit                                                | 7        | 6         | 5         | 4            | 3        | 2            | 1        | 0        |  |

|                                                    | EB7      | EB6       | EB5       | EB4          | EB3      | EB2          | EB1      | EB0      |  |

| Modes 1 to { Initial value 4, and 6 { Read/Write   | 0<br>R   | 0<br>R    | 0<br>R    | 0<br>R       | 0<br>R   | 0<br>R       | 0<br>R   | 0<br>R   |  |

| Modes 5 { Initial value<br>and 7 { Read/Write      | 0<br>R   | 0<br>R/W  | 0<br>R/W  | 0<br>R/W     | 0<br>R/W | 0<br>R/W     | 0<br>R/W | 0<br>R/W |  |

|                                                    | Bloo     | ck 7 to 0 |           |              |          |              |          |          |  |

| 0 Block EB7 to EB0 is not selected (Initial value) |          |           |           |              |          |              |          |          |  |

|                                                    | 1        | Block E   | EB7 to EB | ) is selecte | ed       |              |          |          |  |

Notes: 1. When not erasing, clear EBR to H'00. Writes are invalid.

A value of 1 cannot be set in this register in mode 6.

2. This register is used only by the flash memory version and do not exist in the mask ROM version. In the mask ROM version reading these addresses always returns a value of 1, and it is not possible to write to them.