THE PERSON NUMBER

Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8/16-Bit                                                                  |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 34                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 4K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-VQFN (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega32c4-mhr |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Ordering Information** 1.

| Ordering code                  | Flash<br>[bytes] | EEPROM<br>[bytes] | SRAM<br>[bytes] | Speed<br>[MHz] | Power supply<br>[V] | Package <sup>(1)(2)(3)</sup> | Temp.<br>[°C] |

|--------------------------------|------------------|-------------------|-----------------|----------------|---------------------|------------------------------|---------------|

| ATxmega32C4-AU                 | 32K + 4K         | 1K                | 4K              |                |                     |                              |               |

| ATxmega32C4-AUR <sup>(4)</sup> | 32K + 4K         | 1K                | 4K              |                |                     | 44A                          |               |

| ATxmega16C4-AU                 | 16K + 4K         | 1K                | 2K              |                |                     | 44A                          |               |

| ATxmega16C4-AUR <sup>(4)</sup> | 16K + 4K         | 1K                | 2K              |                |                     |                              |               |

| ATxmega32C4-MH                 | 32K + 4K         | 1K                | 4K              |                |                     |                              | _             |

| ATxmega32C4-MHR <sup>(4)</sup> | 32K + 4K         | 1K                | 4K              |                |                     | DW                           | 40.05         |

| ATxmega16C4-MH                 | 16K + 4K         | 1K                | 2K              |                |                     | PW                           | -40 - 85      |

| ATxmega16C4-MHR <sup>(4)</sup> | 16K + 4K         | 1K                | 2K              |                |                     |                              |               |

| ATxmega32C4-CU                 | 32K + 4K         | 1K                | 4K              |                |                     |                              |               |

| ATxmega32C4-CUR <sup>(4)</sup> | 32K + 4K         | 1K                | 4K              |                |                     | 7P                           |               |

| ATxmega16C4-CU                 | 16K + 4K         | 1K                | 2K              | 32             | 1.6 - 3.6           |                              |               |

| ATxmega16C4-CUR <sup>(4)</sup> | 16K + 4K         | 1K                | 2K              |                |                     |                              |               |

| ATxmega32C4-AN                 | 32K + 4K         | 1K                | 4K              | -              |                     |                              |               |

| ATxmega32C4-ANR <sup>(4)</sup> | 32K + 4K         | 1K                | 4K              |                |                     |                              |               |

| ATxmega16C4-AN                 | 16K + 4K         | 1K                | 2K              | -              |                     | 44A                          |               |

| ATxmega16C4-ANR <sup>(4)</sup> | 16K + 4K         | 1K                | 2K              |                |                     |                              |               |

| ATxmega32C4-M7                 | 32K + 4K         | 1K                | 4K              |                |                     |                              | -40 - 105     |

| ATxmega32C4-M7R <sup>(4)</sup> | 32K + 4K         | 1K                | 4K              |                |                     |                              |               |

| ATxmega16C4-M7                 | 16K + 4K         | 1K                | 2K              |                |                     | PW                           |               |

| ATxmega16C4-M7R <sup>(4)</sup> | 16K + 4K         | 1K                | 2K              |                |                     |                              |               |

2. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

3. For packaging information, see "Packaging Information" on page 62.

4. Tape and Reel.

## 7. Memories

### 7.1 Features

- Flash program memory

- One linear address space

- In-system programmable

- Self-programming and boot loader support

- Application section for application code

- Application table section for application code or data storage

- Boot section for application code or boot loader code

- Separate read/write protection lock bits for all sections

- Built in fast CRC check of a selectable flash program memory section

- Data memory

- One linear address space

- Single-cycle access from CPU

- SRAM

- EEPROM

- Byte and page accessible

- Optional memory mapping for direct load and store

- I/O memory

- Configuration and status registers for all peripherals and modules

- Four bit-accessible general purpose registers for global variables or flags

- Separate buses for SRAM, EEPROM and I/O memory

- Simultaneous bus access for CPU

- Production signature row memory for factory programmed data

- ID for each microcontroller device type

- Serial number for each device

- Calibration bytes for factory calibrated peripherals

- User signature row

- One flash page in size

- Can be read and written from software

- Content is kept after chip erase

### 7.2 Overview

The Atmel AVR architecture has two main memory spaces, the program memory and the data memory. Executable code can reside only in the program memory, while data can be stored in the program memory and the data memory. The data memory includes the internal SRAM, and EEPROM for nonvolatile data storage. All memory spaces are linear and require no memory bank switching. Nonvolatile memory (NVM) spaces can be locked for further write and read/write operations. This prevents unrestricted access to the application software.

A separate memory section contains the fuse bytes. These are used for configuring important system functions, and can only be written by an external programmer.

The available memory size configurations are shown in "Ordering Information" on page 2. In addition, each device has a Flash memory signature row for calibration data, device identification, serial number etc.

### 7.3 Flash Program Memory

The Atmel AVR XMEGA devices contain on-chip, in-system reprogrammable flash memory for program storage. The flash memory can be accessed for read and write from an external programmer through the PDI or from application software running in the device.

All AVR CPU instructions are 16 or 32 bits wide, and each flash location is 16 bits wide. The flash memory is organized in two main sections, the application section and the boot loader section. The sizes of the different sections are fixed, but

## 10. Power Management and Sleep Modes

### 10.1 Features

- · Power management for adjusting power consumption and functions

- Five sleep modes:

- Idle

- Power down

- Power save

- Standby

- Extended standby

- Power reduction register to disable clock and turn off unused peripherals in active and idle modes

### 10.2 Overview

Various sleep modes and clock gating are provided in order to tailor power consumption to application requirements. This enables the Atmel AVR XMEGA microcontroller to stop unused modules to save power.

All sleep modes are available and can be entered from active mode. In active mode, the CPU is executing application code. When the device enters sleep mode, program execution is stopped and interrupts or a reset is used to wake the device again. The application code decides which sleep mode to enter and when. Interrupts from enabled peripherals and all enabled reset sources can restore the microcontroller from sleep to active mode.

In addition, power reduction registers provide a method to stop the clock to individual peripherals from software. When this is done, the current state of the peripheral is frozen, and there is no power consumption from that peripheral. This reduces the power consumption in active mode and idle sleep modes and enables much more fine-tuned power management than sleep modes alone.

### 10.3 Sleep Modes

Sleep modes are used to shut down modules and clock domains in the microcontroller in order to save power. XMEGA microcontrollers have five different sleep modes tuned to match the typical functional stages during application execution. A dedicated sleep instruction (SLEEP) is available to enter sleep mode. Interrupts are used to wake the device from sleep, and the available interrupt wake-up sources are dependent on the configured sleep mode. When an enabled interrupt occurs, the device will wake up and execute the interrupt service routine before continuing normal program execution from the first instruction after the SLEEP instruction. If other, higher priority interrupts are pending when the wake-up occurs, their interrupt service routines will be executed according to their priority before the interrupt service routine for the wake-up interrupt is executed. After wake-up, the CPU is halted for four cycles before execution starts.

The content of the register file, SRAM and registers are kept during sleep. If a reset occurs during sleep, the device will reset, start up, and execute from the reset vector.

#### 10.3.1 Idle Mode

In idle mode the CPU and nonvolatile memory are stopped (note that any ongoing programming will be completed), but all peripherals, including the interrupt controller, and event system are kept running. Any enabled interrupt will wake the device.

### 10.3.2 Power-down Mode

In power-down mode, all clocks, including the real-time counter clock source, are stopped. This allows operation only of asynchronous modules that do not require a running clock. The only interrupts that can wake up the MCU are the twowire interface address match interrupt, asynchronous port interrupts, and the USB resume interrupt.

## 13. Interrupts and Programmable Multilevel Interrupt Controller

### 13.1 Features

- Short and predictable interrupt response time

- Separate interrupt configuration and vector address for each interrupt

- Programmable multilevel interrupt controller

- Interrupt prioritizing according to level and vector address

- Three selectable interrupt levels for all interrupts: low, medium, and high

- Selectable, round-robin priority scheme within low-level interrupts

- Non-maskable interrupts for critical functions

- Interrupt vectors optionally placed in the application section or the boot loader section

### 13.2 Overview

Interrupts signal a change of state in peripherals, and this can be used to alter program execution. Peripherals can have one or more interrupts, and all are individually enabled and configured. When an interrupt is enabled and configured, it will generate an interrupt request when the interrupt condition is present. The programmable multilevel interrupt controller (PMIC) controls the handling and prioritizing of interrupt requests. When an interrupt request is acknowledged by the PMIC, the program counter is set to point to the interrupt vector, and the interrupt handler can be executed.

All peripherals can select between three different priority levels for their interrupts: low, medium, and high. Interrupts are prioritized according to their level and their interrupt vector address. Medium-level interrupts will interrupt low-level interrupt handlers. High-level interrupts will interrupt both medium- and low-level interrupt handlers. Within each level, the interrupt priority is decided from the interrupt vector address, where the lowest interrupt vector address has the highest interrupt priority. Low-level interrupts have an optional round-robin scheduling scheme to ensure that all interrupts are serviced within a certain amount of time.

Non-maskable interrupts (NMI) are also supported, and can be used for system critical functions.

### 13.3 Interrupt Vectors

The interrupt vector is the sum of the peripheral's base interrupt address and the offset address for specific interrupts in each peripheral. The base addresses for the Atmel AVR XMEGA C4 devices are shown in Table 13-1 on page 28. Offset addresses for each interrupt available in the peripheral are described for each peripheral in the XMEGA C manual. For peripherals or modules that have only one interrupt, the interrupt vector is shown in Table 13-1 on page 28. The program address is the word address.

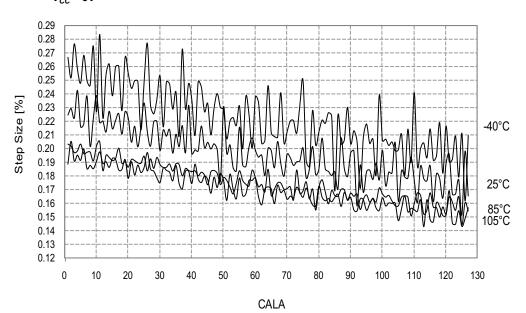

Only Timer/Counter 0 has the split mode feature that split it into two 8-bit Timer/Counters with four compare channels each.

Some timer/counters have extensions to enable more specialized waveform and frequency generation. The advanced waveform extension (AWeX) is intended for motor control and other power control applications. It enables low- and high-side output with dead-time insertion, as well as fault protection for disabling and shutting down external drivers. It can also generate a synchronized bit pattern across the port pins.

The advanced waveform extension can be enabled to provide extra and more advanced features for the Timer/Counter. This are only available for Timer/Counter 0. See "AWeX – Advanced Waveform Extension" on page 36 for more details.

The high-resolution (hi-res) extension can be used to increase the waveform output resolution by four or eight times by using an internal clock source running up to four times faster than the peripheral clock. See "Hi-Res – High Resolution Extension" on page 37 for more details.

Figure 15-1. Overview of a Timer/Counter and Closely Related Peripherals

PORTC has one Timer/Counter 0 and one Timer/Counter1. PORTD, and PORTE each has one timer/counter 0. Notation of these are TCC0 (time/counter C0), TCC1, TCD0, and TCE0 respectively.

| Mnemonics Operands Description |       |                                              |                       | ation                                                                           |                                   | Flags     | #Clocks          |

|--------------------------------|-------|----------------------------------------------|-----------------------|---------------------------------------------------------------------------------|-----------------------------------|-----------|------------------|

| SPM                            | Z+    | Store Program Memory and Post-Increment by 2 | (RAMPZ:Z)<br>Z        | ←<br>←                                                                          | R1:R0,<br>Z + 2                   | None      | -                |

| IN                             | Rd, A | In From I/O Location                         | Rd                    | ←                                                                               | I/O(A)                            | None      | 1                |

| OUT                            | A, Rr | Out To I/O Location                          | I/O(A)                | ←                                                                               | Rr                                | None      | 1                |

| PUSH                           | Rr    | Push Register on Stack                       | STACK                 | ←                                                                               | Rr                                | None      | 1 <sup>(1)</sup> |

| POP                            | Rd    | Pop Register from Stack                      | Rd                    | ←                                                                               | STACK                             | None      | 2 <sup>(1)</sup> |

| ХСН                            | Z, Rd | Exchange RAM location                        | Temp<br>Rd<br>(Z)     | $\begin{array}{c} \uparrow \\ \uparrow \\ \downarrow \\ \downarrow \end{array}$ | Rd,<br>(Z),<br>Temp               | None      | 2                |

| LAS                            | Z, Rd | Load and Set RAM location                    | Temp<br>Rd<br>(Z)     | $\downarrow \downarrow \downarrow$                                              | Rd,<br>(Z),<br>Temp v (Z)         | None      | 2                |

| LAC                            | Z, Rd | Load and Clear RAM location                  | Temp<br>Rd<br>(Z)     | $\begin{array}{c} \leftarrow \\ \leftarrow \\ \leftarrow \end{array}$           | Rd,<br>(Z),<br>(\$FFh – Rd) ● (Z) | None      | 2                |

| LAT                            | Z, Rd | Load and Toggle RAM location                 | Temp<br>Rd<br>(Z)     | $\begin{array}{c} \leftarrow \\ \leftarrow \\ \leftarrow \end{array}$           | Rd,<br>(Z),<br>Temp ⊕ (Z)         | None      | 2                |

|                                |       | Bit and                                      | bit-test instructions |                                                                                 |                                   |           | _                |

| LSL                            | Rd    | Logical Shift Left                           | Rd(n+1)<br>Rd(0)<br>C | $\downarrow \uparrow \downarrow$                                                | Rd(n),<br>0,<br>Rd(7)             | Z,C,N,V,H | 1                |

| LSR                            | Rd    | Logical Shift Right                          | Rd(n)<br>Rd(7)<br>C   | $\downarrow \downarrow \downarrow$                                              | Rd(n+1),<br>0,<br>Rd(0)           | Z,C,N,V   | 1                |

| ROL                            | Rd    | Rotate Left Through Carry                    | Rd(0)<br>Rd(n+1)<br>C | $\downarrow \downarrow \downarrow$                                              | C,<br>Rd(n),<br>Rd(7)             | Z,C,N,V,H | 1                |

| ROR                            | Rd    | Rotate Right Through Carry                   | Rd(7)<br>Rd(n)<br>C   | $\begin{array}{c} \leftarrow \\ \leftarrow \\ \leftarrow \end{array}$           | C,<br>Rd(n+1),<br>Rd(0)           | Z,C,N,V   | 1                |

| ASR                            | Rd    | Arithmetic Shift Right                       | Rd(n)                 | ←                                                                               | Rd(n+1), n=06                     | Z,C,N,V   | 1                |

| SWAP                           | Rd    | Swap Nibbles                                 | Rd(30)                | $\leftrightarrow$                                                               | Rd(74)                            | None      | 1                |

| BSET                           | S     | Flag Set                                     | SREG(s)               | ←                                                                               | 1                                 | SREG(s)   | 1                |

| BCLR                           | s     | Flag Clear                                   | SREG(s)               | ←                                                                               | 0                                 | SREG(s)   | 1                |

| SBI                            | A, b  | Set Bit in I/O Register                      | I/O(A, b)             | ←                                                                               | 1                                 | None      | 1                |

| CBI                            | A, b  | Clear Bit in I/O Register                    | I/O(A, b)             | ←                                                                               | 0                                 | None      | 1                |

| BST                            | Rr, b | Bit Store from Register to T                 | Т                     | ←                                                                               | Rr(b)                             | т         | 1                |

| BLD                            | Rd, b | Bit load from T to Register                  | Rd(b)                 | ←                                                                               | т                                 | None      | 1                |

| SEC                            |       | Set Carry                                    | С                     | ←                                                                               | 1                                 | с         | 1                |

| CLC                            |       | Clear Carry                                  | C                     | ←                                                                               | 0                                 | с         | 1                |

| SEN                            |       | Set Negative Flag                            | N                     | ←                                                                               | 1                                 | N         | 1                |

| CLN                            |       | Clear Negative Flag                          | N                     | ←                                                                               | 0                                 | N         | 1                |

| SEZ                            |       | Set Zero Flag                                | Z                     | ←                                                                               | 1                                 | Z         | 1                |

| CLZ                            |       | Clear Zero Flag                              | Z                     | ←                                                                               | 0                                 | Z         | 1                |

| SEI                            |       | Global Interrupt Enable                      | I                     | ←                                                                               | 1                                 | 1         | 1                |

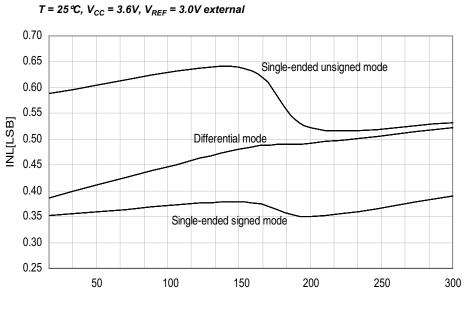

#### Table 33-39. Accuracy Characteristics

| Symbol             | Parameter                  | Co                            | ndition <sup>(2)</sup>          | Min. | Тур. | Max. | Units |

|--------------------|----------------------------|-------------------------------|---------------------------------|------|------|------|-------|

| RES                | Resolution                 | 12-bit resolution             | Differential                    | 8    | 12   | 12   |       |

|                    |                            |                               | Single ended signed             | 7    | 11   | 11   | Bits  |

|                    |                            |                               | Single ended unsigned           | 8    | 12   | 12   |       |

|                    |                            | D‴                            | 16ksps, V <sub>REF</sub> = 3V   |      | 0.5  | 1    |       |

|                    |                            |                               | 16ksps, all V <sub>REF</sub>    |      | 0.8  | 2    |       |

| INL <sup>(1)</sup> | Integral non-linearity     | Differential mode             | 300ksps, V <sub>REF</sub> = 3V  |      | 0.6  | 1    | _     |

|                    | integral non-inteanty      |                               | 300ksps, all V <sub>REF</sub>   |      | 1    | 2    |       |

|                    |                            | Single ended                  | 16ksps, V <sub>REF</sub> = 3.0V |      | 0.5  | 1    | _     |

|                    |                            | unsigned mode                 | 16ksps, all V <sub>REF</sub>    |      | 1.3  | 2    | Isb   |

|                    |                            |                               | 16ksps, V <sub>REF</sub> = 3V   |      | 0.3  | 1    | - 150 |

|                    |                            | Differential mode             | 16ksps, all V <sub>REF</sub>    |      | 0.5  | 1    |       |

| DNL <sup>(1)</sup> | Differential non-linearity | Differential mode             | 300ksps, V <sub>REF</sub> = 3V  |      | 0.35 | 1    |       |

| DINLY              |                            |                               | 300ksps, all V <sub>REF</sub>   |      | 0.5  | 1    |       |

|                    |                            | Single ended<br>unsigned mode | 16ksps, V <sub>REF</sub> = 3.0V |      | 0.6  | 1    |       |

|                    |                            |                               | 16ksps, all V <sub>REF</sub>    |      | 0.6  | 1    |       |

|                    |                            | Differential mode             |                                 |      | 8    |      | mV    |

|                    | Offset Error               |                               | Temperature drift               |      | 0.01 |      | mV/K  |

|                    |                            |                               | Operating voltage drift         |      | 0.25 |      | mV/V  |

|                    |                            |                               | External reference              |      | -5   |      |       |

|                    |                            | Gain Error Differential mode  | AV <sub>CC</sub> /1.6           |      | -5   |      | mV    |

|                    | Gain Error                 |                               | AV <sub>CC</sub> /2.0           |      | -6   |      |       |

|                    | Gain Entri                 |                               | Bandgap                         |      | ±10  |      |       |

|                    |                            |                               | Temperature drift               |      | 0.02 |      | mV/K  |

|                    |                            |                               | Operating voltage drift         |      | 2    |      | mV/V  |

|                    |                            |                               | External reference              |      | -8   |      |       |

|                    |                            | Single ended<br>unsigned mode | AV <sub>CC</sub> /1.6           |      | -8   |      | mV    |

|                    | Gain Error                 |                               | AV <sub>CC</sub> /2.0           |      | -8   |      | IIIV  |

|                    | Gamenor                    |                               | Bandgap                         |      | ±10  |      |       |

|                    |                            |                               | Temperature drift               |      | 0.03 |      | mV/K  |

|                    |                            |                               | Operating voltage drift         |      | 2    |      | mV/V  |

Notes: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% input voltage range.

2. Unless otherwise noted all linearity, offset and gain error numbers are valid under the condition that external VREF is used.

#### Table 33-58. Two-wire Interface Characteristics

| Symbol              | Parameter                                                      | Condition                                                         | Min.                                   | Тур. | Max.                 | Units |

|---------------------|----------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------|------|----------------------|-------|

| V <sub>IH</sub>     | Input high voltage                                             |                                                                   | 0.7*V <sub>CC</sub>                    |      | V <sub>CC</sub> +0.5 |       |

| V <sub>IL</sub>     | Input low voltage                                              |                                                                   | -0.5                                   |      | 0.3*V <sub>CC</sub>  | V     |

| V <sub>hys</sub>    | Hysteresis of Schmitt trigger inputs                           |                                                                   | 0.05*V <sub>CC</sub> <sup>(1)</sup>    |      |                      | V     |

| V <sub>OL</sub>     | Output low voltage                                             | 3mA, sink current                                                 | 0                                      |      | 0.4                  |       |

| t <sub>r</sub>      | Rise time for both SDA and SCL                                 |                                                                   | 20+0.1C <sub>b</sub> <sup>(1)(2)</sup> |      | 300                  |       |

| t <sub>of</sub>     | Output fall time from $V_{\text{IHmin}}$ to $V_{\text{ILmax}}$ | $10pF < C_b < 400pF^{(2)}$                                        | 20+0.1C <sub>b</sub> <sup>(1)(2)</sup> |      | 250                  | ns    |

| t <sub>SP</sub>     | Spikes suppressed by input filter                              |                                                                   | 0                                      |      | 50                   |       |

| I <sub>I</sub>      | Input current for each I/O Pin                                 | $0.1V_{CC} < V_{I} < 0.9V_{CC}$                                   | -10                                    |      | 10                   | μA    |

| CI                  | Capacitance for each I/O Pin                                   |                                                                   |                                        |      | 10                   | pF    |

| f <sub>SCL</sub>    | SCL clock frequency                                            | f <sub>PER</sub> <sup>(3)</sup> >max(10f <sub>SCL</sub> , 250kHz) | 0                                      |      | 400                  | kHz   |

| <b>_</b>            |                                                                | $f_{SCL} \le 100 kHz$                                             | $V_{CC} - 0.4V$                        |      | $\frac{100ns}{C_b}$  | 0     |

| R <sub>P</sub>      | Value of pull-up resistor                                      | f <sub>SCL</sub> > 100kHz                                         | $\frac{V_{CC} - 0.4V}{3mA}$            |      | $\frac{300ns}{C_b}$  | Ω     |

|                     |                                                                | f <sub>SCL</sub> ≤ 100kHz                                         | 4.0                                    |      |                      |       |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition                           | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                      |       |

|                     | Low pariad of SCL alask                                        | $f_{SCL} \le 100 kHz$                                             | 4.7                                    |      |                      |       |

| t <sub>LOW</sub>    | Low period of SCL clock                                        | f <sub>SCL</sub> > 100kHz                                         | 1.3                                    |      |                      |       |

| +                   | High period of SCL clock                                       | $f_{SCL} \le 100 kHz$                                             | 4.0                                    |      |                      |       |

| t <sub>HIGH</sub>   | high period of SCL clock                                       | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                      |       |

| t                   | Set-up time for a repeated START                               | for a repeated START $f_{SCL} \le 100 \text{kHz}$                 | 4.7                                    |      |                      |       |

| t <sub>SU;STA</sub> | condition                                                      | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                      |       |

| +                   | Data hold time                                                 | $f_{SCL} \le 100 kHz$                                             | 0                                      |      | 3.45                 | μs    |

| t <sub>HD;DAT</sub> |                                                                | f <sub>SCL</sub> > 100kHz                                         | 0                                      |      | 0.9                  |       |

| +                   | Data setup time                                                | $f_{SCL} \le 100 kHz$                                             | 250                                    |      |                      |       |

| t <sub>SU;DAT</sub> |                                                                | f <sub>SCL</sub> > 100kHz                                         | 100                                    |      |                      |       |

| t                   | Setup time for STOP condition                                  | $f_{SCL} \le 100 kHz$                                             | 4.0                                    |      |                      |       |

| t <sub>su;sто</sub> |                                                                | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                      |       |

| t                   | Bus free time between a STOP and                               | $f_{SCL} \le 100 kHz$                                             | 4.7                                    |      |                      |       |

| t <sub>BUF</sub>    | START condition                                                | f <sub>SCL</sub> > 100kHz                                         | 1.3                                    |      |                      |       |

Notes:

Required only for f<sub>SCL</sub> > 100kHz.

C<sub>b</sub> = Capacitance of one bus line in pF.

3.  $f_{PER}$  = Peripheral clock frequency.

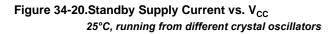

#### 34.1.1.5 Standby Mode Supply Current

Figure 34-19.Standby Supply Current vs. V<sub>CC</sub> Standby, f<sub>SYS</sub> = 1MHz

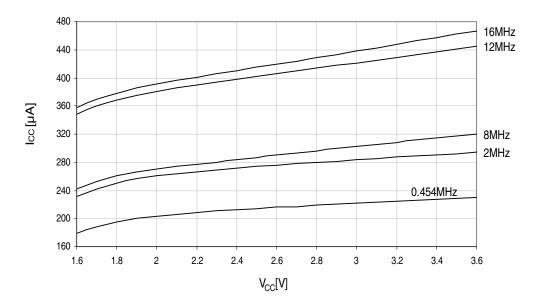

Figure 34-31. I/O Pin Output Voltage vs. Sink Current

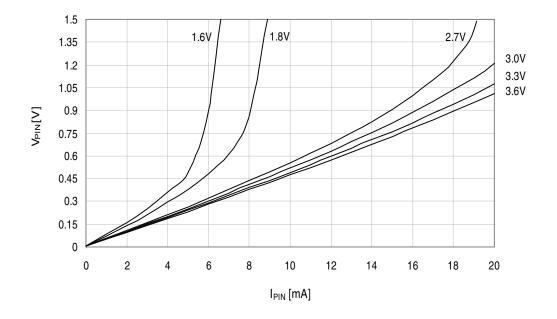

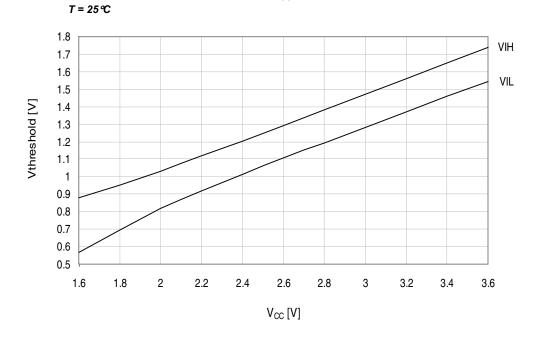

### 34.1.2.3 Thresholds and Hysteresis

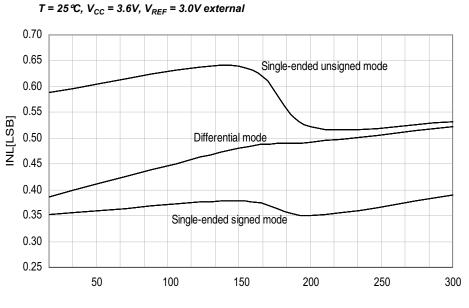

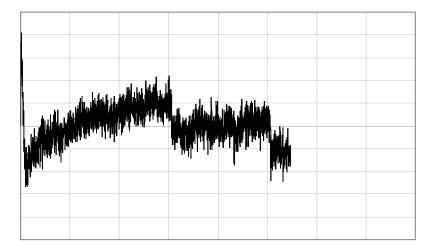

Figure 34-37. INL Error vs. Sample Rate

ADC sample rate [ksps]

Figure 34-38. INL Error vs. Input Code

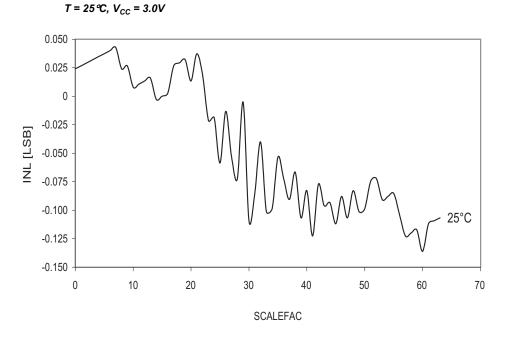

Figure 34-53. Voltage Scaler INL vs. SCALEFAC

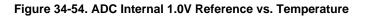

### 34.1.5 Internal 1.0V Reference Characteristics

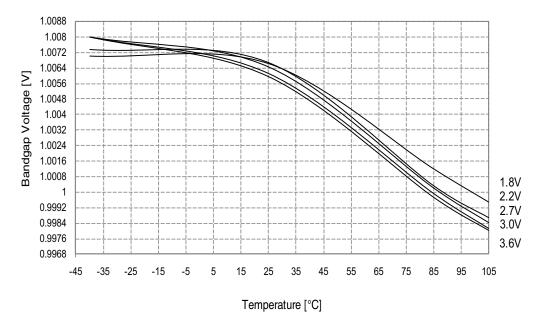

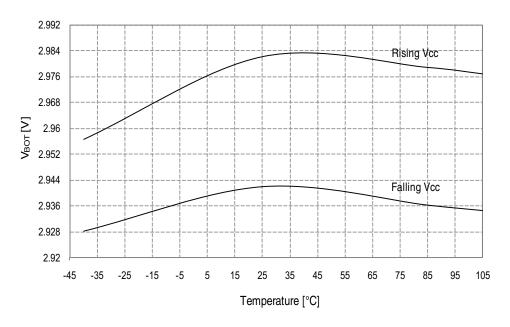

Figure 34-55. BOD Thresholds vs. Temperature BOD level = 1.6V

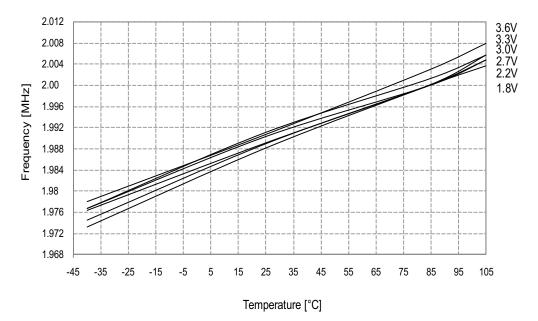

#### 34.1.9.4 32MHz Internal Oscillator

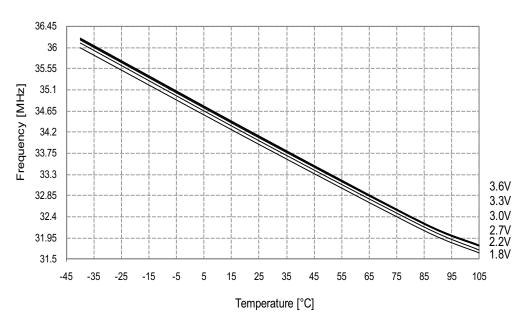

Figure 34-71. 32MHz Internal Oscillator Frequency vs. Temperature DFLL disabled

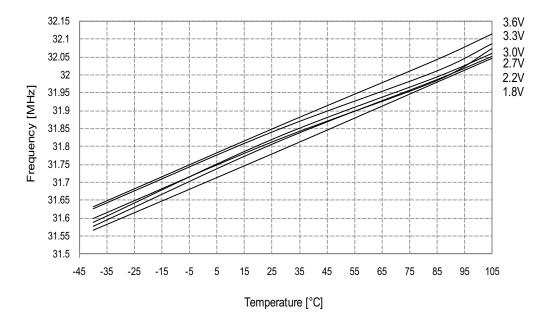

Figure 34-72. 32MHz Internal Oscillator Frequency vs. Temperature DFLL enabled, from the 32.768kHz internal oscillator

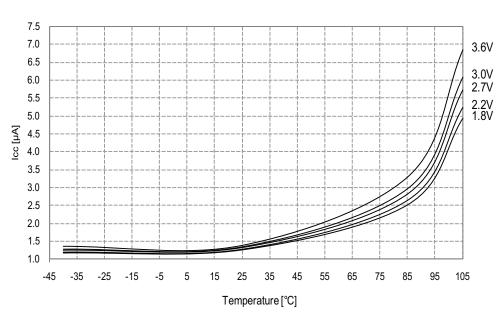

### Figure 34-96. Power-down Mode Supply Current vs. Temperature Watchdog and sampled BOD enabled and running from internal ULP oscillator

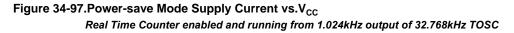

#### 34.2.1.4 Power-save Mode Supply Current

#### 34.2.2 I/O Pin Characteristics

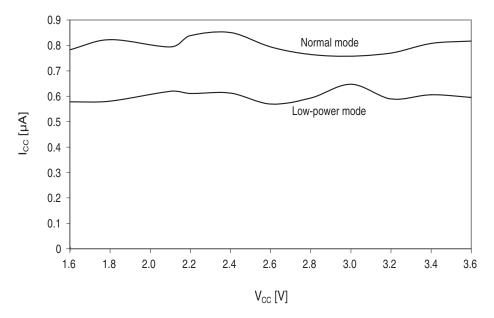

### 34.2.2.1 Pull-up

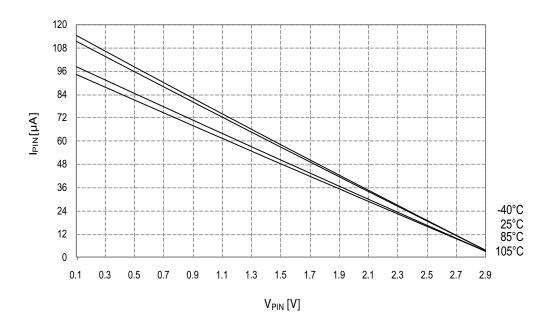

Figure 34-100. I/O Pin Pull-up Resistor Current vs. Input Voltage

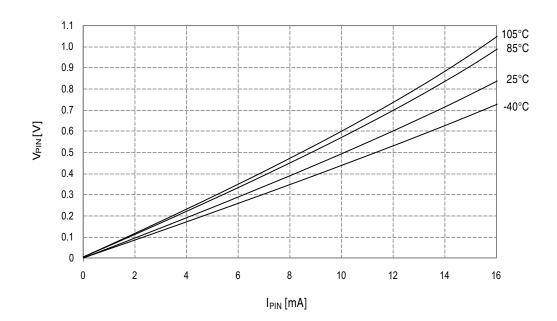

Figure 34-108. I/O Pin Output Voltage vs. Sink Current  $V_{cc} = 3.0V$

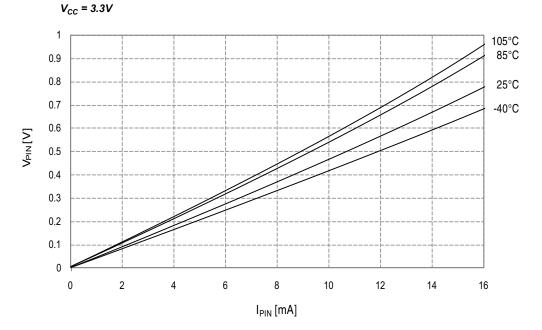

Figure 34-109. I/O Pin Output Voltage vs. Sink Current

Figure 34-116. INL Error vs. Sample Rate

ADC sample rate [ksps]

Figure 34-117. INL Error vs. Input Code

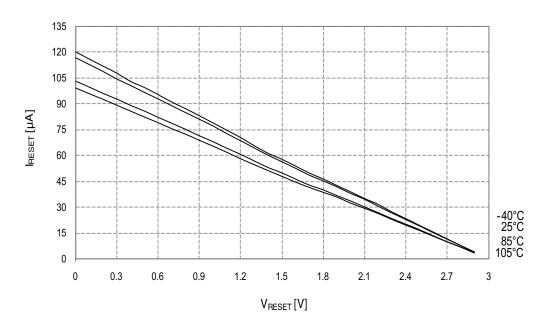

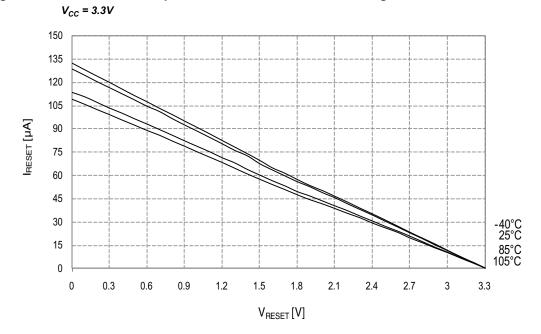

Figure 34-138. Reset Pin Pull-up Resistor Current vs. Reset Pin Voltage  $V_{CC} = 3.0V$

Figure 34-139. Reset Pin Pull-up Resistor Current vs. Reset Pin Voltage

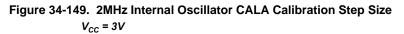

Figure 34-148. 2MHz Internal Oscillator Frequency vs. Temperature DFLL enabled, from the 32.768kHz internal oscillator