#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8/16-Bit                                                                 |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 34                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 1K x 8                                                                   |

| RAM Size                   | 4K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega32c4-mn |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

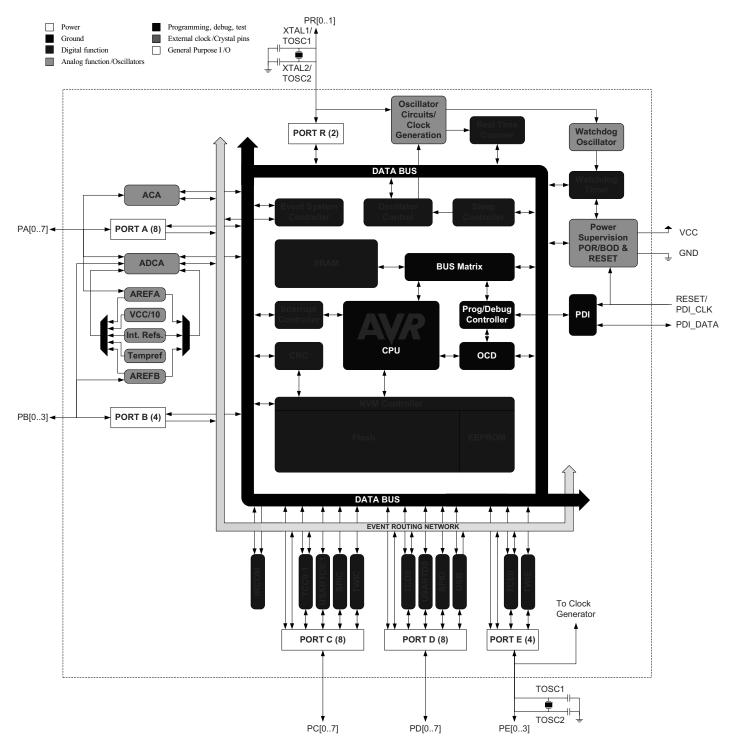

## 3.1 Block Diagram

### Figure 3-1. XMEGA C4 Block Diagram

Six of the 32 registers can be used as three 16-bit address register pointers for data space addressing, enabling efficient address calculations. One of these address pointers can also be used as an address pointer for lookup tables in flash program memory.

## 25. CRC – Cyclic Redundancy Check Generator

## 25.1 Features

- Cyclic redundancy check (CRC) generation and checking for

- Communication data

- Program or data in flash memory

- Data in SRAM and I/O memory space

- Integrated with flash memory, and CPU

- Automatic CRC of the complete or a selectable range of the flash memory

- CPU can load data to the CRC generator through the I/O interface

- CRC polynomial software selectable to

- CRC-16 (CRC-CCITT)

- CRC-32 (IEEE 802.3)

- Zero remainder detection

### 25.2 Overview

A cyclic redundancy check (CRC) is an error detection technique test algorithm used to find accidental errors in data, and it is commonly used to determine the correctness of a data transmission, and data present in the data and program memories. A CRC takes a data stream or a block of data as input and generates a 16- or 32-bit output that can be appended to the data and used as a checksum. When the same data are later received or read, the device or application repeats the calculation. If the new CRC result does not match the one calculated earlier, the block contains a data error. The application will then detect this and may take a corrective action, such as requesting the data to be sent again or simply not using the incorrect data.

Typically, an n-bit CRC applied to a data block of arbitrary length will detect any single error burst not longer than n bits (any single alteration that spans no more than n bits of the data), and will detect the fraction 1-2<sup>-n</sup> of all longer error bursts. The CRC module in Atmel AVR XMEGA devices supports two commonly used CRC polynomials; CRC-16 (CRC-CCITT) and CRC-32 (IEEE 802.3).

### • CRC-16:

Polynomial:  $x^{16}+x^{12}+x^5+1$

Hex value: 0x1021

• CRC-32:

Polynomial:  $x^{32}+x^{26}+x^{23}+x^{22}+x^{16}+x^{12}+x^{11}+x^{10}+x^8+x^7+x^5+x^4+x^2+x+1$ Hex value: 0x04C11DB7

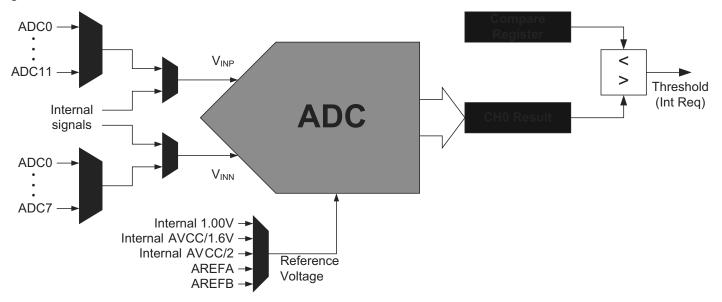

# 26. ADC – 12-bit Analog to Digital Converter

## 26.1 Features

- One Analog to Digital Converter (ADC)

- 12-bit resolution

- Up to 300 thousand samples per second

- Down to 2.3µs conversion time with 8-bit resolution

- Down to 3.35µs conversion time with 12-bit resolution

- Differential and single-ended input

- 12 single-ended inputs

- 12x4 differential inputs without gain

- 8x4 differential input with gain

- Built-in differential gain stage

- 1/2x, 1x, 2x, 4x, 8x, 16x, 32x, and 64x gain options

- Single, continuous and scan conversion options

- Three internal inputs

- Internal temperature sensor

- AV<sub>CC</sub> voltage divided by 10

- 1.1V bandgap voltage

- Internal and external reference options

- Compare function for accurate monitoring of user defined thresholds

- Optional event triggered conversion for accurate timing

- Optional interrupt/event on compare result

### 26.2 Overview

The ADC converts analog signals to digital values. The ADC has 12-bit resolution and is capable of converting up to 300 thousand samples per second (ksps). The input selection is flexible, and both single-ended and differential measurements can be done. For differential measurements, an optional gain stage is available to increase the dynamic range. In addition, several internal signal inputs are available. The ADC can provide both signed and unsigned results.

The ADC measurements can either be started by application software or an incoming event from another peripheral in the device. The ADC measurements can be started with predictable timing, and without software intervention.

Both internal and external reference voltages can be used. An integrated temperature sensor is available for use with the ADC. The  $AV_{CC}/10$  and the bandgap voltage can also be measured by the ADC.

The ADC has a compare function for accurate monitoring of user defined thresholds with minimum software intervention required.

Figure 26-1. ADC Overview

The ADC may be configured for 8- or 12-bit result, reducing the minimum conversion time (propagation delay) from 3.35µs for 12-bit to 2.3µs for 8-bit result.

ADC conversion results are provided left- or right adjusted with optional '1' or '0' padding. This eases calculation when the result is represented as a signed integer (signed 16-bit number).

PORTA has one ADC. Notation of this peripheral is ADCA.

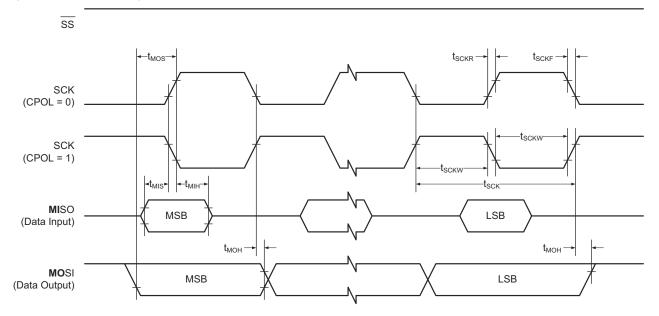

| SCK | Serial Clock for SPI |

|-----|----------------------|

| D-  | Data- for USB        |

| D+  | Data+ for USB        |

## 29.1.6 Oscillators, Clock, and Event

| TOSCn  | Timer Oscillator pin n            |

|--------|-----------------------------------|

| XTALn  | Input/Output for Oscillator pin n |

| CLKOUT | Peripheral Clock Output           |

| EVOUT  | Event Channel Output              |

| RTCOUT | RTC Clock Source Output           |

## 29.1.7 Debug/System Functions

| RESET    | Reset pin                             |

|----------|---------------------------------------|

| PDI_CLK  | Program and Debug Interface Clock pin |

| PDI_DATA | Program and Debug Interface Data pin  |

| Mnemonics | cs Operands Description Op |                                                     | Oper                                         | ation        |                     | Flags | #Clocks             |

|-----------|----------------------------|-----------------------------------------------------|----------------------------------------------|--------------|---------------------|-------|---------------------|

| LDS       | Rd, k                      | Load Direct from data space                         | Rd                                           | ←            | (k)                 | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, X                      | Load Indirect                                       | Rd                                           | ←            | (X)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, X+                     | Load Indirect and Post-Increment                    | Rd<br>X                                      | ←<br>←       | (X)<br>X + 1        | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -X                     | Load Indirect and Pre-Decrement                     | $X \leftarrow X - 1,$<br>Rd $\leftarrow (X)$ | ←<br>←       | X - 1<br>(X)        | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, Y                      | Load Indirect                                       | $Rd \gets (Y)$                               | ~            | (Y)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, Y+                     | Load Indirect and Post-Increment                    | Rd<br>Y                                      | ←<br>←       | (Y)<br>Y + 1        | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -Y                     | Load Indirect and Pre-Decrement                     | Y<br>Rd                                      | $\leftarrow$ | Y - 1<br>(Y)        | None  | 2 <sup>(1)(2)</sup> |

| LDD       | Rd, Y+q                    | Load Indirect with Displacement                     | Rd                                           | ~            | (Y + q)             | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, Z                      | Load Indirect                                       | Rd                                           | ←            | (Z)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, Z+                     | Load Indirect and Post-Increment                    | Rd<br>Z                                      | ←<br>←       | (Z),<br>Z+1         | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -Z                     | Load Indirect and Pre-Decrement                     | Z<br>Rd                                      | ←<br>←       | Z - 1,<br>(Z)       | None  | 2 <sup>(1)(2)</sup> |

| LDD       | Rd, Z+q                    | Load Indirect with Displacement                     | Rd                                           | ~            | (Z + q)             | None  | 2 <sup>(1)(2)</sup> |

| STS       | k, Rr                      | Store Direct to Data Space                          | (k)                                          | ←            | Rd                  | None  | 2 <sup>(1)</sup>    |

| ST        | X, Rr                      | Store Indirect                                      | (X)                                          | ←            | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | X+, Rr                     | Store Indirect and Post-Increment                   | (X)<br>X                                     | ←<br>←       | Rr,<br>X + 1        | None  | 1 <sup>(1)</sup>    |

| ST        | -X, Rr                     | Store Indirect and Pre-Decrement                    | X<br>(X)                                     | ←<br>←       | X - 1,<br>Rr        | None  | 2 <sup>(1)</sup>    |

| ST        | Y, Rr                      | Store Indirect                                      | (Y)                                          | ←            | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | Y+, Rr                     | Store Indirect and Post-Increment                   | (Y)<br>Y                                     | ←<br>←       | Rr,<br>Y + 1        | None  | 1 <sup>(1)</sup>    |

| ST        | -Y, Rr                     | Store Indirect and Pre-Decrement                    | Y<br>(Y)                                     | ←<br>←       | Y - 1,<br>Rr        | None  | 2 <sup>(1)</sup>    |

| STD       | Y+q, Rr                    | Store Indirect with Displacement                    | (Y + q)                                      | ←            | Rr                  | None  | 2(1)                |

| ST        | Z, Rr                      | Store Indirect                                      | (Z)                                          | ←            | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | Z+, Rr                     | Store Indirect and Post-Increment                   | (Z)<br>Z                                     | ←<br>←       | Rr<br>Z + 1         | None  | 1 <sup>(1)</sup>    |

| ST        | -Z, Rr                     | Store Indirect and Pre-Decrement                    | Z                                            | ←            | Z - 1               | None  | 2(1)                |

| STD       | Z+q,Rr                     | Store Indirect with Displacement                    | (Z + q)                                      | ←            | Rr                  | None  | 2 <sup>(1)</sup>    |

| LPM       |                            | Load Program Memory                                 | R0                                           | ~            | (Z)                 | None  | 3                   |

| LPM       | Rd, Z                      | Load Program Memory                                 | Rd                                           | ←            | (Z)                 | None  | 3                   |

| LPM       | Rd, Z+                     | Load Program Memory and Post-Increment              | Rd<br>Z                                      | ←<br>←       | (Z),<br>Z + 1       | None  | 3                   |

| ELPM      |                            | Extended Load Program Memory                        | R0                                           | ~            | (RAMPZ:Z)           | None  | 3                   |

| ELPM      | Rd, Z                      | Extended Load Program Memory                        | Rd                                           | ~            | (RAMPZ:Z)           | None  | 3                   |

| ELPM      | Rd, Z+                     | Extended Load Program Memory and Post-<br>Increment | Rd<br>Z                                      | ←<br>←       | (RAMPZ:Z),<br>Z + 1 | None  | 3                   |

| SPM       |                            | Store Program Memory                                | (RAMPZ:Z)                                    | ←            | R1:R0               | None  | -                   |

#### 33.1.5 I/O Pin Characteristics

The I/O pins complies with the JEDEC LVTTL and LVCMOS specification and the high- and low-level input and output voltage limits reflect or exceed this specification.

| Symbol                                                             | Parameter                     | Con                          | Min.                   | Тур.                | Max.  | Units                |    |

|--------------------------------------------------------------------|-------------------------------|------------------------------|------------------------|---------------------|-------|----------------------|----|

| I <sub>OH</sub> <sup>(1)</sup> /<br>I <sub>OL</sub> <sup>(2)</sup> | I/O pin source/sink current   |                              |                        | -20                 |       | 20                   | mA |

| V                                                                  | High level input voltage      | V <sub>CC</sub> = 2.4 - 3.6V |                        | 0.7*Vcc             |       | V <sub>CC</sub> +0.5 |    |

| V <sub>IH</sub>                                                    | riigii level liiput voltage   | V <sub>CC</sub> = 1.6 - 2.4V |                        | 0.8*V <sub>CC</sub> |       | V <sub>CC</sub> +0.5 |    |

| V <sub>IL</sub>                                                    | Low level input voltage       | V <sub>CC</sub> = 2.4- 3.6V  |                        | -0.5                |       | 0.3*V <sub>CC</sub>  |    |

| ۷IL                                                                | Low level input voltage       | V <sub>CC</sub> = 1.6 - 2.4V |                        | -0.5                |       | 0.2*V <sub>CC</sub>  |    |

|                                                                    | High level output voltage     | $V_{CC} = 3.3V$              | I <sub>OH</sub> = -4mA | 2.6                 | 2.9   |                      | V  |

| V <sub>OH</sub>                                                    |                               | $V_{CC} = 3.0V$              | I <sub>OH</sub> = -3mA | 2.1                 | 2.7   |                      | V  |

|                                                                    |                               | $V_{CC} = 1.8V$              | I <sub>OH</sub> = -1mA | 1.4                 | 1.6   |                      |    |

|                                                                    |                               | $V_{CC} = 3.3V$              | I <sub>OL</sub> = 8mA  |                     | 0.4   | 0.76                 |    |

| V <sub>OL</sub>                                                    | Low level output voltage      | $V_{CC} = 3.0V$              | $I_{OL} = 5mA$         |                     | 0.3   | 0.64                 |    |

|                                                                    |                               | $V_{\rm CC} = 1.8V$          | I <sub>OL</sub> = 3mA  |                     | 0.2   | 0.46                 |    |

| I <sub>IN</sub>                                                    | Input leakage current I/O pin | T = 25°C                     |                        |                     | <0.01 | 1                    | μA |

| R <sub>P</sub>                                                     | Pull/buss keeper resistor     |                              |                        |                     | 25    |                      | kΩ |

Notes:

1. The sum of all I<sub>OH</sub> for PORTA and PORTB must not exceed 100mA. The sum of all I<sub>OH</sub> for PORTC, PORTD, and PORTE must for each port not exceed 200mA. The sum of all I<sub>OH</sub> for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all I<sub>OL</sub> for pins PF[6-7] on PORTF, PORTR, and PDI must not exceed 100mA.

The sum of all  $I_{OL}$  for PORTC, PORTD, and PORTE must not exceed 100mA. The sum of all  $I_{OL}$  for PORTC, PORTD, and PORTE must for each port not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[0-5] on PORTF, PORTR, and PDI must not exceed 100mA. 2.

#### Table 33-10. Accuracy Characteristics

| Symbol             | Parameter                   | Co                            | Min.                            | Тур. | Max. | Units |      |

|--------------------|-----------------------------|-------------------------------|---------------------------------|------|------|-------|------|

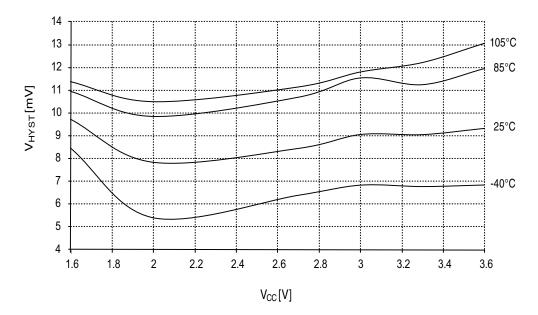

|                    | Resolution                  | 12-bit resolution             | Differential                    | 8    | 12   | 12    |      |

| RES                |                             |                               | Single ended signed             | 7    | 11   | 11    | Bits |

|                    |                             |                               | Single ended unsigned           | 8    | 12   | 12    |      |

|                    |                             |                               | 16ksps, V <sub>REF</sub> = 3V   |      | 0.5  | 1     | -    |

|                    |                             | Differential mode             | 16ksps, all V <sub>REF</sub>    |      | 0.8  | 2     |      |

| INL <sup>(1)</sup> | late and a condition on the | Differential mode             | 300ksps, $V_{REF} = 3V$         |      | 0.6  | 1     |      |

| IINL <sup>()</sup> | Integral non-linearity      |                               | 300ksps, all V <sub>REF</sub>   |      | 1    | 2     |      |

|                    |                             | Single ended                  | 16ksps, V <sub>REF</sub> = 3.0V |      | 0.5  | 1     |      |

|                    |                             | unsigned mode                 | 16ksps, all V <sub>REF</sub>    |      | 1.3  | 2     | lah  |

|                    |                             |                               | 16ksps, V <sub>REF</sub> = 3V   |      | 0.3  | 1     | lsb  |

|                    |                             | Differential mode             | 16ksps, all V <sub>REF</sub>    |      | 0.5  | 1     |      |

| DNL <sup>(1)</sup> | Differential non-linearity  | Differential mode             | 300ksps, $V_{REF} = 3V$         |      | 0.35 | 1     |      |

| DINL               |                             |                               | 300ksps, all V <sub>REF</sub>   |      | 0.5  | 1     |      |

|                    |                             | Single ended<br>unsigned mode | 16ksps, $V_{REF} = 3.0V$        |      | 0.6  | 1     |      |

|                    |                             |                               | 16ksps, all V <sub>REF</sub>    |      | 0.6  | 1     |      |

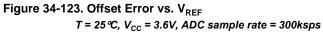

|                    |                             | Differential mode             |                                 |      | 8    |       | mV   |

|                    | Offset Error                |                               | Temperature drift               |      | 0.01 |       | mV/K |

|                    |                             |                               | Operating voltage drift         |      | 0.25 |       | mV/V |

|                    |                             |                               | External reference              |      | -5   |       |      |

|                    |                             |                               | AV <sub>CC</sub> /1.6           |      | -5   |       | mV   |

|                    | Gain Error                  | Differential mode             | AV <sub>CC</sub> /2.0           |      | -6   |       |      |

|                    | Gain Endi                   | Differential mode             | Bandgap                         |      | ±10  |       |      |

|                    |                             |                               | Temperature drift               |      | 0.02 |       | mV/K |

|                    |                             |                               | Operating voltage drift         |      | 2    |       | mV/V |

|                    |                             |                               | External reference              |      | -8   |       |      |

|                    |                             |                               | AV <sub>CC</sub> /1.6           |      | -8   |       | mV   |

|                    | Gain Error                  | Single ended                  | AV <sub>CC</sub> /2.0           |      | -8   |       | IIIV |

|                    | Gaill EllUI                 | unsigned mode                 | Bandgap                         |      | ±10  |       |      |

|                    |                             |                               | Temperature drift               |      | 0.03 |       | mV/K |

|                    |                             |                               | Operating voltage drift         |      | 2    |       | mV/V |

Notes: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% input voltage range.

2. Unless otherwise noted all linearity, offset and gain error numbers are valid under the condition that external VREF is used.

#### 33.2.5 I/O Pin Characteristics

The I/O pins complies with the JEDEC LVTTL and LVCMOS specification and the high- and low level input and output voltage limits reflect or exceed this specification.

#### Table 33-36. I/O Pin Characteristics

| Symbol                                                             | Parameter                     | Condition                    |                        | Min.                | Тур.  | Max.                 | Units |

|--------------------------------------------------------------------|-------------------------------|------------------------------|------------------------|---------------------|-------|----------------------|-------|

| I <sub>OH</sub> <sup>(1)</sup> /<br>I <sub>OL</sub> <sup>(2)</sup> | I/O pin source/sink current   |                              |                        | -20                 |       | 20                   | mA    |

| V <sub>IH</sub>                                                    | High level input voltage      | V <sub>CC</sub> = 2.4 - 3.6V |                        | 0.7*Vcc             |       | V <sub>CC</sub> +0.5 |       |

| VIH                                                                | riigii level liiput voltage   | V <sub>CC</sub> = 1.6 - 2.4V |                        | 0.8*V <sub>CC</sub> |       | V <sub>CC</sub> +0.5 |       |

| V <sub>IL</sub>                                                    | Low level input voltage       | V <sub>CC</sub> = 2.4- 3.6V  |                        | -0.5                |       | 0.3*V <sub>CC</sub>  |       |

| ۷IL                                                                | Low level input voltage       | V <sub>CC</sub> = 1.6 - 2.4V |                        | -0.5                |       | 0.2*V <sub>CC</sub>  |       |

|                                                                    | High level output voltage     | $V_{CC} = 3.3V$              | I <sub>OH</sub> = -4mA | 2.6                 | 2.9   |                      | V     |

| V <sub>OH</sub>                                                    |                               | $V_{CC} = 3.0V$              | I <sub>OH</sub> = -3mA | 2.1                 | 2.7   |                      | v     |

|                                                                    |                               | V <sub>CC</sub> = 1.8V       | I <sub>OH</sub> = -1mA | 1.4                 | 1.6   |                      |       |

|                                                                    |                               | $V_{CC} = 3.3V$              | I <sub>OL</sub> = 8mA  |                     | 0.4   | 0.76                 |       |

| V <sub>OL</sub>                                                    | Low level output voltage      | $V_{CC} = 3.0 V$             | I <sub>OL</sub> = 5mA  |                     | 0.3   | 0.64                 |       |

|                                                                    |                               | V <sub>CC</sub> = 1.8V       | I <sub>OL</sub> = 3mA  |                     | 0.2   | 0.46                 |       |

| I <sub>IN</sub>                                                    | Input leakage current I/O pin | T = 25°C                     |                        |                     | <0.01 | 1                    | μA    |

| R <sub>P</sub>                                                     | Pull/buss keeper resistor     |                              |                        |                     | 25    |                      | kΩ    |

Notes:

1. The sum of all I<sub>OH</sub> for PORTA and PORTB must not exceed 100mA. The sum of all I<sub>OH</sub> for PORTC, PORTD, and PORTE must for each port not exceed 200mA. The sum of all I<sub>OH</sub> for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all I<sub>OL</sub> for pins PF[6-7] on PORTF, PORTR, and PDI must not exceed 100mA.

The sum of all  $I_{OL}$  for PORTA and PORTB must not exceed 100mA. The sum of all  $I_{OL}$  for PORTC, PORTD, and PORTE must for each port not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[0-5] on PORTF, PORTR, and PDI must not exceed 100mA. 2.

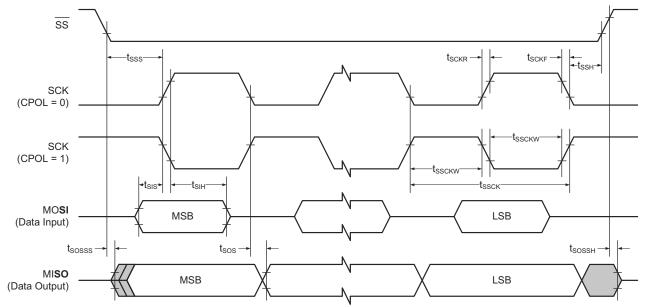

#### 33.2.14 SPI Characteristics

#### Table 33-58. Two-wire Interface Characteristics

| Symbol              | Parameter                                                      | Condition                                                         | Min.                                   | Тур. | Max.                 | Units |

|---------------------|----------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------|------|----------------------|-------|

| V <sub>IH</sub>     | Input high voltage                                             |                                                                   | 0.7*V <sub>CC</sub>                    |      | V <sub>CC</sub> +0.5 |       |

| V <sub>IL</sub>     | Input low voltage                                              |                                                                   | -0.5                                   |      | 0.3*V <sub>CC</sub>  | V     |

| V <sub>hys</sub>    | Hysteresis of Schmitt trigger inputs                           |                                                                   | 0.05*V <sub>CC</sub> <sup>(1)</sup>    |      |                      | V     |

| V <sub>OL</sub>     | Output low voltage                                             | 3mA, sink current                                                 | 0                                      |      | 0.4                  |       |

| t <sub>r</sub>      | Rise time for both SDA and SCL                                 |                                                                   | 20+0.1C <sub>b</sub> <sup>(1)(2)</sup> |      | 300                  |       |

| t <sub>of</sub>     | Output fall time from $V_{\text{IHmin}}$ to $V_{\text{ILmax}}$ | $10pF < C_b < 400pF^{(2)}$                                        | 20+0.1C <sub>b</sub> <sup>(1)(2)</sup> |      | 250                  | ns    |

| t <sub>SP</sub>     | Spikes suppressed by input filter                              |                                                                   | 0                                      |      | 50                   |       |

| I <sub>I</sub>      | Input current for each I/O Pin                                 | $0.1V_{CC} < V_{I} < 0.9V_{CC}$                                   | -10                                    |      | 10                   | μA    |

| CI                  | Capacitance for each I/O Pin                                   |                                                                   |                                        |      | 10                   | pF    |

| f <sub>SCL</sub>    | SCL clock frequency                                            | f <sub>PER</sub> <sup>(3)</sup> >max(10f <sub>SCL</sub> , 250kHz) | 0                                      |      | 400                  | kHz   |

| -                   | Value of pull-up resistor                                      | $f_{SCL} \le 100 kHz$                                             | $V_{CC} - 0.4V$                        |      | $\frac{100ns}{C_b}$  |       |

| R <sub>P</sub>      |                                                                | f <sub>SCL</sub> > 100kHz                                         | $\frac{V_{CC} - 0.4V}{3mA}$            |      | $\frac{300ns}{C_b}$  | Ω     |

|                     |                                                                | $f_{SCL} \le 100 kHz$                                             | 4.0                                    |      |                      |       |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition                           | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                      |       |

|                     | Low paried of COL clash                                        | $f_{SCL} \le 100 kHz$                                             | 4.7                                    |      |                      |       |

| t <sub>LOW</sub>    | Low period of SCL clock                                        | f <sub>SCL</sub> > 100kHz                                         | 1.3                                    |      |                      |       |

| 4                   | Link period of COL alask                                       | $f_{SCL} \leq 100 kHz$                                            | 4.0                                    |      |                      |       |

| t <sub>HIGH</sub>   | High period of SCL clock                                       | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                      |       |

|                     | Set-up time for a repeated START                               | $f_{SCL} \leq 100 kHz$                                            | 4.7                                    |      |                      |       |

| t <sub>SU;STA</sub> | condition                                                      | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                      |       |

|                     | Dete held fine                                                 | $f_{SCL} \leq 100 kHz$                                            | 0                                      |      | 3.45                 | μs    |

| t <sub>HD;DAT</sub> | Data hold time                                                 | f <sub>SCL</sub> > 100kHz                                         | 0                                      |      | 0.9                  |       |

|                     |                                                                | $f_{SCL} \le 100 kHz$                                             | 250                                    |      |                      |       |

| t <sub>SU;DAT</sub> | Data setup time                                                | f <sub>SCL</sub> > 100kHz                                         | 100                                    |      |                      |       |

| +                   | Sotup time for STOP condition                                  | $f_{SCL} \leq 100 kHz$                                            | 4.0                                    |      |                      |       |

| t <sub>su;sto</sub> | Setup time for STOP condition                                  | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                      |       |

|                     | Bus free time between a STOP and                               | $f_{SCL} \leq 100 kHz$                                            | 4.7                                    |      |                      |       |

| t <sub>BUF</sub>    | START condition                                                | f <sub>SCL</sub> > 100kHz                                         | 1.3                                    |      |                      |       |

Notes:

Required only for f<sub>SCL</sub> > 100kHz.

C<sub>b</sub> = Capacitance of one bus line in pF.

3.  $f_{PER}$  = Peripheral clock frequency.

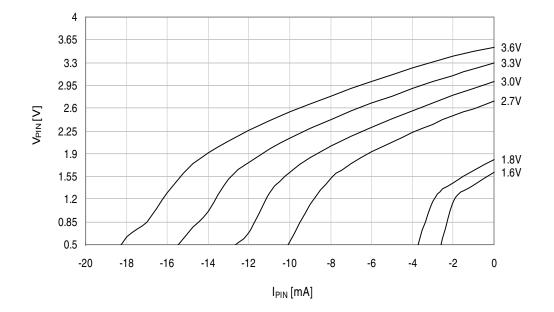

Figure 34-27. I/O Pin Output Voltage vs. Source Current

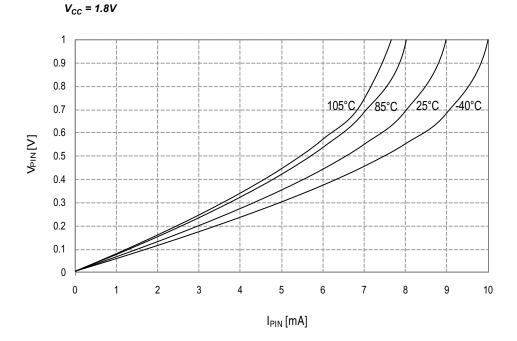

Figure 34-28. I/O Pin Output Voltage vs. Sink Current

#### 34.1.4 Analog Comparator Characteristics

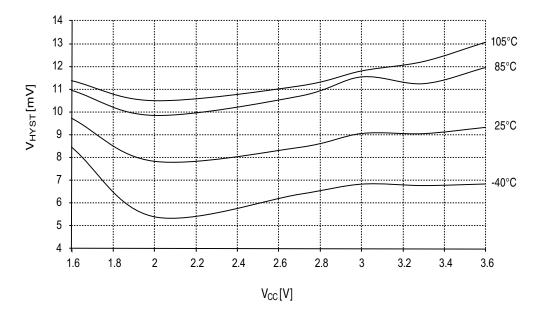

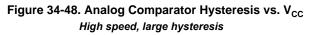

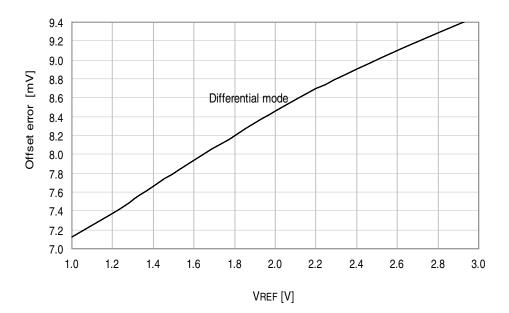

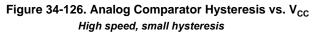

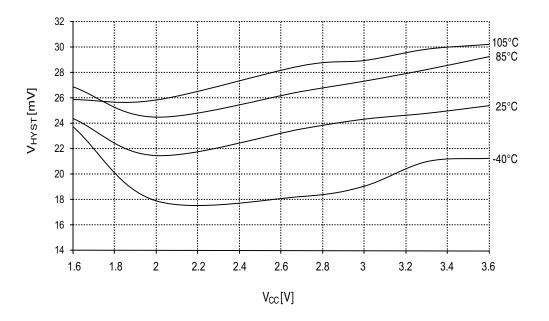

Figure 34-47. Analog Comparator Hysteresis vs. V<sub>CC</sub> High speed, small hysteresis

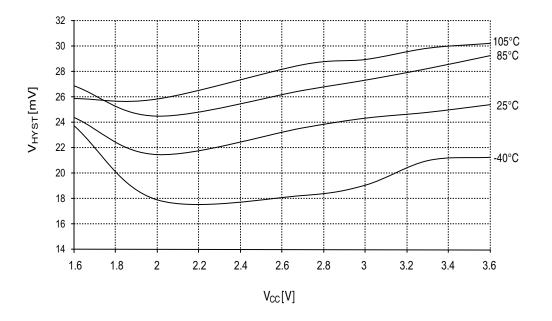

#### 34.1.10 Two-Wire Interface Characteristics

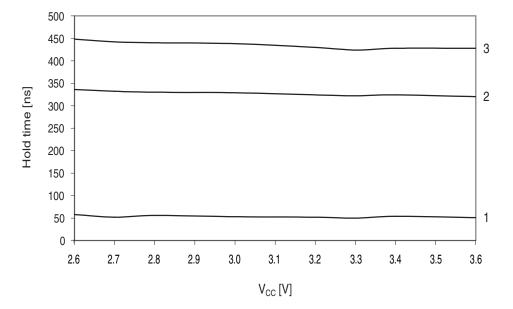

Figure 34-78. SDA Hold Time vs. Supply Voltage

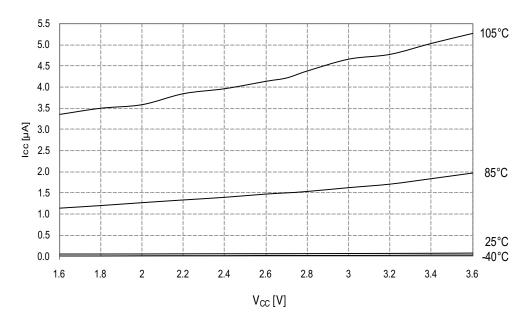

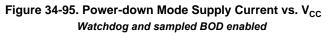

#### 34.2.1.3 Power-down Mode Supply Current

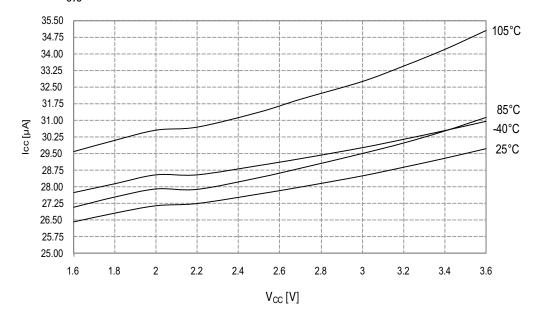

Figure 34-94. Power-down Mode Supply Current vs. V<sub>CC</sub> All functions disabled

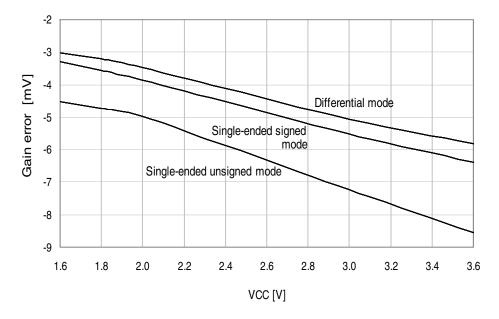

Figure 34-122. Gain Error vs. V<sub>CC</sub>

$T = 25 \,$ °C,  $V_{REF} = external 1.0V$ , ADC sample rate = 300ksps

#### 34.2.4 Analog Comparator Characteristics

#### 34.2.9 Oscillator Characteristics

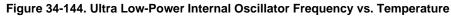

34.2.9.1 Ultra Low-Power Internal Oscillator

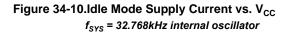

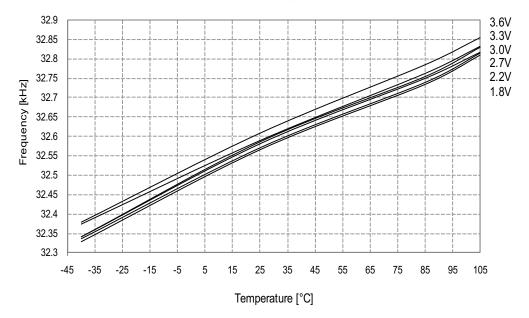

#### 34.2.9.2 32.768kHz Internal Oscillator

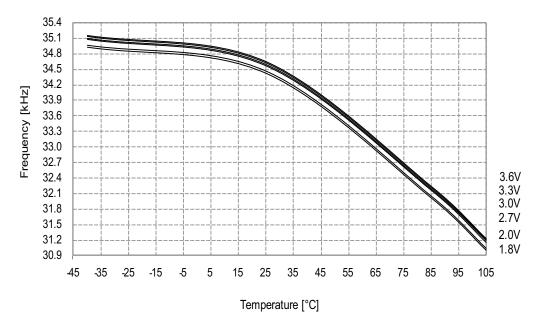

Figure 34-145. 32.768kHz Internal Oscillator Frequency vs. Temperature