Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 624                                                       |

| Number of Logic Elements/Cells | 4992                                                      |

| Total RAM Bits                 | 49152                                                     |

| Number of I/O                  | 186                                                       |

| Number of Gates                | 257000                                                    |

| Voltage - Supply               | 2.375V ~ 2.625V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 70°C (TA)                                           |

| Package / Case                 | 256-BGA                                                   |

| Supplier Device Package        | 256-FBGA (17x17)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1k100fc256-3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 5 shows ACEX 1K device performance for more complex designs. These designs are available as Altera MegaCore $^{\rm TM}$  functions.

| Table 5. ACEX 1K Device Performance for Compl               | ex Design | s    |             |          |       |

|-------------------------------------------------------------|-----------|------|-------------|----------|-------|

| Application                                                 | LEs       |      | Perform     | ance     |       |

|                                                             | Used      |      | Speed Grade | <b>!</b> | Units |

|                                                             | ·         | -1   | -2          | -3       |       |

| 16-bit, 8-tap parallel finite impulse response (FIR) filter | 597       | 192  | 156         | 116      | MSPS  |

| 8-bit, 512-point Fast Fourier transform (FFT)               | 1,854     | 23.4 | 28.7        | 38.9     | μs    |

| function                                                    |           | 113  | 92          | 68       | MHz   |

| a16450 universal asynchronous receiver/transmitter (UART)   | 342       | 36   | 28          | 20.5     | MHz   |

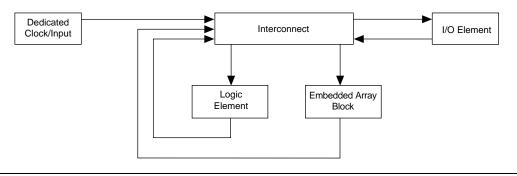

Each ACEX 1K device contains an embedded array and a logic array. The embedded array is used to implement a variety of memory functions or complex logic functions, such as digital signal processing (DSP), wide data-path manipulation, microcontroller applications, and data-transformation functions. The logic array performs the same function as the sea-of-gates in the gate array and is used to implement general logic such as counters, adders, state machines, and multiplexers. The combination of embedded and logic arrays provides the high performance and high density of embedded gate arrays, enabling designers to implement an entire system on a single device.

ACEX 1K devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers EPC16, EPC2, EPC1, and EPC1441 configuration devices, which configure ACEX 1K devices via a serial data stream. Configuration data can also be downloaded from system RAM or via the Altera MasterBlaster $^{\text{TM}}$ , ByteBlasterMV $^{\text{TM}}$ , or BitBlaster $^{\text{TM}}$  download cables. After an ACEX 1K device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Because reconfiguration requires less than 40 ms, real-time changes can be made during system operation.

ACEX 1K devices contain an interface that permits microprocessors to configure ACEX 1K devices serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat an ACEX 1K device as memory and configure it by writing to a virtual memory location, simplifying device reconfiguration.

# **Embedded Array Block**

The EAB is a flexible block of RAM, with registers on the input and output ports, that is used to implement common gate array megafunctions. Because it is large and flexible, the EAB is suitable for functions such as multipliers, vector scalars, and error correction circuits. These functions can be combined in applications such as digital filters and microcontrollers.

Logic functions are implemented by programming the EAB with a read-only pattern during configuration, thereby creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of EABs. The large capacity of EABs enables designers to implement complex functions in a single logic level without the routing delays associated with linked LEs or field-programmable gate array (FPGA) RAM blocks. For example, a single EAB can implement any function with 8 inputs and 16 outputs. Parameterized functions, such as LPM functions, can take advantage of the EAB automatically.

The ACEX 1K enhanced EAB supports dual-port RAM. The dual-port structure is ideal for FIFO buffers with one or two clocks. The ACEX 1K EAB can also support up to 16-bit-wide RAM blocks. The ACEX 1K EAB can act in dual-port or single-port mode. When in dual-port mode, separate clocks may be used for EAB read and write sections, allowing the EAB to be written and read at different rates. It also has separate synchronous clock enable signals for the EAB read and write sections, which allow independent control of these sections.

The EAB can also be used for bidirectional, dual-port memory applications where two ports read or write simultaneously. To implement this type of dual-port memory, two EABs are used to support two simultaneous reads or writes.

Alternatively, one clock and clock enable can be used to control the input registers of the EAB, while a different clock and clock enable control the output registers (see Figure 2).

If necessary, all EABs in a device can be cascaded to form a single RAM block. EABs can be cascaded to form RAM blocks of up to 2,048 words without impacting timing. Altera software automatically combines EABs to meet a designer's RAM specifications.

EABs provide flexible options for driving and controlling clock signals. Different clocks and clock enables can be used for reading and writing to the EAB. Registers can be independently inserted on the data input, EAB output, write address, write enable signals, read address, and read enable signals. The global signals and the EAB local interconnect can drive write-enable, read-enable, and clock-enable signals. The global signals, dedicated clock pins, and EAB local interconnect can drive the EAB clock signals. Because the LEs drive the EAB local interconnect, the LEs can control write-enable, read-enable, clear, clock, and clock-enable signals.

An EAB is fed by a row interconnect and can drive out to row and column interconnects. Each EAB output can drive up to two row channels and up to two column channels; the unused row channel can be driven by other LEs. This feature increases the routing resources available for EAB outputs (see Figures 2 and 4). The column interconnect, which is adjacent to the EAB, has twice as many channels as other columns in the device.

# Logic Array Block

An LAB consists of eight LEs, their associated carry and cascade chains, LAB control signals, and the LAB local interconnect. The LAB provides the coarse-grained structure to the ACEX 1K architecture, facilitating efficient routing with optimum device utilization and high performance. Figure 7 shows the ACEX 1K LAB.

#### **Asynchronous Clear**

The flipflop can be cleared by either LABCTRL1 or LABCTRL2. In this mode, the preset signal is tied to VCC to deactivate it.

## **Asynchronous Preset**

An asynchronous preset is implemented as an asynchronous load, or with an asynchronous clear. If DATA3 is tied to VCC, asserting LABCTRL1 asynchronously loads a one into the register. Alternatively, the Altera software can provide preset control by using the clear and inverting the register's input and output. Inversion control is available for the inputs to both LEs and IOEs. Therefore, if a register is preset by only one of the two LABCTRL signals, the DATA3 input is not needed and can be used for one of the LE operating modes.

#### **Asynchronous Preset & Clear**

When implementing asynchronous clear and preset, LABCTRL1 controls the preset, and LABCTRL2 controls the clear. DATA3 is tied to VCC, so that asserting LABCTRL1 asynchronously loads a one into the register, effectively presetting the register. Asserting LABCTRL2 clears the register.

## **Asynchronous Load with Clear**

When implementing an asynchronous load in conjunction with the clear, LABCTRL1 implements the asynchronous load of DATA3 by controlling the register preset and clear. LABCTRL2 implements the clear by controlling the register clear; LABCTRL2 does not have to feed the preset circuits.

#### **Asynchronous Load with Preset**

When implementing an asynchronous load in conjunction with preset, the Altera software provides preset control by using the clear and inverting the input and output of the register. Asserting LABCTRL2 presets the register, while asserting LABCTRL1 loads the register. The Altera software inverts the signal that drives DATA3 to account for the inversion of the register's output.

#### Asynchronous Load without Preset or Clear

When implementing an asynchronous load without preset or clear, LABCTRL1 implements the asynchronous load of DATA3 by controlling the register preset and clear.

See Figure 17 for details. I/O Element (IOE) IOF IIOF IOE IOE IOE IOE Row LAB LAB See Figure 16 I AR Interconnect Α1 A2 АЗ for details. Column ►To LAB A5 Interconnect ►To LAB A4 IOE IOE LAB LAB I AR Cascade & B1 R2 В3 Carry Chains To LAB B5 ►To LAB B4 IOE IOE IOE

Figure 14. ACEX 1K Interconnect Resources

# I/O Element

An IOE contains a bidirectional I/O buffer and a register that can be used either as an input register for external data that requires a fast setup time or as an output register for data that requires fast clock-to-output performance. In some cases, using an LE register for an input register will result in a faster setup time than using an IOE register. IOEs can be used as input, output, or bidirectional pins. The compiler uses the programmable inversion option to invert signals from the row and column interconnect automatically where appropriate. For bidirectional registered I/O implementation, the output register should be in the IOE and the data input and output enable registers should be LE registers placed adjacent to the bidirectional pin. Figure 15 shows the bidirectional I/O registers.

When dedicated inputs drive non-inverted and inverted peripheral clears, clock enables, and output enables, two signals on the peripheral control bus will be used.

Table 7 lists the sources for each peripheral control signal and shows how the output enable, clock enable, clock, and clear signals share 12 peripheral control signals. Table 7 also shows the rows that can drive global signals.

| Table 7. Peripheral Bus Sources | for ACEX Devices |        |        |         |

|---------------------------------|------------------|--------|--------|---------|

| Peripheral Control Signal       | EP1K10           | EP1K30 | EP1K50 | EP1K100 |

| OE0                             | Row A            | Row A  | Row A  | Row A   |

| OE1                             | Row A            | Row B  | Row B  | Row C   |

| OE2                             | Row B            | Row C  | Row D  | Row E   |

| OE3                             | Row B            | Row D  | Row F  | Row L   |

| OE4                             | Row C            | Row E  | Row H  | Row I   |

| OE5                             | Row C            | Row F  | Row J  | Row K   |

| CLKENAO/CLKO/GLOBALO            | Row A            | Row A  | Row A  | Row F   |

| CLKENA1/OE6/GLOBAL1             | Row A            | Row B  | Row C  | Row D   |

| CLKENA2/CLR0                    | Row B            | Row C  | Row E  | Row B   |

| CLKENA3/OE7/GLOBAL2             | Row B            | Row D  | Row G  | Row H   |

| CLKENA4/CLR1                    | Row C            | Row E  | Row I  | Row J   |

| CLKENA5/CLK1/GLOBAL3            | Row C            | Row F  | Row J  | Row G   |

Signals on the peripheral control bus can also drive the four global signals, referred to as <code>GLOBALO</code> through <code>GLOBALO</code>. An internally generated signal can drive a global signal, providing the same low-skew, low-delay characteristics as a signal driven by an input pin. An LE drives the global signal by driving a row line that drives the peripheral bus which then drives the global signal. This feature is ideal for internally generated clear or clock signals with high fan-out. However, internally driven global signals offer no advantage over the general-purpose interconnect for routing data signals.

The chip-wide output enable pin is an active-high pin that can be used to tri-state all pins on the device. This option can be set in the Altera software. The built-in I/O pin pull-up resistors (which are active during configuration) are active when the chip-wide output enable pin is asserted. The registers in the IOE can also be reset by the chip-wide reset pin.

#### Column-to-IOE Connections

When an IOE is used as an input, it can drive up to two separate column channels. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the column channels. Two IOEs connect to each side of the column channels. Each IOE can be driven by column channels via a multiplexer. The set of column channels is different for each IOE (see Figure 17).

Each IOE is driven by a m-to-1 multiplexer

Column Interconnect

Figure 17. ACEX 1K Column-to-IOE Connections Note (1)

# Note:

The values for m and n are shown in Table 9.

Table 9 lists the ACEX 1K column-to-IOE interconnect resources.

Each IOE can drive two column channels.

| Table 9. ACEX 1K Column-to-IOE Interconnect Resources |                         |                             |  |  |  |  |

|-------------------------------------------------------|-------------------------|-----------------------------|--|--|--|--|

| Device                                                | Channels per Column (n) | Column Channels per Pin (m) |  |  |  |  |

| EP1K10                                                | 24                      | 16                          |  |  |  |  |

| EP1K30                                                | 24                      | 16                          |  |  |  |  |

| EP1K50                                                | 24                      | 16                          |  |  |  |  |

| EP1K100                                               | 24                      | 16                          |  |  |  |  |

For designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to the GCLK1 pin. In the Altera software, the GCLK1 pin can feed both the ClockLock and ClockBoost circuitry in the ACEX 1K device. However, when both circuits are used, the other clock pin cannot be used.

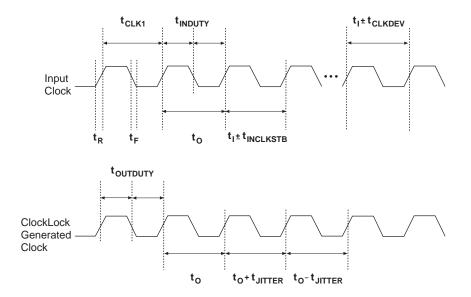

# ClockLock & ClockBoost Timing Parameters

For the ClockLock and ClockBoost circuitry to function properly, the incoming clock must meet certain requirements. If these specifications are not met, the circuitry may not lock onto the incoming clock, which generates an erroneous clock within the device. The clock generated by the ClockLock and ClockBoost circuitry must also meet certain specifications. If the incoming clock meets these requirements during configuration, the ClockLock and ClockBoost circuitry will lock onto the clock during configuration. The circuit will be ready for use immediately after configuration. Figure 19 shows the incoming and generated clock specifications.

Figure 19. Specifications for the Incoming & Generated Clocks Note (1)

#### Note:

(1) The  $\mathbf{t_I}$  parameter refers to the nominal input clock period; the  $\mathbf{t_O}$  parameter refers to the nominal output clock period.

Tables 11 and 12 summarize the ClockLock and ClockBoost parameters for -1 and -2 speed-grade devices, respectively.

| Table 11.             | ClockLock & ClockBoost Parameters for -1                                | Speed-Grade De             | vices |     |                               |      |

|-----------------------|-------------------------------------------------------------------------|----------------------------|-------|-----|-------------------------------|------|

| Symbol                | Parameter                                                               | Condition                  | Min   | Тур | Max                           | Unit |

| $t_R$                 | Input rise time                                                         |                            |       |     | 5                             | ns   |

| $t_{F}$               | Input fall time                                                         |                            |       |     | 5                             | ns   |

| $t_{INDUTY}$          | Input duty cycle                                                        |                            | 40    |     | 60                            | %    |

| f <sub>CLK1</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 1) |                            | 25    |     | 180                           | MHz  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 2) |                            | 16    |     | 90                            | MHz  |

| f <sub>CLKDEV</sub>   | Input deviation from user specification in the Altera software $(1)$    |                            |       |     | 25,000<br><i>(</i> 2 <i>)</i> | PPM  |

| t <sub>INCLKSTB</sub> | Input clock stability (measured between adjacent clocks)                |                            |       |     | 100                           | ps   |

| t <sub>LOCK</sub>     | Time required for ClockLock or ClockBoost to acquire lock (3)           |                            |       |     | 10                            | μs   |

| t <sub>JITTER</sub>   | Jitter on ClockLock or ClockBoost-                                      | t <sub>INCLKSTB</sub> <100 |       |     | 250 (4)                       | ps   |

|                       | generated clock (4)                                                     | $t_{INCLKSTB} < 50$        |       |     | 200 (4)                       | ps   |

| t <sub>OUTDUTY</sub>  | Duty cycle for ClockLock or ClockBoost-<br>generated clock              |                            | 40    | 50  | 60                            | %    |

# PCI Pull-Up Clamping Diode Option

ACEX 1K devices have a pull-up clamping diode on every I/O, dedicated input, and dedicated clock pin. PCI clamping diodes clamp the signal to the  $V_{\rm CCIO}$  value and are required for 3.3-V PCI compliance. Clamping diodes can also be used to limit overshoot in other systems.

Clamping diodes are controlled on a pin-by-pin basis. When  $V_{\rm CCIO}$  is 3.3 V, a pin that has the clamping diode option turned on can be driven by a 2.5-V or 3.3-V signal, but not a 5.0-V signal. When  $V_{\rm CCIO}$  is 2.5 V, a pin that has the clamping diode option turned on can be driven by a 2.5-V signal, but not a 3.3-V or 5.0-V signal. Additionally, a clamping diode can be activated for a subset of pins, which allows a device to bridge between a 3.3-V PCI bus and a 5.0-V device.

#### Slew-Rate Control

The output buffer in each IOE has an adjustable output slew rate that can be configured for low-noise or high-speed performance. A slower slew rate reduces system noise and adds a maximum delay of 4.3 ns. The fast slew rate should be used for speed-critical outputs in systems that are adequately protected against noise. Designers can specify the slew rate pin-by-pin or assign a default slew rate to all pins on a device-wide basis. The slow slew rate setting affects only the falling edge of the output.

# **Open-Drain Output Option**

ACEX 1K devices provide an optional open-drain output (electrically equivalent to open-collector output) for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write enable signals) that can be asserted by any of several devices. It can also provide an additional wired- $\[OR]$  plane.

#### MultiVolt I/O Interface

The ACEX 1K device architecture supports the MultiVolt I/O interface feature, which allows ACEX 1K devices in all packages to interface with systems of differing supply voltages. These devices have one set of  $V_{CC}$  pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All ACEX 1K devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. ACEX 1K devices can also be configured using the JTAG pins through the ByteBlasterMV or BitBlaster download cable, or via hardware that uses the Jam<sup>TM</sup> Standard Test and Programming Language (STAPL), JEDEC standard JESD-71. JTAG boundary-scan testing can be performed before or after configuration, but not during configuration. ACEX 1K devices support the JTAG instructions shown in Table 14.

| Table 14. ACEX 1K J | TAG Instructions                                                                                                                                                                                                               |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Instruction    | Description                                                                                                                                                                                                                    |

| SAMPLE/PRELOAD      | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation and permits an initial data pattern to be output at the device pins.                                                |

| EXTEST              | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                         |

| BYPASS              | Places the 1-bit bypass register between the TDI and TDO pins, allowing the BST data to pass synchronously through a selected device to adjacent devices during normal operation.                                              |

| USERCODE            | Selects the user electronic signature (USERCODE) register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                 |

| IDCODE              | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                          |

| ICR Instructions    | These instructions are used when configuring an ACEX 1K device via JTAG ports using a MasterBlaster, ByteBlasterMV, or BitBlaster download cable, or a Jam File (.jam) or Jam Byte-Code File (.jbc) via an embedded processor. |

The instruction register length of ACEX 1K devices is 10 bits. The USERCODE register length in ACEX 1K devices is 32 bits; 7 bits are determined by the user, and 25 bits are pre-determined. Tables 15 and 16 show the boundary-scan register length and device IDCODE information for ACEX 1K devices.

| Table 15. ACEX 1K Boundary-Scan Register Length |                               |  |  |  |  |

|-------------------------------------------------|-------------------------------|--|--|--|--|

| Device                                          | Boundary-Scan Register Length |  |  |  |  |

| EP1K10 438                                      |                               |  |  |  |  |

| EP1K30 690                                      |                               |  |  |  |  |

| EP1K50                                          | 798                           |  |  |  |  |

| EP1K100                                         | 1,050                         |  |  |  |  |

# **Generic Testing**

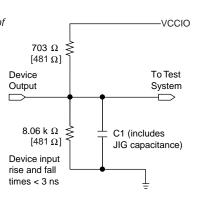

Each ACEX 1K device is functionally tested. Complete testing of each configurable static random access memory (SRAM) bit and all logic functionality ensures 100% yield. AC test measurements for ACEX 1K devices are made under conditions equivalent to those shown in Figure 21. Multiple test patterns can be used to configure devices during all stages of the production flow.

Figure 21. ACEX 1K AC Test Conditions

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast-groundcurrent transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result. Numbers in brackets are for 2.5-V devices or outputs. Numbers without brackets are for 3.3-V devices or outputs.

# Operating Conditions

Tables 18 through 21 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 2.5-V ACEX 1K devices.

| Table 1            | 8. ACEX 1K Device Absolute I | Maximum Ratings Note (1)                 |      |      |      |

|--------------------|------------------------------|------------------------------------------|------|------|------|

| Symbol             | Parameter                    | Conditions                               | Min  | Max  | Unit |

| V <sub>CCINT</sub> | Supply voltage               | With respect to ground (2)               | -0.5 | 3.6  | V    |

| V <sub>CCIO</sub>  |                              |                                          | -0.5 | 4.6  | V    |

| V <sub>I</sub>     | DC input voltage             |                                          | -2.0 | 5.75 | V    |

| I <sub>OUT</sub>   | DC output current, per pin   |                                          | -25  | 25   | mA   |

| T <sub>STG</sub>   | Storage temperature          | No bias                                  | -65  | 150  | ° C  |

| T <sub>AMB</sub>   | Ambient temperature          | Under bias                               | -65  | 135  | ° C  |

| TJ                 | Junction temperature         | PQFP, TQFP, and BGA packages, under bias |      | 135  | ° C  |

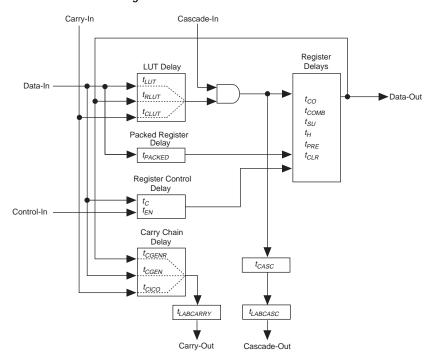

Figure 24 shows the overall timing model, which maps the possible paths to and from the various elements of the ACEX 1K device.

Figure 24. ACEX 1K Device Timing Model

Figures 25 through 28 show the delays that correspond to various paths and functions within the LE, IOE, EAB, and bidirectional timing models.

Figure 25. ACEX 1K Device LE Timing Model

Tables 27 through 29 describe the ACEX 1K external timing parameters and their symbols.

| Table 27. Exte   | ernal Reference Timing Parameters Note (1)                                                     |            |

|------------------|------------------------------------------------------------------------------------------------|------------|

| Symbol           | Parameter                                                                                      | Conditions |

| t <sub>DRR</sub> | Register-to-register delay via four LEs, three row interconnects, and four local interconnects | (2)        |

| Table 28. Ex       | ternal Timing Parameters                                                  |            |

|--------------------|---------------------------------------------------------------------------|------------|

| Symbol             | Parameter                                                                 | Conditions |

| t <sub>INSU</sub>  | Setup time with global clock at IOE register                              | (3)        |

| t <sub>INH</sub>   | Hold time with global clock at IOE register                               | (3)        |

| tоитсо             | Clock-to-output delay with global clock at IOE register                   | (3)        |

| t <sub>PCISU</sub> | Setup time with global clock for registers used in PCI designs            | (3), (4)   |

| t <sub>PCIH</sub>  | Hold time with global clock for registers used in PCI designs             | (3), (4)   |

| t <sub>PCICO</sub> | Clock-to-output delay with global clock for registers used in PCI designs | (3), (4)   |

| Table 29. Ext          | ernal Bidirectional Timing Parameters Note (3)                                             |            |

|------------------------|--------------------------------------------------------------------------------------------|------------|

| Symbol                 | Parameter                                                                                  | Conditions |

| t <sub>INSUBIDIR</sub> | Setup time for bidirectional pins with global clock at same-row or same-column LE register |            |

| t <sub>INHBIDIR</sub>  | Hold time for bidirectional pins with global clock at same-row or same-column LE register  |            |

| toutcobidir            | Clock-to-output delay for bidirectional pins with global clock at IOE register             | CI = 35 pF |

| t <sub>XZBIDIR</sub>   | Synchronous IOE output buffer disable delay                                                | CI = 35 pF |

| t <sub>ZXBIDIR</sub>   | Synchronous IOE output buffer enable delay, slow slew rate = off                           | CI = 35 pF |

## Notes to tables:

- (1) External reference timing parameters are factory-tested, worst-case values specified by Altera. A representative subset of signal paths is tested to approximate typical device applications.

- (2) Contact Altera Applications for test circuit specifications and test conditions.

- (3) These timing parameters are sample-tested only.

- (4) This parameter is measured with the measurement and test conditions, including load, specified in the *PCI Local Bus Specification, Revision 2.2.*

| Symbol              |     |     | Speed | Grade |     |      | Unit |

|---------------------|-----|-----|-------|-------|-----|------|------|

|                     | -   | 1   | -     | -2    |     | -3   |      |

|                     | Min | Max | Min   | Max   | Min | Max  |      |

| $t_{IOD}$           |     | 2.6 |       | 3.1   |     | 4.0  | ns   |

| t <sub>IOC</sub>    |     | 0.3 |       | 0.4   |     | 0.5  | ns   |

| t <sub>IOCO</sub>   |     | 0.9 |       | 1.0   |     | 1.4  | ns   |

| t <sub>IOCOMB</sub> |     | 0.0 |       | 0.0   |     | 0.0  | ns   |

| t <sub>iosu</sub>   | 1.3 |     | 1.5   |       | 2.0 |      | ns   |

| t <sub>IOH</sub>    | 0.9 |     | 1.0   |       | 1.4 |      | ns   |

| t <sub>IOCLR</sub>  |     | 1.1 |       | 1.3   |     | 1.7  | ns   |

| t <sub>OD1</sub>    |     | 3.1 |       | 3.7   |     | 4.1  | ns   |

| t <sub>OD2</sub>    |     | 2.6 |       | 3.3   |     | 3.9  | ns   |

| t <sub>OD3</sub>    |     | 5.8 |       | 6.9   |     | 8.3  | ns   |

| $t_{XZ}$            |     | 3.8 |       | 4.5   |     | 5.9  | ns   |

| $t_{ZX1}$           |     | 3.8 |       | 4.5   |     | 5.9  | ns   |

| $t_{ZX2}$           |     | 3.3 |       | 4.1   |     | 5.7  | ns   |

| $t_{ZX3}$           |     | 6.5 |       | 7.7   |     | 10.1 | ns   |

| t <sub>INREG</sub>  |     | 3.7 |       | 4.3   |     | 5.7  | ns   |

| t <sub>IOFD</sub>   |     | 0.9 |       | 1.0   |     | 1.4  | ns   |

| t <sub>INCOMB</sub> |     | 1.9 |       | 2.3   |     | 3.0  | ns   |

| Symbol                 | Speed Grade |     |     |     |     |     |    |  |

|------------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                        | -           | -1  |     | -2  |     | -3  |    |  |

|                        | Min         | Max | Min | Max | Min | Max |    |  |

| t <sub>EABDATA1</sub>  |             | 1.8 |     | 1.9 |     | 1.9 | ns |  |

| t <sub>EABDATA2</sub>  |             | 0.6 |     | 0.7 |     | 0.7 | ns |  |

| t <sub>EABWE1</sub>    |             | 1.2 |     | 1.2 |     | 1.2 | ns |  |

| t <sub>EABWE2</sub>    |             | 0.4 |     | 0.4 |     | 0.4 | ns |  |

| t <sub>EABRE1</sub>    |             | 0.9 |     | 0.9 |     | 0.9 | ns |  |

| t <sub>EABRE2</sub>    |             | 0.4 |     | 0.4 |     | 0.4 | ns |  |

| t <sub>EABCLK</sub>    |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>EABCO</sub>     |             | 0.3 |     | 0.3 |     | 0.3 | ns |  |

| t <sub>EABBYPASS</sub> |             | 0.5 |     | 0.6 |     | 0.6 | ns |  |

| t <sub>EABSU</sub>     | 1.0         |     | 1.0 |     | 1.0 |     | ns |  |

| t <sub>EABH</sub>      | 0.5         |     | 0.4 |     | 0.4 |     | ns |  |

| t <sub>EABCLR</sub>    | 0.3         |     | 0.3 |     | 0.3 |     | ns |  |

| $t_{AA}$               |             | 3.4 |     | 3.6 |     | 3.6 | ns |  |

| $t_{WP}$               | 2.7         |     | 2.8 |     | 2.8 |     | ns |  |

| $t_{RP}$               | 1.0         |     | 1.0 |     | 1.0 |     | ns |  |

| t <sub>WDSU</sub>      | 1.0         |     | 1.0 |     | 1.0 |     | ns |  |

| t <sub>WDH</sub>       | 0.1         |     | 0.1 |     | 0.1 |     | ns |  |

| t <sub>WASU</sub>      | 1.8         |     | 1.9 |     | 1.9 |     | ns |  |

| t <sub>WAH</sub>       | 1.9         |     | 2.0 |     | 2.0 |     | ns |  |

| t <sub>RASU</sub>      | 3.1         |     | 3.5 |     | 3.5 |     | ns |  |

| t <sub>RAH</sub>       | 0.2         |     | 0.2 |     | 0.2 |     | ns |  |

| $t_{WO}$               |             | 2.7 |     | 2.8 |     | 2.8 | ns |  |

| $t_{DD}$               |             | 2.7 |     | 2.8 |     | 2.8 | ns |  |

| t <sub>EABOUT</sub>    |             | 0.5 |     | 0.6 |     | 0.6 | ns |  |

| t <sub>EABCH</sub>     | 1.5         |     | 2.0 |     | 2.0 |     | ns |  |

| t <sub>EABCL</sub>     | 2.7         |     | 2.8 |     | 2.8 |     | ns |  |

| Symbol                   | Speed Grade |     |     |     |     |     |    |  |

|--------------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                          | -1          |     | -2  |     | -3  |     |    |  |

|                          | Min         | Max | Min | Max | Min | Max |    |  |

| t <sub>DIN2IOE</sub>     |             | 2.3 |     | 2.7 |     | 3.6 | ns |  |

| t <sub>DIN2LE</sub>      |             | 0.8 |     | 1.1 |     | 1.4 | ns |  |

| t <sub>DIN2DATA</sub>    |             | 1.1 |     | 1.4 |     | 1.8 | ns |  |

| t <sub>DCLK2IOE</sub>    |             | 2.3 |     | 2.7 |     | 3.6 | ns |  |

| t <sub>DCLK2LE</sub>     |             | 0.8 |     | 1.1 |     | 1.4 | ns |  |

| t <sub>SAMELAB</sub>     |             | 0.1 |     | 0.1 |     | 0.2 | ns |  |

| t <sub>SAMEROW</sub>     |             | 1.8 |     | 2.1 |     | 2.9 | ns |  |

| t <sub>SAME</sub> COLUMN |             | 0.3 |     | 0.4 |     | 0.7 | ns |  |

| t <sub>DIFFROW</sub>     |             | 2.1 |     | 2.5 |     | 3.6 | ns |  |

| t <sub>TWOROWS</sub>     |             | 3.9 |     | 4.6 |     | 6.5 | ns |  |

| t <sub>LEPERIPH</sub>    |             | 3.3 |     | 3.7 |     | 4.8 | ns |  |

| t <sub>LABCARRY</sub>    |             | 0.3 |     | 0.4 |     | 0.5 | ns |  |

| t <sub>LABCASC</sub>     |             | 0.9 |     | 1.0 |     | 1.4 | ns |  |

| Table 35. EP1K10            | ) External Ti | ming Param | eters No | te (1) |     |      |    |

|-----------------------------|---------------|------------|----------|--------|-----|------|----|

| Symbol                      |               | Unit       |          |        |     |      |    |

|                             | -             | 1          | -2       |        | -3  |      |    |

|                             | Min           | Max        | Min      | Max    | Min | Max  |    |

| t <sub>DRR</sub>            |               | 7.5        |          | 9.5    |     | 12.5 | ns |

| t <sub>INSU</sub> (2), (3)  | 2.4           |            | 2.7      |        | 3.6 |      | ns |

| t <sub>INH</sub> (2), (3)   | 0.0           |            | 0.0      |        | 0.0 |      | ns |

| t <sub>оитсо</sub> (2), (3) | 2.0           | 6.6        | 2.0      | 7.8    | 2.0 | 9.6  | ns |

| t <sub>INSU</sub> (4), (3)  | 1.4           |            | 1.7      |        | -   |      | ns |

| t <sub>INH</sub> (4), (3)   | 0.5           | 5.1        | 0.5      | 6.4    | -   | -    | ns |

| t <sub>оитсо</sub> (4), (3) | 0.0           |            | 0.0      |        | -   |      | ns |

| t <sub>PCISU</sub> (3)      | 3.0           |            | 4.2      |        | 6.4 |      | ns |

| t <sub>PCIH</sub> (3)       | 0.0           |            | 0.0      |        | -   |      | ns |

| t <sub>PCICO</sub> (3)      | 2.0           | 6.0        | 2.0      | 7.5    | 2.0 | 10.2 | ns |

| Symbol                      | Speed Grade |     |     |     |     |      |    |  |

|-----------------------------|-------------|-----|-----|-----|-----|------|----|--|

|                             | -1          |     | -2  |     | -3  |      |    |  |

|                             | Min         | Max | Min | Max | Min | Max  |    |  |

| t <sub>INSUBIDIR</sub> (2)  | 2.7         |     | 3.2 |     | 4.3 |      | ns |  |

| t <sub>INHBIDIR</sub> (2)   | 0.0         |     | 0.0 |     | 0.0 |      | ns |  |

| t <sub>INSUBIDIR</sub> (3)  | 3.7         |     | 4.2 |     | -   |      | ns |  |

| t <sub>INHBIDIR</sub> (3)   | 0.0         |     | 0.0 |     | _   |      | ns |  |

| t <sub>OUTCOBIDIR</sub> (2) | 2.0         | 4.5 | 2.0 | 5.2 | 2.0 | 7.3  | ns |  |

| t <sub>XZBIDIR</sub> (2)    |             | 6.8 |     | 7.8 |     | 10.1 | ns |  |

| t <sub>ZXBIDIR</sub> (2)    |             | 6.8 |     | 7.8 |     | 10.1 | ns |  |

| toutcobidir (3)             | 0.5         | 3.5 | 0.5 | 4.2 | =   | -    |    |  |

| t <sub>XZBIDIR</sub> (3)    |             | 6.8 |     | 8.4 |     | -    | ns |  |

| t <sub>ZXBIDIR</sub> (3)    |             | 6.8 |     | 8.4 | •   | -    | ns |  |

#### Notes to tables:

- All timing parameters are described in Tables 22 through 29. This parameter is measured without use of the ClockLock or ClockBoost circuits. (2)

- This parameter is measured with use of the ClockLock or ClockBoost circuits (3)

Tables 51 through 57 show EP1K100 device internal and external timing parameters.

| Symbol              | Speed Grade |     |     |     |     |     |    |  |

|---------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                     | -1          |     | -2  |     | -3  |     |    |  |

|                     | Min         | Max | Min | Max | Min | Max |    |  |

| $t_{LUT}$           |             | 0.7 |     | 1.0 |     | 1.5 | ns |  |

| t <sub>CLUT</sub>   |             | 0.5 |     | 0.7 |     | 0.9 | ns |  |

| t <sub>RLUT</sub>   |             | 0.6 |     | 0.8 |     | 1.1 | ns |  |

| t <sub>PACKED</sub> |             | 0.3 |     | 0.4 |     | 0.5 | ns |  |

| t <sub>EN</sub>     |             | 0.2 |     | 0.3 |     | 0.3 | ns |  |

| t <sub>CICO</sub>   |             | 0.1 |     | 0.1 |     | 0.2 | ns |  |

| t <sub>CGEN</sub>   |             | 0.4 |     | 0.5 |     | 0.7 | ns |  |

| t <sub>CGENR</sub>  |             | 0.1 |     | 0.1 |     | 0.2 | ns |  |

| t <sub>CASC</sub>   |             | 0.6 |     | 0.9 |     | 1.2 | ns |  |

| $t_C$               |             | 0.8 |     | 1.0 |     | 1.4 | ns |  |

| $t_{CO}$            |             | 0.6 |     | 0.8 |     | 1.1 | ns |  |

| t <sub>COMB</sub>   |             | 0.4 |     | 0.5 |     | 0.7 | ns |  |

| t <sub>SU</sub>     | 0.4         |     | 0.6 |     | 0.7 |     | ns |  |

| t <sub>H</sub>      | 0.5         |     | 0.7 |     | 0.9 |     | ns |  |

| t <sub>PRE</sub>    |             | 0.8 |     | 1.0 |     | 1.4 | ns |  |

| t <sub>CLR</sub>    |             | 0.8 |     | 1.0 |     | 1.4 | ns |  |

| t <sub>CH</sub>     | 1.5         |     | 2.0 |     | 2.5 |     | ns |  |

| $t_{CL}$            | 1.5         |     | 2.0 |     | 2.5 | i i | ns |  |

| Symbol                  | Speed Grade |     |     |     |      |     |    |  |

|-------------------------|-------------|-----|-----|-----|------|-----|----|--|

|                         | -1          |     | -2  |     | -3   |     |    |  |

|                         | Min         | Max | Min | Max | Min  | Max |    |  |

| t <sub>EABAA</sub>      |             | 5.9 |     | 7.6 |      | 9.9 | ns |  |

| t <sub>EABRCOMB</sub>   | 5.9         |     | 7.6 |     | 9.9  |     | ns |  |

| t <sub>EABRCREG</sub>   | 5.1         |     | 6.5 |     | 8.5  |     | ns |  |

| t <sub>EABWP</sub>      | 2.7         |     | 3.5 |     | 4.7  |     | ns |  |

| t <sub>EABWCOMB</sub>   | 5.9         |     | 7.7 |     | 10.3 |     | ns |  |

| t <sub>EABWCREG</sub>   | 5.4         |     | 7.0 |     | 9.4  |     | ns |  |

| t <sub>EABDD</sub>      |             | 3.4 |     | 4.5 |      | 5.9 | ns |  |

| t <sub>EABDATA</sub> CO |             | 0.5 |     | 0.7 |      | 0.8 | ns |  |

| t <sub>EABDATASU</sub>  | 0.8         |     | 1.0 |     | 1.4  |     | ns |  |

| t <sub>EABDATAH</sub>   | 0.1         |     | 0.1 |     | 0.2  |     | ns |  |

| t <sub>EABWESU</sub>    | 1.1         |     | 1.4 |     | 1.9  |     | ns |  |

| t <sub>EABWEH</sub>     | 0.0         |     | 0.0 |     | 0.0  |     | ns |  |

| t <sub>EABWDSU</sub>    | 1.0         |     | 1.3 |     | 1.7  |     | ns |  |

| t <sub>EABWDH</sub>     | 0.2         |     | 0.2 |     | 0.3  |     | ns |  |

| t <sub>EABWASU</sub>    | 4.1         |     | 5.2 |     | 6.8  |     | ns |  |

| t <sub>EABWAH</sub>     | 0.0         |     | 0.0 |     | 0.0  |     | ns |  |

| t <sub>EABWO</sub>      |             | 3.4 |     | 4.5 |      | 5.9 | ns |  |