Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 624                                                       |

| Number of Logic Elements/Cells | 4992                                                      |

| Total RAM Bits                 | 49152                                                     |

| Number of I/O                  | 147                                                       |

| Number of Gates                | 257000                                                    |

| Voltage - Supply               | 2.375V ~ 2.625V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 70°C (TA)                                           |

| Package / Case                 | 208-BFQFP                                                 |

| Supplier Device Package        | 208-PQFP (28x28)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1k100qc208-2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 5 shows ACEX 1K device performance for more complex designs. These designs are available as Altera MegaCore $^{\rm TM}$  functions.

| Table 5. ACEX 1K Device Performance for Complex Designs     |       |             |      |      |       |  |

|-------------------------------------------------------------|-------|-------------|------|------|-------|--|

| Application                                                 |       | Performance |      |      |       |  |

|                                                             | Used  | Speed Grade |      |      | Units |  |

|                                                             | ·     | -1          | -2   | -3   |       |  |

| 16-bit, 8-tap parallel finite impulse response (FIR) filter | 597   | 192         | 156  | 116  | MSPS  |  |

| 8-bit, 512-point Fast Fourier transform (FFT)               | 1,854 | 23.4        | 28.7 | 38.9 | μs    |  |

| function                                                    |       | 113         | 92   | 68   | MHz   |  |

| a16450 universal asynchronous receiver/transmitter (UART)   | 342   | 36          | 28   | 20.5 | MHz   |  |

Each ACEX 1K device contains an embedded array and a logic array. The embedded array is used to implement a variety of memory functions or complex logic functions, such as digital signal processing (DSP), wide data-path manipulation, microcontroller applications, and data-transformation functions. The logic array performs the same function as the sea-of-gates in the gate array and is used to implement general logic such as counters, adders, state machines, and multiplexers. The combination of embedded and logic arrays provides the high performance and high density of embedded gate arrays, enabling designers to implement an entire system on a single device.

ACEX 1K devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers EPC16, EPC2, EPC1, and EPC1441 configuration devices, which configure ACEX 1K devices via a serial data stream. Configuration data can also be downloaded from system RAM or via the Altera MasterBlaster $^{\text{TM}}$ , ByteBlasterMV $^{\text{TM}}$ , or BitBlaster $^{\text{TM}}$  download cables. After an ACEX 1K device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Because reconfiguration requires less than 40 ms, real-time changes can be made during system operation.

ACEX 1K devices contain an interface that permits microprocessors to configure ACEX 1K devices serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat an ACEX 1K device as memory and configure it by writing to a virtual memory location, simplifying device reconfiguration.

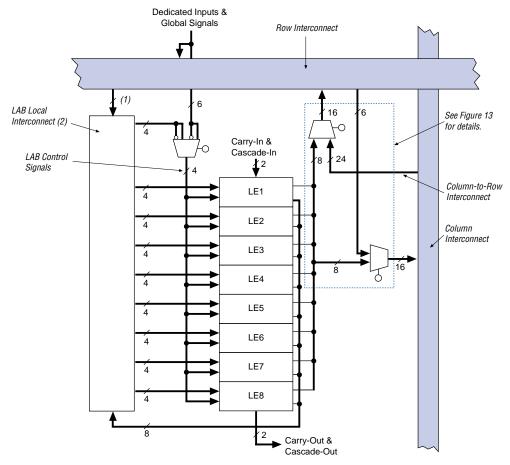

Figure 7. ACEX 1K LAB

#### Notes:

- (1) EP1K10, EP1K30, and EP1K50 devices have 22 inputs to the LAB local interconnect channel from the row; EP1K100 devices have 26.

- (2) EP1K10, EP1K30, and EP1K50 devices have 30 LAB local interconnect channels; EP1K100 devices have 34.

## Carry Chain

The carry chain provides a very fast (as low as 0.2 ns) carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the ACEX 1K architecture to efficiently implement high-speed counters, adders, and comparators of arbitrary width. Carry chain logic can be created automatically by the compiler during design processing, or manually by the designer during design entry. Parameterized functions, such as LPM and DesignWare functions, automatically take advantage of carry chains.

Carry chains longer than eight LEs are automatically implemented by linking LABs together. For enhanced fitting, a long carry chain skips alternate LABs in a row. A carry chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from odd-numbered LAB to odd-numbered LAB. For example, the last LE of the first LAB in a row carries to the first LE of the third LAB in the row. The carry chain does not cross the EAB at the middle of the row. For instance, in the EP1K50 device, the carry chain stops at the eighteenth LAB, and a new carry chain begins at the nineteenth LAB.

Figure 9 shows how an n-bit full adder can be implemented in n+1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for an accumulator function. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it can be used as a general-purpose signal.

#### **Clearable Counter Mode**

The clearable counter mode is similar to the up/down counter mode, but it supports a synchronous clear instead of the up/down control. The clear function is substituted for the cascade-in signal in the up/down counter mode. Two 3-input LUTs are used; one generates the counter data, and the other generates the fast carry bit. Synchronous loading is provided by a 2-to-1 multiplexer. The output of this multiplexer is AND ed with a synchronous clear signal.

#### Internal Tri-State Emulation

Internal tri-state emulation provides internal tri-states without the limitations of a physical tri-state bus. In a physical tri-state bus, the tri-state buffers' output enable (OE) signals select which signal drives the bus. However, if multiple OE signals are active, contending signals can be driven onto the bus. Conversely, if no OE signals are active, the bus will float. Internal tri-state emulation resolves contending tri-state buffers to a low value and floating buses to a high value, thereby eliminating these problems. The Altera software automatically implements tri-state bus functionality with a multiplexer.

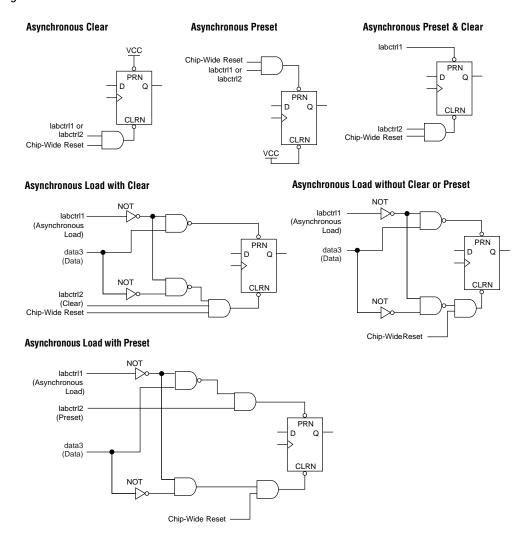

## Clear & Preset Logic Control

Logic for the programmable register's clear and preset functions is controlled by the DATA3, LABCTRL1, and LABCTRL2 inputs to the LE. The clear and preset control structure of the LE asynchronously loads signals into a register. Either LABCTRL1 or LABCTRL2 can control the asynchronous clear. Alternatively, the register can be set up so that LABCTRL1 implements an asynchronous load. The data to be loaded is driven to DATA3; when LABCTRL1 is asserted, DATA3 is loaded into the register.

During compilation, the compiler automatically selects the best control signal implementation. Because the clear and preset functions are active-low, the Compiler automatically assigns a logic high to an unused clear or preset.

The clear and preset logic is implemented in one of the following six modes chosen during design entry:

- Asynchronous clear

- Asynchronous preset

- Asynchronous clear and preset

- Asynchronous load with clear

- Asynchronous load with preset

- Asynchronous load without clear or preset

In addition to the six clear and preset modes, ACEX 1K devices provide a chip-wide reset pin that can reset all registers in the device. Use of this feature is set during design entry. In any of the clear and preset modes, the chip-wide reset overrides all other signals. Registers with asynchronous presets may be preset when the chip-wide reset is asserted. Inversion can be used to implement the asynchronous preset. Figure 12 shows examples of how to setup the preset and clear inputs for the desired functionality.

Figure 12. ACEX 1K LE Clear & Preset Modes

See Figure 17 for details. I/O Element (IOE) IOF IIOF IOE IOE IOE IOE Row LAB LAB See Figure 16 I AR Interconnect Α1 A2 АЗ for details. Column ►To LAB A5 Interconnect ►To LAB A4 IOE IOE LAB LAB I AR Cascade & B1 R2 В3 Carry Chains To LAB B5 ►To LAB B4 IOE IOE IOE

Figure 14. ACEX 1K Interconnect Resources

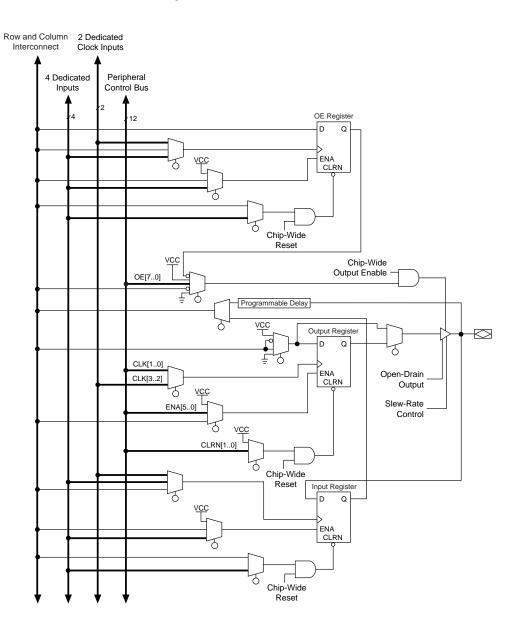

## I/O Element

An IOE contains a bidirectional I/O buffer and a register that can be used either as an input register for external data that requires a fast setup time or as an output register for data that requires fast clock-to-output performance. In some cases, using an LE register for an input register will result in a faster setup time than using an IOE register. IOEs can be used as input, output, or bidirectional pins. The compiler uses the programmable inversion option to invert signals from the row and column interconnect automatically where appropriate. For bidirectional registered I/O implementation, the output register should be in the IOE and the data input and output enable registers should be LE registers placed adjacent to the bidirectional pin. Figure 15 shows the bidirectional I/O registers.

Figure 15. ACEX 1K Bidirectional I/O Registers

The VCCINT pins must always be connected to a 2.5-V power supply. With a 2.5-V  $V_{\rm CCINT}$  level, input voltages are compatible with 2.5-V, 3.3-V, and 5.0-V inputs. The VCCIO pins can be connected to either a 2.5-V or 3.3-V power supply, depending on the output requirements. When the VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is at 3.3 V and is therefore compatible with 3.3-V or 5.0-V systems. Devices operating with  $V_{\rm CCIO}$  levels higher than 3.0 V achieve a faster timing delay of  $t_{OD2}$  instead of  $t_{OD1}$ .

Table 13 summarizes ACEX 1K MultiVolt I/O support.

| Table 13. ACEX 1K MultiVolt I/O Support                  |          |              |              |              |          |          |

|----------------------------------------------------------|----------|--------------|--------------|--------------|----------|----------|

| V <sub>CCIO</sub> (V) Input Signal (V) Output Signal (V) |          |              |              |              |          | (V)      |

|                                                          | 2.5      | 3.3          | 5.0          | 2.5          | 3.3      | 5.0      |

| 2.5                                                      | <b>✓</b> | <b>✓</b> (1) | <b>√</b> (1) | ✓            |          |          |

| 3.3                                                      | <b>✓</b> | <b>✓</b>     | <b>√</b> (1) | <b>√</b> (2) | <b>✓</b> | <b>✓</b> |

#### Notes:

- (1) The PCI clamping diode must be disabled on an input which is driven with a voltage higher than  $V_{\rm CCIO}$ .

- (2) When  $V_{\rm CCIO}$  = 3.3 V, an ACEX 1K device can drive a 2.5-V device that has 3.3-V tolerant inputs.

Open-drain output pins on ACEX 1K devices (with a pull-up resistor to the 5.0-V supply) can drive 5.0-V CMOS input pins that require a higher  $V_{IH}$  than LVTTL. When the open-drain pin is active, it will drive low. When the pin is inactive, the resistor will pull up the trace to 5.0 V, thereby meeting the CMOS  $V_{OH}$  requirement. The open-drain pin will only drive low or tri-state; it will never drive high. The rise time is dependent on the value of the pull-up resistor and load impedance. The  $I_{OL}$  current specification should be considered when selecting a pull-up resistor.

## Power Sequencing & Hot-Socketing

Because ACEX 1K devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. The  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  power planes can be powered in any order.

Signals can be driven into ACEX 1K devices before and during power up without damaging the device. Additionally, ACEX 1K devices do not drive out during power up. Once operating conditions are reached, ACEX 1K devices operate as specified by the user.

| Table 16. 32-Bit IDCODE for ACEX 1K Devices Note (1) |                     |                       |                                   |               |  |  |  |

|------------------------------------------------------|---------------------|-----------------------|-----------------------------------|---------------|--|--|--|

| Device                                               |                     | IDCODE (32 Bits)      |                                   |               |  |  |  |

|                                                      | Version<br>(4 Bits) | Part Number (16 Bits) | Manufacturer's Identity (11 Bits) | 1 (1 Bit) (2) |  |  |  |

| EP1K10                                               | 0001                | 0001 0000 0001 0000   | 00001101110                       | 1             |  |  |  |

| EP1K30                                               | 0001                | 0001 0000 0011 0000   | 00001101110                       | 1             |  |  |  |

| EP1K50                                               | 0001                | 0001 0000 0101 0000   | 00001101110                       | 1             |  |  |  |

| EP1K100                                              | 0010                | 0000 0001 0000 0000   | 00001101110                       | 1             |  |  |  |

#### Notes to tables:

- (1) The most significant bit (MSB) is on the left.

- (2) The least significant bit (LSB) for all JTAG IDCODEs is 1.

ACEX 1K devices include weak pull-up resistors on the JTAG pins.

For more information, see the following documents:

- Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- ByteBlasterMV Parallel Port Download Cable Data Sheet

- BitBlaster Serial Download Cable Data Sheet

- Jam Programming & Test Language Specification

Figure 20 shows the timing requirements for the JTAG signals.

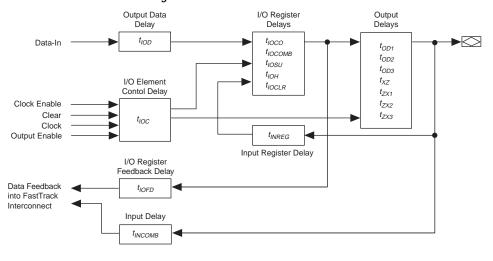

Figure 26. ACEX 1K Device IOE Timing Model

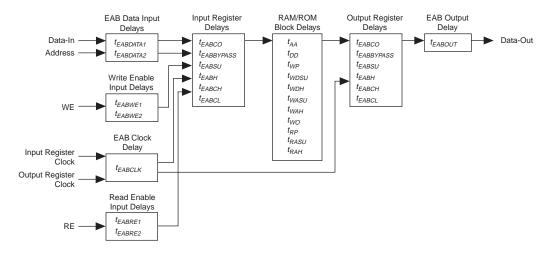

Figure 27. ACEX 1K Device EAB Timing Model

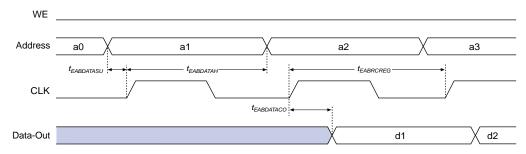

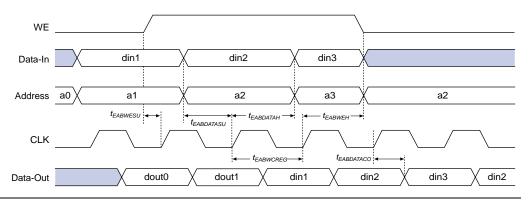

Figure 30. EAB Synchronous Timing Waveforms

## **EAB Synchronous Read**

## EAB Synchronous Write (EAB Output Registers Used)

Tables 22 through 26 describe the ACEX 1K device internal timing parameters.

| Table 22. LE Timing Microparameters (Part 1 of 2) Note (1) |                                         |  |  |  |  |  |

|------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|

| Symbol                                                     | Parameter Condition                     |  |  |  |  |  |

| $t_{LUT}$                                                  | LUT delay for data-in                   |  |  |  |  |  |

| t <sub>CLUT</sub>                                          | LUT delay for carry-in                  |  |  |  |  |  |

| t <sub>RLUT</sub>                                          | LUT delay for LE register feedback      |  |  |  |  |  |

| t <sub>PACKED</sub>                                        | Data-in to packed register delay        |  |  |  |  |  |

| t <sub>EN</sub>                                            | LE register enable delay                |  |  |  |  |  |

| t <sub>CICO</sub>                                          | Carry-in to carry-out delay             |  |  |  |  |  |

| t <sub>CGEN</sub>                                          | Data-in to carry-out delay              |  |  |  |  |  |

| t <sub>CGENR</sub>                                         | LE register feedback to carry-out delay |  |  |  |  |  |

| Table 22. LE Timing Microparameters (Part 2 of 2) Note (1) |                                                                                                                                      |            |  |  |  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| Symbol                                                     | Parameter                                                                                                                            | Conditions |  |  |  |

| t <sub>CASC</sub>                                          | Cascade-in to cascade-out delay                                                                                                      |            |  |  |  |

| $t_{C}$                                                    | LE register control signal delay                                                                                                     |            |  |  |  |

| $t_{CO}$                                                   | LE register clock-to-output delay                                                                                                    |            |  |  |  |

| t <sub>COMB</sub>                                          | Combinatorial delay                                                                                                                  |            |  |  |  |

| t <sub>SU</sub>                                            | LE register setup time for data and enable signals before clock; LE register recovery time after asynchronous clear, preset, or load |            |  |  |  |

| $t_H$                                                      | LE register hold time for data and enable signals after clock                                                                        |            |  |  |  |

| t <sub>PRE</sub>                                           | LE register preset delay                                                                                                             |            |  |  |  |

| t <sub>CLR</sub>                                           | LE register clear delay                                                                                                              |            |  |  |  |

| t <sub>CH</sub>                                            | Minimum clock high time from clock pin                                                                                               |            |  |  |  |

| $t_{CL}$                                                   | Minimum clock low time from clock pin                                                                                                |            |  |  |  |

| Table 23. 10        | E Timing Microparameters Note (1)                                                                                     |                |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|----------------|

| Symbol              | Parameter                                                                                                             | Conditions     |

| $t_{IOD}$           | IOE data delay                                                                                                        |                |

| $t_{IOC}$           | IOE register control signal delay                                                                                     |                |

| t <sub>IOCO</sub>   | IOE register clock-to-output delay                                                                                    |                |

| t <sub>IOCOMB</sub> | IOE combinatorial delay                                                                                               |                |

| t <sub>IOSU</sub>   | IOE register setup time for data and enable signals before clock; IOE register recovery time after asynchronous clear |                |

| t <sub>IOH</sub>    | IOE register hold time for data and enable signals after clock                                                        |                |

| t <sub>IOCLR</sub>  | IOE register clear time                                                                                               |                |

| t <sub>OD1</sub>    | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = 3.3 V                                          | C1 = 35 pF (2) |

| t <sub>OD2</sub>    | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = 2.5 V                                          | C1 = 35 pF (3) |

| t <sub>OD3</sub>    | Output buffer and pad delay, slow slew rate = on                                                                      | C1 = 35 pF (4) |

| $t_{XZ}$            | IOE output buffer disable delay                                                                                       |                |

| $t_{ZX1}$           | IOE output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = 3.3 V                                       | C1 = 35 pF (2) |

| $t_{ZX2}$           | IOE output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = 2.5 V                                       | C1 = 35 pF (3) |

| t <sub>ZX3</sub>    | IOE output buffer enable delay, slow slew rate = on                                                                   | C1 = 35 pF (4) |

| t <sub>INREG</sub>  | IOE input pad and buffer to IOE register delay                                                                        |                |

| t <sub>IOFD</sub>   | IOE register feedback delay                                                                                           |                |

| t <sub>INCOMB</sub> | IOE input pad and buffer to FastTrack Interconnect delay                                                              |                |

| Symbol                 | Parameter                                                        | Conditions |  |

|------------------------|------------------------------------------------------------------|------------|--|

| t <sub>EABDATA1</sub>  | Data or address delay to EAB for combinatorial input             |            |  |

| t <sub>EABDATA2</sub>  | Data or address delay to EAB for registered input                |            |  |

| t <sub>EABWE1</sub>    | Write enable delay to EAB for combinatorial input                |            |  |

| t <sub>EABWE2</sub>    | Write enable delay to EAB for registered input                   |            |  |

| t <sub>EABRE1</sub>    | Read enable delay to EAB for combinatorial input                 |            |  |

| t <sub>EABRE2</sub>    | Read enable delay to EAB for registered input                    |            |  |

| t <sub>EABCLK</sub>    | EAB register clock delay                                         |            |  |

| t <sub>EABCO</sub>     | EAB register clock-to-output delay                               |            |  |

| t <sub>EABBYPASS</sub> | Bypass register delay                                            |            |  |

| t <sub>EABSU</sub>     | EAB register setup time before clock                             |            |  |

| t <sub>EABH</sub>      | EAB register hold time after clock                               |            |  |

| t <sub>EABCLR</sub>    | EAB register asynchronous clear time to output delay             |            |  |

| $t_{AA}$               | Address access delay (including the read enable to output delay) |            |  |

| $t_{WP}$               | Write pulse width                                                |            |  |

| $t_{RP}$               | Read pulse width                                                 |            |  |

| t <sub>WDSU</sub>      | Data setup time before falling edge of write pulse               | (5)        |  |

| t <sub>WDH</sub>       | Data hold time after falling edge of write pulse                 | (5)        |  |

| t <sub>WASU</sub>      | Address setup time before rising edge of write pulse             | (5)        |  |

| t <sub>WAH</sub>       | Address hold time after falling edge of write pulse              | (5)        |  |

| t <sub>RASU</sub>      | Address setup time before rising edge of read pulse              |            |  |

| t <sub>RAH</sub>       | Address hold time after falling edge of read pulse               |            |  |

| $t_{WO}$               | Write enable to data output valid delay                          |            |  |

| $t_{DD}$               | Data-in to data-out valid delay                                  |            |  |

| t <sub>EABOUT</sub>    | Data-out delay                                                   |            |  |

| t <sub>EABCH</sub>     | Clock high time                                                  |            |  |

| t <sub>EABCL</sub>     | Clock low time                                                   |            |  |

Tables 27 through 29 describe the ACEX 1K external timing parameters and their symbols.

| Table 27. External Reference Timing Parameters Note (1) |                                                                                                |            |  |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------|------------|--|--|

| Symbol                                                  | Parameter                                                                                      | Conditions |  |  |

| t <sub>DRR</sub>                                        | Register-to-register delay via four LEs, three row interconnects, and four local interconnects | (2)        |  |  |

| Table 28. External Timing Parameters |                                                                           |            |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------|------------|--|--|--|--|

| Symbol                               | Parameter                                                                 | Conditions |  |  |  |  |

| t <sub>INSU</sub>                    | Setup time with global clock at IOE register                              | (3)        |  |  |  |  |

| t <sub>INH</sub>                     | Hold time with global clock at IOE register                               | (3)        |  |  |  |  |

| tоитсо                               | Clock-to-output delay with global clock at IOE register                   | (3)        |  |  |  |  |

| t <sub>PCISU</sub>                   | Setup time with global clock for registers used in PCI designs            | (3), (4)   |  |  |  |  |

| t <sub>PCIH</sub>                    | Hold time with global clock for registers used in PCI designs             | (3), (4)   |  |  |  |  |

| t <sub>PCICO</sub>                   | Clock-to-output delay with global clock for registers used in PCI designs | (3), (4)   |  |  |  |  |

| Table 29. External Bidirectional Timing Parameters Note (3) |                                                                                            |            |  |  |  |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------|--|--|--|--|

| Symbol                                                      | Parameter                                                                                  | Conditions |  |  |  |  |

| t <sub>INSUBIDIR</sub>                                      | Setup time for bidirectional pins with global clock at same-row or same-column LE register |            |  |  |  |  |

| t <sub>INHBIDIR</sub>                                       | Hold time for bidirectional pins with global clock at same-row or same-column LE register  |            |  |  |  |  |

| t <sub>OUTCOBIDIR</sub>                                     | Clock-to-output delay for bidirectional pins with global clock at IOE register             | CI = 35 pF |  |  |  |  |

| t <sub>XZBIDIR</sub>                                        | Synchronous IOE output buffer disable delay                                                | CI = 35 pF |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                        | Synchronous IOE output buffer enable delay, slow slew rate = off                           | CI = 35 pF |  |  |  |  |

## Notes to tables:

- (1) External reference timing parameters are factory-tested, worst-case values specified by Altera. A representative subset of signal paths is tested to approximate typical device applications.

- (2) Contact Altera Applications for test circuit specifications and test conditions.

- (3) These timing parameters are sample-tested only.

- (4) This parameter is measured with the measurement and test conditions, including load, specified in the *PCI Local Bus Specification, Revision 2.2.*

Tables 30 through 36 show EP1K10 device internal and external timing parameters.

| Table 30. EP1K10 Device LE Timing Microparameters Note (1) |     |     |       |       |     |     |      |  |

|------------------------------------------------------------|-----|-----|-------|-------|-----|-----|------|--|

| Symbol                                                     |     |     | Speed | Grade |     |     | Unit |  |

|                                                            | -   | 1   | -2    |       | -3  |     |      |  |

|                                                            | Min | Max | Min   | Max   | Min | Max |      |  |

| $t_{LUT}$                                                  |     | 0.7 |       | 0.8   |     | 1.1 | ns   |  |

| $t_{CLUT}$                                                 |     | 0.5 |       | 0.6   |     | 0.8 | ns   |  |

| t <sub>RLUT</sub>                                          |     | 0.6 |       | 0.7   |     | 1.0 | ns   |  |

| t <sub>PACKED</sub>                                        |     | 0.4 |       | 0.4   |     | 0.5 | ns   |  |

| $t_{EN}$                                                   |     | 0.9 |       | 1.0   |     | 1.3 | ns   |  |

| $t_{CICO}$                                                 |     | 0.1 |       | 0.1   |     | 0.2 | ns   |  |

| t <sub>CGEN</sub>                                          |     | 0.4 |       | 0.5   |     | 0.7 | ns   |  |

| t <sub>CGENR</sub>                                         |     | 0.1 |       | 0.1   |     | 0.2 | ns   |  |

| t <sub>CASC</sub>                                          |     | 0.7 |       | 0.9   |     | 1.1 | ns   |  |

| $t_{C}$                                                    |     | 1.1 |       | 1.3   |     | 1.7 | ns   |  |

| $t_{\rm CO}$                                               |     | 0.5 |       | 0.7   |     | 0.9 | ns   |  |

| t <sub>COMB</sub>                                          |     | 0.4 |       | 0.5   |     | 0.7 | ns   |  |

| t <sub>SU</sub>                                            | 0.7 |     | 0.8   |       | 1.0 |     | ns   |  |

| t <sub>H</sub>                                             | 0.9 |     | 1.0   |       | 1.1 |     | ns   |  |

| t <sub>PRE</sub>                                           |     | 0.8 |       | 1.0   |     | 1.4 | ns   |  |

| t <sub>CLR</sub>                                           |     | 0.9 |       | 1.0   |     | 1.4 | ns   |  |

| t <sub>CH</sub>                                            | 2.0 |     | 2.5   |       | 2.5 |     | ns   |  |

| $t_{CL}$                                                   | 2.0 |     | 2.5   |       | 2.5 |     | ns   |  |

| Symbol                 | Speed Grade |     |     |     |     |     |    |  |

|------------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                        | -1          |     | -2  |     | -3  |     |    |  |

|                        | Min         | Max | Min | Max | Min | Max |    |  |

| t <sub>EABDATA1</sub>  |             | 1.8 |     | 1.9 |     | 1.9 | ns |  |

| t <sub>EABDATA2</sub>  |             | 0.6 |     | 0.7 |     | 0.7 | ns |  |

| t <sub>EABWE1</sub>    |             | 1.2 |     | 1.2 |     | 1.2 | ns |  |

| t <sub>EABWE2</sub>    |             | 0.4 |     | 0.4 |     | 0.4 | ns |  |

| t <sub>EABRE1</sub>    |             | 0.9 |     | 0.9 |     | 0.9 | ns |  |

| t <sub>EABRE2</sub>    |             | 0.4 |     | 0.4 |     | 0.4 | ns |  |

| t <sub>EABCLK</sub>    |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>EABCO</sub>     |             | 0.3 |     | 0.3 |     | 0.3 | ns |  |

| t <sub>EABBYPASS</sub> |             | 0.5 |     | 0.6 |     | 0.6 | ns |  |

| t <sub>EABSU</sub>     | 1.0         |     | 1.0 |     | 1.0 |     | ns |  |

| t <sub>EABH</sub>      | 0.5         |     | 0.4 |     | 0.4 |     | ns |  |

| t <sub>EABCLR</sub>    | 0.3         |     | 0.3 |     | 0.3 |     | ns |  |

| $t_{AA}$               |             | 3.4 |     | 3.6 |     | 3.6 | ns |  |

| $t_{WP}$               | 2.7         |     | 2.8 |     | 2.8 |     | ns |  |

| $t_{RP}$               | 1.0         |     | 1.0 |     | 1.0 |     | ns |  |

| t <sub>WDSU</sub>      | 1.0         |     | 1.0 |     | 1.0 |     | ns |  |

| t <sub>WDH</sub>       | 0.1         |     | 0.1 |     | 0.1 |     | ns |  |

| t <sub>WASU</sub>      | 1.8         |     | 1.9 |     | 1.9 |     | ns |  |

| t <sub>WAH</sub>       | 1.9         |     | 2.0 |     | 2.0 |     | ns |  |

| t <sub>RASU</sub>      | 3.1         |     | 3.5 |     | 3.5 |     | ns |  |

| t <sub>RAH</sub>       | 0.2         |     | 0.2 |     | 0.2 |     | ns |  |

| $t_{WO}$               |             | 2.7 |     | 2.8 |     | 2.8 | ns |  |

| $t_{DD}$               |             | 2.7 |     | 2.8 |     | 2.8 | ns |  |

| t <sub>EABOUT</sub>    |             | 0.5 |     | 0.6 |     | 0.6 | ns |  |

| t <sub>EABCH</sub>     | 1.5         |     | 2.0 |     | 2.0 |     | ns |  |

| t <sub>EABCL</sub>     | 2.7         |     | 2.8 |     | 2.8 |     | ns |  |

| Symbol                  | Speed Grade |     |     |     |     |     |    |  |

|-------------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                         | -1          |     | -2  |     | -3  |     |    |  |

|                         | Min         | Max | Min | Max | Min | Max |    |  |

| t <sub>EABAA</sub>      |             | 6.7 |     | 7.3 |     | 7.3 | ns |  |

| t <sub>EABRCCOMB</sub>  | 6.7         |     | 7.3 |     | 7.3 |     | ns |  |

| t <sub>EABRCREG</sub>   | 4.7         |     | 4.9 |     | 4.9 |     | ns |  |

| t <sub>EABWP</sub>      | 2.7         |     | 2.8 |     | 2.8 |     | ns |  |

| t <sub>EABWCCOMB</sub>  | 6.4         |     | 6.7 |     | 6.7 |     | ns |  |

| t <sub>EABWCREG</sub>   | 7.4         |     | 7.6 |     | 7.6 |     | ns |  |

| t <sub>EABDD</sub>      |             | 6.0 |     | 6.5 |     | 6.5 | ns |  |

| t <sub>EABDATA</sub> CO |             | 0.8 |     | 0.9 |     | 0.9 | ns |  |

| t <sub>EABDATASU</sub>  | 1.6         |     | 1.7 |     | 1.7 |     | ns |  |

| t <sub>EABDATAH</sub>   | 0.0         |     | 0.0 |     | 0.0 |     | ns |  |

| t <sub>EABWESU</sub>    | 1.4         |     | 1.4 |     | 1.4 |     | ns |  |

| t <sub>EABWEH</sub>     | 0.1         |     | 0.0 |     | 0.0 |     | ns |  |

| t <sub>EABWDSU</sub>    | 1.6         |     | 1.7 |     | 1.7 |     | ns |  |

| t <sub>EABWDH</sub>     | 0.0         |     | 0.0 |     | 0.0 |     | ns |  |

| t <sub>EABWASU</sub>    | 3.1         |     | 3.4 |     | 3.4 |     | ns |  |

| t <sub>EABWAH</sub>     | 0.6         |     | 0.5 |     | 0.5 |     | ns |  |

| t <sub>EABWO</sub>      |             | 5.4 |     | 5.8 |     | 5.8 | ns |  |

| Symbol                   | Speed Grade |     |     |     |     |     |    |  |  |

|--------------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                          | -1          |     | -2  |     | -3  |     |    |  |  |

|                          | Min         | Max | Min | Max | Min | Max |    |  |  |

| t <sub>DIN2IOE</sub>     |             | 2.3 |     | 2.7 |     | 3.6 | ns |  |  |

| t <sub>DIN2LE</sub>      |             | 0.8 |     | 1.1 |     | 1.4 | ns |  |  |

| t <sub>DIN2DATA</sub>    |             | 1.1 |     | 1.4 |     | 1.8 | ns |  |  |

| t <sub>DCLK2IOE</sub>    |             | 2.3 |     | 2.7 |     | 3.6 | ns |  |  |

| t <sub>DCLK2LE</sub>     |             | 0.8 |     | 1.1 |     | 1.4 | ns |  |  |

| t <sub>SAMELAB</sub>     |             | 0.1 |     | 0.1 |     | 0.2 | ns |  |  |

| t <sub>SAMEROW</sub>     |             | 1.8 |     | 2.1 |     | 2.9 | ns |  |  |

| t <sub>SAME</sub> COLUMN |             | 0.3 |     | 0.4 |     | 0.7 | ns |  |  |

| t <sub>DIFFROW</sub>     |             | 2.1 |     | 2.5 |     | 3.6 | ns |  |  |

| t <sub>TWOROWS</sub>     |             | 3.9 |     | 4.6 |     | 6.5 | ns |  |  |

| t <sub>LEPERIPH</sub>    |             | 3.3 |     | 3.7 |     | 4.8 | ns |  |  |

| t <sub>LABCARRY</sub>    |             | 0.3 |     | 0.4 |     | 0.5 | ns |  |  |

| t <sub>LABCASC</sub>     |             | 0.9 |     | 1.0 |     | 1.4 | ns |  |  |

| Table 35. EP1K10            | ) External Ti | ming Param | eters No | te (1) |     |      |    |

|-----------------------------|---------------|------------|----------|--------|-----|------|----|

| Symbol                      |               | Unit       |          |        |     |      |    |

|                             | -             | 1          | -        | 2      | -   | 3    |    |

|                             | Min           | Max        | Min      | Max    | Min | Max  |    |

| t <sub>DRR</sub>            |               | 7.5        |          | 9.5    |     | 12.5 | ns |

| t <sub>INSU</sub> (2), (3)  | 2.4           |            | 2.7      |        | 3.6 |      | ns |

| t <sub>INH</sub> (2), (3)   | 0.0           |            | 0.0      |        | 0.0 |      | ns |

| t <sub>оитсо</sub> (2), (3) | 2.0           | 6.6        | 2.0      | 7.8    | 2.0 | 9.6  | ns |

| t <sub>INSU</sub> (4), (3)  | 1.4           |            | 1.7      |        | -   |      | ns |

| t <sub>INH</sub> (4), (3)   | 0.5           | 5.1        | 0.5      | 6.4    | -   | _    | ns |

| t <sub>оитсо</sub> (4), (3) | 0.0           |            | 0.0      |        | _   |      | ns |

| t <sub>PCISU</sub> (3)      | 3.0           |            | 4.2      |        | 6.4 |      | ns |

| t <sub>PCIH</sub> (3)       | 0.0           |            | 0.0      |        | -   |      | ns |

| t <sub>PCICO</sub> (3)      | 2.0           | 6.0        | 2.0      | 7.5    | 2.0 | 10.2 | ns |

**ACEX 1K Programmable Logic Device Family Data Sheet**

| Symbol                 | Speed Grade |     |     |     |     |     |    |  |

|------------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                        | -1          |     | -2  |     | -3  |     |    |  |

|                        | Min         | Max | Min | Max | Min | Max |    |  |

| t <sub>EABAA</sub>     |             | 6.4 |     | 7.6 |     | 8.8 | ns |  |

| t <sub>EABRCOMB</sub>  | 6.4         |     | 7.6 |     | 8.8 |     | ns |  |

| t <sub>EABRCREG</sub>  | 4.4         |     | 5.1 |     | 6.0 |     | ns |  |

| t <sub>EABWP</sub>     | 2.5         |     | 2.9 | -   | 3.3 |     | ns |  |

| t <sub>EABWCOMB</sub>  | 6.0         |     | 7.0 |     | 8.0 |     | ns |  |

| t <sub>EABWCREG</sub>  | 6.8         |     | 7.8 |     | 9.0 |     | ns |  |

| t <sub>EABDD</sub>     |             | 5.7 |     | 6.7 |     | 7.7 | ns |  |

| t <sub>EABDATACO</sub> |             | 0.8 |     | 0.9 |     | 1.1 | ns |  |

| t <sub>EABDATASU</sub> | 1.5         |     | 1.7 |     | 2.0 |     | ns |  |

| t <sub>EABDATAH</sub>  | 0.0         |     | 0.0 |     | 0.0 |     | ns |  |

| t <sub>EABWESU</sub>   | 1.3         |     | 1.4 |     | 1.7 |     | ns |  |

| t <sub>EABWEH</sub>    | 0.0         |     | 0.0 |     | 0.0 |     | ns |  |

| t <sub>EABWDSU</sub>   | 1.5         |     | 1.7 |     | 2.0 |     | ns |  |

| t <sub>EABWDH</sub>    | 0.0         |     | 0.0 |     | 0.0 |     | ns |  |

| t <sub>EABWASU</sub>   | 3.0         |     | 3.6 |     | 4.3 |     | ns |  |

| t <sub>EABWAH</sub>    | 0.5         |     | 0.5 |     | 0.4 |     | ns |  |

| t <sub>EABWO</sub>     |             | 5.1 |     | 6.0 |     | 6.8 | ns |  |

| Symbol                 | Speed Grade |     |     |     |     |     |    |  |

|------------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                        | -1          |     | -2  |     | -3  |     |    |  |

|                        | Min         | Max | Min | Max | Min | Max |    |  |

| t <sub>EABDATA1</sub>  |             | 1.7 |     | 2.4 |     | 3.2 | ns |  |

| t <sub>EABDATA2</sub>  |             | 0.4 |     | 0.6 |     | 0.8 | ns |  |

| t <sub>EABWE1</sub>    |             | 1.0 |     | 1.4 |     | 1.9 | ns |  |

| t <sub>EABWE2</sub>    |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>EABRE1</sub>    |             | 0.0 |     | 0.0 |     | 0.0 |    |  |

| t <sub>EABRE2</sub>    |             | 0.4 |     | 0.6 |     | 0.8 | -  |  |

| t <sub>EABCLK</sub>    |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>EABCO</sub>     |             | 0.8 |     | 1.1 |     | 1.5 | ns |  |

| t <sub>EABBYPASS</sub> |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>EABSU</sub>     | 0.7         |     | 1.0 |     | 1.3 |     | ns |  |

| t <sub>EABH</sub>      | 0.4         |     | 0.6 |     | 0.8 |     | ns |  |

| t <sub>EABCLR</sub>    | 0.8         |     | 1.1 |     | 1.5 |     |    |  |

| $t_{AA}$               |             | 2.0 |     | 2.8 |     | 3.8 | ns |  |

| $t_{WP}$               | 2.0         |     | 2.8 |     | 3.8 |     | ns |  |

| t <sub>RP</sub>        | 1.0         |     | 1.4 |     | 1.9 |     |    |  |

| t <sub>WDSU</sub>      | 0.5         |     | 0.7 |     | 0.9 |     | ns |  |

| t <sub>WDH</sub>       | 0.1         |     | 0.1 |     | 0.2 |     | ns |  |

| t <sub>WASU</sub>      | 1.0         |     | 1.4 |     | 1.9 |     | ns |  |

| t <sub>WAH</sub>       | 1.5         |     | 2.1 |     | 2.9 |     | ns |  |

| t <sub>RASU</sub>      | 1.5         |     | 2.1 |     | 2.8 |     |    |  |

| t <sub>RAH</sub>       | 0.1         |     | 0.1 |     | 0.2 |     |    |  |

| $t_{WO}$               |             | 2.1 |     | 2.9 |     | 4.0 | ns |  |

| t <sub>DD</sub>        |             | 2.1 |     | 2.9 |     | 4.0 | ns |  |

| t <sub>EABOUT</sub>    |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>EABCH</sub>     | 1.5         |     | 2.0 |     | 2.5 |     | ns |  |

| t <sub>EABCL</sub>     | 1.5         |     | 2.0 |     | 2.5 |     | ns |  |