Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 72                                                       |

| Number of Logic Elements/Cells | 576                                                      |

| Total RAM Bits                 | 12288                                                    |

| Number of I/O                  | 66                                                       |

| Number of Gates                | 56000                                                    |

| Voltage - Supply               | 2.375V ~ 2.625V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 85°C (TA)                                        |

| Package / Case                 | 100-TQFP                                                 |

| Supplier Device Package        | 100-TQFP (14x14)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1k10ti100-2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Embedded Array Block**

The EAB is a flexible block of RAM, with registers on the input and output ports, that is used to implement common gate array megafunctions. Because it is large and flexible, the EAB is suitable for functions such as multipliers, vector scalars, and error correction circuits. These functions can be combined in applications such as digital filters and microcontrollers.

Logic functions are implemented by programming the EAB with a read-only pattern during configuration, thereby creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of EABs. The large capacity of EABs enables designers to implement complex functions in a single logic level without the routing delays associated with linked LEs or field-programmable gate array (FPGA) RAM blocks. For example, a single EAB can implement any function with 8 inputs and 16 outputs. Parameterized functions, such as LPM functions, can take advantage of the EAB automatically.

The ACEX 1K enhanced EAB supports dual-port RAM. The dual-port structure is ideal for FIFO buffers with one or two clocks. The ACEX 1K EAB can also support up to 16-bit-wide RAM blocks. The ACEX 1K EAB can act in dual-port or single-port mode. When in dual-port mode, separate clocks may be used for EAB read and write sections, allowing the EAB to be written and read at different rates. It also has separate synchronous clock enable signals for the EAB read and write sections, which allow independent control of these sections.

The EAB can also be used for bidirectional, dual-port memory applications where two ports read or write simultaneously. To implement this type of dual-port memory, two EABs are used to support two simultaneous reads or writes.

Alternatively, one clock and clock enable can be used to control the input registers of the EAB, while a different clock and clock enable control the output registers (see Figure 2).

EABs can be used to implement synchronous RAM, which is easier to use than asynchronous RAM. A circuit using asynchronous RAM must generate the RAM write enable signal, while ensuring that its data and address signals meet setup and hold time specifications relative to the write enable signal. In contrast, the EAB's synchronous RAM generates its own write enable signal and is self-timed with respect to the input or write clock. A circuit using the EAB's self-timed RAM must only meet the setup and hold time specifications of the global clock.

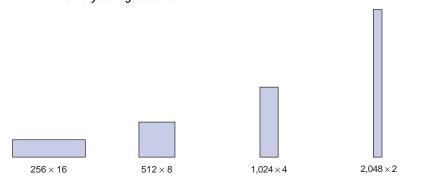

When used as RAM, each EAB can be configured in any of the following sizes:  $256 \times 16$ ;  $512 \times 8$ ;  $1,024 \times 4$ ; or  $2,048 \times 2$ . Figure 5 shows the ACEX 1K EAB memory configurations.

Figure 5. ACEX 1K EAB Memory Configurations

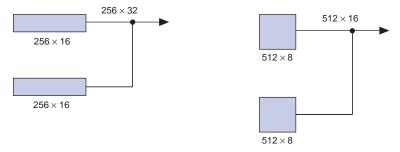

Larger blocks of RAM are created by combining multiple EABs. For example, two  $256 \times 16$  RAM blocks can be combined to form a  $256 \times 32$  block, and two  $512 \times 8$  RAM blocks can be combined to form a  $512 \times 16$  block. Figure 6 shows examples of multiple EAB combination.

Figure 6. Examples of Combining ACEX 1K EABs

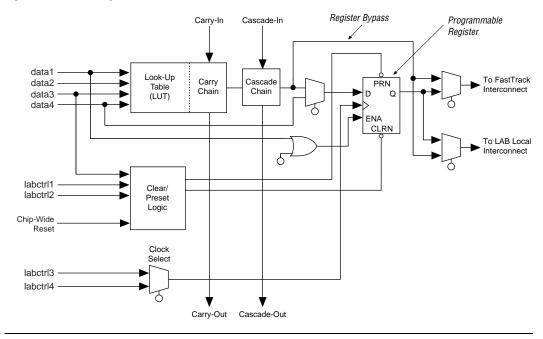

Figure 8. ACEX 1K Logic Element

The programmable flipflop in the LE can be configured for D, T, JK, or SR operation. The clock, clear, and preset control signals on the flipflop can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the flipflop is bypassed and the LUT's output drives the LE's output.

The LE has two outputs that drive the interconnect: one drives the local interconnect, and the other drives either the row or column FastTrack Interconnect routing structure. The two outputs can be controlled independently. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, can improve LE utilization because the register and the LUT can be used for unrelated functions.

The ACEX 1K architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. The carry chain supports high-speed counters and adders, and the cascade chain implements wide-input functions with minimum delay. Carry and cascade chains connect all LEs in a LAB and all LABs in the same row. Intensive use of carry and cascade chains can reduce routing flexibility. Therefore, the use of these chains should be limited to speed-critical portions of a design.

### LE Operating Modes

The ACEX 1K LE can operate in the following four modes:

- Normal mode

- Arithmetic mode

- Up/down counter mode

- Clearable counter mode

Each of these modes uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. Three inputs to the LE provide clock, clear, and preset control for the register. The Altera software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions that use a specific LE operating mode for optimal performance.

The architecture provides a synchronous clock enable to the register in all four modes. The Altera software can set DATA1 to enable the register synchronously, providing easy implementation of fully synchronous designs.

Figure 11 shows the ACEX 1K LE operating modes.

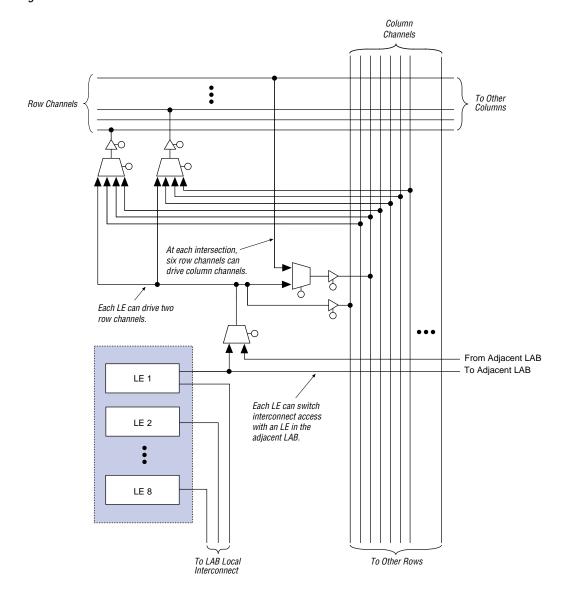

Figure 13. ACEX 1K LAB Connections to Row & Column Interconnect

For improved routing, the row interconnect consists of a combination of full-length and half-length channels. The full-length channels connect to all LABs in a row; the half-length channels connect to the LABs in half of the row. The EAB can be driven by the half-length channels in the left half of the row and by the full-length channels. The EAB drives out to the full-length channels. In addition to providing a predictable, row-wide interconnect, this architecture provides increased routing resources. Two neighboring LABs can be connected using a half-row channel, thereby saving the other half of the channel for the other half of the row.

Table 6 summarizes the FastTrack Interconnect routing structure resources available in each ACEX 1K device.

| Table 6. ACEX 1 | Table 6. ACEX 1K FastTrack Interconnect Resources |                     |         |                        |  |  |  |

|-----------------|---------------------------------------------------|---------------------|---------|------------------------|--|--|--|

| Device          | Rows                                              | Channels per<br>Row | Columns | Channels per<br>Column |  |  |  |

| EP1K10          | 3                                                 | 144                 | 24      | 24                     |  |  |  |

| EP1K30          | 6                                                 | 216                 | 36      | 24                     |  |  |  |

| EP1K50          | 10                                                | 216                 | 36      | 24                     |  |  |  |

| EP1K100         | 12                                                | 312                 | 52      | 24                     |  |  |  |

In addition to general-purpose I/O pins, ACEX 1K devices have six dedicated input pins that provide low-skew signal distribution across the device. These six inputs can be used for global clock, clear, preset, and peripheral output-enable and clock-enable control signals. These signals are available as control signals for all LABs and IOEs in the device. The dedicated inputs can also be used as general-purpose data inputs because they can feed the local interconnect of each LAB in the device.

Figure 14 shows the interconnection of adjacent LABs and EABs, with row, column, and local interconnects, as well as the associated cascade and carry chains. Each LAB is labeled according to its location: a letter represents the row and a number represents the column. For example, LAB B3 is in row B, column 3.

When dedicated inputs drive non-inverted and inverted peripheral clears, clock enables, and output enables, two signals on the peripheral control bus will be used.

Table 7 lists the sources for each peripheral control signal and shows how the output enable, clock enable, clock, and clear signals share 12 peripheral control signals. Table 7 also shows the rows that can drive global signals.

| Table 7. Peripheral Bus Sources for ACEX Devices |        |        |        |         |  |  |

|--------------------------------------------------|--------|--------|--------|---------|--|--|

| Peripheral Control Signal                        | EP1K10 | EP1K30 | EP1K50 | EP1K100 |  |  |

| OE0                                              | Row A  | Row A  | Row A  | Row A   |  |  |

| OE1                                              | Row A  | Row B  | Row B  | Row C   |  |  |

| OE2                                              | Row B  | Row C  | Row D  | Row E   |  |  |

| OE3                                              | Row B  | Row D  | Row F  | Row L   |  |  |

| OE4                                              | Row C  | Row E  | Row H  | Row I   |  |  |

| OE5                                              | Row C  | Row F  | Row J  | Row K   |  |  |

| CLKENAO/CLKO/GLOBALO                             | Row A  | Row A  | Row A  | Row F   |  |  |

| CLKENA1/OE6/GLOBAL1                              | Row A  | Row B  | Row C  | Row D   |  |  |

| CLKENA2/CLR0                                     | Row B  | Row C  | Row E  | Row B   |  |  |

| CLKENA3/OE7/GLOBAL2                              | Row B  | Row D  | Row G  | Row H   |  |  |

| CLKENA4/CLR1                                     | Row C  | Row E  | Row I  | Row J   |  |  |

| CLKENA5/CLK1/GLOBAL3                             | Row C  | Row F  | Row J  | Row G   |  |  |

Signals on the peripheral control bus can also drive the four global signals, referred to as <code>GLOBALO</code> through <code>GLOBALO</code>. An internally generated signal can drive a global signal, providing the same low-skew, low-delay characteristics as a signal driven by an input pin. An LE drives the global signal by driving a row line that drives the peripheral bus which then drives the global signal. This feature is ideal for internally generated clear or clock signals with high fan-out. However, internally driven global signals offer no advantage over the general-purpose interconnect for routing data signals.

The chip-wide output enable pin is an active-high pin that can be used to tri-state all pins on the device. This option can be set in the Altera software. The built-in I/O pin pull-up resistors (which are active during configuration) are active when the chip-wide output enable pin is asserted. The registers in the IOE can also be reset by the chip-wide reset pin.

#### Row-to-IOE Connections

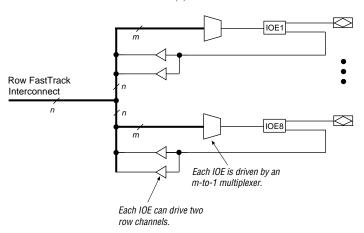

When an IOE is used as an input signal, it can drive two separate row channels. The signal is accessible by all LEs within that row. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the row channels. Up to eight IOEs connect to each side of each row channel (see Figure 16).

Figure 16. ACEX 1K Row-to-IOE Connections Note (1)

#### Note:

(1) The values for m and n are shown in Table 8.

Table 8 lists the ACEX 1K row-to-IOE interconnect resources.

| Table 8. ACEX 1K Row-to-IOE Interconnect Resources |                      |                          |  |  |  |

|----------------------------------------------------|----------------------|--------------------------|--|--|--|

| Device                                             | Channels per Row (n) | Row Channels per Pin (m) |  |  |  |

| EP1K10                                             | 144                  | 18                       |  |  |  |

| EP1K30                                             | 216                  | 27                       |  |  |  |

| EP1K50                                             | 216                  | 27                       |  |  |  |

| EP1K100                                            | 312                  | 39                       |  |  |  |

#### Column-to-IOE Connections

When an IOE is used as an input, it can drive up to two separate column channels. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the column channels. Two IOEs connect to each side of the column channels. Each IOE can be driven by column channels via a multiplexer. The set of column channels is different for each IOE (see Figure 17).

Each IOE is driven by a m-to-1 multiplexer

Column Interconnect

Figure 17. ACEX 1K Column-to-IOE Connections Note (1)

## Note:

The values for m and n are shown in Table 9.

Table 9 lists the ACEX 1K column-to-IOE interconnect resources.

Each IOE can drive two column channels.

| Table 9. ACEX 1K Column-to-IOE Interconnect Resources |                         |                             |  |  |  |  |

|-------------------------------------------------------|-------------------------|-----------------------------|--|--|--|--|

| Device                                                | Channels per Column (n) | Column Channels per Pin (m) |  |  |  |  |

| EP1K10                                                | 24                      | 16                          |  |  |  |  |

| EP1K30                                                | 24                      | 16                          |  |  |  |  |

| EP1K50                                                | 24                      | 16                          |  |  |  |  |

| EP1K100                                               | 24                      | 16                          |  |  |  |  |

The VCCINT pins must always be connected to a 2.5-V power supply. With a 2.5-V  $V_{\rm CCINT}$  level, input voltages are compatible with 2.5-V, 3.3-V, and 5.0-V inputs. The VCCIO pins can be connected to either a 2.5-V or 3.3-V power supply, depending on the output requirements. When the VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is at 3.3 V and is therefore compatible with 3.3-V or 5.0-V systems. Devices operating with  $V_{\rm CCIO}$  levels higher than 3.0 V achieve a faster timing delay of  $t_{OD2}$  instead of  $t_{OD1}$ .

Table 13 summarizes ACEX 1K MultiVolt I/O support.

| Table 13. ACEX 1      | K MultiVo | It I/O Supp  | oort         |              |            |          |

|-----------------------|-----------|--------------|--------------|--------------|------------|----------|

| V <sub>CCIO</sub> (V) | Inp       | out Signal   | (V)          | Out          | put Signal | (V)      |

|                       | 2.5       | 3.3          | 5.0          | 2.5          | 3.3        | 5.0      |

| 2.5                   | <b>✓</b>  | <b>√</b> (1) | <b>√</b> (1) | ✓            |            |          |

| 3.3                   | <b>✓</b>  | <b>✓</b>     | <b>√</b> (1) | <b>√</b> (2) | <b>✓</b>   | <b>✓</b> |

#### Notes:

- (1) The PCI clamping diode must be disabled on an input which is driven with a voltage higher than  $V_{\rm CCIO}$ .

- (2) When  $V_{\rm CCIO}$  = 3.3 V, an ACEX 1K device can drive a 2.5-V device that has 3.3-V tolerant inputs.

Open-drain output pins on ACEX 1K devices (with a pull-up resistor to the 5.0-V supply) can drive 5.0-V CMOS input pins that require a higher  $V_{IH}$  than LVTTL. When the open-drain pin is active, it will drive low. When the pin is inactive, the resistor will pull up the trace to 5.0 V, thereby meeting the CMOS  $V_{OH}$  requirement. The open-drain pin will only drive low or tri-state; it will never drive high. The rise time is dependent on the value of the pull-up resistor and load impedance. The  $I_{OL}$  current specification should be considered when selecting a pull-up resistor.

## Power Sequencing & Hot-Socketing

Because ACEX 1K devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. The  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  power planes can be powered in any order.

Signals can be driven into ACEX 1K devices before and during power up without damaging the device. Additionally, ACEX 1K devices do not drive out during power up. Once operating conditions are reached, ACEX 1K devices operate as specified by the user.

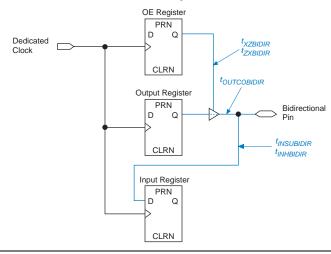

Figure 28. Synchronous Bidirectional Pin External Timing Model

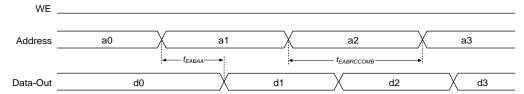

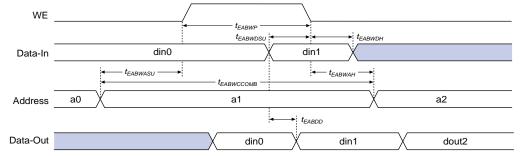

Tables 29 and 30 show the asynchronous and synchronous timing waveforms, respectively, for the EAB macroparameters in Table 24.

Figure 29. EAB Asynchronous Timing Waveforms

#### **EAB Asynchronous Write**

| Table 22. LE      | Timing Microparameters (Part 2 of 2) Note (1)                                                                                        |            |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|

| Symbol            | Parameter                                                                                                                            | Conditions |

| t <sub>CASC</sub> | Cascade-in to cascade-out delay                                                                                                      |            |

| $t_{C}$           | LE register control signal delay                                                                                                     |            |

| $t_{CO}$          | LE register clock-to-output delay                                                                                                    |            |

| t <sub>COMB</sub> | Combinatorial delay                                                                                                                  |            |

| t <sub>SU</sub>   | LE register setup time for data and enable signals before clock; LE register recovery time after asynchronous clear, preset, or load |            |

| $t_H$             | LE register hold time for data and enable signals after clock                                                                        |            |

| t <sub>PRE</sub>  | LE register preset delay                                                                                                             |            |

| t <sub>CLR</sub>  | LE register clear delay                                                                                                              |            |

| t <sub>CH</sub>   | Minimum clock high time from clock pin                                                                                               |            |

| $t_{CL}$          | Minimum clock low time from clock pin                                                                                                |            |

| Table 23. IOE       | Timing Microparameters Note (1)                                                                                       |                |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|----------------|

| Symbol              | Parameter                                                                                                             | Conditions     |

| $t_{IOD}$           | IOE data delay                                                                                                        |                |

| $t_{IOC}$           | IOE register control signal delay                                                                                     |                |

| $t_{IOCO}$          | IOE register clock-to-output delay                                                                                    |                |

| $t_{IOCOMB}$        | IOE combinatorial delay                                                                                               |                |

| t <sub>IOSU</sub>   | IOE register setup time for data and enable signals before clock; IOE register recovery time after asynchronous clear |                |

| $t_{IOH}$           | IOE register hold time for data and enable signals after clock                                                        |                |

| t <sub>IOCLR</sub>  | IOE register clear time                                                                                               |                |

| t <sub>OD1</sub>    | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = 3.3 V                                          | C1 = 35 pF (2) |

| $t_{OD2}$           | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = 2.5 V                                          | C1 = 35 pF (3) |

| $t_{OD3}$           | Output buffer and pad delay, slow slew rate = on                                                                      | C1 = 35 pF (4) |

| $t_{XZ}$            | IOE output buffer disable delay                                                                                       |                |

| $t_{ZX1}$           | IOE output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = 3.3 V                                       | C1 = 35 pF (2) |

| $t_{ZX2}$           | IOE output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = 2.5 V                                       | C1 = 35 pF (3) |

| $t_{ZX3}$           | IOE output buffer enable delay, slow slew rate = on                                                                   | C1 = 35 pF (4) |

| t <sub>INREG</sub>  | IOE input pad and buffer to IOE register delay                                                                        | -              |

| $t_{IOFD}$          | IOE register feedback delay                                                                                           |                |

| t <sub>INCOMB</sub> | IOE input pad and buffer to FastTrack Interconnect delay                                                              |                |

| Symbol                   | Parameter                                                                                                            | Conditions |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|------------|

| t <sub>DIN2IOE</sub>     | Delay from dedicated input pin to IOE control input                                                                  | (7)        |

| t <sub>DIN2LE</sub>      | Delay from dedicated input pin to LE or EAB control input                                                            | (7)        |

| t <sub>DIN2DATA</sub>    | Delay from dedicated input or clock to LE or EAB data                                                                | (7)        |

| t <sub>DCLK2IOE</sub>    | Delay from dedicated clock pin to IOE clock                                                                          | (7)        |

| t <sub>DCLK2LE</sub>     | Delay from dedicated clock pin to LE or EAB clock                                                                    | (7)        |

| t <sub>SAMELAB</sub>     | Routing delay for an LE driving another LE in the same LAB                                                           | (7)        |

| t <sub>SAMEROW</sub>     | Routing delay for a row IOE, LE, or EAB driving a row IOE, LE, or EAB in the same row                                | (7)        |

| t <sub>SAME</sub> COLUMN | Routing delay for an LE driving an IOE in the same column                                                            | (7)        |

| t <sub>DIFFROW</sub>     | Routing delay for a column IOE, LE, or EAB driving an LE or EAB in a different row                                   | (7)        |

| t <sub>TWOROWS</sub>     | Routing delay for a row IOE or EAB driving an LE or EAB in a different row                                           | (7)        |

| t <sub>LEPERIPH</sub>    | Routing delay for an LE driving a control signal of an IOE via the peripheral control bus                            | (7)        |

| t <sub>LABCARRY</sub>    | Routing delay for the carry-out signal of an LE driving the carry-in signal of a different LE in a different LAB     |            |

| t <sub>LABCASC</sub>     | Routing delay for the cascade-out signal of an LE driving the cascade-in signal of a different LE in a different LAB |            |

#### Notes to tables:

- Microparameters are timing delays contributed by individual architectural elements. These parameters cannot be measured explicitly.

- Operating conditions:  $V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial or industrial and extended use in ACEX 1K devices

- Operating conditions:  $V_{CCIO} = 2.5 \text{ V} \pm 5\%$  for commercial or industrial and extended use in ACEX 1K devices. Operating conditions:  $V_{CCIO} = 2.5 \text{ V} \text{ or } 3.3 \text{ V}$ . (3)

- (4)

- Because the RAM in the EAB is self-timed, this parameter can be ignored when the WE signal is registered.

- EAB macroparameters are internal parameters that can simplify predicting the behavior of an EAB at its boundary; these parameters are calculated by summing selected microparameters.

- These parameters are worst-case values for typical applications. Post-compilation timing simulation and timing analysis are required to determine actual worst-case performance.

Tables 30 through 36 show EP1K10 device internal and external timing parameters.

| Symbol              | Speed Grade |     |     |     |     |     |    |

|---------------------|-------------|-----|-----|-----|-----|-----|----|

|                     | -1          |     | -   | -2  |     | 3   |    |

|                     | Min         | Max | Min | Max | Min | Max |    |

| $t_{LUT}$           |             | 0.7 |     | 0.8 |     | 1.1 | ns |

| t <sub>CLUT</sub>   |             | 0.5 |     | 0.6 |     | 0.8 | ns |

| t <sub>RLUT</sub>   |             | 0.6 |     | 0.7 |     | 1.0 | ns |

| t <sub>PACKED</sub> |             | 0.4 |     | 0.4 |     | 0.5 | ns |

| t <sub>EN</sub>     |             | 0.9 |     | 1.0 |     | 1.3 | ns |

| t <sub>CICO</sub>   |             | 0.1 |     | 0.1 |     | 0.2 | ns |

| t <sub>CGEN</sub>   |             | 0.4 |     | 0.5 |     | 0.7 | ns |

| t <sub>CGENR</sub>  |             | 0.1 |     | 0.1 |     | 0.2 | ns |

| t <sub>CASC</sub>   |             | 0.7 |     | 0.9 |     | 1.1 | ns |

| $t_C$               |             | 1.1 |     | 1.3 |     | 1.7 | ns |

| $t_{CO}$            |             | 0.5 |     | 0.7 |     | 0.9 | ns |

| t <sub>COMB</sub>   |             | 0.4 |     | 0.5 |     | 0.7 | ns |

| t <sub>SU</sub>     | 0.7         |     | 0.8 |     | 1.0 |     | ns |

| t <sub>H</sub>      | 0.9         |     | 1.0 |     | 1.1 |     | ns |

| t <sub>PRE</sub>    |             | 0.8 |     | 1.0 |     | 1.4 | ns |

| t <sub>CLR</sub>    |             | 0.9 |     | 1.0 |     | 1.4 | ns |

| t <sub>CH</sub>     | 2.0         |     | 2.5 |     | 2.5 |     | ns |

| $t_{CL}$            | 2.0         |     | 2.5 |     | 2.5 |     | ns |

| Symbol                 | Speed Grade |     |     |     |     |     |    |

|------------------------|-------------|-----|-----|-----|-----|-----|----|

|                        | -1          |     | -   | -2  |     | 3   |    |

|                        | Min         | Max | Min | Max | Min | Max |    |

| t <sub>EABDATA1</sub>  |             | 1.8 |     | 1.9 |     | 1.9 | ns |

| t <sub>EABDATA2</sub>  |             | 0.6 |     | 0.7 |     | 0.7 | ns |

| t <sub>EABWE1</sub>    |             | 1.2 |     | 1.2 |     | 1.2 | ns |

| t <sub>EABWE2</sub>    |             | 0.4 |     | 0.4 |     | 0.4 | ns |

| t <sub>EABRE1</sub>    |             | 0.9 |     | 0.9 |     | 0.9 | ns |

| t <sub>EABRE2</sub>    |             | 0.4 |     | 0.4 |     | 0.4 | ns |

| t <sub>EABCLK</sub>    |             | 0.0 |     | 0.0 |     | 0.0 | ns |

| t <sub>EABCO</sub>     |             | 0.3 |     | 0.3 |     | 0.3 | ns |

| t <sub>EABBYPASS</sub> |             | 0.5 |     | 0.6 |     | 0.6 | ns |

| t <sub>EABSU</sub>     | 1.0         |     | 1.0 |     | 1.0 |     | ns |

| t <sub>EABH</sub>      | 0.5         |     | 0.4 |     | 0.4 |     | ns |

| t <sub>EABCLR</sub>    | 0.3         |     | 0.3 |     | 0.3 |     | ns |

| $t_{AA}$               |             | 3.4 |     | 3.6 |     | 3.6 | ns |

| $t_{WP}$               | 2.7         |     | 2.8 |     | 2.8 |     | ns |

| $t_{RP}$               | 1.0         |     | 1.0 |     | 1.0 |     | ns |

| t <sub>WDSU</sub>      | 1.0         |     | 1.0 |     | 1.0 |     | ns |

| t <sub>WDH</sub>       | 0.1         |     | 0.1 |     | 0.1 |     | ns |

| t <sub>WASU</sub>      | 1.8         |     | 1.9 |     | 1.9 |     | ns |

| t <sub>WAH</sub>       | 1.9         |     | 2.0 |     | 2.0 |     | ns |

| t <sub>RASU</sub>      | 3.1         |     | 3.5 |     | 3.5 |     | ns |

| t <sub>RAH</sub>       | 0.2         |     | 0.2 |     | 0.2 |     | ns |

| $t_{WO}$               |             | 2.7 |     | 2.8 |     | 2.8 | ns |

| $t_{DD}$               |             | 2.7 |     | 2.8 |     | 2.8 | ns |

| t <sub>EABOUT</sub>    |             | 0.5 |     | 0.6 |     | 0.6 | ns |

| t <sub>EABCH</sub>     | 1.5         |     | 2.0 |     | 2.0 |     | ns |

| t <sub>EABCL</sub>     | 2.7         |     | 2.8 |     | 2.8 |     | ns |

| Symbol                   |     |     | Speed | Grade |     |     | Unit |

|--------------------------|-----|-----|-------|-------|-----|-----|------|

|                          | -1  |     | -2    |       | -3  |     |      |

|                          | Min | Max | Min   | Max   | Min | Max |      |

| t <sub>DIN2IOE</sub>     |     | 2.3 |       | 2.7   |     | 3.6 | ns   |

| t <sub>DIN2LE</sub>      |     | 0.8 |       | 1.1   |     | 1.4 | ns   |

| t <sub>DIN2DATA</sub>    |     | 1.1 |       | 1.4   |     | 1.8 | ns   |

| t <sub>DCLK2IOE</sub>    |     | 2.3 |       | 2.7   |     | 3.6 | ns   |

| t <sub>DCLK2LE</sub>     |     | 0.8 |       | 1.1   |     | 1.4 | ns   |

| t <sub>SAMELAB</sub>     |     | 0.1 |       | 0.1   |     | 0.2 | ns   |

| t <sub>SAMEROW</sub>     |     | 1.8 |       | 2.1   |     | 2.9 | ns   |

| t <sub>SAME</sub> COLUMN |     | 0.3 |       | 0.4   |     | 0.7 | ns   |

| t <sub>DIFFROW</sub>     |     | 2.1 |       | 2.5   |     | 3.6 | ns   |

| t <sub>TWOROWS</sub>     |     | 3.9 |       | 4.6   |     | 6.5 | ns   |

| t <sub>LEPERIPH</sub>    |     | 3.3 |       | 3.7   |     | 4.8 | ns   |

| t <sub>LABCARRY</sub>    |     | 0.3 |       | 0.4   |     | 0.5 | ns   |

| t <sub>LABCASC</sub>     |     | 0.9 |       | 1.0   |     | 1.4 | ns   |

| Table 35. EP1K10            | ) External Ti | ming Param | eters No | te (1) |     |      |    |

|-----------------------------|---------------|------------|----------|--------|-----|------|----|

| Symbol                      |               | Unit       |          |        |     |      |    |

|                             | -             | 1          | -        | 2      | -   | 3    |    |

|                             | Min           | Max        | Min      | Max    | Min | Max  |    |

| t <sub>DRR</sub>            |               | 7.5        |          | 9.5    |     | 12.5 | ns |

| t <sub>INSU</sub> (2), (3)  | 2.4           |            | 2.7      |        | 3.6 |      | ns |

| t <sub>INH</sub> (2), (3)   | 0.0           |            | 0.0      |        | 0.0 |      | ns |

| t <sub>оитсо</sub> (2), (3) | 2.0           | 6.6        | 2.0      | 7.8    | 2.0 | 9.6  | ns |

| t <sub>INSU</sub> (4), (3)  | 1.4           |            | 1.7      |        | _   |      | ns |

| t <sub>INH</sub> (4), (3)   | 0.5           | 5.1        | 0.5      | 6.4    | _   | _    | ns |

| t <sub>оитсо</sub> (4), (3) | 0.0           |            | 0.0      |        | _   |      | ns |

| t <sub>PCISU</sub> (3)      | 3.0           |            | 4.2      |        | 6.4 |      | ns |

| t <sub>PCIH</sub> (3)       | 0.0           |            | 0.0      |        | -   |      | ns |

| t <sub>PCICO</sub> (3)      | 2.0           | 6.0        | 2.0      | 7.5    | 2.0 | 10.2 | ns |

| Symbol                   | Speed Grade |     |     |     |     |     |    |  |

|--------------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                          | -1          |     | -2  |     | -3  |     |    |  |

|                          | Min         | Max | Min | Max | Min | Max |    |  |

| DIN2IOE                  |             | 1.8 |     | 2.4 |     | 2.9 | ns |  |

| t <sub>DIN2LE</sub>      |             | 1.5 |     | 1.8 |     | 2.4 | ns |  |

| t <sub>DIN2DATA</sub>    |             | 1.5 |     | 1.8 |     | 2.2 | ns |  |

| t <sub>DCLK2IOE</sub>    |             | 2.2 |     | 2.6 |     | 3.0 | ns |  |

| t <sub>DCLK2LE</sub>     |             | 1.5 |     | 1.8 |     | 2.4 | ns |  |

| t <sub>SAMELAB</sub>     |             | 0.1 |     | 0.2 |     | 0.3 | ns |  |

| t <sub>SAMEROW</sub>     |             | 2.0 |     | 2.4 |     | 2.7 | ns |  |

| t <sub>SAME</sub> COLUMN |             | 0.7 |     | 1.0 |     | 0.8 | ns |  |

| t <sub>DIFFROW</sub>     |             | 2.7 |     | 3.4 |     | 3.5 | ns |  |

| t <sub>TWOROWS</sub>     |             | 4.7 |     | 5.8 |     | 6.2 | ns |  |

| LEPERIPH                 |             | 2.7 |     | 3.4 |     | 3.8 | ns |  |

| LABCARRY                 |             | 0.3 |     | 0.4 |     | 0.5 | ns |  |

| t <sub>LABCASC</sub>     |             | 0.8 |     | 0.8 |     | 1.1 | ns |  |

| Table 42. EP1K3        | 0 External Ti | ming Param | <b>eters</b> Not | es (1), (2) |     |      |    |

|------------------------|---------------|------------|------------------|-------------|-----|------|----|

| Symbol                 |               | Unit       |                  |             |     |      |    |

|                        |               | -1         | -                | 2           | -   | 3    |    |

|                        | Min           | Max        | Min              | Max         | Min | Max  |    |

| t <sub>DRR</sub>       |               | 8.0        |                  | 9.5         |     | 12.5 | ns |

| t <sub>INSU</sub> (3)  | 2.1           |            | 2.5              |             | 3.9 |      | ns |

| t <sub>INH</sub> (3)   | 0.0           |            | 0.0              |             | 0.0 |      | ns |

| t <sub>оитсо</sub> (3) | 2.0           | 4.9        | 2.0              | 5.9         | 2.0 | 7.6  | ns |

| t <sub>INSU</sub> (4)  | 1.1           |            | 1.5              |             | -   |      | ns |

| t <sub>INH</sub> (4)   | 0.0           |            | 0.0              |             | -   |      | ns |

| t <sub>оитсо</sub> (4) | 0.5           | 3.9        | 0.5              | 4.9         | -   | -    | ns |

| t <sub>PCISU</sub>     | 3.0           |            | 4.2              |             | -   |      | ns |

| t <sub>PCIH</sub>      | 0.0           |            | 0.0              |             | -   |      | ns |

| t <sub>PCICO</sub>     | 2.0           | 6.0        | 2.0              | 7.5         | -   | -    | ns |

| Symbol            |     | Speed Grade |     |     |     |     |    |  |  |

|-------------------|-----|-------------|-----|-----|-----|-----|----|--|--|

|                   | -1  |             | -2  |     | -3  |     |    |  |  |

|                   | Min | Max         | Min | Max | Min | Max |    |  |  |

| $t_{CO}$          |     | 0.6         |     | 0.6 |     | 0.7 | ns |  |  |

| t <sub>COMB</sub> |     | 0.3         |     | 0.4 |     | 0.5 | ns |  |  |

| t <sub>SU</sub>   | 0.5 |             | 0.6 |     | 0.7 |     | ns |  |  |

| $t_H$             | 0.5 |             | 0.6 |     | 0.8 |     | ns |  |  |

| t <sub>PRE</sub>  |     | 0.4         |     | 0.5 |     | 0.7 | ns |  |  |

| t <sub>CLR</sub>  |     | 0.8         |     | 1.0 |     | 1.2 | ns |  |  |

| t <sub>CH</sub>   | 2.0 |             | 2.5 |     | 3.0 |     | ns |  |  |

| $t_{CL}$          | 2.0 |             | 2.5 |     | 3.0 |     | ns |  |  |

| Symbol              | Speed Grade |     |     |     |     |     |    |  |

|---------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                     | -1          |     | -2  |     | -3  |     |    |  |

|                     | Min         | Max | Min | Max | Min | Max |    |  |

| $t_{IOD}$           |             | 1.3 |     | 1.3 |     | 1.9 | ns |  |

| t <sub>IOC</sub>    |             | 0.3 |     | 0.4 |     | 0.4 | ns |  |

| t <sub>IOCO</sub>   |             | 1.7 |     | 2.1 |     | 2.6 | ns |  |

| t <sub>IOCOMB</sub> |             | 0.5 |     | 0.6 |     | 0.8 | ns |  |

| t <sub>IOSU</sub>   | 0.8         |     | 1.0 |     | 1.3 |     | ns |  |

| t <sub>IOH</sub>    | 0.4         |     | 0.5 |     | 0.6 |     | ns |  |

| t <sub>IOCLR</sub>  |             | 0.2 |     | 0.2 |     | 0.4 | ns |  |

| t <sub>OD1</sub>    |             | 1.2 |     | 1.2 |     | 1.9 | ns |  |

| t <sub>OD2</sub>    |             | 0.7 |     | 0.8 |     | 1.7 | ns |  |

| t <sub>OD3</sub>    |             | 2.7 |     | 3.0 |     | 4.3 | ns |  |

| $t_{XZ}$            |             | 4.7 |     | 5.7 |     | 7.5 | ns |  |

| $t_{ZX1}$           |             | 4.7 |     | 5.7 |     | 7.5 | ns |  |

| $t_{ZX2}$           |             | 4.2 |     | 5.3 |     | 7.3 | ns |  |

| $t_{ZX3}$           |             | 6.2 |     | 7.5 |     | 9.9 | ns |  |

| t <sub>INREG</sub>  |             | 3.5 |     | 4.2 |     | 5.6 | ns |  |

| t <sub>IOFD</sub>   |             | 1.1 |     | 1.3 |     | 1.8 | ns |  |

| t <sub>INCOMB</sub> |             | 1.1 |     | 1.3 |     | 1.8 | ns |  |

| Symbol                 | Speed Grade |     |     |     |     |     |    |  |

|------------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                        | -1          |     | -2  |     | -3  |     |    |  |

|                        | Min         | Max | Min | Max | Min | Max |    |  |

| t <sub>EABDATA1</sub>  |             | 1.7 |     | 2.4 |     | 3.2 | ns |  |

| t <sub>EABDATA2</sub>  |             | 0.4 |     | 0.6 |     | 0.8 | ns |  |

| t <sub>EABWE1</sub>    |             | 1.0 |     | 1.4 |     | 1.9 | ns |  |

| t <sub>EABWE2</sub>    |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>EABRE1</sub>    |             | 0.0 |     | 0.0 |     | 0.0 |    |  |

| t <sub>EABRE2</sub>    |             | 0.4 |     | 0.6 |     | 0.8 | -  |  |

| t <sub>EABCLK</sub>    |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>EABCO</sub>     |             | 0.8 |     | 1.1 |     | 1.5 | ns |  |

| t <sub>EABBYPASS</sub> |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>EABSU</sub>     | 0.7         |     | 1.0 |     | 1.3 |     | ns |  |

| t <sub>EABH</sub>      | 0.4         |     | 0.6 |     | 0.8 |     | ns |  |

| t <sub>EABCLR</sub>    | 0.8         |     | 1.1 |     | 1.5 |     |    |  |

| $t_{AA}$               |             | 2.0 |     | 2.8 |     | 3.8 | ns |  |

| $t_{WP}$               | 2.0         |     | 2.8 |     | 3.8 |     | ns |  |

| $t_{RP}$               | 1.0         |     | 1.4 |     | 1.9 |     |    |  |

| t <sub>WDSU</sub>      | 0.5         |     | 0.7 |     | 0.9 |     | ns |  |

| t <sub>WDH</sub>       | 0.1         |     | 0.1 |     | 0.2 |     | ns |  |

| t <sub>WASU</sub>      | 1.0         |     | 1.4 |     | 1.9 |     | ns |  |

| t <sub>WAH</sub>       | 1.5         |     | 2.1 |     | 2.9 |     | ns |  |

| t <sub>RASU</sub>      | 1.5         |     | 2.1 |     | 2.8 |     |    |  |

| t <sub>RAH</sub>       | 0.1         |     | 0.1 |     | 0.2 |     |    |  |

| $t_{WO}$               |             | 2.1 |     | 2.9 |     | 4.0 | ns |  |

| t <sub>DD</sub>        |             | 2.1 |     | 2.9 |     | 4.0 | ns |  |

| t <sub>EABOUT</sub>    |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>EABCH</sub>     | 1.5         |     | 2.0 |     | 2.5 |     | ns |  |

| t <sub>EABCL</sub>     | 1.5         |     | 2.0 |     | 2.5 |     | ns |  |

| Symbol                  | Speed Grade |     |     |     |      |     |    |  |

|-------------------------|-------------|-----|-----|-----|------|-----|----|--|

|                         | -1          |     | -2  |     | -3   |     |    |  |

|                         | Min         | Max | Min | Max | Min  | Max |    |  |

| t <sub>EABAA</sub>      |             | 3.7 |     | 5.2 |      | 7.0 | ns |  |

| t <sub>EABRCCOMB</sub>  | 3.7         |     | 5.2 |     | 7.0  |     | ns |  |

| t <sub>EABRCREG</sub>   | 3.5         |     | 4.9 |     | 6.6  |     | ns |  |

| t <sub>EABWP</sub>      | 2.0         |     | 2.8 |     | 3.8  |     | ns |  |

| t <sub>EABWCCOMB</sub>  | 4.5         |     | 6.3 |     | 8.6  |     | ns |  |

| t <sub>EABWCREG</sub>   | 5.6         |     | 7.8 |     | 10.6 |     | ns |  |

| t <sub>EABDD</sub>      |             | 3.8 |     | 5.3 |      | 7.2 | ns |  |

| t <sub>EABDATA</sub> CO |             | 0.8 |     | 1.1 |      | 1.5 | ns |  |

| t <sub>EABDATASU</sub>  | 1.1         |     | 1.6 |     | 2.1  |     | ns |  |

| t <sub>EABDATAH</sub>   | 0.0         |     | 0.0 |     | 0.0  |     | ns |  |

| t <sub>EABWESU</sub>    | 0.7         |     | 1.0 |     | 1.3  |     | ns |  |

| t <sub>EABWEH</sub>     | 0.4         |     | 0.6 |     | 0.8  |     | ns |  |

| t <sub>EABWDSU</sub>    | 1.2         |     | 1.7 |     | 2.2  |     | ns |  |

| t <sub>EABWDH</sub>     | 0.0         |     | 0.0 |     | 0.0  |     | ns |  |

| t <sub>EABWASU</sub>    | 1.6         |     | 2.3 |     | 3.0  |     | ns |  |

| t <sub>EABWAH</sub>     | 0.9         |     | 1.2 |     | 1.8  |     | ns |  |

| t <sub>EABWO</sub>      |             | 3.1 |     | 4.3 |      | 5.9 | ns |  |