Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 360                                                       |

| Number of Logic Elements/Cells | 2880                                                      |

| Total RAM Bits                 | 40960                                                     |

| Number of I/O                  | 186                                                       |

| Number of Gates                | 199000                                                    |

| Voltage - Supply               | 2.375V ~ 2.625V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 70°C (TA)                                           |

| Package / Case                 | 256-BGA                                                   |

| Supplier Device Package        | 256-FBGA (17x17)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1k50fc256-2n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

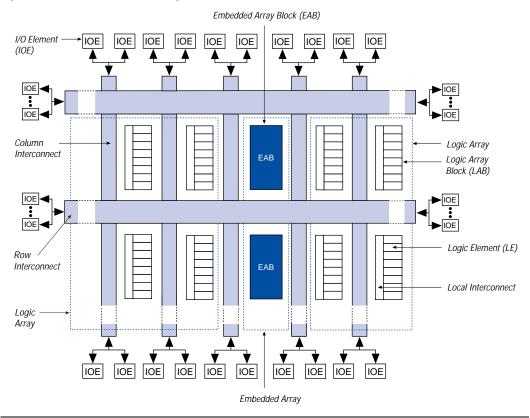

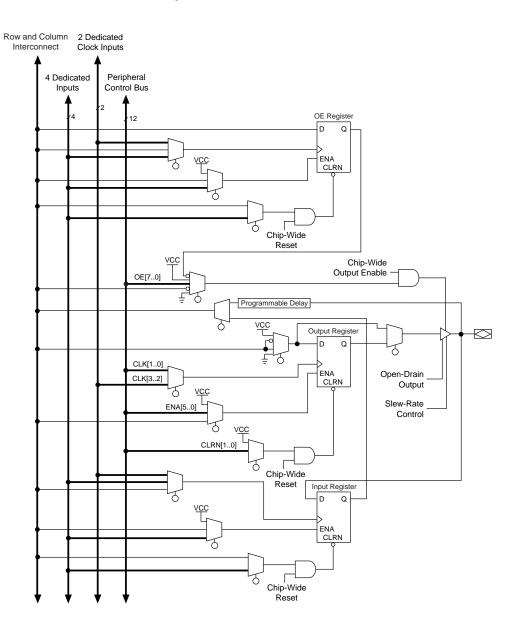

Figure 1. ACEX 1K Device Block Diagram

ACEX 1K devices provide six dedicated inputs that drive the flipflops' control inputs and ensure the efficient distribution of high-speed, low-skew (less than 1.0 ns) control signals. These signals use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect routing structure. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device.

#### **Embedded Array Block**

The EAB is a flexible block of RAM, with registers on the input and output ports, that is used to implement common gate array megafunctions. Because it is large and flexible, the EAB is suitable for functions such as multipliers, vector scalars, and error correction circuits. These functions can be combined in applications such as digital filters and microcontrollers.

Logic functions are implemented by programming the EAB with a read-only pattern during configuration, thereby creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of EABs. The large capacity of EABs enables designers to implement complex functions in a single logic level without the routing delays associated with linked LEs or field-programmable gate array (FPGA) RAM blocks. For example, a single EAB can implement any function with 8 inputs and 16 outputs. Parameterized functions, such as LPM functions, can take advantage of the EAB automatically.

The ACEX 1K enhanced EAB supports dual-port RAM. The dual-port structure is ideal for FIFO buffers with one or two clocks. The ACEX 1K EAB can also support up to 16-bit-wide RAM blocks. The ACEX 1K EAB can act in dual-port or single-port mode. When in dual-port mode, separate clocks may be used for EAB read and write sections, allowing the EAB to be written and read at different rates. It also has separate synchronous clock enable signals for the EAB read and write sections, which allow independent control of these sections.

The EAB can also be used for bidirectional, dual-port memory applications where two ports read or write simultaneously. To implement this type of dual-port memory, two EABs are used to support two simultaneous reads or writes.

Alternatively, one clock and clock enable can be used to control the input registers of the EAB, while a different clock and clock enable control the output registers (see Figure 2).

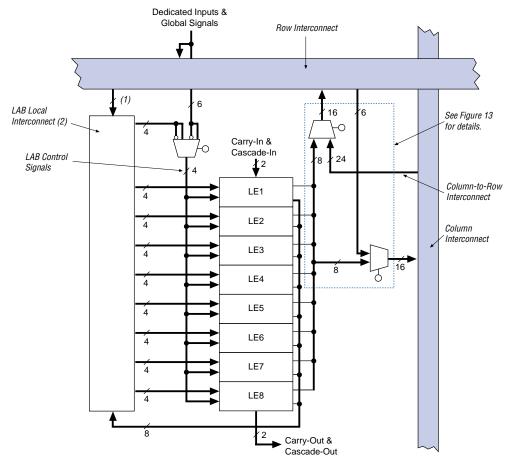

Figure 7. ACEX 1K LAB

#### Notes:

- (1) EP1K10, EP1K30, and EP1K50 devices have 22 inputs to the LAB local interconnect channel from the row; EP1K100 devices have 26.

- (2) EP1K10, EP1K30, and EP1K50 devices have 30 LAB local interconnect channels; EP1K100 devices have 34.

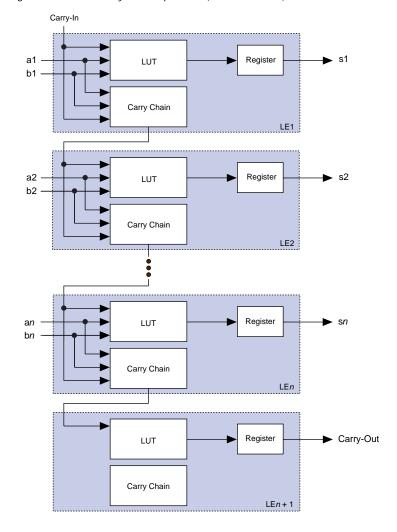

Figure 9. ACEX 1K Carry Chain Operation (n-Bit Full Adder)

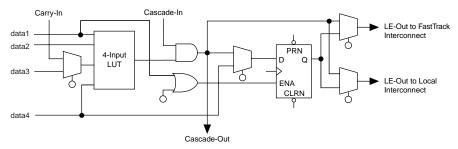

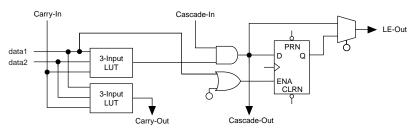

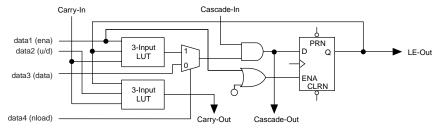

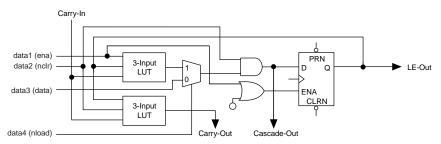

Figure 11. ACEX 1K LE Operating Modes

#### **Normal Mode**

#### **Arithmetic Mode**

#### **Up/Down Counter Mode**

#### **Clearable Counter Mode**

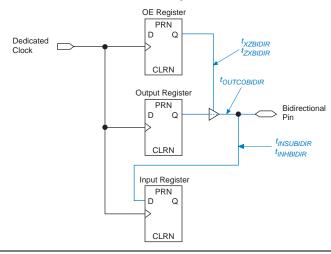

Figure 15. ACEX 1K Bidirectional I/O Registers

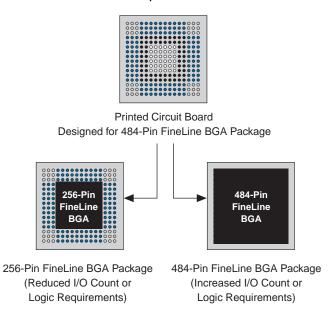

# SameFrame Pin-Outs

ACEX 1K devices support the SameFrame pin-out feature for FineLine BGA packages. The SameFrame pin-out feature is the arrangement of balls on FineLine BGA packages such that the lower-ball-count packages form a subset of the higher-ball-count packages. SameFrame pin-outs provide the flexibility to migrate not only from device to device within the same package, but also from one package to another. A given printed circuit board (PCB) layout can support multiple device density/package combinations. For example, a single board layout can support a range of devices from an EP1K10 device in a 256-pin FineLine BGA package to an EP1K100 device in a 484-pin FineLine BGA package.

The Altera software provides support to design PCBs with SameFrame pin-out devices. Devices can be defined for present and future use. The Altera software generates pin-outs describing how to lay out a board that takes advantage of this migration. Figure 18 shows an example of SameFrame pin-out.

Figure 18. SameFrame Pin-Out Example

Table 10 shows the ACEX 1K device/package combinations that support SameFrame pin-outs for ACEX 1K devices. All FineLine BGA packages support SameFrame pin-outs, providing the flexibility to migrate not only from device to device within the same package, but also from one package to another. The I/O count will vary from device to device.

| Table 2           | 0. ACEX 1K Device DC Operatii            | ng Conditions (Part 2 of a                                       | <b>2)</b> Notes (6 | 6), (7) |                         |      |

|-------------------|------------------------------------------|------------------------------------------------------------------|--------------------|---------|-------------------------|------|

| Symbol            | Parameter                                | Conditions                                                       | Min                | Тур     | Max                     | Unit |

| V <sub>OL</sub>   | 3.3-V low-level TTL output voltage       | I <sub>OL</sub> = 12 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (10)   |                    |         | 0.45                    | V    |

|                   | 3.3-V low-level CMOS output voltage      | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 3.00 V (10)  |                    |         | 0.2                     | V    |

|                   | 3.3-V low-level PCI output voltage       | $I_{OL}$ = 1.5 mA DC,<br>$V_{CCIO}$ = 3.00 to 3.60 V<br>(10)     |                    |         | 0.1 × V <sub>CCIO</sub> | V    |

|                   | 2.5-V low-level output voltage           | I <sub>OL</sub> = 0.1 mA DC,<br>V <sub>CCIO</sub> = 2.375 V (10) |                    |         | 0.2                     | V    |

|                   |                                          | I <sub>OL</sub> = 1 mA DC,<br>V <sub>CCIO</sub> = 2.375 V (10)   |                    |         | 0.4                     | V    |

|                   |                                          | I <sub>OL</sub> = 2 mA DC,<br>V <sub>CCIO</sub> = 2.375 V (10)   |                    |         | 0.7                     | V    |

| I <sub>I</sub>    | Input pin leakage current                | $V_I = 5.3 \text{ to } -0.3 \text{ V } (11)$                     | -10                |         | 10                      | μΑ   |

| I <sub>OZ</sub>   | Tri-stated I/O pin leakage current       | $V_0 = 5.3 \text{ to } -0.3 \text{ V } (11)$                     | -10                |         | 10                      | μΑ   |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current (standby) | V <sub>I</sub> = ground, no load,<br>no toggling inputs          |                    | 5       |                         | mA   |

|                   |                                          | V <sub>I</sub> = ground, no load,<br>no toggling inputs (12)     |                    | 10      |                         | mA   |

| R <sub>CONF</sub> | Value of I/O pin pull-up                 | V <sub>CCIO</sub> = 3.0 V (13)                                   | 20                 |         | 50                      | kΩ   |

|                   | resistor before and during configuration | V <sub>CCIO</sub> = 2.375 V (13)                                 | 30                 |         | 80                      | kΩ   |

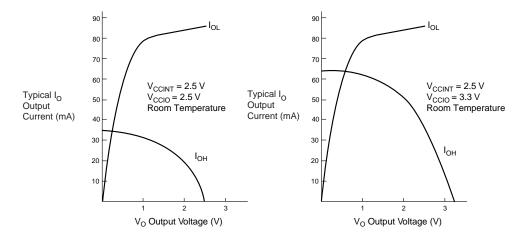

Figure 23. Output Drive Characteristics of ACEX 1K Devices

### **Timing Model**

The continuous, high-performance FastTrack Interconnect routing resources ensure accurate simulation and timing analysis as well as predictable performance. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and, therefore, have an unpredictable performance.

Device performance can be estimated by following the signal path from a source, through the interconnect, to the destination. For example, the registered performance between two LEs on the same row can be calculated by adding the following parameters:

- LE register clock-to-output delay  $(t_{CO})$

- Interconnect delay (*t<sub>SAMEROW</sub>*)

- LE look-up table delay ( $t_{LUT}$ )

- LE register setup time  $(t_{SI})$

The routing delay depends on the placement of the source and destination LEs. A more complex registered path may involve multiple combinatorial LEs between the source and destination LEs.

Timing simulation and delay prediction are available with the simulator and Timing Analyzer, or with industry-standard EDA tools. The Simulator offers both pre-synthesis functional simulation to evaluate logic design accuracy and post-synthesis timing simulation with 0.1-ns resolution. The Timing Analyzer provides point-to-point timing delay information, setup and hold time analysis, and device-wide performance analysis.

Figure 28. Synchronous Bidirectional Pin External Timing Model

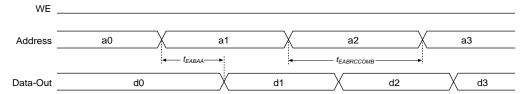

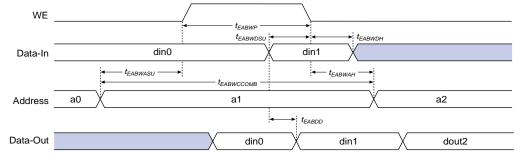

Tables 29 and 30 show the asynchronous and synchronous timing waveforms, respectively, for the EAB macroparameters in Table 24.

Figure 29. EAB Asynchronous Timing Waveforms

#### **EAB Asynchronous Write**

| Symbol                 |     |     | Speed | Grade |     |     | Unit |

|------------------------|-----|-----|-------|-------|-----|-----|------|

|                        | -   | 1   | -     | 2     | -   | 3   |      |

|                        | Min | Max | Min   | Max   | Min | Max |      |

| t <sub>EABDATA1</sub>  |     | 1.8 |       | 1.9   |     | 1.9 | ns   |

| t <sub>EABDATA2</sub>  |     | 0.6 |       | 0.7   |     | 0.7 | ns   |

| t <sub>EABWE1</sub>    |     | 1.2 |       | 1.2   |     | 1.2 | ns   |

| t <sub>EABWE2</sub>    |     | 0.4 |       | 0.4   |     | 0.4 | ns   |

| t <sub>EABRE1</sub>    |     | 0.9 |       | 0.9   |     | 0.9 | ns   |

| t <sub>EABRE2</sub>    |     | 0.4 |       | 0.4   |     | 0.4 | ns   |

| t <sub>EABCLK</sub>    |     | 0.0 |       | 0.0   |     | 0.0 | ns   |

| t <sub>EABCO</sub>     |     | 0.3 |       | 0.3   |     | 0.3 | ns   |

| t <sub>EABBYPASS</sub> |     | 0.5 |       | 0.6   |     | 0.6 | ns   |

| t <sub>EABSU</sub>     | 1.0 |     | 1.0   |       | 1.0 |     | ns   |

| t <sub>EABH</sub>      | 0.5 |     | 0.4   |       | 0.4 |     | ns   |

| t <sub>EABCLR</sub>    | 0.3 |     | 0.3   |       | 0.3 |     | ns   |

| $t_{AA}$               |     | 3.4 |       | 3.6   |     | 3.6 | ns   |

| $t_{WP}$               | 2.7 |     | 2.8   |       | 2.8 |     | ns   |

| $t_{RP}$               | 1.0 |     | 1.0   |       | 1.0 |     | ns   |

| t <sub>WDSU</sub>      | 1.0 |     | 1.0   |       | 1.0 |     | ns   |

| t <sub>WDH</sub>       | 0.1 |     | 0.1   |       | 0.1 |     | ns   |

| t <sub>WASU</sub>      | 1.8 |     | 1.9   |       | 1.9 |     | ns   |

| t <sub>WAH</sub>       | 1.9 |     | 2.0   |       | 2.0 |     | ns   |

| t <sub>RASU</sub>      | 3.1 |     | 3.5   |       | 3.5 |     | ns   |

| t <sub>RAH</sub>       | 0.2 |     | 0.2   |       | 0.2 |     | ns   |

| $t_{WO}$               |     | 2.7 |       | 2.8   |     | 2.8 | ns   |

| $t_{DD}$               |     | 2.7 |       | 2.8   |     | 2.8 | ns   |

| t <sub>EABOUT</sub>    |     | 0.5 |       | 0.6   |     | 0.6 | ns   |

| t <sub>EABCH</sub>     | 1.5 |     | 2.0   |       | 2.0 |     | ns   |

| t <sub>EABCL</sub>     | 2.7 |     | 2.8   |       | 2.8 |     | ns   |

| Symbol                  |     |     | Speed | Grade |     |     | Unit |

|-------------------------|-----|-----|-------|-------|-----|-----|------|

|                         | _   | 1   | -     | 2     | -   | 3   |      |

|                         | Min | Max | Min   | Max   | Min | Max |      |

| t <sub>EABAA</sub>      |     | 6.7 |       | 7.3   |     | 7.3 | ns   |

| t <sub>EABRCCOMB</sub>  | 6.7 |     | 7.3   |       | 7.3 |     | ns   |

| t <sub>EABRCREG</sub>   | 4.7 |     | 4.9   |       | 4.9 |     | ns   |

| t <sub>EABWP</sub>      | 2.7 |     | 2.8   |       | 2.8 |     | ns   |

| t <sub>EABWCCOMB</sub>  | 6.4 |     | 6.7   |       | 6.7 |     | ns   |

| t <sub>EABWCREG</sub>   | 7.4 |     | 7.6   |       | 7.6 |     | ns   |

| t <sub>EABDD</sub>      |     | 6.0 |       | 6.5   |     | 6.5 | ns   |

| t <sub>EABDATA</sub> CO |     | 0.8 |       | 0.9   |     | 0.9 | ns   |

| t <sub>EABDATASU</sub>  | 1.6 |     | 1.7   |       | 1.7 |     | ns   |

| t <sub>EABDATAH</sub>   | 0.0 |     | 0.0   |       | 0.0 |     | ns   |

| t <sub>EABWESU</sub>    | 1.4 |     | 1.4   |       | 1.4 |     | ns   |

| t <sub>EABWEH</sub>     | 0.1 |     | 0.0   |       | 0.0 |     | ns   |

| t <sub>EABWDSU</sub>    | 1.6 |     | 1.7   |       | 1.7 |     | ns   |

| t <sub>EABWDH</sub>     | 0.0 |     | 0.0   |       | 0.0 |     | ns   |

| t <sub>EABWASU</sub>    | 3.1 |     | 3.4   |       | 3.4 |     | ns   |

| t <sub>EABWAH</sub>     | 0.6 |     | 0.5   |       | 0.5 |     | ns   |

| t <sub>EABWO</sub>      |     | 5.4 |       | 5.8   |     | 5.8 | ns   |

| Symbol                      |     | Speed Grade |     |      |     |      |    |  |  |  |

|-----------------------------|-----|-------------|-----|------|-----|------|----|--|--|--|

|                             | -1  |             | -   | -2   |     | 3    |    |  |  |  |

|                             | Min | Max         | Min | Max  | Min | Max  |    |  |  |  |

| t <sub>INSUBIDIR</sub> (2)  | 2.2 |             | 2.3 |      | 3.2 |      | ns |  |  |  |

| t <sub>INHBIDIR</sub> (2)   | 0.0 |             | 0.0 |      | 0.0 |      | ns |  |  |  |

| t <sub>OUTCOBIDIR</sub> (2) | 2.0 | 6.6         | 2.0 | 7.8  | 2.0 | 9.6  | ns |  |  |  |

| t <sub>XZBIDIR</sub> (2)    |     | 8.8         |     | 11.2 |     | 14.0 | ns |  |  |  |

| t <sub>ZXBIDIR</sub> (2)    |     | 8.8         |     | 11.2 |     | 14.0 | ns |  |  |  |

| t <sub>INSUBIDIR</sub> (4)  | 3.1 |             | 3.3 |      | -   | -    |    |  |  |  |

| t <sub>INHBIDIR</sub> (4)   | 0.0 |             | 0.0 |      | -   |      |    |  |  |  |

| toutcobidir (4)             | 0.5 | 5.1         | 0.5 | 6.4  | -   | -    | ns |  |  |  |

| t <sub>XZBIDIR</sub> (4)    |     | 7.3         |     | 9.2  |     | _    | ns |  |  |  |

| t <sub>ZXBIDIR</sub> (4)    |     | 7.3         |     | 9.2  |     | -    | ns |  |  |  |

#### Notes to tables:

- (1) All timing parameters are described in Tables 22 through 29 in this data sheet.

- (2) This parameter is measured without the use of the ClockLock or ClockBoost circuits.

- (3) These parameters are specified by characterization.

- (4) This parameter is measured with the use of the ClockLock or ClockBoost circuits.

Tables 37 through 43 show EP1K30 device internal and external timing parameters.

| Symbol              |     |     | Speed | Grade |     |     | Unit |

|---------------------|-----|-----|-------|-------|-----|-----|------|

|                     | -1  |     | -     | 2     | -   | 3   |      |

|                     | Min | Max | Min   | Max   | Min | Max |      |

| $t_{LUT}$           |     | 0.7 |       | 0.8   |     | 1.1 | ns   |

| t <sub>CLUT</sub>   |     | 0.5 |       | 0.6   |     | 0.8 | ns   |

| t <sub>RLUT</sub>   |     | 0.6 |       | 0.7   |     | 1.0 | ns   |

| t <sub>PACKED</sub> |     | 0.3 |       | 0.4   |     | 0.5 | ns   |

| $t_{EN}$            |     | 0.6 |       | 0.8   |     | 1.0 | ns   |

| t <sub>CICO</sub>   |     | 0.1 |       | 0.1   |     | 0.2 | ns   |

| t <sub>CGEN</sub>   |     | 0.4 |       | 0.5   |     | 0.7 | ns   |

| t <sub>CGENR</sub>  |     | 0.1 |       | 0.1   |     | 0.2 | ns   |

| t <sub>CASC</sub>   |     | 0.6 |       | 0.8   |     | 1.0 | ns   |

| t <sub>C</sub>      |     | 0.0 |       | 0.0   |     | 0.0 | ns   |

| t <sub>co</sub>     |     | 0.3 |       | 0.4   |     | 0.5 | ns   |

**ACEX 1K Programmable Logic Device Family Data Sheet**

| Symbol                 |     |     | Speed | Grade |     |     | Unit |

|------------------------|-----|-----|-------|-------|-----|-----|------|

|                        | _   | 1   | -     | 2     | -   | 3   |      |

|                        | Min | Max | Min   | Max   | Min | Max |      |

| t <sub>EABAA</sub>     |     | 6.4 |       | 7.6   |     | 8.8 | ns   |

| t <sub>EABRCOMB</sub>  | 6.4 |     | 7.6   |       | 8.8 |     | ns   |

| t <sub>EABRCREG</sub>  | 4.4 |     | 5.1   |       | 6.0 |     | ns   |

| t <sub>EABWP</sub>     | 2.5 |     | 2.9   | -     | 3.3 |     | ns   |

| t <sub>EABWCOMB</sub>  | 6.0 |     | 7.0   |       | 8.0 |     | ns   |

| t <sub>EABWCREG</sub>  | 6.8 |     | 7.8   |       | 9.0 |     | ns   |

| t <sub>EABDD</sub>     |     | 5.7 |       | 6.7   |     | 7.7 | ns   |

| t <sub>EABDATACO</sub> |     | 0.8 |       | 0.9   |     | 1.1 | ns   |

| t <sub>EABDATASU</sub> | 1.5 |     | 1.7   |       | 2.0 |     | ns   |

| t <sub>EABDATAH</sub>  | 0.0 |     | 0.0   |       | 0.0 |     | ns   |

| t <sub>EABWESU</sub>   | 1.3 |     | 1.4   |       | 1.7 |     | ns   |

| t <sub>EABWEH</sub>    | 0.0 |     | 0.0   |       | 0.0 |     | ns   |

| t <sub>EABWDSU</sub>   | 1.5 |     | 1.7   |       | 2.0 |     | ns   |

| t <sub>EABWDH</sub>    | 0.0 |     | 0.0   |       | 0.0 |     | ns   |

| t <sub>EABWASU</sub>   | 3.0 |     | 3.6   |       | 4.3 |     | ns   |

| t <sub>EABWAH</sub>    | 0.5 |     | 0.5   |       | 0.4 |     | ns   |

| t <sub>EABWO</sub>     |     | 5.1 |       | 6.0   |     | 6.8 | ns   |

| Symbol            |     |     | Speed | Grade |     |     | Unit |

|-------------------|-----|-----|-------|-------|-----|-----|------|

|                   | -   | 1   | -2    |       | -   | 3   |      |

|                   | Min | Max | Min   | Max   | Min | Max |      |

| $t_{CO}$          |     | 0.6 |       | 0.6   |     | 0.7 | ns   |

| t <sub>COMB</sub> |     | 0.3 |       | 0.4   |     | 0.5 | ns   |

| t <sub>SU</sub>   | 0.5 |     | 0.6   |       | 0.7 |     | ns   |

| $t_H$             | 0.5 |     | 0.6   |       | 0.8 |     | ns   |

| t <sub>PRE</sub>  |     | 0.4 |       | 0.5   |     | 0.7 | ns   |

| t <sub>CLR</sub>  |     | 0.8 |       | 1.0   |     | 1.2 | ns   |

| t <sub>CH</sub>   | 2.0 |     | 2.5   |       | 3.0 |     | ns   |

| $t_{CL}$          | 2.0 |     | 2.5   |       | 3.0 |     | ns   |

| Symbol              |     |     | Speed | Grade |     |     | Unit |

|---------------------|-----|-----|-------|-------|-----|-----|------|

|                     | -   | 1   | -     | 2     | -   | 3   |      |

|                     | Min | Max | Min   | Max   | Min | Max |      |

| $t_{IOD}$           |     | 1.3 |       | 1.3   |     | 1.9 | ns   |

| t <sub>IOC</sub>    |     | 0.3 |       | 0.4   |     | 0.4 | ns   |

| t <sub>IOCO</sub>   |     | 1.7 |       | 2.1   |     | 2.6 | ns   |

| t <sub>IOCOMB</sub> |     | 0.5 |       | 0.6   |     | 0.8 | ns   |

| t <sub>IOSU</sub>   | 0.8 |     | 1.0   |       | 1.3 |     | ns   |

| t <sub>IOH</sub>    | 0.4 |     | 0.5   |       | 0.6 |     | ns   |

| t <sub>IOCLR</sub>  |     | 0.2 |       | 0.2   |     | 0.4 | ns   |

| t <sub>OD1</sub>    |     | 1.2 |       | 1.2   |     | 1.9 | ns   |

| t <sub>OD2</sub>    |     | 0.7 |       | 0.8   |     | 1.7 | ns   |

| t <sub>OD3</sub>    |     | 2.7 |       | 3.0   |     | 4.3 | ns   |

| $t_{XZ}$            |     | 4.7 |       | 5.7   |     | 7.5 | ns   |

| $t_{ZX1}$           |     | 4.7 |       | 5.7   |     | 7.5 | ns   |

| $t_{ZX2}$           |     | 4.2 |       | 5.3   |     | 7.3 | ns   |

| $t_{ZX3}$           |     | 6.2 |       | 7.5   |     | 9.9 | ns   |

| t <sub>INREG</sub>  |     | 3.5 |       | 4.2   |     | 5.6 | ns   |

| t <sub>IOFD</sub>   |     | 1.1 |       | 1.3   |     | 1.8 | ns   |

| t <sub>INCOMB</sub> |     | 1.1 |       | 1.3   |     | 1.8 | ns   |

| Symbol                 |     |     | Speed | Grade |     |     | Unit |

|------------------------|-----|-----|-------|-------|-----|-----|------|

|                        | _   | 1   | -     | 2     | -   | 3   |      |

|                        | Min | Max | Min   | Max   | Min | Max |      |

| t <sub>EABDATA1</sub>  |     | 1.7 |       | 2.4   |     | 3.2 | ns   |

| t <sub>EABDATA2</sub>  |     | 0.4 |       | 0.6   |     | 0.8 | ns   |

| t <sub>EABWE1</sub>    |     | 1.0 |       | 1.4   |     | 1.9 | ns   |

| t <sub>EABWE2</sub>    |     | 0.0 |       | 0.0   |     | 0.0 | ns   |

| t <sub>EABRE1</sub>    |     | 0.0 |       | 0.0   |     | 0.0 |      |

| t <sub>EABRE2</sub>    |     | 0.4 |       | 0.6   |     | 0.8 |      |

| t <sub>EABCLK</sub>    |     | 0.0 |       | 0.0   |     | 0.0 | ns   |

| t <sub>EABCO</sub>     |     | 0.8 |       | 1.1   |     | 1.5 | ns   |

| t <sub>EABBYPASS</sub> |     | 0.0 |       | 0.0   |     | 0.0 | ns   |

| t <sub>EABSU</sub>     | 0.7 |     | 1.0   |       | 1.3 |     | ns   |

| t <sub>EABH</sub>      | 0.4 |     | 0.6   |       | 0.8 |     | ns   |

| t <sub>EABCLR</sub>    | 0.8 |     | 1.1   |       | 1.5 |     |      |

| $t_{AA}$               |     | 2.0 |       | 2.8   |     | 3.8 | ns   |

| $t_{WP}$               | 2.0 |     | 2.8   |       | 3.8 |     | ns   |

| t <sub>RP</sub>        | 1.0 |     | 1.4   |       | 1.9 |     |      |

| t <sub>WDSU</sub>      | 0.5 |     | 0.7   |       | 0.9 |     | ns   |

| t <sub>WDH</sub>       | 0.1 |     | 0.1   |       | 0.2 |     | ns   |

| t <sub>WASU</sub>      | 1.0 |     | 1.4   |       | 1.9 |     | ns   |

| t <sub>WAH</sub>       | 1.5 |     | 2.1   |       | 2.9 |     | ns   |

| t <sub>RASU</sub>      | 1.5 |     | 2.1   |       | 2.8 |     |      |

| t <sub>RAH</sub>       | 0.1 |     | 0.1   |       | 0.2 |     |      |

| $t_{WO}$               |     | 2.1 |       | 2.9   |     | 4.0 | ns   |

| t <sub>DD</sub>        |     | 2.1 |       | 2.9   |     | 4.0 | ns   |

| t <sub>EABOUT</sub>    |     | 0.0 |       | 0.0   |     | 0.0 | ns   |

| t <sub>EABCH</sub>     | 1.5 |     | 2.0   |       | 2.5 |     | ns   |

| t <sub>EABCL</sub>     | 1.5 |     | 2.0   |       | 2.5 |     | ns   |

Tables 51 through 57 show EP1K100 device internal and external timing parameters.

| Symbol              |     |     | Speed | Grade |     |     | Unit |

|---------------------|-----|-----|-------|-------|-----|-----|------|

|                     | -   | 1   | -     | 2     | -   | 3   |      |

|                     | Min | Max | Min   | Max   | Min | Max |      |

| $t_{LUT}$           |     | 0.7 |       | 1.0   |     | 1.5 | ns   |

| t <sub>CLUT</sub>   |     | 0.5 |       | 0.7   |     | 0.9 | ns   |

| t <sub>RLUT</sub>   |     | 0.6 |       | 0.8   |     | 1.1 | ns   |

| t <sub>PACKED</sub> |     | 0.3 |       | 0.4   |     | 0.5 | ns   |

| t <sub>EN</sub>     |     | 0.2 |       | 0.3   |     | 0.3 | ns   |

| t <sub>CICO</sub>   |     | 0.1 |       | 0.1   |     | 0.2 | ns   |

| t <sub>CGEN</sub>   |     | 0.4 |       | 0.5   |     | 0.7 | ns   |

| t <sub>CGENR</sub>  |     | 0.1 |       | 0.1   |     | 0.2 | ns   |

| t <sub>CASC</sub>   |     | 0.6 |       | 0.9   |     | 1.2 | ns   |

| $t_{C}$             |     | 0.8 |       | 1.0   |     | 1.4 | ns   |

| t <sub>CO</sub>     |     | 0.6 |       | 0.8   |     | 1.1 | ns   |

| t <sub>COMB</sub>   |     | 0.4 |       | 0.5   |     | 0.7 | ns   |

| t <sub>SU</sub>     | 0.4 |     | 0.6   |       | 0.7 |     | ns   |

| $t_H$               | 0.5 |     | 0.7   |       | 0.9 |     | ns   |

| t <sub>PRE</sub>    |     | 0.8 |       | 1.0   |     | 1.4 | ns   |

| t <sub>CLR</sub>    |     | 0.8 |       | 1.0   |     | 1.4 | ns   |

| t <sub>CH</sub>     | 1.5 |     | 2.0   |       | 2.5 |     | ns   |

| t <sub>CL</sub>     | 1.5 |     | 2.0   |       | 2.5 |     | ns   |

| Symbol                 |     |     | Speed | Grade |     |     | Unit |

|------------------------|-----|-----|-------|-------|-----|-----|------|

|                        | _   | 1   | -     | 2     | -   | 3   |      |

|                        | Min | Max | Min   | Max   | Min | Max |      |

| t <sub>EABDATA1</sub>  |     | 1.5 |       | 2.0   |     | 2.6 | ns   |

| t <sub>EABDATA1</sub>  |     | 0.0 |       | 0.0   |     | 0.0 | ns   |

| t <sub>EABWE1</sub>    |     | 1.5 |       | 2.0   |     | 2.6 | ns   |

| t <sub>EABWE2</sub>    |     | 0.3 |       | 0.4   |     | 0.5 | ns   |

| t <sub>EABRE1</sub>    |     | 0.3 |       | 0.4   |     | 0.5 | ns   |

| t <sub>EABRE2</sub>    |     | 0.0 |       | 0.0   |     | 0.0 | ns   |

| t <sub>EABCLK</sub>    |     | 0.0 |       | 0.0   |     | 0.0 | ns   |

| t <sub>EABCO</sub>     |     | 0.3 |       | 0.4   |     | 0.5 | ns   |

| t <sub>EABBYPASS</sub> |     | 0.1 |       | 0.1   |     | 0.2 | ns   |

| t <sub>EABSU</sub>     | 0.8 |     | 1.0   |       | 1.4 |     | ns   |

| t <sub>EABH</sub>      | 0.1 |     | 0.1   |       | 0.2 |     | ns   |

| t <sub>EABCLR</sub>    | 0.3 |     | 0.4   |       | 0.5 |     | ns   |

| $t_{AA}$               |     | 4.0 |       | 5.1   |     | 6.6 | ns   |

| $t_{WP}$               | 2.7 |     | 3.5   |       | 4.7 |     | ns   |

| t <sub>RP</sub>        | 1.0 |     | 1.3   |       | 1.7 |     | ns   |

| t <sub>WDSU</sub>      | 1.0 |     | 1.3   |       | 1.7 |     | ns   |

| t <sub>WDH</sub>       | 0.2 |     | 0.2   |       | 0.3 |     | ns   |

| t <sub>WASU</sub>      | 1.6 |     | 2.1   |       | 2.8 |     | ns   |

| t <sub>WAH</sub>       | 1.6 |     | 2.1   |       | 2.8 |     | ns   |

| t <sub>RASU</sub>      | 3.0 |     | 3.9   |       | 5.2 |     | ns   |

| t <sub>RAH</sub>       | 0.1 |     | 0.1   |       | 0.2 |     | ns   |

| $t_{WO}$               |     | 1.5 |       | 2.0   |     | 2.6 | ns   |

| t <sub>DD</sub>        |     | 1.5 |       | 2.0   |     | 2.6 | ns   |

| t <sub>EABOUT</sub>    |     | 0.2 |       | 0.3   |     | 0.3 | ns   |

| t <sub>EABCH</sub>     | 1.5 |     | 2.0   |       | 2.5 |     | ns   |

| t <sub>EABCL</sub>     | 2.7 |     | 3.5   |       | 4.7 |     | ns   |

| Symbol                  | Speed Grade |     |     |     |      |     | Unit |

|-------------------------|-------------|-----|-----|-----|------|-----|------|

|                         | -1          |     | -2  |     | -3   |     |      |

|                         | Min         | Max | Min | Max | Min  | Max |      |

| t <sub>EABAA</sub>      |             | 5.9 |     | 7.6 |      | 9.9 | ns   |

| t <sub>EABRCOMB</sub>   | 5.9         |     | 7.6 |     | 9.9  |     | ns   |

| t <sub>EABRCREG</sub>   | 5.1         |     | 6.5 |     | 8.5  |     | ns   |

| t <sub>EABWP</sub>      | 2.7         |     | 3.5 |     | 4.7  |     | ns   |

| t <sub>EABWCOMB</sub>   | 5.9         |     | 7.7 |     | 10.3 |     | ns   |

| t <sub>EABWCREG</sub>   | 5.4         |     | 7.0 |     | 9.4  |     | ns   |

| t <sub>EABDD</sub>      |             | 3.4 |     | 4.5 |      | 5.9 | ns   |

| t <sub>EABDATA</sub> CO |             | 0.5 |     | 0.7 |      | 0.8 | ns   |

| t <sub>EABDATASU</sub>  | 0.8         |     | 1.0 |     | 1.4  |     | ns   |

| t <sub>EABDATAH</sub>   | 0.1         |     | 0.1 |     | 0.2  |     | ns   |

| t <sub>EABWESU</sub>    | 1.1         |     | 1.4 |     | 1.9  |     | ns   |

| t <sub>EABWEH</sub>     | 0.0         |     | 0.0 |     | 0.0  |     | ns   |

| t <sub>EABWDSU</sub>    | 1.0         |     | 1.3 |     | 1.7  |     | ns   |

| t <sub>EABWDH</sub>     | 0.2         |     | 0.2 |     | 0.3  |     | ns   |

| t <sub>EABWASU</sub>    | 4.1         |     | 5.2 |     | 6.8  |     | ns   |

| t <sub>EABWAH</sub>     | 0.0         |     | 0.0 |     | 0.0  |     | ns   |

| t <sub>EABWO</sub>      |             | 3.4 |     | 4.5 |      | 5.9 | ns   |

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 www.altera.com Applications Hotline: (800) 800-EPLD Literature Services: lit\_req@altera.com

Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described

herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

I.S. EN ISO 9001