Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 360                                                      |

| Number of Logic Elements/Cells | 2880                                                     |

| Total RAM Bits                 | 40960                                                    |

| Number of I/O                  | 186                                                      |

| Number of Gates                | 199000                                                   |

| Voltage - Supply               | 2.375V ~ 2.625V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 85°C (TA)                                        |

| Package / Case                 | 256-BGA                                                  |

| Supplier Device Package        | 256-FBGA (17x17)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1k50fi256-2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

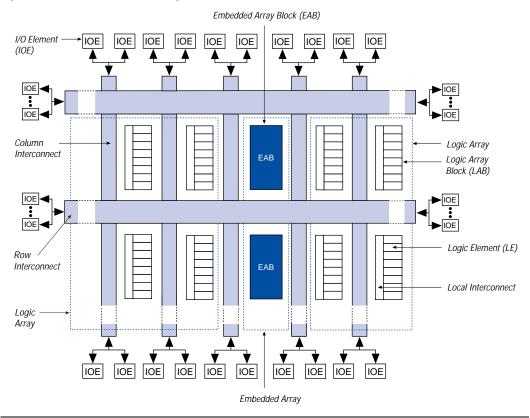

Figure 1. ACEX 1K Device Block Diagram

ACEX 1K devices provide six dedicated inputs that drive the flipflops' control inputs and ensure the efficient distribution of high-speed, low-skew (less than 1.0 ns) control signals. These signals use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect routing structure. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device.

### **Embedded Array Block**

The EAB is a flexible block of RAM, with registers on the input and output ports, that is used to implement common gate array megafunctions. Because it is large and flexible, the EAB is suitable for functions such as multipliers, vector scalars, and error correction circuits. These functions can be combined in applications such as digital filters and microcontrollers.

Logic functions are implemented by programming the EAB with a read-only pattern during configuration, thereby creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of EABs. The large capacity of EABs enables designers to implement complex functions in a single logic level without the routing delays associated with linked LEs or field-programmable gate array (FPGA) RAM blocks. For example, a single EAB can implement any function with 8 inputs and 16 outputs. Parameterized functions, such as LPM functions, can take advantage of the EAB automatically.

The ACEX 1K enhanced EAB supports dual-port RAM. The dual-port structure is ideal for FIFO buffers with one or two clocks. The ACEX 1K EAB can also support up to 16-bit-wide RAM blocks. The ACEX 1K EAB can act in dual-port or single-port mode. When in dual-port mode, separate clocks may be used for EAB read and write sections, allowing the EAB to be written and read at different rates. It also has separate synchronous clock enable signals for the EAB read and write sections, which allow independent control of these sections.

The EAB can also be used for bidirectional, dual-port memory applications where two ports read or write simultaneously. To implement this type of dual-port memory, two EABs are used to support two simultaneous reads or writes.

Alternatively, one clock and clock enable can be used to control the input registers of the EAB, while a different clock and clock enable control the output registers (see Figure 2).

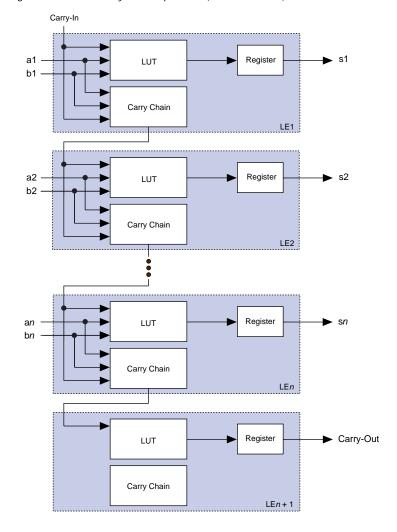

Figure 9. ACEX 1K Carry Chain Operation (n-Bit Full Adder)

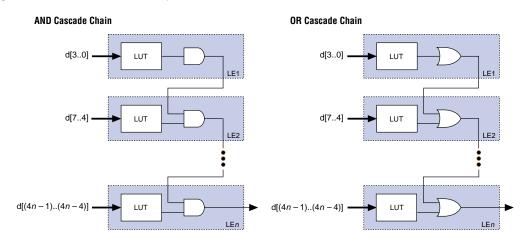

#### Cascade Chain

With the cascade chain, the ACEX 1K architecture can implement functions that have a very wide fan-in. Adjacent LUTs can be used to compute portions of the function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical  ${\tt AND}$  or logical  ${\tt OR}$  (via De Morgan's inversion) to connect the outputs of adjacent LEs. With a delay as low as 0.6 ns per LE, each additional LE provides four more inputs to the effective width of a function. Cascade chain logic can be created automatically by the compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than eight bits are implemented automatically by linking several LABs together. For easier routing, a long cascade chain skips every other LAB in a row. A cascade chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from odd-numbered LAB to odd-numbered LAB (e.g., the last LE of the first LAB in a row cascades to the first LE of the third LAB). The cascade chain does not cross the center of the row (e.g., in the EP1K50 device, the cascade chain stops at the eighteenth LAB, and a new one begins at the nineteenth LAB). This break is due to the EAB's placement in the middle of the row.

Figure 10 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in. These examples show functions of 4n variables implemented with n LEs. The LE delay is 1.3 ns; the cascade chain delay is 0.6 ns. With the cascade chain, decoding a 16-bit address requires 3.1 ns.

Figure 10. ACEX 1K Cascade Chain Operation

### LE Operating Modes

The ACEX 1K LE can operate in the following four modes:

- Normal mode

- Arithmetic mode

- Up/down counter mode

- Clearable counter mode

Each of these modes uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. Three inputs to the LE provide clock, clear, and preset control for the register. The Altera software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions that use a specific LE operating mode for optimal performance.

The architecture provides a synchronous clock enable to the register in all four modes. The Altera software can set DATA1 to enable the register synchronously, providing easy implementation of fully synchronous designs.

Figure 11 shows the ACEX 1K LE operating modes.

For improved routing, the row interconnect consists of a combination of full-length and half-length channels. The full-length channels connect to all LABs in a row; the half-length channels connect to the LABs in half of the row. The EAB can be driven by the half-length channels in the left half of the row and by the full-length channels. The EAB drives out to the full-length channels. In addition to providing a predictable, row-wide interconnect, this architecture provides increased routing resources. Two neighboring LABs can be connected using a half-row channel, thereby saving the other half of the channel for the other half of the row.

Table 6 summarizes the FastTrack Interconnect routing structure resources available in each ACEX 1K device.

| Table 6. ACEX 1 | Table 6. ACEX 1K FastTrack Interconnect Resources |                     |         |                        |  |  |  |  |

|-----------------|---------------------------------------------------|---------------------|---------|------------------------|--|--|--|--|

| Device          | Rows                                              | Channels per<br>Row | Columns | Channels per<br>Column |  |  |  |  |

| EP1K10          | 3                                                 | 144                 | 24      | 24                     |  |  |  |  |

| EP1K30          | 6                                                 | 216                 | 36      | 24                     |  |  |  |  |

| EP1K50          | 10                                                | 216                 | 36      | 24                     |  |  |  |  |

| EP1K100         | 12                                                | 312                 | 52      | 24                     |  |  |  |  |

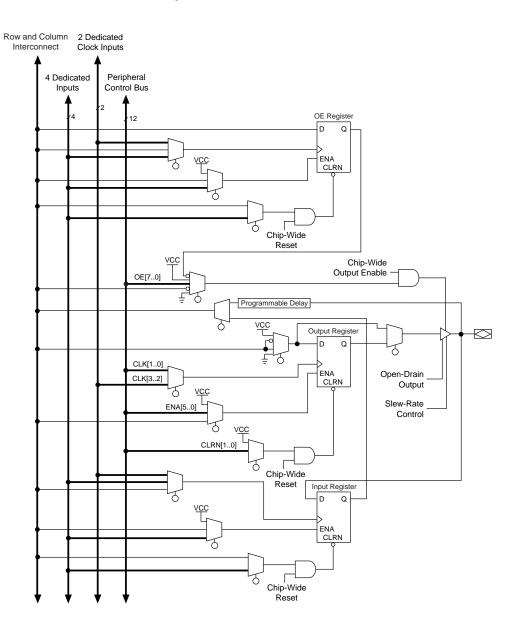

In addition to general-purpose I/O pins, ACEX 1K devices have six dedicated input pins that provide low-skew signal distribution across the device. These six inputs can be used for global clock, clear, preset, and peripheral output-enable and clock-enable control signals. These signals are available as control signals for all LABs and IOEs in the device. The dedicated inputs can also be used as general-purpose data inputs because they can feed the local interconnect of each LAB in the device.

Figure 14 shows the interconnection of adjacent LABs and EABs, with row, column, and local interconnects, as well as the associated cascade and carry chains. Each LAB is labeled according to its location: a letter represents the row and a number represents the column. For example, LAB B3 is in row B, column 3.

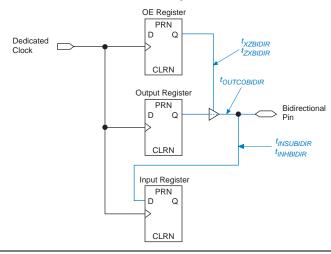

Figure 15. ACEX 1K Bidirectional I/O Registers

Tables 11 and 12 summarize the ClockLock and ClockBoost parameters for -1 and -2 speed-grade devices, respectively.

| Table 11.             | ClockLock & ClockBoost Parameters for -1                                | Speed-Grade De             | vices |     |                               |      |

|-----------------------|-------------------------------------------------------------------------|----------------------------|-------|-----|-------------------------------|------|

| Symbol                | Parameter                                                               | Condition                  | Min   | Тур | Max                           | Unit |

| $t_R$                 | Input rise time                                                         |                            |       |     | 5                             | ns   |

| $t_{F}$               | Input fall time                                                         |                            |       |     | 5                             | ns   |

| $t_{INDUTY}$          | Input duty cycle                                                        |                            | 40    |     | 60                            | %    |

| f <sub>CLK1</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 1) |                            | 25    |     | 180                           | MHz  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 2) |                            | 16    |     | 90                            | MHz  |

| f <sub>CLKDEV</sub>   | Input deviation from user specification in the Altera software $(1)$    |                            |       |     | 25,000<br><i>(</i> 2 <i>)</i> | PPM  |

| t <sub>INCLKSTB</sub> | Input clock stability (measured between adjacent clocks)                |                            |       |     | 100                           | ps   |

| t <sub>LOCK</sub>     | Time required for ClockLock or ClockBoost to acquire lock (3)           |                            |       |     | 10                            | μs   |

| t <sub>JITTER</sub>   | Jitter on ClockLock or ClockBoost-                                      | t <sub>INCLKSTB</sub> <100 |       |     | 250 (4)                       | ps   |

|                       | generated clock (4)                                                     | t <sub>INCLKSTB</sub> < 50 |       |     | 200 (4)                       | ps   |

| t <sub>OUTDUTY</sub>  | Duty cycle for ClockLock or ClockBoost-<br>generated clock              |                            | 40    | 50  | 60                            | %    |

| Table 12.             | ClockLock & ClockBoost Parameters for -2                                | ? Speed-Grade De            | vices |     |                |      |

|-----------------------|-------------------------------------------------------------------------|-----------------------------|-------|-----|----------------|------|

| Symbol                | Parameter                                                               | Condition                   | Min   | Тур | Max            | Unit |

| $t_R$                 | Input rise time                                                         |                             |       |     | 5              | ns   |

| $t_{\digamma}$        | Input fall time                                                         |                             |       |     | 5              | ns   |

| t <sub>INDUTY</sub>   | Input duty cycle                                                        |                             | 40    |     | 60             | %    |

| f <sub>CLK1</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 1) |                             | 25    |     | 80             | MHz  |

| f <sub>CLK2</sub>     | Input clock frequency (ClockBoost clock multiplication factor equals 2) |                             | 16    |     | 40             | MHz  |

| f <sub>CLKDEV</sub>   | Input deviation from user specification in the software (1)             |                             |       |     | 25,000         | PPM  |

| t <sub>INCLKSTB</sub> | Input clock stability (measured between adjacent clocks)                |                             |       |     | 100            | ps   |

| t <sub>LOCK</sub>     | Time required for ClockLock or ClockBoost to acquire lock (3)           |                             |       |     | 10             | μs   |

| t <sub>JITTER</sub>   | Jitter on ClockLock or ClockBoost-                                      | t <sub>INCLKSTB</sub> < 100 |       |     | 250 <i>(4)</i> | ps   |

|                       | generated clock (4)                                                     | t <sub>INCLKSTB</sub> < 50  |       |     | 200 (4)        | ps   |

| toutduty              | Duty cycle for ClockLock or ClockBoost-<br>generated clock              |                             | 40    | 50  | 60             | %    |

#### Notes to tables:

- (1) To implement the ClockLock and ClockBoost circuitry with the Altera software, designers must specify the input frequency. The Altera software tunes the PLL in the ClockLock and ClockBoost circuitry to this frequency. The f<sub>CLKDEV</sub> parameter specifies how much the incoming clock can differ from the specified frequency during device operation. Simulation does not reflect this parameter.

- (2) Twenty-five thousand parts per million (PPM) equates to 2.5% of input clock period.

- (3) During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration because the  $t_{LOCK}$  value is less than the time required for configuration.

- (4) The  $t_{IITTER}$  specification is measured under long-term observation. The maximum value for  $t_{IITTER}$  is 200 ps if  $t_{INCLKSTB}$  is lower than 50 ps.

# I/O Configuration

This section discusses the PCI pull-up clamping diode option, slew-rate control, open-drain output option, and MultiVolt I/O interface for ACEX 1K devices. The PCI pull-up clamping diode, slew-rate control, and open-drain output options are controlled pin-by-pin via Altera software logic options. The MultiVolt I/O interface is controlled by connecting  $V_{\rm CCIO}$  to a different voltage than  $V_{\rm CCINT}$ . Its effect can be simulated in the Altera software via the **Global Project Device Options** dialog box (Assign menu).

## **Generic Testing**

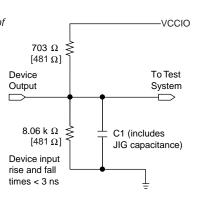

Each ACEX 1K device is functionally tested. Complete testing of each configurable static random access memory (SRAM) bit and all logic functionality ensures 100% yield. AC test measurements for ACEX 1K devices are made under conditions equivalent to those shown in Figure 21. Multiple test patterns can be used to configure devices during all stages of the production flow.

Figure 21. ACEX 1K AC Test Conditions

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast-groundcurrent transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result. Numbers in brackets are for 2.5-V devices or outputs. Numbers without brackets are for 3.3-V devices or outputs.

## Operating Conditions

Tables 18 through 21 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 2.5-V ACEX 1K devices.

| Table 1            | 8. ACEX 1K Device Absolute I | Maximum Ratings Note (1)                 |      |      |      |

|--------------------|------------------------------|------------------------------------------|------|------|------|

| Symbol             | Parameter                    | Conditions                               | Min  | Max  | Unit |

| V <sub>CCINT</sub> | Supply voltage               | With respect to ground (2)               | -0.5 | 3.6  | V    |

| V <sub>CCIO</sub>  |                              |                                          | -0.5 | 4.6  | V    |

| V <sub>I</sub>     | DC input voltage             |                                          | -2.0 | 5.75 | V    |

| I <sub>OUT</sub>   | DC output current, per pin   |                                          | -25  | 25   | mA   |

| T <sub>STG</sub>   | Storage temperature          | No bias                                  | -65  | 150  | ° C  |

| T <sub>AMB</sub>   | Ambient temperature          | Under bias                               | -65  | 135  | ° C  |

| TJ                 | Junction temperature         | PQFP, TQFP, and BGA packages, under bias |      | 135  | ° C  |

Figure 28. Synchronous Bidirectional Pin External Timing Model

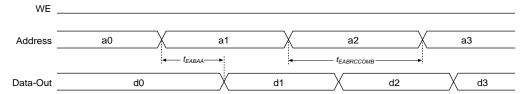

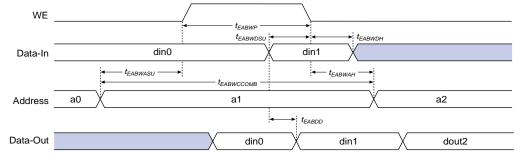

Tables 29 and 30 show the asynchronous and synchronous timing waveforms, respectively, for the EAB macroparameters in Table 24.

Figure 29. EAB Asynchronous Timing Waveforms

#### **EAB Asynchronous Write**

| Table 22. LE      | Timing Microparameters (Part 2 of 2) Note (1)                                                                                        |            |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|

| Symbol            | Parameter                                                                                                                            | Conditions |

| t <sub>CASC</sub> | Cascade-in to cascade-out delay                                                                                                      |            |

| $t_{C}$           | LE register control signal delay                                                                                                     |            |

| $t_{CO}$          | LE register clock-to-output delay                                                                                                    |            |

| t <sub>COMB</sub> | Combinatorial delay                                                                                                                  |            |

| t <sub>SU</sub>   | LE register setup time for data and enable signals before clock; LE register recovery time after asynchronous clear, preset, or load |            |

| $t_H$             | LE register hold time for data and enable signals after clock                                                                        |            |

| t <sub>PRE</sub>  | LE register preset delay                                                                                                             |            |

| t <sub>CLR</sub>  | LE register clear delay                                                                                                              |            |

| t <sub>CH</sub>   | Minimum clock high time from clock pin                                                                                               |            |

| $t_{CL}$          | Minimum clock low time from clock pin                                                                                                |            |

| Table 23. 10        | E Timing Microparameters Note (1)                                                                                     |                |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|----------------|

| Symbol              | Parameter                                                                                                             | Conditions     |

| t <sub>IOD</sub>    | IOE data delay                                                                                                        |                |

| $t_{IOC}$           | IOE register control signal delay                                                                                     |                |

| t <sub>IOCO</sub>   | IOE register clock-to-output delay                                                                                    |                |

| t <sub>IOCOMB</sub> | IOE combinatorial delay                                                                                               |                |

| t <sub>IOSU</sub>   | IOE register setup time for data and enable signals before clock; IOE register recovery time after asynchronous clear |                |

| t <sub>IOH</sub>    | IOE register hold time for data and enable signals after clock                                                        |                |

| t <sub>IOCLR</sub>  | IOE register clear time                                                                                               |                |

| t <sub>OD1</sub>    | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = 3.3 V                                          | C1 = 35 pF (2) |

| t <sub>OD2</sub>    | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = 2.5 V                                          | C1 = 35 pF (3) |

| t <sub>OD3</sub>    | Output buffer and pad delay, slow slew rate = on                                                                      | C1 = 35 pF (4) |

| $t_{XZ}$            | IOE output buffer disable delay                                                                                       |                |

| $t_{ZX1}$           | IOE output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = 3.3 V                                       | C1 = 35 pF (2) |

| $t_{ZX2}$           | IOE output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = 2.5 V                                       | C1 = 35 pF (3) |

| t <sub>ZX3</sub>    | IOE output buffer enable delay, slow slew rate = on                                                                   | C1 = 35 pF (4) |

| t <sub>INREG</sub>  | IOE input pad and buffer to IOE register delay                                                                        |                |

| t <sub>IOFD</sub>   | IOE register feedback delay                                                                                           |                |

| t <sub>INCOMB</sub> | IOE input pad and buffer to FastTrack Interconnect delay                                                              |                |

| Symbol                 | Parameter                                                        | Conditions |

|------------------------|------------------------------------------------------------------|------------|

| t <sub>EABDATA1</sub>  | Data or address delay to EAB for combinatorial input             |            |

| t <sub>EABDATA2</sub>  | Data or address delay to EAB for registered input                |            |

| t <sub>EABWE1</sub>    | Write enable delay to EAB for combinatorial input                |            |

| t <sub>EABWE2</sub>    | Write enable delay to EAB for registered input                   |            |

| t <sub>EABRE1</sub>    | Read enable delay to EAB for combinatorial input                 |            |

| t <sub>EABRE2</sub>    | Read enable delay to EAB for registered input                    |            |

| t <sub>EABCLK</sub>    | EAB register clock delay                                         |            |

| t <sub>EABCO</sub>     | EAB register clock-to-output delay                               |            |

| t <sub>EABBYPASS</sub> | Bypass register delay                                            |            |

| t <sub>EABSU</sub>     | EAB register setup time before clock                             |            |

| t <sub>EABH</sub>      | EAB register hold time after clock                               |            |

| t <sub>EABCLR</sub>    | EAB register asynchronous clear time to output delay             |            |

| $t_{AA}$               | Address access delay (including the read enable to output delay) |            |

| $t_{WP}$               | Write pulse width                                                |            |

| $t_{RP}$               | Read pulse width                                                 |            |

| t <sub>WDSU</sub>      | Data setup time before falling edge of write pulse               | (5)        |

| t <sub>WDH</sub>       | Data hold time after falling edge of write pulse                 | (5)        |

| t <sub>WASU</sub>      | Address setup time before rising edge of write pulse             | (5)        |

| t <sub>WAH</sub>       | Address hold time after falling edge of write pulse              | (5)        |

| t <sub>RASU</sub>      | Address setup time before rising edge of read pulse              |            |

| t <sub>RAH</sub>       | Address hold time after falling edge of read pulse               |            |

| $t_{WO}$               | Write enable to data output valid delay                          |            |

| $t_{DD}$               | Data-in to data-out valid delay                                  |            |

| t <sub>EABOUT</sub>    | Data-out delay                                                   |            |

| t <sub>EABCH</sub>     | Clock high time                                                  |            |

| t <sub>EABCL</sub>     | Clock low time                                                   |            |

| Symbol                 | Speed Grade |     |     |     |     |     |    |  |

|------------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                        | -           | 1   | -   | 2   | -   | 3   |    |  |

|                        | Min         | Max | Min | Max | Min | Max |    |  |

| t <sub>EABDATA1</sub>  |             | 1.8 |     | 1.9 |     | 1.9 | ns |  |

| t <sub>EABDATA2</sub>  |             | 0.6 |     | 0.7 |     | 0.7 | ns |  |

| t <sub>EABWE1</sub>    |             | 1.2 |     | 1.2 |     | 1.2 | ns |  |

| t <sub>EABWE2</sub>    |             | 0.4 |     | 0.4 |     | 0.4 | ns |  |

| t <sub>EABRE1</sub>    |             | 0.9 |     | 0.9 |     | 0.9 | ns |  |

| t <sub>EABRE2</sub>    |             | 0.4 |     | 0.4 |     | 0.4 | ns |  |

| t <sub>EABCLK</sub>    |             | 0.0 |     | 0.0 |     | 0.0 | ns |  |

| t <sub>EABCO</sub>     |             | 0.3 |     | 0.3 |     | 0.3 | ns |  |

| t <sub>EABBYPASS</sub> |             | 0.5 |     | 0.6 |     | 0.6 | ns |  |

| t <sub>EABSU</sub>     | 1.0         |     | 1.0 |     | 1.0 |     | ns |  |

| t <sub>EABH</sub>      | 0.5         |     | 0.4 |     | 0.4 |     | ns |  |

| t <sub>EABCLR</sub>    | 0.3         |     | 0.3 |     | 0.3 |     | ns |  |

| $t_{AA}$               |             | 3.4 |     | 3.6 |     | 3.6 | ns |  |

| $t_{WP}$               | 2.7         |     | 2.8 |     | 2.8 |     | ns |  |

| $t_{RP}$               | 1.0         |     | 1.0 |     | 1.0 |     | ns |  |

| t <sub>WDSU</sub>      | 1.0         |     | 1.0 |     | 1.0 |     | ns |  |

| t <sub>WDH</sub>       | 0.1         |     | 0.1 |     | 0.1 |     | ns |  |

| t <sub>WASU</sub>      | 1.8         |     | 1.9 |     | 1.9 |     | ns |  |

| t <sub>WAH</sub>       | 1.9         |     | 2.0 |     | 2.0 |     | ns |  |

| t <sub>RASU</sub>      | 3.1         |     | 3.5 |     | 3.5 |     | ns |  |

| t <sub>RAH</sub>       | 0.2         |     | 0.2 |     | 0.2 |     | ns |  |

| $t_{WO}$               |             | 2.7 |     | 2.8 |     | 2.8 | ns |  |

| $t_{DD}$               |             | 2.7 |     | 2.8 |     | 2.8 | ns |  |

| t <sub>EABOUT</sub>    |             | 0.5 |     | 0.6 |     | 0.6 | ns |  |

| t <sub>EABCH</sub>     | 1.5         |     | 2.0 |     | 2.0 |     | ns |  |

| t <sub>EABCL</sub>     | 2.7         |     | 2.8 |     | 2.8 |     | ns |  |

| Symbol            |     |     | Speed | Grade |     |     | Unit |

|-------------------|-----|-----|-------|-------|-----|-----|------|

|                   | -   | 1   | -:    | -2    |     | 3   |      |

|                   | Min | Max | Min   | Max   | Min | Max |      |

| $t_{CO}$          |     | 0.6 |       | 0.6   |     | 0.7 | ns   |

| t <sub>COMB</sub> |     | 0.3 |       | 0.4   |     | 0.5 | ns   |

| t <sub>SU</sub>   | 0.5 |     | 0.6   |       | 0.7 |     | ns   |

| $t_H$             | 0.5 |     | 0.6   |       | 0.8 |     | ns   |

| t <sub>PRE</sub>  |     | 0.4 |       | 0.5   |     | 0.7 | ns   |

| t <sub>CLR</sub>  |     | 0.8 |       | 1.0   |     | 1.2 | ns   |

| t <sub>CH</sub>   | 2.0 |     | 2.5   |       | 3.0 |     | ns   |

| $t_{CL}$          | 2.0 |     | 2.5   |       | 3.0 |     | ns   |

| Symbol              |     |     | Speed | Grade |     |     | Unit |  |

|---------------------|-----|-----|-------|-------|-----|-----|------|--|

|                     | -   | 1   | -2    |       | -3  |     |      |  |

|                     | Min | Max | Min   | Max   | Min | Max |      |  |

| $t_{IOD}$           |     | 1.3 |       | 1.3   |     | 1.9 | ns   |  |

| t <sub>IOC</sub>    |     | 0.3 |       | 0.4   |     | 0.4 | ns   |  |

| t <sub>IOCO</sub>   |     | 1.7 |       | 2.1   |     | 2.6 | ns   |  |

| t <sub>IOCOMB</sub> |     | 0.5 |       | 0.6   |     | 0.8 | ns   |  |

| t <sub>IOSU</sub>   | 0.8 |     | 1.0   |       | 1.3 |     | ns   |  |

| $t_{IOH}$           | 0.4 |     | 0.5   |       | 0.6 |     | ns   |  |

| t <sub>IOCLR</sub>  |     | 0.2 |       | 0.2   |     | 0.4 | ns   |  |

| t <sub>OD1</sub>    |     | 1.2 |       | 1.2   |     | 1.9 | ns   |  |

| t <sub>OD2</sub>    |     | 0.7 |       | 0.8   |     | 1.7 | ns   |  |

| t <sub>OD3</sub>    |     | 2.7 |       | 3.0   |     | 4.3 | ns   |  |

| $t_{XZ}$            |     | 4.7 |       | 5.7   |     | 7.5 | ns   |  |

| $t_{ZX1}$           |     | 4.7 |       | 5.7   |     | 7.5 | ns   |  |

| $t_{ZX2}$           |     | 4.2 |       | 5.3   |     | 7.3 | ns   |  |

| $t_{ZX3}$           |     | 6.2 |       | 7.5   |     | 9.9 | ns   |  |

| t <sub>INREG</sub>  |     | 3.5 |       | 4.2   |     | 5.6 | ns   |  |

| t <sub>IOFD</sub>   |     | 1.1 |       | 1.3   |     | 1.8 | ns   |  |

| t <sub>INCOMB</sub> |     | 1.1 |       | 1.3   |     | 1.8 | ns   |  |

| Symbol                     |     |     | Speed | Grade |     |      | Unit |

|----------------------------|-----|-----|-------|-------|-----|------|------|

|                            | -1  |     | -     | -2    |     | 3    |      |

|                            | Min | Max | Min   | Max   | Min | Max  |      |

| t <sub>INSUBIDIR</sub> (2) | 2.7 |     | 3.2   |       | 4.3 |      | ns   |

| t <sub>INHBIDIR</sub> (2)  | 0.0 |     | 0.0   |       | 0.0 |      | ns   |

| t <sub>INSUBIDIR</sub> (3) | 3.7 |     | 4.2   |       | -   |      | ns   |

| t <sub>INHBIDIR</sub> (3)  | 0.0 |     | 0.0   |       | -   |      | ns   |

| toutcobidir (2)            | 2.0 | 4.5 | 2.0   | 5.2   | 2.0 | 7.3  | ns   |

| t <sub>XZBIDIR</sub> (2)   |     | 6.8 |       | 7.8   |     | 10.1 | ns   |

| t <sub>ZXBIDIR</sub> (2)   |     | 6.8 |       | 7.8   |     | 10.1 | ns   |

| toutcobidir (3)            | 0.5 | 3.5 | 0.5   | 4.2   | -   | -    |      |

| t <sub>XZBIDIR</sub> (3)   |     | 6.8 |       | 8.4   |     | -    | ns   |

| t <sub>ZXBIDIR</sub> (3)   |     | 6.8 |       | 8.4   |     | _    | ns   |

#### Notes to tables:

- All timing parameters are described in Tables 22 through 29. This parameter is measured without use of the ClockLock or ClockBoost circuits. (2)

- This parameter is measured with use of the ClockLock or ClockBoost circuits (3)

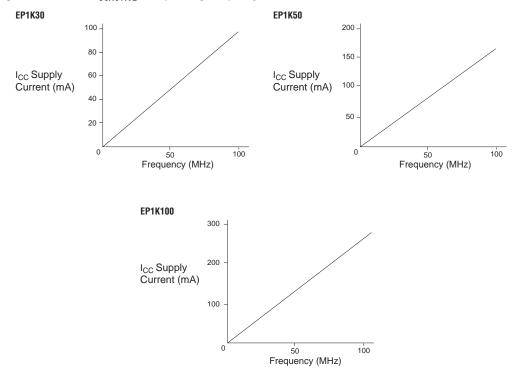

The I<sub>CCACTIVE</sub> value can be calculated with the following equation:

$$I_{CCACTIVE} = K \times f_{MAX} \times N \times tog_{LC} (\mu A)$$

Where:

**f**<sub>MAX</sub> = Maximum operating frequency in MHz N = Total number of LEs used in the device

tog<sub>LC</sub> = Average percent of LEs toggling at each clock

(typically 12.5%)

K = Constant

Table 58 provides the constant (K) values for ACEX 1K devices.

| Table 58. ACEX 1K Constant Values |         |

|-----------------------------------|---------|

| Device                            | K Value |

| EP1K10                            | 4.5     |

| EP1K30                            | 4.5     |

| EP1K50                            | 4.5     |

| EP1K100                           | 4.5     |

This supply power calculation provides an  $I_{CC}$  estimate based on typical conditions with no output load. The actual  $I_{CC}$  should be verified during operation because this measurement is sensitive to the actual pattern in the device and the environmental operating conditions.

To better reflect actual designs, the power model (and the constant K in the power calculation equations) for continuous interconnect ACEX 1K devices assumes that LEs drive FastTrack Interconnect channels. In contrast, the power model of segmented FPGAs assumes that all LEs drive only one short interconnect segment. This assumption may lead to inaccurate results when compared to measured power consumption for actual designs in segmented FPGAs.

Figure 31 shows the relationship between the current and operating frequency of ACEX 1K devices. For information on other ACEX 1K devices, contact Altera Applications at (800) 800-EPLD.

Figure 31. ACEX 1K I<sub>CCACTIVE</sub> vs. Operating Frequency

## Configuration & Operation

The ACEX 1K architecture supports several configuration schemes. This section summarizes the device operating modes and available device configuration schemes.

## **Operating Modes**

The ACEX 1K architecture uses SRAM configuration elements that require configuration data to be loaded every time the circuit powers up. The process of physically loading the SRAM data into the device is called *configuration*. Before configuration, as  $V_{CC}$  rises, the device initiates a Power-On Reset (POR). This POR event clears the device and prepares it for configuration. The ACEX 1K POR time does not exceed 50  $\mu s$ .

When configuring with a configuration device, refer to the relevant configuration device data sheet for POR timing information.

## Revision History

The information contained in the *ACEX 1K Programmable Logic Device Family Data Sheet* version 3.4 supersedes information published in previous versions.

The following changes were made to the *ACEX 1K Programmable Logic Device Family Data Sheet* version 3.4: added extended temperature support.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 www.altera.com Applications Hotline: (800) 800-EPLD Literature Services: lit\_req@altera.com

Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described

herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

I.S. EN ISO 9001