Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 27                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

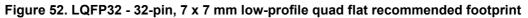

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l051k6t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 5. Functionalities depending on the working mode (from Run/active down to standby) (continued)<sup>(1)</sup>

|                                                     |                                                 |                                                | Low-    | Low-              |  | Stop                               |  | Stop Stand                             |  | standby |

|-----------------------------------------------------|-------------------------------------------------|------------------------------------------------|---------|-------------------|--|------------------------------------|--|----------------------------------------|--|---------|

| IPs                                                 | Run/Active                                      | Sleep power<br>run                             |         | power<br>sleep    |  | Wakeup<br>capability               |  | Wakeup<br>capability                   |  |         |

|                                                     |                                                 | Down to<br>37 µA/MHz<br>(from Flash<br>memory) |         | Down to<br>4.5 µA |  | ↓ μΑ (No<br>V <sub>DD</sub> =1.8 V |  | 28 µA (No<br>) V <sub>DD</sub> =1.8 V  |  |         |

| Consumption $V_{-} = 1.8 \text{ to } 3.6 \text{ V}$ | Down to<br>140 μA/MHz<br>(from Flash<br>memory) |                                                | Down to |                   |  | µA (with<br>V <sub>DD</sub> =1.8 V |  | 5 µA (with<br>) V <sub>DD</sub> =1.8 V |  |         |

| V <sub>DD</sub> =1.8 to 3.6 V<br>(Typ)              |                                                 |                                                | 8 µA    |                   |  | ↓μΑ (No<br>V <sub>DD</sub> =3.0 V  |  | 29 µA (No<br>) V <sub>DD</sub> =3.0 V  |  |         |

|                                                     |                                                 |                                                |         |                   |  | (with RTC)<br><sub>9D</sub> =3.0 V |  | 5 μΑ (with<br>) V <sub>DD</sub> =3.0 V |  |         |

1. Legend:

"Y" = Yes (enable). "O" = Optional can be enabled/disabled by software)

"-" = Not available

- Some peripherals with wakeup from Stop capability can request HSI to be enabled. In this case, HSI is woken up by the peripheral, and only feeds the peripheral which requested it. HSI is automatically put off when the peripheral does not need it anymore.

- 3. UART and LPUART reception is functional in Stop mode. It generates a wakeup interrupt on Start. To generate a wakeup on address match or received frame event, the LPUART can run on LSE clock while the UART has to wake up or keep running the HSI clock.

- 4. I2C address detection is functional in Stop mode. It generates a wakeup interrupt in case of address match. It will wake up the HSI during reception.

#### 3.2 Interconnect matrix

Several peripherals are directly interconnected. This allows autonomous communication between peripherals, thus saving CPU resources and power consumption. In addition, these hardware connections allow fast and predictable latency.

Depending on peripherals, these interconnections can operate in Run, Sleep, Low-power run, Low-power sleep and Stop modes.

| Interconnect Interconnect source destination |                      | Interconnect action                                               | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | Stop |  |

|----------------------------------------------|----------------------|-------------------------------------------------------------------|-----|-------|----------------------|------------------------|------|--|

| COMPx                                        | TIM2,TIM21,<br>TIM22 | Timer input channel,<br>trigger from analog<br>signals comparison | Y   | Y     | Y                    | Y                      | -    |  |

|                                              | LPTIM                | Timer input channel,<br>trigger from analog<br>signals comparison | Y   | Y     | Y                    | Y                      | Y    |  |

| TIMx                                         | TIMx                 | Timer triggered by other timer                                    | Y   | Y     | Y                    | Y                      | -    |  |

Table 6. STM32L0xx peripherals interconnect matrix

| Interconnect<br>source | Interconnect<br>destination | Interconnect action                                                         | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | Stop |  |

|------------------------|-----------------------------|-----------------------------------------------------------------------------|-----|-------|----------------------|------------------------|------|--|

| BTC                    | TIM21                       | Timer triggered by Auto<br>wake-up                                          | Y   | Y     | Y                    | Y                      | -    |  |

| RTC                    | LPTIM                       | Timer triggered by RTC event                                                | Y   | Y     | Y                    | Y                      | Y    |  |

| All clock<br>source    | TIMx                        | Clock source used as<br>input channel for RC<br>measurement and<br>trimming | Y   | Y     | Y                    | Y                      | -    |  |

| GPIO                   | TIMx                        | Timer input channel and trigger                                             | Y   | Y     | Y                    | Y                      | -    |  |

|                        | LPTIM                       | Timer input channel and trigger                                             | Y   | Y     | Y                    | Y                      | Y    |  |

|                        | ADC                         | Conversion trigger                                                          | Y   | Y     | Y                    | Y                      | -    |  |

Table 6. STM32L0xx peripherals interconnect matrix (continued)

# 3.3 ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core with MPU

The Cortex-M0+ processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- a simple architecture that is easy to learn and program

- ultra-low power, energy-efficient operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with Cortex-M processor family

- platform security robustness, with integrated Memory Protection Unit (MPU).

The Cortex-M0+ processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0+ processor provides the exceptional performance expected of a modern 32bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

Owing to its embedded ARM core, the STM32L051x6/8 are compatible with all ARM tools and software.

#### STM32L051x6 STM32L051x8

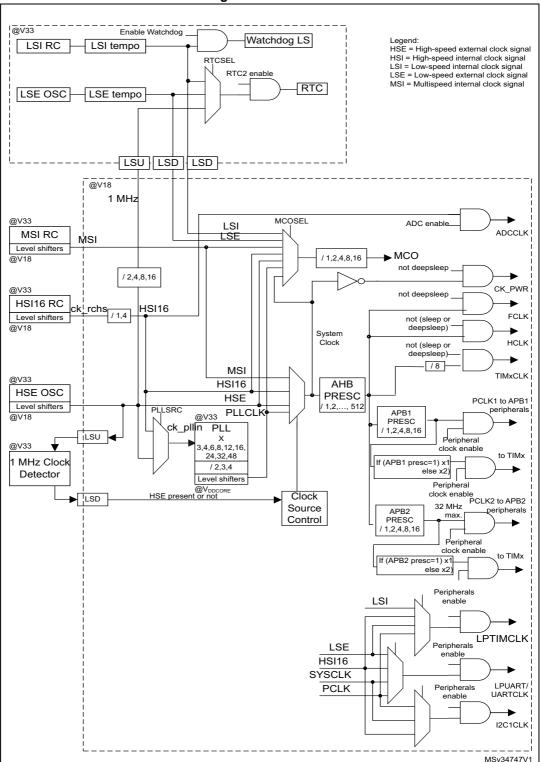

Figure 2. Clock tree

| 4<br>5            |        |      | Table 18. Alternate funct       | on port C |                            |

|-------------------|--------|------|---------------------------------|-----------|----------------------------|

| 45/131            | -      |      | AF0                             | AF1       | AF2                        |

|                   | P      | ort  | LPUART1/LPTIM/TIM21/12/EVENTOUT | -         | SPI2/I2S2/LPUART1/EVENTOUT |

|                   |        | PC0  | LPTIM1_IN1                      | -         | EVENTOUT                   |

|                   |        | PC1  | LPTIM1_OUT                      | -         | EVENTOUT                   |

|                   |        | PC2  | LPTIM1_IN2                      | -         | SPI2_MISO/I2S2_MCK         |

|                   |        | PC3  | LPTIM1_ETR                      | -         | SPI2_MOSI/I2S2_SD          |

|                   |        | PC4  | EVENTOUT                        | -         | LPUART1_TX                 |

|                   |        | PC5  |                                 | -         | LPUART1_RX                 |

|                   |        | PC6  | TIM22_CH1                       | -         | -                          |

|                   | Dert   | PC7  | TIM22_CH2                       | -         | -                          |

|                   | Port C | PC8  | TIM22_ETR                       | -         | -                          |

| Doc10035038 Dav 7 |        | PC9  | TIM21_ETR                       | -         | -                          |

| 0503              |        | PC10 | LPUART1_TX                      | -         | -                          |

| ö<br>U            |        | PC11 | LPUART1_RX                      | -         | -                          |

| 7                 |        | PC12 | -                               | -         | -                          |

|                   | PC13   | PC13 | -                               | -         | -                          |

|                   |        | PC14 | -                               | -         | -                          |

|                   |        | PC15 | -                               | -         | -                          |

# Table 19. Alternate function port D

|  | Port   |     | AF0            | AF1 |

|--|--------|-----|----------------|-----|

|  |        |     | LPUART1        | -   |

|  | Port D | PD2 | LPUART1_RTS_DE | -   |

Pin descriptions

# 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the ambient temperature condition summarized in *Table 23*.

| Symbol                          | Parameter                                                                                                                                                                                                                                                                                                                                           | Conditions                                          | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Тур  | Мах      | Unit |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|------|

|                                 |                                                                                                                                                                                                                                                                                                                                                     | BOR detector enabled                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -    | $\infty$ |      |

| t <sub>VDD</sub> <sup>(1)</sup> | V <sub>DD</sub> rise time rate                                                                                                                                                                                                                                                                                                                      | BOR detector disabled                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -    | 1000     |      |

| <sup>I</sup> VDD <sup>(1)</sup> |                                                                                                                                                                                                                                                                                                                                                     | BOR detector enabled                                | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -    | ∞        | µs/V |

|                                 | V <sub>DD</sub> fall time rate                                                                                                                                                                                                                                                                                                                      | BOR detector disabled                               | 0-∞0-100020-∞0-1000-23.30.40.71.611.51.651.31.51.651.671.71.741.691.761.81.871.931.972.222.302.352.312.412.442.452.552.62.542.662.72.682.82.852.782.92.951.81.851.881.881.941.991.982.042.092.082.142.182.202.242.282.282.342.38                                                                                                                                                                                                                                                                                                                                                                                                        |      |          |      |

| <b>T</b> (1)                    | Deast to measuration                                                                                                                                                                                                                                                                                                                                | V <sub>DD</sub> rising, BOR enabled                 | 0     -     0       0     -     10       20     -     10       20     -     10       0     -     10       -     20     -       0     -     10       -     2     3       0.4     0.7     1       1     1.5     1.       1.3     1.5     1.       1.67     1.7     1.       1.69     1.76     1       1.87     1.93     1.       1.96     2.03     2.       2.22     2.30     2.       2.31     2.41     2.       2.45     2.55     2       2.54     2.66     2       2.68     2.8     2.       2.78     2.9     2.       1.8     1.85     1.       1.98     2.04     2.       2.08     2.14     2.       2.08     2.14     2.       2.20 | 3.3  |          |      |

| RSTTEMPO <sup>(1)</sup>         | Reset temporization                                                                                                                                                                                                                                                                                                                                 | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.7  | 1.6      | ms   |

| M                               | Power-on/power down reset                                                                                                                                                                                                                                                                                                                           | Falling edge                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.5  | 1.65     |      |

| V <sub>POR/PDR</sub>            | threshold                                                                                                                                                                                                                                                                                                                                           | Rising edge                                         | 1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.5  | 1.65     |      |

|                                 |                                                                                                                                                                                                                                                                                                                                                     | Falling edge                                        | 1.67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.7  | 1.74     |      |

| V <sub>BOR0</sub>               | Brown-out reset threshold 0                                                                                                                                                                                                                                                                                                                         | Rising edge                                         | 1.69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.76 | 1.8      |      |

|                                 |                                                                                                                                                                                                                                                                                                                                                     | Falling edge                                        | 1.87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.93 | 1.97     |      |

| V <sub>BOR1</sub>               | Brown-out reset threshold 1                                                                                                                                                                                                                                                                                                                         | Rising edge                                         | 1.96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.03 | 2.07     |      |

|                                 | Drawn aut as at three shaled O                                                                                                                                                                                                                                                                                                                      | Falling edge                                        | 2.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.30 | 2.35     |      |

| V <sub>BOR2</sub>               | Brown-out reset threshold 2                                                                                                                                                                                                                                                                                                                         | Rising edge                                         | 2.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.41 | 2.44     |      |

| N/                              |                                                                                                                                                                                                                                                                                                                                                     | Falling edge                                        | 2.45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.55 | 2.6      |      |

| V <sub>BOR3</sub>               | Brown-out reset threshold 3 Rising edge                                                                                                                                                                                                                                                                                                             |                                                     | 2.54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.66 | 2.7      |      |

|                                 | VBOR2 Brown-out reset threshold 2 Rising edge   VBOR3 Brown-out reset threshold 3 Falling edge   VBOR4 Brown-out reset threshold 4 Falling edge | Falling edge                                        | 2.68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.8  | 2.85     |      |

| V <sub>BOR4</sub>               |                                                                                                                                                                                                                                                                                                                                                     | 2.78                                                | 2.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.95 |          |      |

|                                 | Programmable voltage detector                                                                                                                                                                                                                                                                                                                       | Falling edge                                        | 1.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.85 | 1.88     | V    |

| V <sub>PVD0</sub>               | threshold 0                                                                                                                                                                                                                                                                                                                                         | Rising edge                                         | 1.88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.94 | 1.99     |      |

| M                               | DVD three shales 4                                                                                                                                                                                                                                                                                                                                  | Falling edge                                        | 1.98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.04 | 2.09     |      |

| V <sub>PVD1</sub>               | PVD threshold 1                                                                                                                                                                                                                                                                                                                                     | Rising edge                                         | 2.08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.14 | 2.18     |      |

|                                 |                                                                                                                                                                                                                                                                                                                                                     | Falling edge                                        | 2.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.24 | 2.28     |      |

| V <sub>PVD2</sub>               | PVD threshold 2                                                                                                                                                                                                                                                                                                                                     | Rising edge                                         | 2.28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.34 | 2.38     |      |

|                                 | DVD threehold 2                                                                                                                                                                                                                                                                                                                                     | Falling edge                                        | 2.39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.44 | 2.48     | 1    |

| V <sub>PVD3</sub>               | PVD threshold 3                                                                                                                                                                                                                                                                                                                                     | Rising edge                                         | 2.47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.54 | 2.58     |      |

|                                 |                                                                                                                                                                                                                                                                                                                                                     | Falling edge                                        | 2.57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.64 | 2.69     |      |

| V <sub>PVD4</sub>               | PVD threshold 4                                                                                                                                                                                                                                                                                                                                     | Rising edge                                         | 2.68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.74 | 2.79     |      |

|                                 |                                                                                                                                                                                                                                                                                                                                                     | Falling edge                                        | 2.77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.83 | 2.88     |      |

| V <sub>PVD5</sub>               | PVD threshold 5                                                                                                                                                                                                                                                                                                                                     | Rising edge                                         | 2.87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.94 | 2.99     |      |

# Low-speed internal (LSI) RC oscillator

| Symbol                              | Parameter                                                   | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                               | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift<br>0°C ≤T <sub>A</sub> ≤85°C | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                 | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                            | -   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

# Multi-speed internal (MSI) RC oscillator

| Symbol                                                                                                                                                                                                                      | Parameter                                                                                  | Condition   | Тур   | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------|-------|------|------|

| f <sub>MSI</sub>                                                                                                                                                                                                            |                                                                                            | MSI range 0 | 65.5  | -    |      |

|                                                                                                                                                                                                                             |                                                                                            | MSI range 1 | 131   | -    |      |

|                                                                                                                                                                                                                             |                                                                                            | MSI range 2 | 262   | -    | kHz  |

|                                                                                                                                                                                                                             | Frequency after factory calibration, done at $V_{DD}$ = 3.3 V and T <sub>A</sub> = 25 °C   | MSI range 3 | 524   | -    |      |

|                                                                                                                                                                                                                             |                                                                                            | MSI range 4 | 1.05  | -    |      |

|                                                                                                                                                                                                                             |                                                                                            | MSI range 5 | 2.1   | -    | MHz  |

|                                                                                                                                                                                                                             |                                                                                            | MSI range 6 | 4.2   | -    |      |

| ACC <sub>MSI</sub>                                                                                                                                                                                                          | Frequency error after factory calibration                                                  | -           | ±0.5  | -    | %    |

|                                                                                                                                                                                                                             | MSI oscillator frequency drift<br>0 °C ≤T <sub>A</sub> <i>≤</i> 85 °C                      | -           | ±3    | -    |      |

| ACC <sub>MSI</sub> Frequency error after factory calibration     MSI oscillator frequency drift   - $0 \ ^{\circ}C \leq T_A \leq 85 \ ^{\circ}C$ -     D <sub>TEMP(MSI)</sub> <sup>(1)</sup> MSI oscillator frequency drift |                                                                                            | MSI range 0 | - 8.9 | +7.0 |      |

|                                                                                                                                                                                                                             | MSI range 1                                                                                | - 7.1       | +5.0  |      |      |

| D <sub>TEMP(MSI)</sub> <sup>(1)</sup>                                                                                                                                                                                       |                                                                                            | MSI range 2 | - 6.4 | +4.0 | %    |

|                                                                                                                                                                                                                             | MSI oscillator frequency drift<br>V <sub>DD</sub> = 3.3 V, − 40 °C ≤T <sub>A</sub> ≤110 °C | MSI range 3 | - 6.2 | +3.0 |      |

|                                                                                                                                                                                                                             |                                                                                            | MSI range 4 | - 5.2 | +3.0 |      |

|                                                                                                                                                                                                                             |                                                                                            | MSI range 5 | - 4.8 | +2.0 |      |

|                                                                                                                                                                                                                             |                                                                                            | MSI range 6 | - 4.7 | +2.0 |      |

| D <sub>VOLT(MSI)</sub> <sup>(1)</sup>                                                                                                                                                                                       | MSI oscillator frequency drift<br>1.65 V ≤V <sub>DD</sub> ≤3.6 V, T <sub>A</sub> = 25 °C   | -           | -     | 2.5  | %/V  |

#### Table 46. MSI oscillator characteristics

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol                |            |                                                                                   | Monitored       | Мах             | vs. f <sub>osc</sub> /1 | СРИ              |      |

|-----------------------|------------|-----------------------------------------------------------------------------------|-----------------|-----------------|-------------------------|------------------|------|

|                       | Parameter  | Conditions                                                                        | frequency band  | 8 MHz/<br>4 MHz | 8 MHz/<br>16 MHz        | 8 MHz/<br>32 MHz | Unit |

| S <sub>EMI</sub> Peak |            | Peak level $V_{DD} = 3.6 V$ ,<br>$T_A = 25 °C$ ,<br>compliant with IEC<br>61967-2 | 0.1 to 30 MHz   | -21             | -15                     | -12              |      |

|                       | Dook lovel |                                                                                   | 30 to 130 MHz   | -14             | -12                     | -1               | dBµV |

|                       | CC         |                                                                                   | 130 MHz to 1GHz | -10             | -11                     | -7               |      |

|                       |            |                                                                                   | EMI Level       | 1               | 1                       | 1                | -    |

| Table | 52. | EMI | characteristics |

|-------|-----|-----|-----------------|

# 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence oscillator frequency deviation).

The test results are given in the Table 55.

|                  |                                                                     | Functional s       |                    |      |

|------------------|---------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                         | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0                                           | -0                 | NA                 |      |

| I <sub>INJ</sub> | Injected current on PA0, PA4, PA5, PA11,<br>PA12, PC15, PH0 and PH1 | -5                 | 0                  | mA   |

|                  | Injected current on any other FT, FTf pins                          | -5 <sup>(1)</sup>  | NA                 |      |

|                  | Injected current on any other pins                                  | -5 <sup>(1)</sup>  | +5                 |      |

#### Table 55. I/O current injection susceptibility

1. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

## **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 23*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                | Conditions                                                                                         | Min                   | Max  | Unit |

|-----------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup> ,<br>I <sub>IO</sub> = +8 mA                                              | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin | $1_{\text{IO}} = 1_{\text{O}} = 1_{\text{O}}$<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V         | V <sub>DD</sub> -0.4  | -    |      |

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin  | TTL port <sup>(2)</sup> ,<br>$I_{IO}$ =+ 8 mA<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V         | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | TTL port <sup>(2)</sup> ,<br>$I_{IO} = -6 \text{ mA}$<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V | 2.4                   | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> |                                          |                                                                                                    | -                     | 1.3  | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | $I_{IO}$ = -15 mA<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                     | V <sub>DD</sub> -1.3  | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +4 mA<br>1.65 V ≤V <sub>DD</sub> < 3.6 V                                         | -                     | 0.45 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | $I_{IO}$ = -4 mA<br>1.65 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                     | V <sub>DD</sub> -0.45 | -    |      |

| V <sub>OLFM+</sub> (1)(4)         | Output low level voltage for an FTf      | $I_{IO} = 20 \text{ mA}$ $2.7 \text{ V} \leq V_{DD} \leq 3.6 \text{ V}$                            | -                     | 0.4  |      |

| VOLFM+                            | I/O pin in Fm+ mode                      | $I_{IO}$ = 10 mA<br>1.65 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                     | -                     | 0.4  |      |

The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 21*. The sum of the currents sunk by all the I/Os (I/O ports and control pins) must always be respected and must not exceed ΣI<sub>IO(PIN)</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 21. The sum of the currents sourced by all the I/Os (I/O ports and control pins) must always be respected and must not exceed  $\Sigma I_{IO(PIN)}$ .

4. Guaranteed by characterization results.

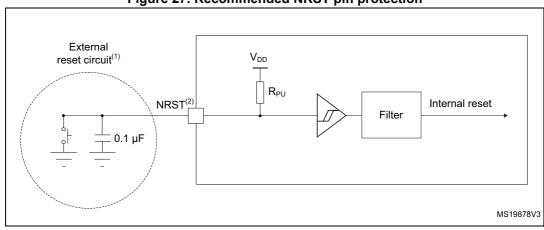

Figure 27. Recommended NRST pin protection

- 1. The reset network protects the device against parasitic resets.

- 2. The external capacitor must be placed as close as possible to the device.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 59. Otherwise the reset will not be taken into account by the device.

## 6.3.15 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 60* are derived from tests performed under ambient temperature, f<sub>PCLK</sub> frequency and V<sub>DDA</sub> supply voltage conditions summarized in *Table 23: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                           | Parameter                                        | Conditions                                      | Min                 | Тур | Мах               | Unit               |  |

|----------------------------------|--------------------------------------------------|-------------------------------------------------|---------------------|-----|-------------------|--------------------|--|

|                                  | Analog supply voltage for                        | Fast channel                                    | 1.65                | -   | 3.6               |                    |  |

| V <sub>DDA</sub>                 | ADC ON                                           | Standard channel                                | 1.75 <sup>(1)</sup> | -   | 3.6               | V                  |  |

| V <sub>REF+</sub>                | Positive reference voltage                       | -                                               | 1.65                |     | V <sub>DDA</sub>  | V                  |  |

|                                  | Current consumption of the                       | 1.14 Msps                                       | -                   | 200 | -                 |                    |  |

| I <sub>DDA (ADC)</sub>           | ADC on $V_{DDA}$ and $V_{REF+}$                  | 10 ksps                                         | -                   | 40  | -                 |                    |  |

|                                  | Current consumption of the ADC on $V_{DD}^{(2)}$ | 1.14 Msps                                       | -                   | 70  | -                 | μA                 |  |

|                                  |                                                  | 10 ksps                                         | -                   | 1   | -                 |                    |  |

|                                  | ADC clock frequency                              | Voltage scaling Range 1                         | 0.14                | -   | 16                |                    |  |

| f <sub>ADC</sub>                 |                                                  | Voltage scaling Range 2                         | 0.14                | -   | 8                 | MHz                |  |

|                                  |                                                  | Voltage scaling Range 3                         | 0.14                | -   | 4                 |                    |  |

| $f_S^{(3)}$                      | Sampling rate                                    | 12-bit resolution                               | 0.01                | -   | 1.14              | MHz                |  |

| f <sub>TRIG</sub> <sup>(3)</sup> | External trigger frequency                       | f <sub>ADC</sub> = 16 MHz,<br>12-bit resolution | -                   | -   | 941               | kHz                |  |

|                                  |                                                  | -                                               | -                   | -   | 17                | 1/f <sub>ADC</sub> |  |

| V <sub>AIN</sub>                 | Conversion voltage range                         | -                                               | 0                   | -   | V <sub>REF+</sub> | V                  |  |

### Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} < \frac{T_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The simplified formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

|                            |                        | P may for                                         |       | R <sub>AIN</sub> max for standard channels (kΩ) |                             |                                                            |                                                           |       |       |  |  |

|----------------------------|------------------------|---------------------------------------------------|-------|-------------------------------------------------|-----------------------------|------------------------------------------------------------|-----------------------------------------------------------|-------|-------|--|--|

| T <sub>s</sub><br>(cycles) | t <sub>S</sub><br>(μs) | R <sub>AIN</sub> max for<br>fast channels<br>(kΩ) |       |                                                 | V <sub>DD</sub> ><br>1.75 V | V <sub>DD</sub> > 1.65 V<br>and<br>T <sub>A</sub> > -10 °C | V <sub>DD</sub> > 1.65 V<br>and<br>T <sub>A</sub> > 25 °C |       |       |  |  |

| 1.5                        | 0.09                   | 0.5                                               | < 0.1 | NA                                              | NA                          | NA                                                         | NA                                                        | NA    | NA    |  |  |

| 3.5                        | 0.22                   | 1                                                 | 0.2   | < 0.1                                           | NA                          | NA                                                         | NA                                                        | NA    | NA    |  |  |

| 7.5                        | 0.47                   | 2.5                                               | 1.7   | 1.5                                             | < 0.1                       | NA                                                         | NA                                                        | NA    | NA    |  |  |

| 12.5                       | 0.78                   | 4                                                 | 3.2   | 3                                               | 1                           | NA                                                         | NA                                                        | NA    | NA    |  |  |

| 19.5                       | 1.22                   | 6.5                                               | 5.7   | 5.5                                             | 3.5                         | NA                                                         | NA                                                        | NA    | < 0.1 |  |  |

| 39.5                       | 2.47                   | 13                                                | 12.2  | 12                                              | 10                          | NA                                                         | NA                                                        | NA    | 5     |  |  |

| 79.5                       | 4.97                   | 27                                                | 26.2  | 26                                              | 24                          | < 0.1                                                      | NA                                                        | NA    | 19    |  |  |

| 160.5                      | 10.03                  | 50                                                | 49.2  | 49                                              | 47                          | 32                                                         | < 0.1                                                     | < 0.1 | 42    |  |  |

Table 61.  $R_{AIN}$  max for  $f_{ADC}$  = 16 MHz<sup>(1)</sup>

1. Guaranteed by design.

Table 62. ADC accuracy<sup>(1)(2)(3)</sup>

| Symbol | Parameter                                                                          | Conditions                                                            | Min  | Тур  | Max | Unit |

|--------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|------|-----|------|

| ET     | Total unadjusted error                                                             |                                                                       | -    | 2    | 4   |      |

| EO     | Offset error                                                                       |                                                                       | -    | 1    | 2.5 |      |

| EG     | Gain error                                                                         |                                                                       | -    | 1    | 2   | LSB  |

| EL     | Integral linearity error                                                           | 1.65 V < V <sub>DDA</sub> = V <sub>REF+</sub> < 3.6 V,<br>range 1/2/3 | -    | 1.5  | 2.5 |      |

| ED     | Differential linearity error                                                       |                                                                       | -    | 1    | 1.5 |      |

|        | Effective number of bits                                                           |                                                                       | 10.2 | 11   |     |      |

| ENOB   | Effective number of bits (16-bit mode oversampling with ratio =256) <sup>(4)</sup> |                                                                       | 11.3 | 12.1 | -   | bits |

| SINAD  | Signal-to-noise distortion                                                         |                                                                       | 63   | 69   | -   |      |

|        | Signal-to-noise ratio                                                              |                                                                       | 63   | 69   | -   |      |

| SNR    | Signal-to-noise ratio (16-bit mode oversampling with ratio =256) <sup>(4)</sup>    |                                                                       | 70   | 76   | -   | dB   |

| THD    | Total harmonic distortion                                                          |                                                                       | -    | -85  | -73 |      |

# 6.3.17 Comparators

| Symbol                   | Parameter                                                      | Conditions                                                                                                                                                                                       | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |  |

|--------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|--|

| $V_{DDA}$                | Analog supply voltage                                          | -                                                                                                                                                                                                | 1.65               |     | 3.6                | V         |  |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                        | -                                                                                                                                                                                                | -                  | 400 | -                  | kΩ        |  |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                         | -                                                                                                                                                                                                | -                  | 10  | -                  |           |  |

| V <sub>IN</sub>          | Comparator 1 input voltage range                               | -                                                                                                                                                                                                | 0.6                | -   | V <sub>DDA</sub>   | V         |  |

| t <sub>START</sub>       | Comparator startup time                                        | -                                                                                                                                                                                                | -                  | 7   | 10                 | 110       |  |

| td                       | Propagation delay <sup>(2)</sup>                               | -                                                                                                                                                                                                | -                  | 3   | 10                 | - μs      |  |

| Voffset                  | Comparator offset                                              | -                                                                                                                                                                                                | -                  | ±3  | ±10                | mV        |  |

| d <sub>Voffset</sub> /dt | Comparator offset variation in worst voltage stress conditions | $\label{eq:VDDA} \begin{split} V_{DDA} &= 3.6 \text{ V},  \text{V}_{\text{IN+}} = 0 \text{ V}, \\ V_{\text{IN-}} &= V_{\text{REFINT}},  \text{T}_{\text{A}} = 25 \ ^{\circ}\text{C} \end{split}$ | 0                  | 1.5 | 10                 | mV/1000 h |  |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                             | -                                                                                                                                                                                                | -                  | 160 | 260                | nA        |  |

1. Guaranteed by characterization.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

| Symbol              | Parameter                                     | Conditions                                                                                                                                                                                                                                          | Min  | Тур       | Max <sup>(1)</sup> | Unit       |