Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 27                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l051k8u6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM<sup>®</sup> Cortex<sup>®</sup>-M4, including ARM<sup>®</sup> Cortex<sup>®</sup>-M3 and ARM<sup>®</sup> Cortex<sup>®</sup>-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 ultra-low-power series are the best solution for applications such as gaz/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

| Interconnect<br>source | Interconnect<br>destination | Interconnect action                                                         | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | Stop |

|------------------------|-----------------------------|-----------------------------------------------------------------------------|-----|-------|----------------------|------------------------|------|

| BTC                    | TIM21                       | Timer triggered by Auto<br>wake-up                                          | Y   | Y     | Y                    | Y                      | -    |

| RTC -                  | LPTIM                       | Timer triggered by RTC event                                                | Y   | Y     | Y                    | Y                      | Y    |

| All clock<br>source    | TIMx                        | Clock source used as<br>input channel for RC<br>measurement and<br>trimming | Y   | Y     | Y                    | Y                      | -    |

|                        | TIMx                        | Timer input channel and trigger                                             | Y   | Y     | Y                    | Y                      | -    |

| GPIO                   | LPTIM                       | Timer input channel and trigger                                             | Y   | Y     | Y                    | Y                      | Y    |

|                        | ADC                         | Conversion trigger                                                          | Y   | Y     | Y                    | Y                      | -    |

Table 6. STM32L0xx peripherals interconnect matrix (continued)

### 3.3 ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core with MPU

The Cortex-M0+ processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- a simple architecture that is easy to learn and program

- ultra-low power, energy-efficient operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with Cortex-M processor family

- platform security robustness, with integrated Memory Protection Unit (MPU).

The Cortex-M0+ processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0+ processor provides the exceptional performance expected of a modern 32bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

Owing to its embedded ARM core, the STM32L051x6/8 are compatible with all ARM tools and software.

#### 3.16.2 Universal synchronous/asynchronous receiver transmitter (USART)

The two USART interfaces (USART1, USART2) are able to communicate at speeds of up to 4 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 driver enable (DE) signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. They also support SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability, auto baud rate feature and has a clock domain independent from the CPU clock, allowing to wake up the MCU from Stop mode using baudrates up to 42 Kbaud.

All USART interfaces can be served by the DMA controller.

Table 12 for the supported modes and features of USART interfaces.

| USART modes/features <sup>(1)</sup>         | USART1 and USART2 |

|---------------------------------------------|-------------------|

| Hardware flow control for modem             | Х                 |

| Continuous communication using DMA          | X                 |

| Multiprocessor communication                | X                 |

| Synchronous mode <sup>(2)</sup>             | X                 |

| Smartcard mode                              | Х                 |

| Single-wire half-duplex communication       | X                 |

| IrDA SIR ENDEC block                        | X                 |

| LIN mode                                    | X                 |

| Dual clock domain and wakeup from Stop mode | X                 |

| Receiver timeout interrupt                  | Х                 |

| Modbus communication                        | Х                 |

| Auto baud rate detection (4 modes)          | Х                 |

| Driver Enable                               | Х                 |

|                                             | •                 |

| Table 12 | . USART | implemen | tation |

|----------|---------|----------|--------|

|----------|---------|----------|--------|

1. X = supported.

2. This mode allows using the USART as an SPI master.

#### 3.16.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock. It can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

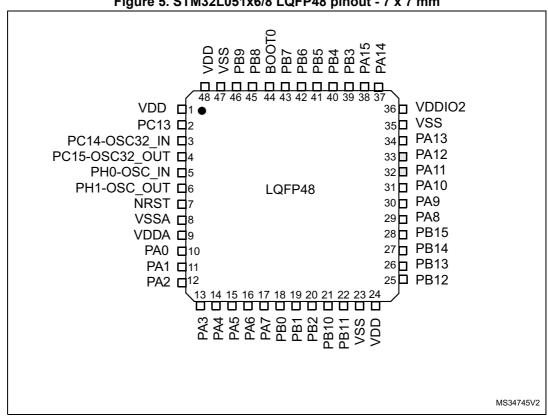

Figure 5. STM32L051x6/8 LQFP48 pinout - 7 x 7 mm

1. The above figure shows the package top view.

2. I/O supplied by VDDIO2.

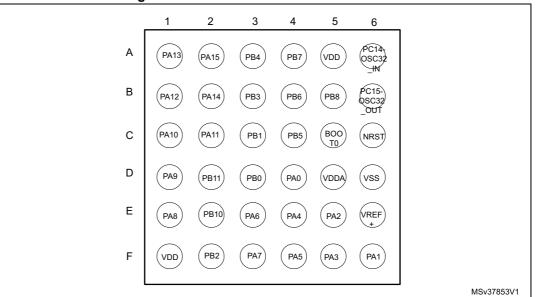

Figure 6. STM32L051x6/8 WLCSP36 ballout

1. The above figure shows the package top view.

1. The above figure shows the package top view.

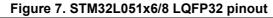

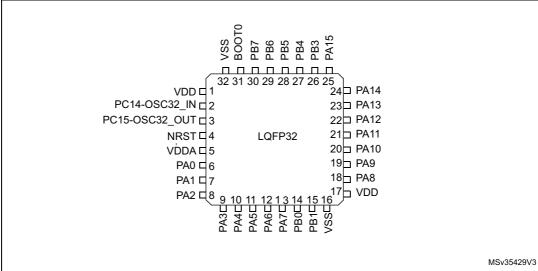

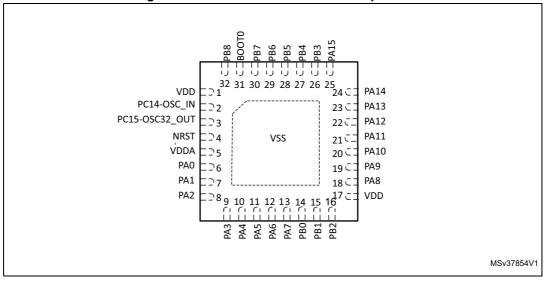

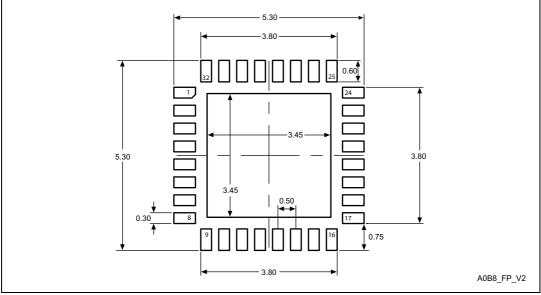

Figure 8. STM32L051x6/8 UFQFPN32 pinout

1. The above figure shows the package top view.

| Nar                                                                         | ne                     | Abbreviation                                   | Definition                                                                           |  |  |  |  |  |

|-----------------------------------------------------------------------------|------------------------|------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin n                                                                       | ame                    |                                                | ed in brackets below the pin name, the pin function during ne as the actual pin name |  |  |  |  |  |

|                                                                             |                        | S                                              | Supply pin                                                                           |  |  |  |  |  |

| Pin t                                                                       | уре                    | I                                              | Input only pin                                                                       |  |  |  |  |  |

|                                                                             |                        | I/O                                            | Input / output pin                                                                   |  |  |  |  |  |

|                                                                             |                        | FT                                             | 5 V tolerant I/O                                                                     |  |  |  |  |  |

|                                                                             |                        | FTf                                            | 5 V tolerant I/O, FM+ capable                                                        |  |  |  |  |  |

| I/O stru                                                                    | ucture                 | TC                                             | Standard 3.3V I/O                                                                    |  |  |  |  |  |

|                                                                             |                        | В                                              | Dedicated BOOT0 pin                                                                  |  |  |  |  |  |

|                                                                             |                        | RST                                            | Bidirectional reset pin with embedded weak pull-up resistor                          |  |  |  |  |  |

| Not                                                                         | es                     | Unless otherwise specific after reset.         | ed by a note, all I/Os are set as floating inputs during and                         |  |  |  |  |  |

| Pin functions                                                               | Alternate<br>functions | Functions selected through GPIOx_AFR registers |                                                                                      |  |  |  |  |  |

| Additional functions directly selected/enabled through peripheral registers |                        |                                                |                                                                                      |  |  |  |  |  |

#### Table 14. Legend/abbreviations used in the pinout table

#### Table 15. STM32L051x6/8 pin definitions

|        |         | Pin Nu | umber                  |        |          |                                       |          |               |       |                     |                                            |

|--------|---------|--------|------------------------|--------|----------|---------------------------------------|----------|---------------|-------|---------------------|--------------------------------------------|

| LQFP64 | TFBGA64 | LQFP48 | WLCSP36 <sup>(1)</sup> | LQFP32 | UFQFPN32 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions | Additional<br>functions                    |

| 1      | B2      | 1      | -                      | -      | -        | VDD                                   | S        | -             | -     | -                   | -                                          |

| 2      | A2      | 2      | -                      | -      | -        | PC13                                  | I/O      | FT            | -     | -                   | RTC_TAMP1/<br>RTC_TS/<br>RTC_OUT/<br>WKUP2 |

| 3      | A1      | 3      | A6                     | 2      | 2        | PC14-<br>OSC32_IN<br>(PC14)           | I/O      | FT            | -     | -                   | OSC32_IN                                   |

| 4      | B1      | 4      | B6                     | 3      | 3        | PC15-<br>OSC32_OUT<br>(PC15)          | I/O      | тс            | -     | -                   | OSC32_OUT                                  |

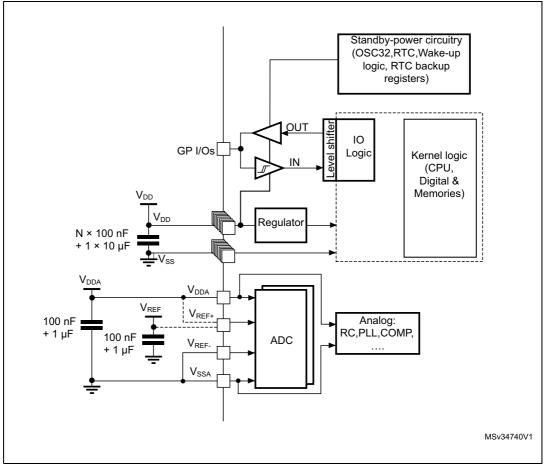

#### Power supply scheme 6.1.6

Figure 12. Power supply scheme

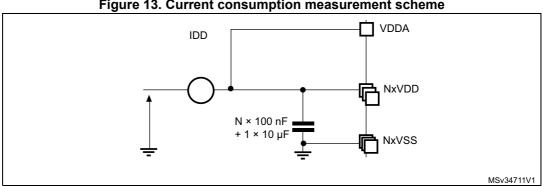

#### 6.1.7 **Current consumption measurement**

### Figure 13. Current consumption measurement scheme

### 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the ambient temperature condition summarized in *Table 23*.

| Symbol                          | Parameter                      | Conditions                                          | Min  | Тур  | Мах      | Unit |

|---------------------------------|--------------------------------|-----------------------------------------------------|------|------|----------|------|

|                                 |                                | BOR detector enabled                                | 0    | -    | $\infty$ |      |

| + (1)                           | V <sub>DD</sub> rise time rate | BOR detector disabled                               | 0    | -    | 1000     |      |

| t <sub>VDD</sub> <sup>(1)</sup> |                                | BOR detector enabled                                | 20   | -    | ∞        | µs/V |

|                                 | V <sub>DD</sub> fall time rate | BOR detector disabled                               | 0    | -    | 1000     |      |

| <b>T</b> (1)                    | Deast to magination            | V <sub>DD</sub> rising, BOR enabled                 | -    | 2    | 3.3      |      |

| RSTTEMPO <sup>(1)</sup>         | Reset temporization            | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6      | ms   |

| M                               | Power-on/power down reset      | Falling edge                                        | 1    | 1.5  | 1.65     |      |

| V <sub>POR/PDR</sub>            | threshold                      | Rising edge                                         | 1.3  | 1.5  | 1.65     |      |

|                                 |                                | Falling edge                                        | 1.67 | 1.7  | 1.74     |      |

| V <sub>BOR0</sub>               | Brown-out reset threshold 0    | Rising edge                                         | 1.69 | 1.76 | 1.8      |      |

|                                 |                                | Falling edge                                        | 1.87 | 1.93 | 1.97     |      |

| V <sub>BOR1</sub>               | Brown-out reset threshold 1    | Rising edge                                         | 1.96 | 2.03 | 2.07     |      |

|                                 |                                | Falling edge                                        | 2.22 | 2.30 | 2.35     |      |

| V <sub>BOR2</sub>               | Brown-out reset threshold 2    | Rising edge                                         | 2.31 | 2.41 | 2.44     |      |

|                                 |                                | Falling edge                                        | 2.45 | 2.55 | 2.6      |      |

| V <sub>BOR3</sub>               | Brown-out reset threshold 3    | Rising edge                                         | 2.54 | 2.66 | 2.7      |      |

|                                 |                                | Falling edge                                        | 2.68 | 2.8  | 2.85     |      |

| V <sub>BOR4</sub>               | Brown-out reset threshold 4    | Rising edge                                         | 2.78 | 2.9  | 2.95     |      |

|                                 | Programmable voltage detector  | Falling edge                                        | 1.8  | 1.85 | 1.88     | V    |

| V <sub>PVD0</sub>               | threshold 0                    | Rising edge                                         | 1.88 | 1.94 | 1.99     |      |

| M                               | DVD three shales 4             | Falling edge                                        | 1.98 | 2.04 | 2.09     |      |

| V <sub>PVD1</sub>               | PVD threshold 1                | Rising edge                                         | 2.08 | 2.14 | 2.18     |      |

|                                 |                                | Falling edge                                        | 2.20 | 2.24 | 2.28     |      |

| V <sub>PVD2</sub>               | PVD threshold 2                | Rising edge                                         | 2.28 | 2.34 | 2.38     |      |

|                                 | DV/D threehold 2               | Falling edge                                        | 2.39 | 2.44 | 2.48     | 1    |

| V <sub>PVD3</sub>               | PVD threshold 3                | Rising edge                                         | 2.47 | 2.54 | 2.58     |      |

|                                 |                                | Falling edge                                        | 2.57 | 2.64 | 2.69     |      |

| V <sub>PVD4</sub>               | PVD threshold 4 Rising         | Rising edge                                         | 2.68 | 2.74 | 2.79     |      |

|                                 |                                | Falling edge                                        | 2.77 | 2.83 | 2.88     |      |

| V <sub>PVD5</sub>               | PVD threshold 5                | Rising edge                                         | 2.87 | 2.94 | 2.99     |      |

| Symbol            | Parameter       | Conditions                                | Min  | Тур  | Max  | Unit |

|-------------------|-----------------|-------------------------------------------|------|------|------|------|

| M                 | PVD threshold 6 | Falling edge                              | 2.97 | 3.05 | 3.09 | V    |

| V <sub>PVD6</sub> |                 | Rising edge                               | 3.08 | 3.15 | 3.20 | v    |

|                   |                 | BOR0 threshold                            | -    | 40   | -    |      |

| V <sub>hyst</sub> |                 | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

Table 24. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

### 6.3.3 Embedded internal reference voltage

The parameters given in *Table 26* are based on characterization results, unless otherwise specified.

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

|                        | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

| Symbol                                   | Parameter                                                            | Conditions                                                                              | Min   | Тур   | Max   | Unit   |

|------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                           | – 40 °C < T <sub>J</sub> < +125 °C                                                      | 1.202 | 1.224 | 1.242 | V      |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                      | -                                                                                       | -     | 2     | 3     | ms     |

| V <sub>VREF_MEAS</sub>                   | $V_{DDA}$ and $V_{REF+}$ voltage during $V_{REFINT}$ factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V      |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured $V_{REFINT}$ value <sup>(3)</sup>       | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV     |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                              | –40 °C < T <sub>J</sub> < +125 °C                                                       | -     | 25    | 100   | ppm/°C |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                  | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm    |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                  | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V  |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage  | -                                                                                       | 5     | 10    | -     | μs     |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                     | -                                                                                       | -     | -     | 10    | μs     |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                      | -                                                                                       | -     | 13.5  | 25    | μA     |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                               | -                                                                                       | -     | -     | 1     | μA     |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                 | -                                                                                       | -     | -     | 50    | pF     |

#### Table 26. Embedded internal reference voltage<sup>(1)</sup>

| ·           | Typical consumption, $V_{DD}$ = 3.0 V, $T_A$ = 25 °C  |                                                       |                                                       |                               |                                |

|-------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------|--------------------------------|

| Peripheral  | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                           |

| All enabled | 283                                                   | 225                                                   | 222.5                                                 | 212.5                         | µA/MHz<br>(f <sub>HCLK</sub> ) |

| PWR         | 2.5                                                   | 2                                                     | 2                                                     | 1                             | µA/MHz<br>(f <sub>HCLK</sub> ) |

| Table 37. Perig | oheral current consum | ption in Run or Slee | p mode <sup>(1)</sup> (continued) |

|-----------------|-----------------------|----------------------|-----------------------------------|

|                 |                       |                      |                                   |

Data based on differential I<sub>DD</sub> measurement between all peripherals OFF an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (range 1), f<sub>HCLK</sub> = 16 MHz (range 2), f<sub>HCLK</sub> = 4 MHz (range 3), f<sub>HCLK</sub> = 64kHz (Low-power run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling. Not tested in production.

2. HSI oscillator is OFF for this measure.

3. Current consumption is negligible and close to 0 µA.

| Symbol                     | Parinharal                   | Typical consump        |                        | Unit   |

|----------------------------|------------------------------|------------------------|------------------------|--------|

| Symbol                     | Peripheral -                 | V <sub>DD</sub> =1.8 V | V <sub>DD</sub> =3.0 V | – Unit |

| I <sub>DD(PVD / BOR)</sub> | -                            | 0.7                    | 1.2                    |        |

| I <sub>REFINT</sub>        | -                            | -                      | 1.4                    |        |

| -                          | LSE Low drive <sup>(2)</sup> | 0,1                    | 0,1                    |        |

| -                          | LPTIM1, Input 100 Hz         | 0,01                   | 0,01                   | μΑ     |

| -                          | LPTIM1, Input 1 MHz          | 6                      | 6                      |        |

| -                          | LPUART1                      | 0,2                    | 0,2                    |        |

| -                          | RTC                          | 0,3                    | 0,48                   |        |

#### Table 38. Peripheral current consumption in Stop and Standby mode<sup>(1)</sup>

1. LPTIM peripheral cannot operate in Standby mode.

2. LSE Low drive consumption is the difference between an external clock on OSC32\_IN and a quartz between OSC32\_IN and OSC32\_OUT.-

### 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                               | Conditions                                                     | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/JEDEC JS-001  | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/ESD STM5.3.1. | C4    | 500                             | v    |

Table 53. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 54. Electrical sensitivities

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +125$ °C conforming to JESD78A | II level A |

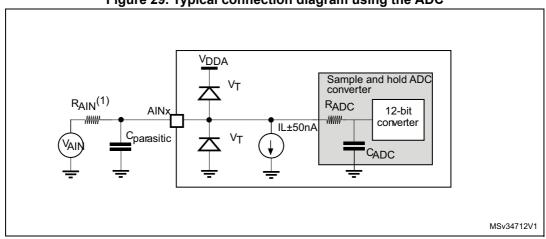

Figure 29. Typical connection diagram using the ADC

- 1. Refer to Table 60: ADC characteristics for the values of RAIN, RADC and CADC.

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

#### **General PCB design guidelines**

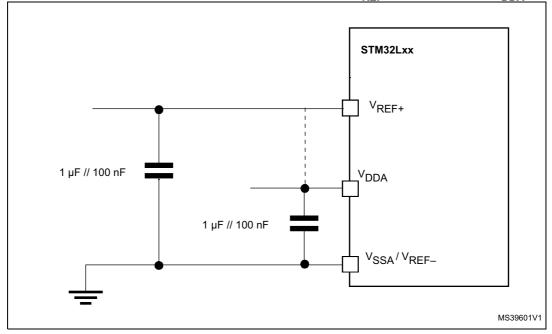

Power supply decoupling should be performed as shown in *Figure 30* or *Figure 31*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

Figure 30. Power supply and reference decoupling (V<sub>REF+</sub> not connected to V<sub>DDA</sub>)

#### 6.3.18 Timer characteristics

#### **TIM timer characteristics**

The parameters given in the Table 67 are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                               | Conditions                    | Min    | Max                     | Unit                 |  |  |

|------------------------|---------------------------------------------------------|-------------------------------|--------|-------------------------|----------------------|--|--|

| t ann                  | Timer resolution time                                   |                               | 1      | -                       | t <sub>TIMxCLK</sub> |  |  |

| <sup>t</sup> res(TIM)  |                                                         | f <sub>TIMxCLK</sub> = 32 MHz | 31.25  | -                       | ns                   |  |  |

| f                      | Timer external clock frequency on CH1                   |                               | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |  |

| f <sub>EXT</sub>       | to CH4                                                  | f <sub>TIMxCLK</sub> = 32 MHz | 0      | 16                      | MHz                  |  |  |

| Res <sub>TIM</sub>     | Timer resolution                                        | -                             |        | 16                      | bit                  |  |  |

|                        | 16-bit counter clock period when                        | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |  |

| t <sub>COUNTER</sub>   | internal clock is selected (timer's prescaler disabled) | f <sub>TIMxCLK</sub> = 32 MHz | 0.0312 | 2048                    | μs                   |  |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count                                  | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |  |

|                        |                                                         | f <sub>TIMxCLK</sub> = 32 MHz | -      | 134.2                   | s                    |  |  |

Table 67. TIMx characteristics<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM2, TIM6, TIM21, and TIM22 timers.

#### 6.3.19 Communications interfaces

#### I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm) : with a bit rate up to 100 kbit/s

- Fast-mode (Fm) : with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+) : with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timing requirements are guaranteed by design when the I<sup>2</sup>C peripheral is properly configured (refer to the reference manual for details). The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and VDDIOx is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement (refer to *Section 6.3.13: I/O port characteristics* for the I2C I/Os characteristics).

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter (see *Table 68* for the analog filter characteristics).

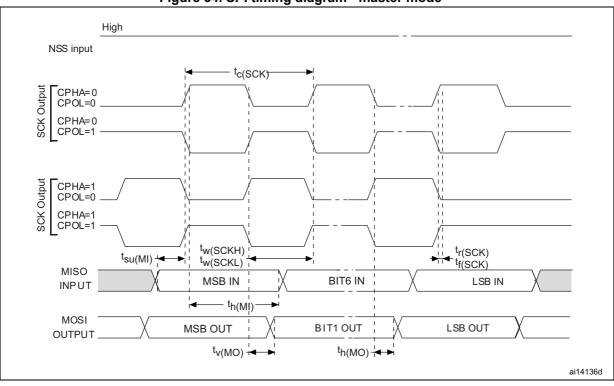

Figure 34. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

## Table 75. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ballgrid array package mechanical data (continued)

| Symbol | millimeters |     |       | inches <sup>(1)</sup> |     |        |

|--------|-------------|-----|-------|-----------------------|-----|--------|

| Symbol | Min         | Тур | Max   | Min                   | Тур | Мах    |

| ddd    | -           | -   | 0.080 | -                     | -   | 0.0031 |

| eee    | -           | -   | 0.150 | -                     | -   | 0.0059 |

| fff    | -           | -   | 0.050 | -                     | -   | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

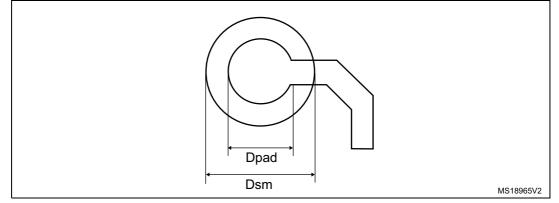

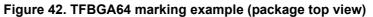

# Figure 41. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball ,grid array recommended footprint

#### Table 76. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension    | Recommended values                                              |  |  |

|--------------|-----------------------------------------------------------------|--|--|

| Pitch        | 0.5                                                             |  |  |

| Dpad         | 0.27 mm                                                         |  |  |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |  |  |

| Solder paste | 0.27 mm aperture diameter.                                      |  |  |

Note:Non solder mask defined (NSMD) pads are recommended.4 to 6 mils solder paste screen printing process.

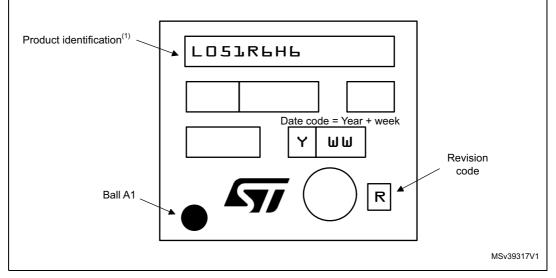

#### **Device marking for TFBGA64**

The following figure gives an example of topside marking versus ball A 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

|        |      | millimeters          |      |       | inches <sup>(1)</sup> |       |  |

|--------|------|----------------------|------|-------|-----------------------|-------|--|

| Symbol | Min  | Тур                  | Мах  | Min   | Тур                   | Мах   |  |

| А      | -    | -                    | 0.33 | -     | -                     | 0.013 |  |

| A1     | -    | 0.10                 | -    | -     | 0.004                 | -     |  |

| A2     | -    | 0.20                 | -    | -     | 0.008                 | -     |  |

| A3     | -    | 0.025 <sup>(2)</sup> | -    | -     | 0.001                 | -     |  |

| b      | 0.16 | 0.19                 | 0.22 | 0.006 | 0.007                 | 0.009 |  |

| D      | 2.59 | 2.61                 | 2.63 | 0.102 | 0.103                 | 0.104 |  |

| E      | 2.86 | 2.88                 | 2.90 | 0.112 | 0.113                 | 0.114 |  |

| е      | -    | 0.40                 | -    | -     | 0.016                 | -     |  |

| e1     | -    | 2.00                 | -    | -     | 0.079                 | -     |  |

| e2     | -    | 2.00                 | -    | -     | 0.079                 | -     |  |

| F      | -    | 0.305 <sup>(3)</sup> | -    | -     | 0.012                 | -     |  |

| G      | -    | 0.440 <sup>(3)</sup> | -    | -     | 0.017                 | -     |  |

| aaa    | -    | -                    | 0.10 | -     | -                     | 0.004 |  |

| bbb    | -    | -                    | 0.10 | -     | -                     | 0.004 |  |

| ccc    | -    | -                    | 0.10 | -     | -                     | 0.004 |  |

| ddd    | -    | -                    | 0.05 | -     | -                     | 0.002 |  |

| eee    | -    | -                    | 0.05 | -     | -                     | 0.002 |  |

## Table 80. Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to the 3rd decimal place.

2. Back side coating. Nominal dimension rounded to the 3rd decimal place results from process capability.

3. Calculated dimensions are rounded to 3rd decimal place.

## Figure 50. Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

|        | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| А      | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |

| A3     | -           | 0.152 | -     | -                     | 0.0060 | -      |

| b      | 0.180       | 0.230 | 0.280 | 0.0071                | 0.0091 | 0.0110 |

| D      | 4.900       | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |

| D1     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |

| D2     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |

| E      | 4.900       | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |

| E1     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |

| E2     | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |

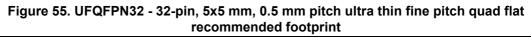

## Table 83. UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

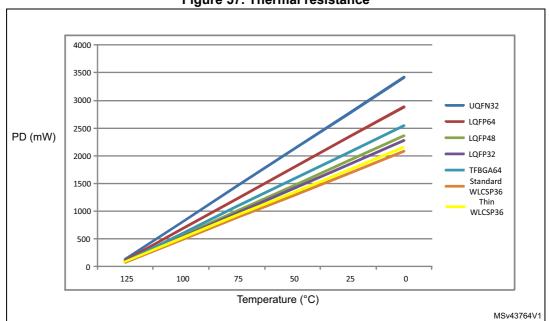

Figure 57. Thermal resistance

### 7.8.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-Sep-2014 | 4        | Extended operating temperature range to 125 °C.<br>Updated minimum ADC operating voltage to 1.65 V.<br>Updated Section 3.4.1: Power supply schemes.<br>Replaced USART3 by LPUART1 and updated I/O structure for PC5<br>and PC15 pins in Table 15: STM32L051x6/8 pin definitions.<br>Replaced LPUART by LPUART1 in Table 16: Alternate function port A,<br>Table 17: Alternate function port B, Table 18: Alternate function port C<br>and Table 19: Alternate function port D.<br>Updated temperature range in Section 2: Description, Table 2: Ultra-<br>low-power STM32L051x6/x8 device features and peripheral counts.<br>Updated temperature range in Section 2: Description, Table 2: Ultra-<br>low-power STM32L051x6/x8 device features and peripheral counts.<br>Updated temperature range in Table 50: Flash memory and data<br>EEPROM endurance and retention, Table 85: STM32L051x6/8<br>ordering information scheme. Update note 1 in Table 27: Current<br>consumption in Run mode, code with data processing running from<br>Flash, Table 29: Current consumption in Run mode, code with data<br>processing running from RAM, Table 31: Current consumption in Sleep<br>mode, Table 32: Current consumptions in Stop mode, Table 34:<br>Typical and maximum current consumptions in Standby mode and<br>Table 33: Low-power mode wakeup timings. Updated Figure 57:<br>Thermal resistance and removed note 1. Updated Table 60: ADC<br>characteristics and Table 62: ADC accuracy.<br>Updated Figure 16: IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Low-<br>power run mode, code running from RAM, Range 3, MSI (Range 0) at<br>64 KHz, 0 WS, Figure 17: IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Stop<br>mode, With RTC enabled and running on LSE Low drive,<br>Figure 18: IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Stop mode with<br>RTC disabled, all clocks OFF.<br>Updated Table 35: Typical and maximum current consumption in Run<br>or Sleep mode.<br>Updated Table 35: Typical and maximum current consumption in Run<br>or Sleep mode.<br>Updated Table 39: Low-power mode wakeup timings.<br>Updated Table 39: Low-power mode wakeup timings.<br>Updated Table 39: Low-power m |

| Table 86. Document revision history (continued) | Table 86. | Document | revision | history | (continued) |

|-------------------------------------------------|-----------|----------|----------|---------|-------------|

|-------------------------------------------------|-----------|----------|----------|---------|-------------|