Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 27                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l051k8u6tr |

|                            |                                                                         |

| Table 46. | MSI oscillator characteristics                                          | 72    |

|-----------|-------------------------------------------------------------------------|-------|

| Table 47. | PLL characteristics                                                     | 74    |

| Table 48. | RAM and hardware registers                                              | 74    |

| Table 49. | Flash memory and data EEPROM characteristics                            | 74    |

| Table 50. | Flash memory and data EEPROM endurance and retention                    | 75    |

| Table 51. | EMS characteristics                                                     | 76    |

| Table 52. | EMI characteristics                                                     | 77    |

| Table 53. | ESD absolute maximum ratings                                            | 78    |

| Table 54. | Electrical sensitivities                                                | 78    |

| Table 55. | I/O current injection susceptibility                                    | 79    |

| Table 56. | I/O static characteristics                                              | 80    |

| Table 57. | Output voltage characteristics                                          | 82    |

| Table 58. | I/O AC characteristics                                                  | 83    |

| Table 59. | NRST pin characteristics                                                | 84    |

| Table 60. | ADC characteristics                                                     | 85    |

| Table 61. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 16 MHz                      |       |

| Table 62. | ADC accuracy                                                            | 87    |

| Table 63. | Temperature sensor calibration values                                   | 90    |

| Table 64. | Temperature sensor characteristics                                      | 90    |

| Table 65. | Comparator 1 characteristics                                            | 91    |

| Table 66. | Comparator 2 characteristics                                            | 91    |

| Table 67. | TIMx characteristics                                                    | 92    |

| Table 68. | I2C analog filter characteristics                                       |       |

| Table 69. | USART/LPUART characteristics                                            | 93    |

| Table 70. | SPI characteristics in voltage Range 1                                  | 94    |

| Table 71. | SPI characteristics in voltage Range 2                                  | 95    |

| Table 72. | SPI characteristics in voltage Range 3                                  |       |

| Table 73. | I2S characteristics                                                     | 99    |

| Table 74. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat                       |       |

|           | package mechanical data                                                 | . 102 |

| Table 75. | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball |       |

|           | grid array package mechanical data                                      |       |

| Table 76. | TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)                 |       |

| Table 77. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical data | . 109 |

| Table 78. | Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale  |       |

|           | mechanical data                                                         |       |

| Table 79. | Standard WLCSP36 recommended PCB design rules                           | . 112 |

| Table 80. | Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale      |       |

|           | package mechanical data                                                 |       |

| Table 81. | WLCSP36 recommended PCB design rules                                    |       |

| Table 82. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical data | . 117 |

| Table 83. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |       |

|           | package mechanical data                                                 |       |

| Table 84. | Thermal characteristics                                                 |       |

| Table 85. | STM32L051x6/8 ordering information scheme                               |       |

| Table 86. | Document revision history                                               | . 125 |

### 1 Introduction

The ultra-low-power STM32L051x6/8 are offered in 7 different package types: from 32 pins to 64 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L051x6/8 microcontrollers suitable for a wide range of applications:

- Gas/water meters and industrial sensors

- Healthcare and fitness equipment

- · Remote control and user interface

- PC peripherals, gaming, GPS equipment

- Alarm system, wired and wireless sensors, video intercom

This STM32L051x6/8 datasheet should be read in conjunction with the STM32L0x1xx reference manual (RM0377).

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core please refer to the Cortex<sup>®</sup>-M0+ Technical Reference Manual, available from the www.arm.com website.

Figure 1 shows the general block diagram of the device family.

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog.

The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

#### RTC clock source

The LSI, LSE or HSE sources can be chosen to clock the RTC, whatever the system clock.

#### Startup clock

After reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

#### • Clock security system (CSS)

This feature can be enabled by software. If an HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled. Another clock security system can be enabled, in case of failure of the LSE it provides an interrupt or wakeup event which is generated if enabled.

# Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

5//

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                              | Memory address            |  |  |

|------------------------|--------------------------------------------------------------------------|---------------------------|--|--|

| TSENSE_CAL1            | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007A - 0x1FF8 007B |  |  |

| TSENSE_CAL2            | TS ADC raw data acquired at temperature of 130 °C V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |  |  |

Table 7. Temperature sensor calibration values

### 3.12.1 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (when no external voltage,  $V_{REF+}$ , is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

Table 8. Internal voltage reference measured values

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

## 3.13 Ultra-low-power comparators and reference voltage

The STM32L051x6/8 embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with ultra low consumption

- One comparator with rail-to-rail inputs, fast or slow mode.

- The threshold can be one of the following:

- External I/O pins

- Internal reference voltage (V<sub>REFINT</sub>)

- submultiple of Internal reference voltage(1/4, 1/2, 3/4) for the rail to rail comparator.

Both comparators can wake up the devices from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1 µA typical).

#### **Communication interfaces** 3.16

#### I<sup>2</sup>C bus 3.16.1

two I<sup>2</sup>C interface (I2C1, I2C2) can operate in multimaster or slave modes.

Each I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask) are also supported as well as programmable analog and digital noise filters.

Table 10. Comparison of I2C analog and digital filters

|                                  | Analog filter                                         | Digital filter                                                                     |

|----------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------|

| Pulse width of suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15 I2C peripheral clocks                             |

| Benefits                         | Available in Stop mode                                | Extra filtering capability vs. standard requirements.     Stable length            |

| Drawbacks                        | Variations depending on temperature, voltage, process | Wakeup from Stop on address match is not available when digital filter is enabled. |

In addition, I2C1 provides hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

Each I2C interface can be served by the DMA controller.

Refer to *Table 11* for an overview of I2C interface features.

Table 11. STM32L051x6/8 I<sup>2</sup>C implementation

| I2C features <sup>(1)</sup>                                  | I2C1 | I2C2             |

|--------------------------------------------------------------|------|------------------|

| 7-bit addressing mode                                        | Х    | Х                |

| 10-bit addressing mode                                       | Х    | Х                |

| Standard mode (up to 100 kbit/s)                             | Х    | Х                |

| Fast mode (up to 400 kbit/s)                                 | Х    | Х                |

| Fast Mode Plus with 20 mA output drive I/Os (up to 1 Mbit/s) | Х    | X <sup>(2)</sup> |

| Independent clock                                            | Х    | -                |

| SMBus                                                        | Х    | -                |

| Wakeup from STOP                                             | Х    | -                |

<sup>1.</sup> X = supported.

DocID025938 Rev 7 30/131

<sup>2.</sup> See for the list of I/Os that feature Fast Mode Plus capability

#### 3.16.2 Universal synchronous/asynchronous receiver transmitter (USART)

The two USART interfaces (USART1, USART2) are able to communicate at speeds of up to 4 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 driver enable (DE) signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. They also support SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability, auto baud rate feature and has a clock domain independent from the CPU clock, allowing to wake up the MCU from Stop mode using baudrates up to 42 Kbaud.

All USART interfaces can be served by the DMA controller.

*Table 12* for the supported modes and features of USART interfaces.

USART modes/features<sup>(1)</sup> **USART1 and USART2** Hardware flow control for modem Χ Χ Continuous communication using DMA Multiprocessor communication Χ Synchronous mode (2) Х Smartcard mode Χ Single-wire half-duplex communication Х IrDA SIR ENDEC block Χ Х I IN mode Dual clock domain and wakeup from Stop mode Χ Χ Receiver timeout interrupt Χ Modbus communication Χ Auto baud rate detection (4 modes) Χ **Driver Enable**

**Table 12. USART implementation**

#### 3.16.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock. It can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

<sup>1.</sup> X = supported.

<sup>2.</sup> This mode allows using the USART as an SPI master.

Table 15. STM32L051x6/8 pin definitions (continued)

|        |         | Pin Nı | umber                  |        |          |                                       |          |               |       |                     |                         |

|--------|---------|--------|------------------------|--------|----------|---------------------------------------|----------|---------------|-------|---------------------|-------------------------|

| LQFP64 | TFBGA64 | LQFP48 | WLCSP36 <sup>(1)</sup> | LQFP32 | UFQFPN32 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions | Additional<br>functions |

| 63     | D4      | 47     | D6                     | 32     | -        | VSS                                   | S        | -             | -     | -                   | -                       |

| 64     | E4      | 48     | A5                     | 1      | 1        | VDD                                   | S        | -             | -     | -                   | -                       |

PB9/12/13/14/15, PH0/1 and PC13 GPIOs should be configured as output and driven Low, even if they are not available on this package.

# 5 Memory mapping

0xFFFF FFFF 0x5000 1FFF IOPORT 0xE010 0000 Cortex-M0+ peripherals 0x5000 0000 0xE000 0000 reserved 6 0xC000 0000 0x4002 63FF 5 AHB 0x4002 0000 0xA000 0000 reserved 0x4001 8000 4 0x1FFF FFFF Option bytes APB2 0x8000 0000 0x4001 0000 System memory 3 0x4000 8000 APB1 0x6000 0000 0x4000 0000 reserved 2 Peripherals 0x4000 0000 Flash system 0x2000 0000 0x0800 0000 reserved CODE 0 Flash, system memory or SRAM, 0x0000 0000 demending on BOOT configuration 0x0000 0000 Reserved MS34761V1

Figure 9. Memory map

| Symbol            | Parameter                           | Conditions                                | Min  | Тур  | Max  | Unit           |  |

|-------------------|-------------------------------------|-------------------------------------------|------|------|------|----------------|--|

| V <sub>PVD6</sub> | PVD threshold 6  Hysteresis voltage | Falling edge                              | 2.97 | 3.05 | 3.09 | V              |  |

|                   |                                     | Rising edge                               | 3.08 | 3.15 | 3.20 | , <sup>v</sup> |  |

|                   |                                     | BOR0 threshold                            | -    | 40   | -    |                |  |

|                   |                                     | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV             |  |

Table 24. Embedded reset and power control block characteristics (continued)

### 6.3.3 Embedded internal reference voltage

The parameters given in *Table 26* are based on characterization results, unless otherwise specified.

Table 25. Embedded internal reference voltage calibration values

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

Table 26. Embedded internal reference voltage<sup>(1)</sup>

| Symbol                                 | Parameter                                                                                 | Conditions                                                       | Min   | Тур   | Max   | Unit   |

|----------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT out</sub> <sup>(2)</sup> | Internal reference voltage                                                                | – 40 °C < T <sub>J</sub> < +125 °C                               | 1.202 | 1.224 | 1.242 | V      |

| T <sub>VREFINT</sub>                   | Internal reference startup time                                                           | -                                                                | -     | 2     | 3     | ms     |

| V <sub>VREF_MEAS</sub>                 | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during V <sub>REFINT</sub> factory measure | -                                                                | 2.99  | 3     | 3.01  | V      |

| A <sub>VREF_MEAS</sub>                 | Accuracy of factory-measured V <sub>REFINT</sub> value <sup>(3)</sup>                     | Including uncertainties due to ADC and $V_{DDA}/V_{REF+}$ values | 1     | 1     | ±5    | mV     |

| T <sub>Coeff</sub> <sup>(4)</sup>      | Temperature coefficient                                                                   | -40 °C < T <sub>J</sub> < +125 °C                                | -     | 25    | 100   | ppm/°C |

| A <sub>Coeff</sub> <sup>(4)</sup>      | Long-term stability                                                                       | 1000 hours, T= 25 °C                                             | -     | -     | 1000  | ppm    |

| V <sub>DDCoeff</sub> <sup>(4)</sup>    | Voltage coefficient                                                                       | 3.0 V < V <sub>DDA</sub> < 3.6 V                                 | -     | -     | 2000  | ppm/V  |

| T <sub>S_vrefint</sub> (4)(5)          | ADC sampling time when reading the internal reference voltage                             | -                                                                | 5     | 10    | -     | μs     |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>    | Startup time of reference voltage buffer for ADC                                          | -                                                                | -     | -     | 10    | μs     |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>    | Consumption of reference voltage buffer for ADC                                           | -                                                                | -     | 13.5  | 25    | μA     |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>   | VREF_OUT output current <sup>(6)</sup>                                                    | -                                                                | -     | -     | 1     | μΑ     |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>   | VREF_OUT output load                                                                      | -                                                                | -     | -     | 50    | pF     |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

### 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 23*.

Table 39. Low-power mode wakeup timings

| Symbol               | Parameter                                                                     | Conditions                                                        | Тур | Max | Unit            |

|----------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----------------|

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode                                                        | f <sub>HCLK</sub> = 32 MHz                                        | 7   | 8   |                 |

| twusleep             | Wakeup from Low-power sleep mode,                                             | f <sub>HCLK</sub> = 262 kHz<br>Flash memory enabled               | 7   | 8   | Number of clock |

|                      | f <sub>HCLK</sub> = 262 kHz                                                   | f <sub>HCLK</sub> = 262 kHz<br>Flash memory switched OFF          | 9   | 10  | cycles          |

| twusleep_lp          |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 5.0 | 8   |                 |

|                      | Wakeup from Stop mode, regulator in Run mode                                  | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |                 |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.0 | 11  |                 |

| <sup>t</sup> wustop  |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 1 | 5.0 | 8   |                 |

|                      | Wakeup from Stop mode, regulator in low-power mode                            | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 2 | 5.0 | 8   |                 |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3 | 5.0 | 8   | μs              |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 7.3 | 13  |                 |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                   | 13  | 23  |                 |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                    | 28  | 38  |                 |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                    | 51  | 65  |                 |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                    | 100 | 120 |                 |

|                      |                                                                               | f <sub>HCLK</sub> = MSI = 65 kHz                                  | 190 | 260 |                 |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |                 |

|                      |                                                                               | $f_{HCLK} = f_{HSI}/4 = 4 \text{ MHz}$                            | 8.0 | 11  |                 |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |                 |

|                      | Wakeup from Stop mode, regulator in low-<br>power mode, code running from RAM | $f_{HCLK} = f_{HSI}/4 = 4 \text{ MHz}$                            | 7.9 | 10  |                 |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 4.7 | 8   |                 |

| t                    | Wakeup from Standby mode, FWU bit = 1                                         | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 65  | 130 | μs              |

| <sup>t</sup> wustdby | Wakeup from Standby mode, FWU bit = 0                                         | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 2.2 | 3   | ms              |

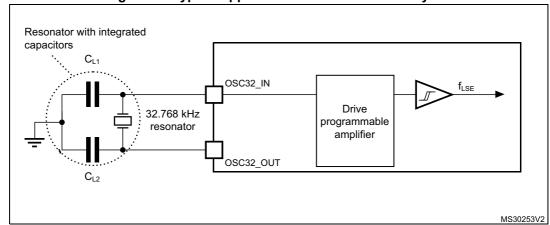

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 43*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                 | Conditions <sup>(2)</sup>                       | Min <sup>(2)</sup> | Тур    | Max  | Unit |

|-------------------------------------|-------------------------------------------|-------------------------------------------------|--------------------|--------|------|------|

| f <sub>LSE</sub>                    | LSE oscillator frequency                  |                                                 | -                  | 32.768 | -    | kHz  |

|                                     |                                           | LSEDRV[1:0]=00 lower driving capability         | -                  | -      | 0.5  |      |

| G                                   | Maximum critical crystal transconductance | LSEDRV[1:0]= 01 medium low driving capability   | -                  | -      | 0.75 | uA/V |

| G <sub>m</sub>                      |                                           | LSEDRV[1:0] = 10 medium high driving capability | -                  | -      | 1.7  | μΑνν |

|                                     |                                           | LSEDRV[1:0]=11 higher driving capability        | -                  | -      | 2.7  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                              | V <sub>DD</sub> is stabilized                   | -                  | 2      | ı    | s    |

Table 43. LSE oscillator characteristics<sup>(1)</sup>

Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 22. Typical application with a 32.768 kHz crystal

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

<sup>1.</sup> Guaranteed by design.

Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

Guaranteed by characterization results. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. To increase speed, address a lower-drive quartz with a high- driver mode.

Table 46. MSI oscillator characteristics (continued)

| Symbol                                | Parameter                          | Condition                                | Тур  | Max | Unit    |  |

|---------------------------------------|------------------------------------|------------------------------------------|------|-----|---------|--|

|                                       |                                    | MSI range 0                              | 0.75 | -   |         |  |

|                                       |                                    | MSI range 1                              | 1    | -   |         |  |

|                                       |                                    | MSI range 2                              | 1.5  | -   | μΑ      |  |

| I <sub>DD(MSI)</sub> <sup>(2)</sup>   | MSI oscillator power consumption   | MSI range 3                              | 2.5  | -   |         |  |

|                                       |                                    | MSI range 4                              | 4.5  | -   |         |  |

|                                       |                                    | MSI range 5                              | 8    | -   |         |  |

|                                       |                                    | MSI range 6                              | 15   | -   |         |  |

|                                       |                                    | MSI range 0                              | 30   | -   |         |  |

|                                       |                                    | MSI range 1                              | 20   | -   |         |  |

|                                       |                                    | MSI range 2                              | 15   | -   |         |  |

|                                       |                                    | MSI range 3                              | 10   | -   |         |  |

| 4                                     | MCI agaillatar startus tima        | MSI range 4                              | 6    | -   | μs      |  |

| t <sub>SU(MSI)</sub>                  | MSI oscillator startup time        | MSI range 5                              | 5    | -   |         |  |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | 3.5  | -   |         |  |

|                                       |                                    | MSI range 6,<br>Voltage range 3          | 5    | -   |         |  |

|                                       |                                    | MSI range 0                              | -    | 40  |         |  |

|                                       |                                    | MSI range 1                              | -    | 20  |         |  |

|                                       |                                    | MSI range 2                              | -    | 10  |         |  |

|                                       |                                    | MSI range 3                              | -    | 4   |         |  |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> | MSI oscillator stabilization time  | MSI range 4                              | -    | 2.5 | μs      |  |

| STAB(MSI)                             | Wor oscillator stabilization time  | MSI range 5                              | -    | 2   | μο      |  |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | -    | 2   |         |  |

|                                       |                                    | MSI range 3,<br>Voltage range 3          | -    | 3   |         |  |

| fo                                    | MSI oscillator frequency overshoot | Any range to range 5                     | -    | 4   | MHz     |  |

| f <sub>OVER(MSI)</sub>                | Mor oscillator frequency overshoot | Any range to range 6                     | -    | 6   | IVII IZ |  |

<sup>1.</sup> This is a deviation for an individual part, once the initial frequency has been measured.

<sup>2.</sup> Guaranteed by characterization results.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

**Table 52. EMI characteristics**

|                           |            |                                                                                              | Monitored       | Max vs. f <sub>osc</sub> /f <sub>CPU</sub> |                  |                  |      |

|---------------------------|------------|----------------------------------------------------------------------------------------------|-----------------|--------------------------------------------|------------------|------------------|------|

| Symbol                    | Parameter  | r Conditions                                                                                 | frequency band  | 8 MHz/<br>4 MHz                            | 8 MHz/<br>16 MHz | 8 MHz/<br>32 MHz | Unit |

|                           | Dook lovel | Peak level $V_{DD} = 3.6 \text{ V},$ $T_A = 25 ^{\circ}\text{C},$ compliant with IEC 61967-2 | 0.1 to 30 MHz   | -21                                        | -15              | -12              |      |

| 9                         |            |                                                                                              | 30 to 130 MHz   | -14                                        | -12              | -1               | dΒμV |

| S <sub>EMI</sub> Peak lev | reak level |                                                                                              | 130 MHz to 1GHz | -10                                        | -11              | -7               |      |

|                           |            |                                                                                              | EMI Level       | 1                                          | 1                | 1                | -    |

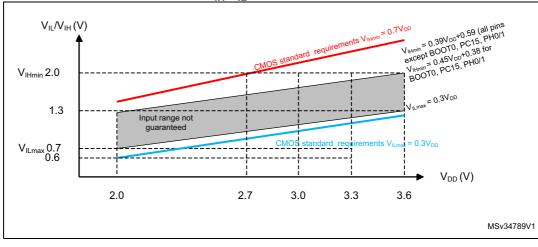

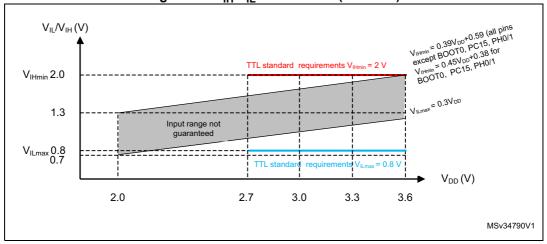

Figure 24. V<sub>IH</sub>/V<sub>IL</sub> versus VDD (CMOS I/Os)

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 15$  mA with the non-standard  $V_{OL}/V_{OH}$  specifications given in *Table 57*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on  $V_{DD}$ , plus the maximum Run consumption of the MCU sourced on  $V_{DD}$ , cannot exceed the absolute maximum rating  $I_{VDD(\Sigma)}$  (see *Table 21*).

- The sum of the currents sunk by all the I/Os on  $V_{SS}$  plus the maximum Run consumption of the MCU sunk on  $V_{SS}$  cannot exceed the absolute maximum rating  $I_{VSS(\Sigma)}$  (see *Table 21*).

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 26* and *Table 58*, respectively.

Unless otherwise specified, the parameters given in *Table 58* are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 23*.

Table 58. I/O AC characteristics<sup>(1)</sup>

| OSPEEDRx[1:0]                |                                                  | Table 58. I/O AC 6                                              |                                                                  |     | (2)                |         |  |

|------------------------------|--------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|-----|--------------------|---------|--|

| bit value <sup>(1)</sup>     | Symbol                                           | Parameter                                                       | Conditions                                                       | Min | Max <sup>(2)</sup> | Unit    |  |

|                              | £                                                | Maximum frequency <sup>(3)</sup>                                | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 400                | kHz     |  |

| 00                           | f <sub>max(IO)out</sub>                          | Maximum frequency                                               | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -   | 100                |         |  |

| 00                           | t <sub>f(IO)out</sub>                            | Output rise and fall time                                       | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 125                | ne      |  |

|                              | t <sub>r(IO)out</sub>                            | Output rise and fail time                                       | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -   | 320                | ns      |  |

|                              | f us                                             | Maximum frequency <sup>(3)</sup>                                | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 2                  | MHz     |  |

| 01                           | f <sub>max(IO)out</sub>                          | Maximum frequency                                               | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -   | 0.6                | IVII IZ |  |

| 01                           | t <sub>f(IO)out</sub>                            | Output rise and fall time                                       | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 30                 | - ns    |  |

|                              | t <sub>r(IO)out</sub>                            | Output fise and fail time                                       | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -   | 65                 |         |  |

|                              | F <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 10                 | MHz     |  |

| 10                           |                                                  | waximum frequency.                                              | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -   | 2                  |         |  |

| 10                           | t <sub>f(IO)</sub> out<br>t <sub>r(IO)</sub> out | Output rise and fall time                                       | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 13                 | - ns    |  |

|                              |                                                  |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -   | 28                 |         |  |

|                              | F <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                | $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 35                 | MHz     |  |

| 11                           |                                                  |                                                                 | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -   | 10                 |         |  |

|                              | t <sub>f(IO)out</sub>                            | Output rise and fall time                                       | $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -   | 6                  | ns      |  |

|                              | t <sub>r(IO)out</sub>                            | Output rise and fail time                                       | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -   | 17                 | 113     |  |

|                              | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                |                                                                  | -   | 1                  | MHz     |  |

|                              | t <sub>f(IO)out</sub>                            | Output fall time                                                | $C_L = 50 \text{ pF}, V_{DD} = 2.5 \text{ V to } 3.6 \text{ V}$  | _   | 10                 | ns      |  |

| Fm+                          | t <sub>r(IO)out</sub>                            | Output rise time                                                |                                                                  | -   | 30                 | 115     |  |

| configuration <sup>(4)</sup> | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                |                                                                  | -   | 350                | KHz     |  |

|                              | t <sub>f(IO)out</sub>                            | Output fall time                                                | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 3.6 \text{ V}$ |     | 15                 | ns      |  |

|                              | t <sub>r(IO)out</sub>                            | Output rise time                                                |                                                                  | -   | 60                 | 115     |  |

| -                            | t <sub>EXTIpw</sub>                              | Pulse width of external signals detected by the EXTI controller | -                                                                | 8   | -                  | ns      |  |

<sup>1.</sup> The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the line reference manual for a description of GPIO Port configuration register.

<sup>4.</sup> When Fm+ configuration is set, the I/O speed control is bypassed. Refer to the line reference manual for a detailed description of Fm+ I/O configuration.

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> The maximum frequency is defined in Figure 26.

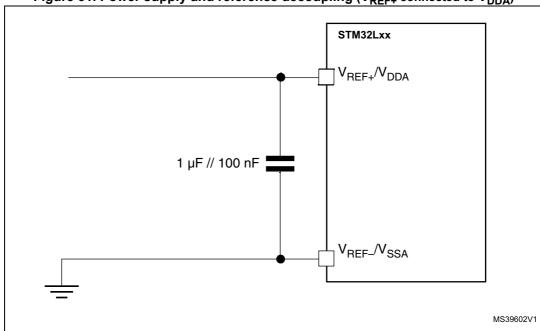

Figure 31. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

### 6.3.16 Temperature sensor characteristics

Table 63. Temperature sensor calibration values

| Calibration value name | Description                                                               | Memory address            |  |

|------------------------|---------------------------------------------------------------------------|---------------------------|--|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V  | 0x1FF8 007A - 0x1FF8 007B |  |

| TS_CAL2                | TS ADC raw data acquired at temperature of 130 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |  |

**Table 64. Temperature sensor characteristics**

| Symbol                                | Parameter                                         | Min  | Тур  | Max       | Unit  |

|---------------------------------------|---------------------------------------------------|------|------|-----------|-------|

| $T_{L}^{(1)}$                         | V <sub>SENSE</sub> linearity with temperature     |      | ±1   | <u>+2</u> | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                     | 1.48 | 1.61 | 1.75      | mV/°C |

| V <sub>130</sub>                      | Voltage at 130°C ±5°C <sup>(2)</sup>              | 640  | 670  | 700       | mV    |

| I <sub>DDA(TEMP)</sub> (3)            | Current consumption                               |      | 3.4  | 6         | μA    |

| t <sub>START</sub> (3)                | Startup time                                      |      | -    | 10        | 116   |

| T <sub>S_temp</sub> <sup>(4)(3)</sup> | ADC sampling time when reading the temperature 10 |      | -    | μs        |       |

- 1. Guaranteed by characterization results.

- 2. Measured at  $V_{DD}$  = 3 V ±10 mV. V130 ADC conversion result is stored in the TS\_CAL2 byte.

- 3. Guaranteed by design.

- 4. Shortest sampling time can be determined in the application by multiple iterations.

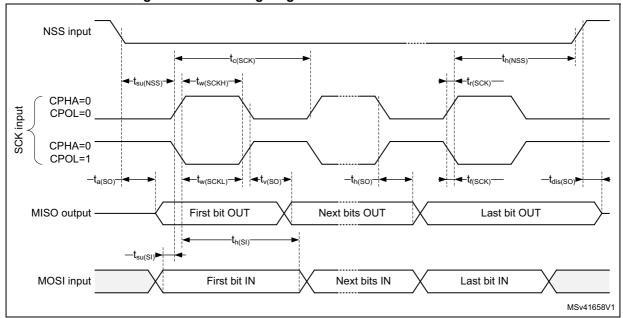

Figure 32. SPI timing diagram - slave mode and CPHA = 0

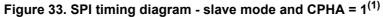

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

Table 78. Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale mechanical data (continued)

| Symbol | millimeters |                      |       | inches <sup>(1)</sup> |       |       |

|--------|-------------|----------------------|-------|-----------------------|-------|-------|

|        | Min         | Тур                  | Max   | Min                   | Тур   | Max   |

| F      | -           | 0.305 <sup>(3)</sup> | -     | -                     | 0.012 | -     |

| G      | -           | 0.440 <sup>(3)</sup> | -     | -                     | 0.017 | -     |

| aaa    | -           | -                    | 0.100 | -                     | -     | 0.004 |

| bbb    | -           | -                    | 0.100 | -                     | -     | 0.004 |

| ccc    | -           | -                    | 0.100 | -                     | -     | 0.004 |

| ddd    | -           | -                    | 0.050 | -                     | -     | 0.002 |

| eee    | -           | -                    | 0.050 | -                     | -     | 0.002 |

- 1. Values in inches are converted from mm and rounded to the 3rd decimal place.

- 2. Nominal dimension rounded to the 3rd decimal place results from process capability.

- 3. Calculated dimensions are rounded to the 3rd decimal place.

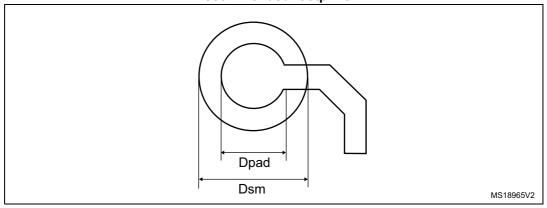

Figure 47. Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale recommended footprint

Table 79. Standard WLCSP36 recommended PCB design rules

| Dimension      | Recommended values                            |

|----------------|-----------------------------------------------|

| Pitch          | 0.4 mm                                        |

| Dpad           | 260 µm max. (circular)<br>220 µm recommended  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)         |

| PCB pad design | Non-solder mask defined via underbump allowed |

Table 80. Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale package mechanical data

| package mechanical data |             |                      |      |                       |       |       |

|-------------------------|-------------|----------------------|------|-----------------------|-------|-------|

| Symbol                  | millimeters |                      |      | inches <sup>(1)</sup> |       |       |

| Symbol                  | Min         | Тур                  | Max  | Min                   | Тур   | Max   |

| Α                       | -           | -                    | 0.33 | -                     | -     | 0.013 |

| A1                      | -           | 0.10                 | -    | -                     | 0.004 | -     |

| A2                      | -           | 0.20                 | -    | -                     | 0.008 | -     |

| А3                      | -           | 0.025 <sup>(2)</sup> | -    | -                     | 0.001 | -     |

| b                       | 0.16        | 0.19                 | 0.22 | 0.006                 | 0.007 | 0.009 |

| D                       | 2.59        | 2.61                 | 2.63 | 0.102                 | 0.103 | 0.104 |

| E                       | 2.86        | 2.88                 | 2.90 | 0.112                 | 0.113 | 0.114 |

| е                       | -           | 0.40                 | -    | -                     | 0.016 | -     |

| e1                      | -           | 2.00                 | -    | -                     | 0.079 | -     |

| e2                      | -           | 2.00                 | -    | -                     | 0.079 | -     |

| F                       | -           | 0.305 <sup>(3)</sup> | -    | -                     | 0.012 | -     |

| G                       | -           | 0.440 <sup>(3)</sup> | -    | -                     | 0.017 | -     |

| aaa                     | -           | -                    | 0.10 | -                     | -     | 0.004 |

| bbb                     | -           | -                    | 0.10 | -                     | -     | 0.004 |

| ccc                     | -           | -                    | 0.10 | -                     | -     | 0.004 |

| ddd                     | -           | -                    | 0.05 | -                     | -     | 0.002 |

| eee                     | -           | -                    | 0.05 | -                     | -     | 0.002 |

- 1. Values in inches are converted from mm and rounded to the 3rd decimal place.

- 2. Back side coating. Nominal dimension rounded to the 3rd decimal place results from process capability.

- 3. Calculated dimensions are rounded to 3rd decimal place.

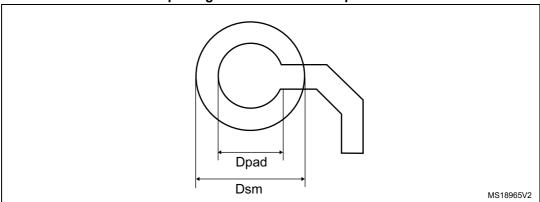

Figure 50. Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

130/131

Table 86. Document revision history (continued)

| Date                    | Revision      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Date</b> 07-Mar-2017 | Revision<br>7 | Changes  Added thin WLCSP36 package  Updated number of I2S interfaces in Table 2: Ultra-low-power STM32L051x6/x8 device features and peripheral counts.  Removed note 2 related to PA4 in Table 15: STM32L051x6/8 pin definitions  Added mission profile compliance with JEDEC JESD47 in Section 6.2: Absolute maximum ratings.  Removed CRS from Table 37: Peripheral current consumption in Run or Sleep mode.  Added note 2. related to the position of the external capacitor below Figure 27: Recommended NRST pin protection.  Updated R <sub>L</sub> in Table 60: ADC characteristics.  Updated t <sub>AF</sub> maximum value for range 1 in Table 68: I2C analog filter characteristics.  Updated t <sub>WUUSART</sub> description in Table 69: USART/LPUART characteristics. |

|                         |               | . , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                         |               | Added reference to optional marking or inset/upset marks in all package device marking sections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                         |               | Previous WLCSP36 package renamed "Standard" WLCSP36; added Note 2. below Figure 46: Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale package outline and updated Table 78: Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale mechanical data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |