Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 27                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l051k8u7tr |

| Interconnect source | Interconnect destination | Interconnect action                                                | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | Stop |

|---------------------|--------------------------|--------------------------------------------------------------------|-----|-------|----------------------|------------------------|------|

| RTC                 | TIM21                    | Timer triggered by Auto wake-up                                    | Y   | Υ     | Y                    | Y                      | -    |

| RIC                 | LPTIM                    | Timer triggered by RTC event                                       | Y   | Y     | Y                    | Y                      | Υ    |

| All clock<br>source | TIMx                     | Clock source used as input channel for RC measurement and trimming | Υ   | Y     | Y                    | Y                      | -    |

|                     | TIMx                     | Timer input channel and trigger                                    | Y   | Υ     | Y                    | Υ                      | -    |

| GPIO                | LPTIM                    | Timer input channel and trigger                                    | Y   | Y     | Y                    | Y                      | Y    |

|                     | ADC                      | Conversion trigger                                                 | Υ   | Υ     | Y                    | Y                      | -    |

Table 6. STM32L0xx peripherals interconnect matrix (continued)

# 3.3 ARM® Cortex®-M0+ core with MPU

The Cortex-M0+ processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- a simple architecture that is easy to learn and program

- ultra-low power, energy-efficient operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with Cortex-M processor family

- platform security robustness, with integrated Memory Protection Unit (MPU).

The Cortex-M0+ processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0+ processor provides the exceptional performance expected of a modern 32-bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

Owing to its embedded ARM core, the STM32L051x6/8 are compatible with all ARM tools and software.

internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note:

The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the start-up time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The devices feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD/VDDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD/VDDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD/VDDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

### 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC\_CSR).

# 3.5 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

### Clock prescaler

To get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

#### Safe clock switching

Clock sources can be changed safely on the fly in Run mode through a configuration register.

#### Clock management

To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

#### System clock source

Three different clock sources can be used to drive the master clock SYSCLK:

- 1-25 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLLMultispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

# Auxiliary clock source

Two ultra-low-power clock sources that can be used to drive the real-time clock:

### 3.8 Memories

The STM32L051x6/8 devices have the following features:

- 8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 32 or 64 Kbytes of embedded Flash program memory

- 2 Kbytes of data EEPROM

- Information block containing 32 user and factory options bytes plus 4 Kbytes of system memory

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

- The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- **Level 2**: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The firewall protects parts of code/data from access by the rest of the code that is executed outside of the protected area. The granularity of the protected code segment or the non-volatile data segment is 256 bytes (Flash memory or EEPROM) against 64 bytes for the volatile data segment (RAM).

The whole non-volatile memory embeds the error correction code (ECC) feature.

# 3.9 Boot modes

At startup, BOOT0 pin and nBOOT1 option bit are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- · Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using SPI1(PA4, PA5, PA6, PA7) or SPI2 (PB12, PB13, PB14, PB15), USART1(PA9, PA10) or USART2(PA2, PA3). See STM32™ microcontroller system memory boot mode AN2606 for details.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                              | Memory address            |  |  |

|------------------------|--------------------------------------------------------------------------|---------------------------|--|--|

| TSENSE_CAL1            | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007A - 0x1FF8 007B |  |  |

| TSENSE_CAL2            | TS ADC raw data acquired at temperature of 130 °C V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |  |  |

Table 7. Temperature sensor calibration values

# 3.12.1 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (when no external voltage,  $V_{REF+}$ , is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

Table 8. Internal voltage reference measured values

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

# 3.13 Ultra-low-power comparators and reference voltage

The STM32L051x6/8 embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with ultra low consumption

- One comparator with rail-to-rail inputs, fast or slow mode.

- The threshold can be one of the following:

- External I/O pins

- Internal reference voltage (V<sub>REFINT</sub>)

- submultiple of Internal reference voltage(1/4, 1/2, 3/4) for the rail to rail comparator.

Both comparators can wake up the devices from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1 µA typical).

# 3.14 System configuration controller

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM21, TIM22 and LPTIM timer input captures. It also controls the routing of internal analog signals to ADC, COMP1 and COMP2 and the internal reference voltage V<sub>REFINT</sub>.

# 3.15 Timers and watchdogs

The ultra-low-power STM32L051x6/8 devices include three general-purpose timers, one low-power timer (LPTIM), one basic timer, two watchdog timers and the SysTick timer.

Table 9 compares the features of the general-purpose and basic timers.

| Timer           | Counter resolution | Counter type         | Prescaler factor                | DMA<br>request<br>generation | Capture/compare channels | Complementary outputs |

|-----------------|--------------------|----------------------|---------------------------------|------------------------------|--------------------------|-----------------------|

| TIM2            | 16-bit             | Up, down,<br>up/down | Any integer between 1 and 65536 | Yes                          | 4                        | No                    |

| TIM21,<br>TIM22 | 16-bit             | Up, down,<br>up/down | Any integer between 1 and 65536 | No                           | 2                        | No                    |

| TIM6            | 16-bit             | Up                   | Any integer between 1 and 65536 | Yes                          | 0                        | No                    |

Table 9. Timer feature comparison

# 3.15.1 General-purpose timers (TIM2, TIM21 and TIM22)

There are three synchronizable general-purpose timers embedded in the STM32L051x6/8 devices (see *Table 9* for differences).

#### TIM<sub>2</sub>

TIM2 is based on 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It features four independent channels each for input capture/output compare, PWM or one-pulse mode output.

The TIM2 general-purpose timers can work together or with the TIM21 and TIM22 general-purpose timers via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2 has independent DMA request generation.

This timer is capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### TIM21 and TIM22

TIM21 and TIM22 are based on a 16-bit auto-reload up/down counter. They include a 16-bit prescaler. They have two independent channels for input capture/output compare, PWM or

Table 15. STM32L051x6/8 pin definitions (continued)

|        |         | Pin Nu | umber                  |        |          |                                       | -        |               |       | ,                                                     |                                                |

|--------|---------|--------|------------------------|--------|----------|---------------------------------------|----------|---------------|-------|-------------------------------------------------------|------------------------------------------------|

| LQFP64 | TFBGA64 | LQFP48 | WLCSP36 <sup>(1)</sup> | LQFP32 | UFQFPN32 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                   | Additional<br>functions                        |

| 5      | C1      | 5      | -                      | -      | -        | PH0-OSC_IN<br>(PH0)                   | I/O      | TC            | -     | -                                                     | OSC_IN                                         |

| 6      | D1      | 6      | -                      | -      | -        | PH1-<br>OSC_OUT<br>(PH1)              | I/O      | тс            | 1     | -                                                     | OSC_OUT                                        |

| 7      | E1      | 7      | C6                     | 4      | 4        | NRST                                  | I/O      | RST           | -     | -                                                     | -                                              |

| 8      | E3      | -      | -                      | -      | -        | PC0                                   | I/O      | FT            | -     | LPTIM1_IN1,<br>EVENTOUT                               | ADC_IN10                                       |

| 9      | E2      | -      | -                      | -      | -        | PC1                                   | I/O      | FT            | -     | LPTIM1_OUT,<br>EVENTOUT                               | ADC_IN11                                       |

| 10     | F2      | -      | -                      | -      | -        | PC2                                   | I/O      | FT            | -     | LPTIM1_IN2,<br>SPI2_MISO/I2S2_M<br>CK                 | ADC_IN12                                       |

| 11     | -       | -      | -                      | ı      | -        | PC3                                   | I/O      | FT            | 1     | LPTIM1_ETR,<br>SPI2_MOSI/I2S2_SD                      | ADC_IN13                                       |

| 12     | F1      | 8      | -                      | -      | -        | VSSA                                  | S        |               | -     | -                                                     | -                                              |

| -      | G1      | -      | E6                     | ı      | ı        | VREF+                                 | S        |               | 1     | -                                                     | -                                              |

| 13     | H1      | 9      | D5                     | 5      | 5        | VDDA                                  | S        |               | ı     | -                                                     | -                                              |

| 14     | G2      | 10     | D4                     | 6      | 6        | PA0                                   | I/O      | TC            | 1     | TIM2_CH1,<br>USART2_CTS,<br>TIM2_ETR,<br>COMP1_OUT    | COMP1_INM6,<br>ADC_IN0,<br>RTC_TAMP2/WKU<br>P1 |

| 15     | H2      | 11     | F6                     | 7      | 7        | PA1                                   | I/O      | FT            | 1     | EVENTOUT,<br>TIM2_CH2,<br>USART2_RTS_DE,<br>TIM21_ETR | COMP1_INP,<br>ADC_IN1                          |

| 16     | F3      | 12     | E5                     | 8      | 8        | PA2                                   | I/O      | FT            | -     | TIM21_CH1,<br>TIM2_CH3,<br>USART2_TX,<br>COMP2_OUT    | COMP2_INM6,<br>ADC_IN2                         |

| 17     | G3      | 13     | F5                     | 9      | 9        | PA3                                   | I/O      | FT            | -     | TIM21_CH2,<br>TIM2_CH4,<br>USART2_RX                  | COMP2_INP,<br>ADC_IN3                          |

| 18     | C2      | -      | -                      | -      | -        | VSS                                   | S        |               | -     | -                                                     | -                                              |

Table 15. STM32L051x6/8 pin definitions (continued)

|        |         | Pin N  | ımber                  |        |          |                                       |          |               |       |                                                                    |                                       |

|--------|---------|--------|------------------------|--------|----------|---------------------------------------|----------|---------------|-------|--------------------------------------------------------------------|---------------------------------------|

| LQFP64 | TFBGA64 | LQFP48 | WLCSP36 <sup>(1)</sup> | LQFP32 | UFQFPN32 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                | Additional<br>functions               |

| 19     | D2      | -      | -                      | -      | -        | VDD                                   | S        |               | -     | -                                                                  | -                                     |

| 20     | НЗ      | 14     | E4                     | 10     | 10       | PA4                                   | I/O      | TC            |       | SPI1_NSS,<br>USART2_CK,<br>TIM22_ETR                               | COMP1_INM4,<br>COMP2_INM4,<br>ADC_IN4 |

| 21     | F4      | 15     | F4                     | 11     | 11       | PA5                                   | I/O      | TC            | ı     | SPI1_SCK,<br>TIM2_ETR,<br>TIM2_CH1                                 | COMP1_INM5,<br>COMP2_INM5,<br>ADC_IN5 |

| 22     | G4      | 16     | E3                     | 12     | 12       | PA6                                   | I/O      | FT            | -     | SPI1_MISO,<br>LPUART1_CTS,<br>TIM22_CH1,<br>EVENTOUT,<br>COMP1_OUT | ADC_IN6                               |

| 23     | H4      | 17     | F3                     | 13     | 13       | PA7                                   | I/O      | FT            | 1     | SPI1_MOSI,<br>TIM22_CH2,<br>EVENTOUT,<br>COMP2_OUT                 | ADC_IN7                               |

| 24     | H5      | ı      | 1                      | -      | -        | PC4                                   | I/O      | FT            | ı     | EVENTOUT,<br>LPUART1_TX                                            | ADC_IN14                              |

| 25     | H6      | ı      | ı                      | -      | -        | PC5                                   | I/O      | FT            | -     | LPUART1_RX,                                                        | ADC_IN15                              |

| 26     | F5      | 18     | D3                     | 14     | 14       | PB0                                   | I/O      | FT            | i     | EVENTOUT                                                           | ADC_IN8,<br>VREF_OUT                  |

| 27     | G5      | 19     | C3                     | 15     | 15       | PB1                                   | I/O      | FT            | i     | LPUART1_RTS_DE                                                     | ADC_IN9,<br>VREF_OUT                  |

| 28     | G6      | 20     | F2                     | -      | 16       | PB2                                   | I/O      | FT            | -     | LPTIM1_OUT                                                         | -                                     |

| 29     | G7      | 21     | E2                     | -      | -        | PB10                                  | I/O      | FT            | -     | TIM2_CH3,<br>LPUART1_TX,<br>SPI2_SCK,<br>I2C2_SCL                  | -                                     |

| 30     | H7      | 22     | D2                     | -      | -        | PB11                                  | I/O      | FT            | -     | EVENTOUT,<br>TIM2_CH4,<br>LPUART1_RX,<br>I2C2_SDA                  | -                                     |

| 31     | D6      | 23     | 1                      | 16     | -        | VSS                                   | S        | -             | -     | -                                                                  | -                                     |

| 32     | E6      | 24     | F1                     | 17     | 17       | VDD                                   | S        | -             | -     | -                                                                  | -                                     |

Table 15. STM32L051x6/8 pin definitions (continued)

|        |         | Pin Nu | umber                  |        | - 101 0  |                                       | , p      |               |       | is (continued)                                                |                         |  |

|--------|---------|--------|------------------------|--------|----------|---------------------------------------|----------|---------------|-------|---------------------------------------------------------------|-------------------------|--|

| LQFP64 | TFBGA64 | LQFP48 | WLCSP36 <sup>(1)</sup> | LQFP32 | UFQFPN32 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                           | Additional<br>functions |  |

| 48     | E5      | 36     | -                      | -      | -        | VDDIO2                                | S        |               | 1     | -                                                             | -                       |  |

| 49     | A7      | 37     | B2                     | 24     | 24       | PA14                                  | I/O      | FT            | -     | SWCLK,<br>USART2_TX                                           |                         |  |

| 50     | A6      | 38     | A2                     | 25     | 25       | PA15                                  | I/O      | FT            | 1     | SPI1_NSS,<br>TIM2_ETR,<br>EVENTOUT,<br>USART2_RX,<br>TIM2_CH1 | ,                       |  |

| 51     | В7      | -      | -                      | -      | -        | PC10                                  | I/O      | FT            | ı     | LPUART1_TX                                                    | -                       |  |

| 52     | В6      | -      | -                      | -      | -        | PC11                                  | I/O      | FT            | ı     | LPUART1_RX                                                    | -                       |  |

| 53     | C5      | -      | -                      | -      | -        | PC12                                  | I/O      | FT            | -     | -                                                             | -                       |  |

| 54     | B5      | -      | -                      | -      | -        | PD2                                   | I/O      | FT            | -     | LPUART1_RTS_DE                                                | -                       |  |

| 55     | A5      | 39     | В3                     | 26     | 26       | PB3                                   | I/O      | FT            | 1     | SPI1_SCK,<br>TIM2_CH2,<br>EVENTOUT                            | COMP2_INN               |  |

| 56     | A4      | 40     | A3                     | 27     | 27       | PB4                                   | I/O      | FT            | 1     | SPI1_MISO,<br>EVENTOUT,<br>TIM22_CH1                          | COMP2_INP               |  |

| 57     | C4      | 41     | C4                     | 28     | 28       | PB5                                   | I/O      | FT            | -     | SPI1_MOSI,<br>LPTIM1_IN1,<br>I2C1_SMBA,<br>TIM22_CH2          | COMP2_INP               |  |

| 58     | D3      | 42     | B4                     | 29     | 29       | PB6                                   | I/O      | FTf           | i     | USART1_TX,<br>I2C1_SCL,<br>LPTIM1_ETR                         | COMP2_INP               |  |

| 59     | C3      | 43     | A4                     | 30     | 30       | PB7                                   | I/O      | FTf           | i     | USART1_RX,<br>I2C1_SDA,<br>LPTIM1_IN2                         | COMP2_INP,<br>PVD_IN    |  |

| 60     | B4      | 44     | C5                     | 31     | 31       | воото                                 | В        |               | -     | -                                                             | -                       |  |

| 61     | ВЗ      | 45     | B5                     | -      | 32       | PB8                                   | I/O      | FTf           | -     | I2C1_SCL                                                      | -                       |  |

| 62     | А3      | 46     | -                      | -      | -        | PB9                                   | I/O      | FTf           | -     | EVENTOUT,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS                    | -                       |  |

|        | Table 16. Alternate function port A |                                 |     |                    |          |                   |            |          |           |  |

|--------|-------------------------------------|---------------------------------|-----|--------------------|----------|-------------------|------------|----------|-----------|--|

|        |                                     | AF0                             | AF1 | AF2                | AF3      | AF4               | AF5        | AF6      | AF7       |  |

| Po     | ort                                 | SPI1/TIM21/SYS_A<br>F/EVENTOUT/ | -   | TIM2/<br>EVENTOUT/ | EVENTOUT | USART1/2/3        | TIM2/21/22 | EVENTOUT | COMP1/2   |  |

|        | PA0                                 | -                               | -   | TIM2_CH1           | -        | USART2_CTS        | TIM2_ETR   | -        | COMP1_OUT |  |

|        | PA1                                 | EVENTOUT                        | -   | TIM2_CH2           | -        | USART2_RTS_<br>DE | TIM21_ETR  | -        | -         |  |

|        | PA2                                 | TIM21_CH1                       | -   | TIM2_CH3           | -        | USART2_TX         | -          | -        | COMP2_OUT |  |

|        | PA3                                 | TIM21_CH2                       | -   | TIM2_CH4           | -        | USART2_RX         | -          | -        | -         |  |

|        | PA4                                 | SPI1_NSS                        | -   | -                  | -        | USART2_CK         | TIM22_ETR  | -        | -         |  |

|        | PA5                                 | SPI1_SCK                        | -   | TIM2_ETR           | -        | -                 | TIM2_CH1   | -        | -         |  |

|        | PA6                                 | SPI1_MISO                       | -   | -                  | -        | LPUART1_CTS       | TIM22_CH1  | EVENTOUT | COMP1_OUT |  |

| Port A | PA7                                 | SPI1_MOSI                       | -   | -                  | -        | -                 | TIM22_CH2  | EVENTOUT | COMP2_OUT |  |

| POILA  | PA8                                 | МСО                             | -   | -                  | EVENTOUT | USART1_CK         | -          | -        | -         |  |

|        | PA9                                 | MCO                             | -   | -                  | -        | USART1_TX         | -          | -        | -         |  |

|        | PA10                                | -                               | -   | -                  | -        | USART1_RX         | -          | -        | -         |  |

|        | PA11                                | SPI1_MISO                       | -   | EVENTOUT           | -        | USART1_CTS        | -          | -        | COMP1_OUT |  |

|        | PA12                                | SPI1_MOSI                       | -   | EVENTOUT           | -        | USART1_RTS_<br>DE | -          | -        | COMP2_OUT |  |

|        | PA13                                | SWDIO                           | -   | -                  | -        | -                 | -          | -        | -         |  |

|        | PA14                                | SWCLK                           | -   | -                  | -        | USART2_TX         | -          | -        | -         |  |

|        | PA15                                | SPI1_NSS                        | -   | TIM2_ETR           | EVENTOUT | USART2_RX         | TIM2_CH1   | -        | -         |  |

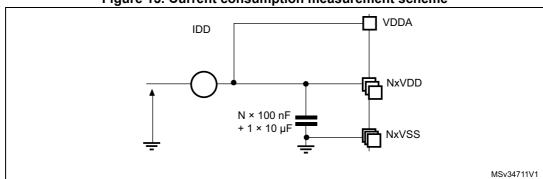

# 6.1.6 Power supply scheme

Standby-power circuitry (OSC32,RTC,Wake-up logic, RTC backup registers) Ю GP I/Os Logic Kernel logic (CPU, Digital & Memories) Regulator N × 100 nF  $+ 1 \times 10 \mu F$  $V_{\text{DDA}}$  $V_{\text{DDA}}$  $V_{REF+}$ 100 nF Analog: RC,PLL,COMP, + 1 µF ADC  $V_{\mathsf{REF}}$  $V_{SSA}$ MSv34740V1

Figure 12. Power supply scheme

# 6.1.7 Current consumption measurement

Figure 13. Current consumption measurement scheme

### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- $\bullet$   $\,$  all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked OFF

- with only one peripheral clocked on

Table 37. Peripheral current consumption in Run or Sleep mode<sup>(1)</sup>

|                      |                     | Typical                                               | consumption, V                                        | / <sub>DD</sub> = 3.0 V, T <sub>A</sub> =             | 25 °C                         |                                |  |  |  |  |

|----------------------|---------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------|--------------------------------|--|--|--|--|

| Per                  | ipheral             | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                           |  |  |  |  |

|                      | I2C1                | 11                                                    | 9.5                                                   | 7.5                                                   | 9                             |                                |  |  |  |  |

|                      | I2C2                | 4                                                     | 3.5                                                   | 3                                                     | 2.5                           |                                |  |  |  |  |

|                      | LPTIM1              | 10                                                    | 8.5                                                   | 6.5                                                   | 8                             |                                |  |  |  |  |

|                      | LPUART1             | 8                                                     | 6.5                                                   | 5.5                                                   | 6                             |                                |  |  |  |  |

| APB1                 | SPI2                | 9                                                     | 4.5                                                   | 3.5                                                   | 4                             | μΑ/MHz<br>(f <sub>HCLK</sub> ) |  |  |  |  |

|                      | USART2              | 14.5                                                  | 12                                                    | 9.5                                                   | 11                            | ('HCLK)                        |  |  |  |  |

|                      | TIM2                | 10.5                                                  | 8.5                                                   | 7                                                     | 9                             |                                |  |  |  |  |

|                      | TIM6                | 3.5                                                   | 3                                                     | 2.5                                                   | 2                             |                                |  |  |  |  |

|                      | WWDG                | 3                                                     | 2                                                     | 2                                                     | 2                             |                                |  |  |  |  |

|                      | ADC1 <sup>(2)</sup> | 5.5                                                   | 5                                                     | 3.5                                                   | 4                             |                                |  |  |  |  |

|                      | SPI1                | 4                                                     | 3                                                     | 3                                                     | 2.5                           |                                |  |  |  |  |

|                      | USART1              | 14.5                                                  | 11.5                                                  | 9.5                                                   | 12                            |                                |  |  |  |  |

| APB2                 | TIM21               | 7.5                                                   | 6                                                     | 5                                                     | 5.5                           | μΑ/MHz                         |  |  |  |  |

| APB2                 | TIM22               | 7                                                     | 6                                                     | 5                                                     | 6                             | (f <sub>HCLK</sub> )           |  |  |  |  |

|                      | FIREWALL            | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                                |  |  |  |  |

|                      | DBGMCU              | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                                |  |  |  |  |

|                      | SYSCFG              | 2.5                                                   | 2                                                     | 2                                                     | 1.5                           |                                |  |  |  |  |

|                      | GPIOA               | 3.5                                                   | 3                                                     | 2.5                                                   | 2.5                           |                                |  |  |  |  |

| Cortex-              | GPIOB               | 3.5                                                   | 2.5                                                   | 2                                                     | 2.5                           | μΑ/MHz                         |  |  |  |  |

| M0+ core<br>I/O port | GPIOC               | 8.5                                                   | 6.5                                                   | 5.5                                                   | 7                             | (f <sub>HCLK</sub> )           |  |  |  |  |

|                      | GPIOD               | 1                                                     | 0.5                                                   | 0.5                                                   | 0.5                           |                                |  |  |  |  |

|                      | CRC                 | 1.5                                                   | 1                                                     | 1                                                     | 1                             |                                |  |  |  |  |

| AHB                  | FLASH               | 0(3)                                                  | 0(3)                                                  | 0(3)                                                  | 0 <sup>(3)</sup>              | μΑ/MHz<br>(f <sub>HCLK</sub> ) |  |  |  |  |

|                      | DMA1                | 10                                                    | 8                                                     | 6.5                                                   | 8.5                           | ('HCLK)                        |  |  |  |  |

Table 46. MSI oscillator characteristics (continued)

| Symbol                                | Parameter                            | Condition                                | Тур  | Max | Unit |  |

|---------------------------------------|--------------------------------------|------------------------------------------|------|-----|------|--|

|                                       |                                      | MSI range 0                              | 0.75 | -   |      |  |

|                                       |                                      | MSI range 1                              | 1    | -   |      |  |

|                                       |                                      | MSI range 2                              | 1.5  | -   |      |  |

| I <sub>DD(MSI)</sub> <sup>(2)</sup>   | MSI oscillator power consumption     | MSI range 3                              | 2.5  | -   | μΑ   |  |

|                                       |                                      | MSI range 4                              | 4.5  | -   |      |  |

|                                       |                                      | MSI range 5                              | 8    | -   |      |  |

|                                       |                                      | MSI range 6                              | 15   | -   |      |  |

|                                       |                                      | MSI range 0                              | 30   | -   |      |  |

|                                       |                                      | MSI range 1                              | 20   | -   |      |  |

|                                       |                                      | MSI range 2                              | 15   | -   |      |  |

|                                       |                                      | MSI range 3                              | 10   | -   |      |  |

|                                       | MCI agaillatar startus tima          | MSI range 4                              | 6    | -   | μs   |  |

| t <sub>SU(MSI)</sub>                  | MSI oscillator startup time          | MSI range 5                              | 5    | -   |      |  |

|                                       |                                      | MSI range 6,<br>Voltage range 1<br>and 2 | 3.5  | -   |      |  |

|                                       |                                      | MSI range 6,<br>Voltage range 3          | 5    | -   |      |  |

|                                       |                                      | MSI range 0                              | -    | 40  |      |  |

|                                       |                                      | MSI range 1                              | -    | 20  | -    |  |

|                                       |                                      | MSI range 2                              | -    | 10  |      |  |

|                                       |                                      | MSI range 3                              | -    | 4   |      |  |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> | MSI oscillator stabilization time    | MSI range 4                              | -    | 2.5 | μs   |  |

| STAB(MSI)                             | Wor oscillator stabilization time    | MSI range 5                              | -    | 2   | μο   |  |

|                                       |                                      | MSI range 6,<br>Voltage range 1<br>and 2 | -    | 2   |      |  |

|                                       |                                      | MSI range 3,<br>Voltage range 3          | -    | 3   |      |  |

| f                                     | MSI oscillator frequency overshoot   | Any range to range 5                     | -    | 4   |      |  |

| f <sub>OVER(MSI)</sub>                | ivior oscillator frequency overshoot | Any range to range 6                     | -    | 6   | MHz  |  |

<sup>1.</sup> This is a deviation for an individual part, once the initial frequency has been measured.

<sup>2.</sup> Guaranteed by characterization results.

# 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

Table 53. ESD absolute maximum ratings

| Symbol                | Ratings                                               | Conditions                                                      | Class | Maximum<br>value <sup>(1)</sup> | Unit     |

|-----------------------|-------------------------------------------------------|-----------------------------------------------------------------|-------|---------------------------------|----------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | T <sub>A</sub> = +25 °C,<br>conforming to<br>ANSI/JEDEC JS-001  | 2     | 2000                            | <b>V</b> |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = +25 °C,<br>conforming to<br>ANSI/ESD STM5.3.1. | C4    | 500                             | V        |

<sup>1.</sup> Guaranteed by characterization results.

### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

Table 54. Electrical sensitivities

| Symbol | Parameter             | Conditions                                     | Class      |

|--------|-----------------------|------------------------------------------------|------------|

| LU     | Static latch-up class | T <sub>A</sub> = +125 °C conforming to JESD78A | II level A |

Table 60. ADC characteristics (continued)

| Symbol                                                | Parameter                          | Conditions                                      | Min                                                                        | Тур | Max                                               | Unit                       |

|-------------------------------------------------------|------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------|-----|---------------------------------------------------|----------------------------|

| R <sub>AIN</sub> <sup>(3)</sup>                       | External input impedance           | See Equation 1 and Table 61 for details         | -                                                                          | -   | 50                                                | kΩ                         |

| R <sub>ADC</sub> (3)(4)                               | Sampling switch resistance         | -                                               | -                                                                          | -   | 1                                                 | kΩ                         |

| C <sub>ADC</sub> <sup>(3)</sup>                       | Internal sample and hold capacitor | -                                               | -                                                                          | -   | 8                                                 | pF                         |

| t <sub>CAL</sub> (3)(5)                               | Calibration time                   | f <sub>ADC</sub> = 16 MHz                       |                                                                            | 5.2 |                                                   | μs                         |

| CAL, ,, ,                                             | Calibration time                   | -                                               |                                                                            | 83  |                                                   | 1/f <sub>ADC</sub>         |

|                                                       |                                    | ADC clock = HSI16                               | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles                          | ı   | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

| W <sub>LATENCY</sub> <sup>(6)</sup>                   | ADC_DR register write latency      | ADC clock = PCLK/2                              | -                                                                          | 4.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                                       |                                    | ADC clock = PCLK/4                              | -                                                                          | 8.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                                       | Trigger conversion latency         | $f_{ADC} = f_{PCLK}/2 = 16 \text{ MHz}$         | 0.266                                                                      |     |                                                   | μs                         |

|                                                       |                                    | $f_{ADC} = f_{PCLK}/2$                          | 8.5                                                                        |     |                                                   | 1/f <sub>PCLK</sub>        |

| t <sub>latr</sub> (3)                                 |                                    | $f_{ADC} = f_{PCLK}/4 = 8 \text{ MHz}$          | 0.516                                                                      |     |                                                   | μs                         |

|                                                       |                                    | $f_{ADC} = f_{PCLK}/4$                          | 16.5                                                                       |     |                                                   | 1/f <sub>PCLK</sub>        |

|                                                       |                                    | $f_{ADC} = f_{HSI16} = 16 \text{ MHz}$          | 0.252                                                                      | -   | 0.260                                             | μs                         |

| Jitter <sub>ADC</sub>                                 | ADC jitter on trigger conversion   | f <sub>ADC</sub> = f <sub>HSI16</sub>           | -                                                                          | 1   | -                                                 | 1/f <sub>HSI16</sub>       |

| ts <sup>(3)</sup>                                     | Sampling time                      | f <sub>ADC</sub> = 16 MHz                       | 0.093                                                                      | -   | 10.03                                             | μs                         |

| ıs. ,                                                 | Sampling time                      | -                                               | 1.5                                                                        | -   | 160.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>UP_LDO</sub> (3)(5) Internal LDO power-up time |                                    | -                                               | -                                                                          | -   | 10                                                | μs                         |

| t <sub>STAB</sub> <sup>(3)(5)</sup>                   | ADC stabilization time             | -                                               | 14                                                                         |     |                                                   | 1/f <sub>ADC</sub>         |

| t <sub>ConV</sub> <sup>(3)</sup>                      | Total conversion time              | f <sub>ADC</sub> = 16 MHz,<br>12-bit resolution | 0.875                                                                      | -   | 10.81                                             | μs                         |

| <sup>L</sup> ConV` ′                                  | (including sampling time)          | 12-bit resolution                               | 14 to 173 (t <sub>S</sub> for sampling +12.5 for successive approximation) |     | 1/f <sub>ADC</sub>                                |                            |

<sup>1.</sup> V<sub>DDA</sub> minimum value can be decreased in specific temperature conditions. Refer to *Table 61: RAIN max for fADC = 16 MHz*.

<sup>2.</sup> A current consumption proportional to the APB clock frequency has to be added (see *Table 37: Peripheral current consumption in Run or Sleep mode*).

<sup>3.</sup> Guaranteed by design.

Standard channels have an extra protection resistance which depends on supply voltage. Refer to Table 61: RAIN max for fADC = 16 MHz.

<sup>5.</sup> This parameter only includes the ADC timing. It does not take into account register access latency.

<sup>6.</sup> This parameter specifies the latency to transfer the conversion result into the ADC\_DR register. EOC bit is set to indicate the conversion is complete and has the same latency.

# 6.3.17 Comparators

Table 65. Comparator 1 characteristics

| Symbol                   | Parameter                                                      | Conditions                                                                                                                         | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |  |

|--------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|--|

| $V_{DDA}$                | Analog supply voltage                                          | -                                                                                                                                  | 1.65               |     | 3.6                | V         |  |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                        | -                                                                                                                                  | -                  | 400 | -                  | kΩ        |  |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                         | -                                                                                                                                  | -                  | 10  | -                  | K22       |  |

| V <sub>IN</sub>          | Comparator 1 input voltage range                               | -                                                                                                                                  | 0.6                | -   | $V_{DDA}$          | V         |  |

| t <sub>START</sub>       | Comparator startup time                                        | -                                                                                                                                  | -                  | 7   | 10                 | 1         |  |

| td                       | Propagation delay <sup>(2)</sup>                               | -                                                                                                                                  | -                  | 3   | 10                 | μs        |  |

| Voffset                  | Comparator offset                                              | -                                                                                                                                  | -                  | ±3  | ±10                | mV        |  |

| d <sub>Voffset</sub> /dt | Comparator offset variation in worst voltage stress conditions | $\begin{split} V_{DDA} &= 3.6 \text{ V}, V_{IN+} = 0 \text{ V}, \\ V_{IN-} &= V_{REFINT}, T_A = 25 \ ^{\circ}\text{C} \end{split}$ | 0                  | 1.5 | 10                 | mV/1000 h |  |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                             | -                                                                                                                                  | -                  | 160 | 260                | nA        |  |

<sup>1.</sup> Guaranteed by characterization.

Table 66. Comparator 2 characteristics

| Symbol              | Parameter                                     | Conditions                                                                                                                                                        | Min     | Тур       | Max <sup>(1)</sup> | Unit       |

|---------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|--------------------|------------|

| $V_{DDA}$           | Analog supply voltage                         | -                                                                                                                                                                 | 1.65    | -         | 3.6                | V          |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                                                                 | 0       | -         | $V_{DDA}$          | V          |

| t                   | Comparator startup time                       | Fast mode                                                                                                                                                         | -       | 15        | 20                 |            |

| t <sub>START</sub>  | Comparator startup time                       | Slow mode                                                                                                                                                         | -       | 20        | 25                 |            |

| •                   | Propagation delay <sup>(2)</sup> in slow mode | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V                                                                                                                                   | -       | 1.8       | 3.5                |            |

| t <sub>d slow</sub> | Propagation delay 7 in Slow mode              | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                                                    | -       | 2.5       | 6                  | μs         |

| •                   | Propagation delay <sup>(2)</sup> in fast mode | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V                                                                                                                                   | -       | 0.8       | 2                  |            |

| t <sub>d fast</sub> | Fropagation delay Virriast mode               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                                                    | - 1.2 4 |           | 4                  | ]          |

| V <sub>offset</sub> | Comparator offset error                       |                                                                                                                                                                   | -       | <u>±4</u> | ±20                | mV         |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | $V_{DDA} = 3.3V$ , $T_A = 0$ to $50 ^{\circ}$ C, $V_{-} = V_{REFINT}$ , $3/4 ^{\circ}$ $V_{REFINT}$ , $1/2 ^{\circ}$ $V_{REFINT}$ , $1/4 ^{\circ}$ $V_{REFINT}$ . | -       | 15        | 30                 | ppm<br>/°C |

| 1                   | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                                                         | -       | 3.5       | 5                  |            |

| I <sub>COMP2</sub>  | Current consumption.                          | Slow mode                                                                                                                                                         | -       | 0.5       | 2                  | μA         |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

<sup>3.</sup> Comparator consumption only. Internal reference voltage not included.

<sup>2.</sup> The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

<sup>3.</sup> Comparator consumption only. Internal reference voltage (required for comparator operation) is not included.

#### 6.3.18 Timer characteristics

#### **TIM timer characteristics**

The parameters given in the *Table 67* are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Symbol Parameter                                        |                               | Min    | Max                     | Unit                 |  |  |

|------------------------|---------------------------------------------------------|-------------------------------|--------|-------------------------|----------------------|--|--|

| t                      | Timer resolution time                                   |                               | 1      | -                       | t <sub>TIMxCLK</sub> |  |  |

| <sup>t</sup> res(TIM)  | Timer resolution time                                   | f <sub>TIMxCLK</sub> = 32 MHz | 31.25  | -                       | ns                   |  |  |

| f                      | Timer external clock frequency on CH1 to CH4            |                               | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |  |

| f <sub>EXT</sub>       |                                                         | f <sub>TIMxCLK</sub> = 32 MHz | 0      | 16                      | MHz                  |  |  |

| Res <sub>TIM</sub>     | Res <sub>TIM</sub> Timer resolution                     |                               |        | 16                      | bit                  |  |  |

|                        | 16-bit counter clock period when                        | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |  |

| <sup>t</sup> COUNTER   | internal clock is selected (timer's prescaler disabled) | f <sub>TIMxCLK</sub> = 32 MHz | 0.0312 | 2048                    | μs                   |  |  |

| +                      | Maximum possible count                                  | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count                                  | f <sub>TIMxCLK</sub> = 32 MHz | -      | 134.2                   | S                    |  |  |

Table 67. TIMx characteristics<sup>(1)</sup>

#### 6.3.19 Communications interfaces

### I<sup>2</sup>C interface characteristics

The I<sup>2</sup>C interface meets the timings requirements of the I<sup>2</sup>C-bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timing requirements are guaranteed by design when the I<sup>2</sup>C peripheral is properly configured (refer to the reference manual for details). The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and VDDIOx is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement (refer to Section 6.3.13: I/O port characteristics for the I2C I/Os characteristics).

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter (see *Table 68* for the analog filter characteristics).

<sup>1.</sup> TIMx is used as a general term to refer to the TIM2, TIM6, TIM21, and TIM22 timers.

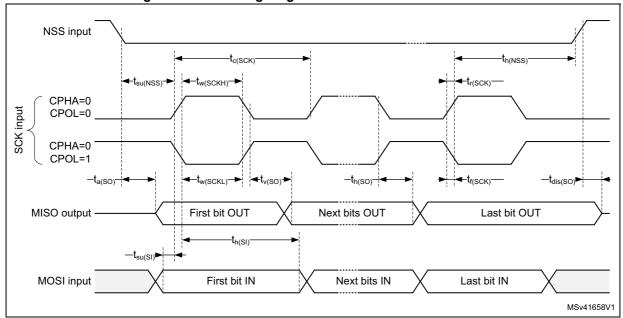

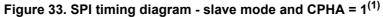

### **SPI** characteristics

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 23*.

Refer to Section 6.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

Table 70. SPI characteristics in voltage Range 1 (1)

| Symbol                                    | Parameter                         | Conditions                                                  | Min     | Тур   | Max               | Unit |

|-------------------------------------------|-----------------------------------|-------------------------------------------------------------|---------|-------|-------------------|------|

|                                           |                                   | Master mode                                                 |         |       | 16                |      |

|                                           | SPI clock frequency               | Slave mode receiver                                         | -       | -     | 16                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> |                                   | Slave mode<br>Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 12 <sup>(2)</sup> | MHz  |

|                                           |                                   | Slave mode<br>Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | -     | 16 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                     | Duty cycle of SPI clock frequency | Slave mode                                                  | 30      | 50    | 70                | %    |

| t <sub>su(NSS)</sub>                      | NSS setup time                    | Slave mode, SPI<br>presc = 2                                | 4*Tpclk | -     | -                 |      |

| t <sub>h(NSS)</sub>                       | NSS hold time                     | Slave mode, SPI<br>presc = 2                                | 2*Tpclk | -     | -                 |      |

| t <sub>w(SCKH)</sub>                      | SCK high and low time             | Master mode                                                 | Tpclk-2 | Tpclk | Tpclk+            |      |

| t <sub>su(MI)</sub>                       | Data input setup time             | Master mode                                                 | 0       | -     | -                 |      |

| t <sub>su(SI)</sub>                       | Data input setup time             | Slave mode                                                  | 3       | -     | -                 |      |

| t <sub>h(MI)</sub>                        | Data input hold time              | Master mode                                                 | 7       | -     | -                 |      |

| t <sub>h(SI)</sub>                        | Data input noid time              | Slave mode                                                  | 3.5     | -     | -                 | ns   |

| t <sub>a(SO</sub>                         | Data output access time           | Slave mode                                                  | 15      | -     | 36                |      |

| t <sub>dis(SO)</sub>                      | Data output disable time          | Slave mode                                                  | 10      | -     | 30                |      |

|                                           | Data output valid time            | Slave mode<br>1.65 V <v<sub>DD&lt;3.6 V</v<sub>             | -       | 18    | 41                |      |

| t <sub>v(SO)</sub>                        |                                   | Slave mode<br>2.7 V <v<sub>DD&lt;3.6 V</v<sub>              | _       | 18    | 25                |      |

| t <sub>v(MO)</sub>                        |                                   | Master mode                                                 | -       | 4     | 7                 |      |

| t <sub>h(SO)</sub>                        | Data output hold time             | Slave mode                                                  | 10      | -     | -                 |      |

| t <sub>h(MO)</sub>                        | Data output noid time             | Master mode                                                 | 0       | -     | -                 |      |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while  $\text{Duty}_{(SCK)} = 50\%$ .

Figure 32. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

Table 78. Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale mechanical data (continued)

| Symbol |     | millimeters          |       |     | inches <sup>(1)</sup> |       |

|--------|-----|----------------------|-------|-----|-----------------------|-------|

| Symbol | Min | Тур                  | Max   | Min | Тур                   | Max   |

| F      | -   | 0.305 <sup>(3)</sup> | -     | -   | 0.012                 | -     |

| G      | -   | 0.440 <sup>(3)</sup> | -     | -   | 0.017                 | -     |

| aaa    | -   | -                    | 0.100 | -   | -                     | 0.004 |

| bbb    | -   | -                    | 0.100 | -   | -                     | 0.004 |

| ccc    | -   | -                    | 0.100 | -   | -                     | 0.004 |

| ddd    | -   | -                    | 0.050 | -   | -                     | 0.002 |

| eee    | -   | -                    | 0.050 | -   | -                     | 0.002 |

- 1. Values in inches are converted from mm and rounded to the 3rd decimal place.

- 2. Nominal dimension rounded to the 3rd decimal place results from process capability.

- 3. Calculated dimensions are rounded to the 3rd decimal place.

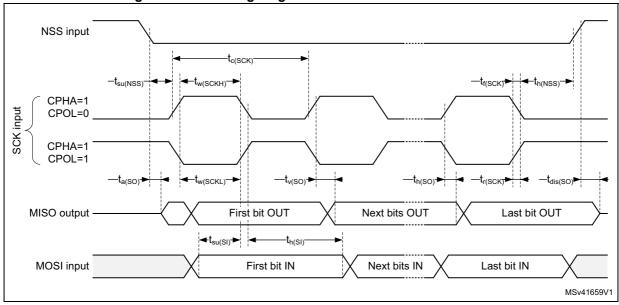

Figure 47. Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale recommended footprint

Table 79. Standard WLCSP36 recommended PCB design rules

| Dimension      | Recommended values                            |

|----------------|-----------------------------------------------|

| Pitch          | 0.4 mm                                        |

| Dpad           | 260 µm max. (circular)<br>220 µm recommended  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)         |

| PCB pad design | Non-solder mask defined via underbump allowed |

# 9 Revision history

**Table 86. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |