Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                       |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l051r8t7 |

# **List of figures**

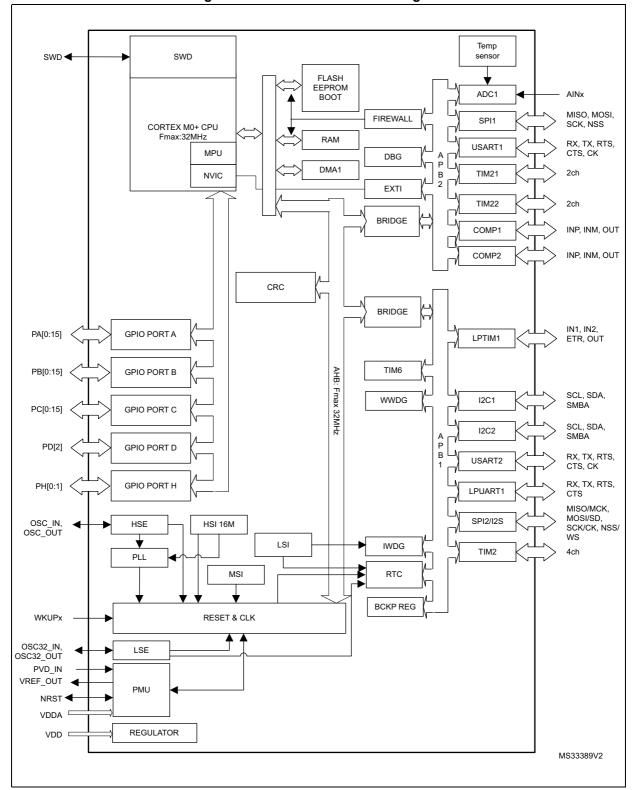

| Figure 1.   | STM32L051x6/8 block diagram                                                                  |     |

|-------------|----------------------------------------------------------------------------------------------|-----|

| Figure 2.   | Clock tree                                                                                   |     |

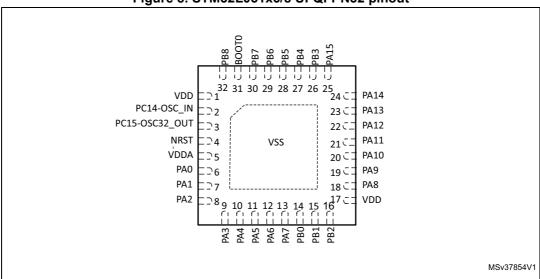

| Figure 3.   | STM32L051x6/8 LQFP64 pinout - 10 x 10 mm                                                     |     |

| Figure 4.   | STM32L051x6/8 TFBGA64 ballout - 5x 5 mm                                                      |     |

| Figure 5.   | STM32L051x6/8 LQFP48 pinout - 7 x 7 mm                                                       |     |

| Figure 6.   | STM32L051x6/8 WLCSP36 ballout                                                                |     |

| Figure 7.   | STM32L051x6/8 LQFP32 pinout                                                                  |     |

| Figure 8.   | STM32L051x6/8 UFQFPN32 pinout                                                                |     |

| Figure 9.   | Memory map                                                                                   | 46  |

| Figure 10.  | Pin loading conditions                                                                       | 47  |

| Figure 11.  | Pin input voltage                                                                            | 47  |

| Figure 12.  | Power supply scheme                                                                          |     |

| Figure 13.  | Current consumption measurement scheme                                                       | 48  |

| Figure 14.  | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from                              |     |

|             | Flash memory, Range 2, HSE, 1WS                                                              | 57  |

| Figure 15.  | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from                              |     |

|             | Flash memory, Range 2, HSI16, 1WS                                                            | 57  |

| Figure 16.  | IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Low-power run mode, code running                    |     |

|             | from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS                                             | 61  |

| Figure 17.  | IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Stop mode with RTC enabled                          |     |

| _           | and running on LSE Low drive                                                                 | 62  |

| Figure 18.  | IDD vs VDD, at TA= 25/55/85/105/125 °C, Stop mode with RTC disabled,                         |     |

| _           | all clocks OFF                                                                               | 62  |

| Figure 19.  | High-speed external clock source AC timing diagram                                           | 67  |

| Figure 20.  | Low-speed external clock source AC timing diagram                                            |     |

| Figure 21.  | HSE oscillator circuit diagram                                                               |     |

| Figure 22.  | Typical application with a 32.768 kHz crystal                                                |     |

| Figure 23.  | HSI16 minimum and maximum value versus temperature                                           |     |

| Figure 24.  | VIH/VIL versus VDD (CMOS I/Os)                                                               |     |

| Figure 25.  | VIH/VIL versus VDD (TTL I/Os)                                                                |     |

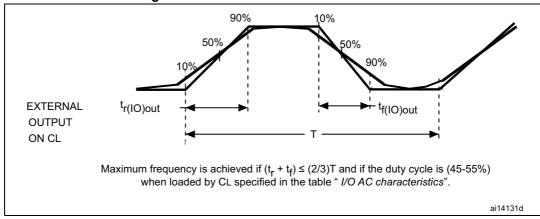

| Figure 26.  | I/O AC characteristics definition                                                            |     |

| Figure 27.  | Recommended NRST pin protection                                                              |     |

| Figure 28.  | ADC accuracy characteristics                                                                 |     |

| Figure 29.  | Typical connection diagram using the ADC                                                     |     |

| Figure 30.  | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |     |

| Figure 31.  | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )     |     |

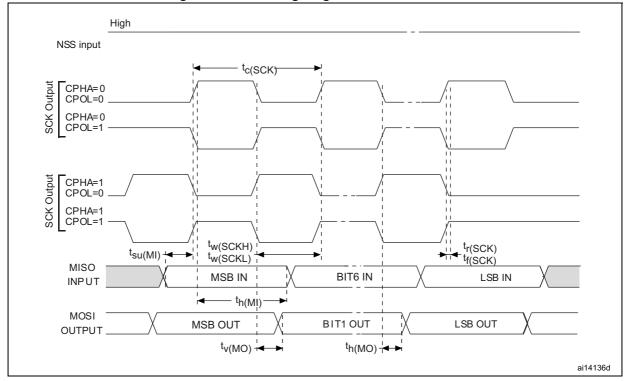

| Figure 32.  | SPI timing diagram - slave mode and CPHA = 0                                                 |     |

| Figure 33.  | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                                  | 97  |

| Figure 34.  | SPI timing diagram - master mode <sup>(1)</sup>                                              | 98  |

| Figure 35.  | SPI timing diagram - master mode <sup>(1)</sup>                                              | 100 |

| Figure 36.  | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>                     | 100 |

| Figure 37.  | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline                            |     |

| Figure 38.  | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint                      |     |

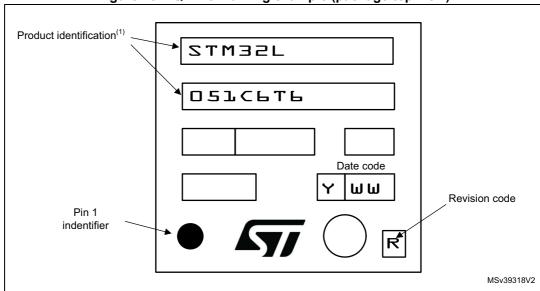

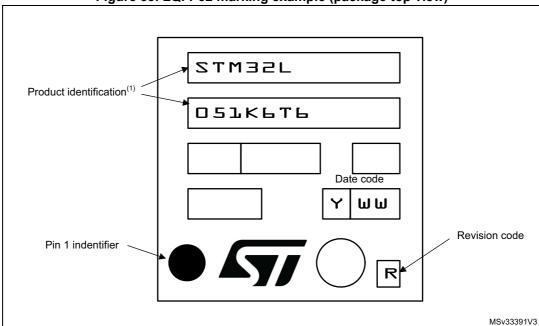

| Figure 39.  | LQFP64 marking example (package top view)                                                    |     |

| Figure 40.  | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch thin profile fine pitch ball                       |     |

| . iguio 40. | grid array package outline                                                                   | 105 |

| Figure 41.  | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball                      |     |

| . 19410 111 | ,grid array recommended footprint                                                            | 106 |

|             |                                                                                              |     |

Figure 1. STM32L051x6/8 block diagram

Table 5. Functionalities depending on the working mode (from Run/active down to standby) (continued)<sup>(1)</sup>

|                               |            |         | Low-         | Low-           |                  | Stop                 | 5 | Standby           |

|-------------------------------|------------|---------|--------------|----------------|------------------|----------------------|---|-------------------|

| IPs                           | Run/Active | Sleep   | power<br>run | power<br>sleep |                  | Wakeup<br>capability |   | Wakeup capability |

| High Speed<br>External (HSE)  | 0          | 0       | 0            | 0              |                  |                      |   |                   |

| Low Speed Internal (LSI)      | 0          | 0       | 0            | 0              | 0                |                      | 0 |                   |

| Low Speed<br>External (LSE)   | 0          | 0       | 0            | 0              | 0                |                      | 0 |                   |

| Multi-Speed<br>Internal (MSI) | 0          | 0       | Υ            | Y              |                  |                      |   |                   |

| Inter-Connect<br>Controller   | Y          | Y       | Y            | Y              | Υ                |                      |   |                   |

| RTC                           | 0          | 0       | 0            | 0              | 0                | 0                    | 0 |                   |

| RTC Tamper                    | 0          | 0       | 0            | 0              | 0                | 0                    | 0 | 0                 |

| Auto WakeUp<br>(AWU)          | 0          | 0       | 0            | 0              | 0                | 0                    | 0 | 0                 |

| USART                         | 0          | 0       | 0            | 0              | O <sup>(3)</sup> | 0                    | - |                   |

| LPUART                        | 0          | 0       | 0            | 0              | O <sup>(3)</sup> | 0                    | - |                   |

| SPI                           | 0          | 0       | 0            | 0              |                  |                      |   |                   |

| I2C                           | 0          | 0       | 0            | 0              | O <sup>(4)</sup> | 0                    |   |                   |

| ADC                           | 0          | 0       |              |                |                  |                      |   |                   |

| Temperature sensor            | 0          | 0       | 0            | 0              | 0                |                      |   |                   |

| Comparators                   | 0          | 0       | 0            | 0              | 0                | 0                    | ı |                   |

| 16-bit timers                 | 0          | 0       | 0            | 0              |                  |                      | ı |                   |

| LPTIMER                       | 0          | 0       | 0            | 0              | 0                | 0                    |   |                   |

| IWDG                          | 0          | 0       | 0            | 0              | 0                | 0                    | 0 | 0                 |

| WWDG                          | 0          | 0       | 0            | 0              |                  |                      | 1 |                   |

| SysTick Timer                 | 0          | 0       | 0            | 0              |                  |                      | - |                   |

| GPIOs                         | 0          | 0       | 0            | 0              | 0                | 0                    |   | 2 pins            |

| Wakeup time to Run mode       | 0 μs       | 0.36 µs | 3 µs         | 32 µs          |                  | 3.5 µs 50 µs         |   | 50 µs             |

#### **Nested vectored interrupt controller (NVIC)**

The ultra-low-power STM32L051x6/8 embed a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels and 4 priority levels.

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- · provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

### 3.4 Reset and supply management

#### 3.4.1 Power supply schemes

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supplies for ADC reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

#### 3.4.2 Power supply supervisor

The devices have an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

Two versions are available:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the VDD min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog.

The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

#### RTC clock source

The LSI, LSE or HSE sources can be chosen to clock the RTC, whatever the system clock.

#### Startup clock

After reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

#### • Clock security system (CSS)

This feature can be enabled by software. If an HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled. Another clock security system can be enabled, in case of failure of the LSE it provides an interrupt or wakeup event which is generated if enabled.

## Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

5//

#### 3.8 Memories

The STM32L051x6/8 devices have the following features:

- 8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 32 or 64 Kbytes of embedded Flash program memory

- 2 Kbytes of data EEPROM

- Information block containing 32 user and factory options bytes plus 4 Kbytes of system memory

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

- The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- **Level 2**: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The firewall protects parts of code/data from access by the rest of the code that is executed outside of the protected area. The granularity of the protected code segment or the non-volatile data segment is 256 bytes (Flash memory or EEPROM) against 64 bytes for the volatile data segment (RAM).

The whole non-volatile memory embeds the error correction code (ECC) feature.

### 3.9 Boot modes

At startup, BOOT0 pin and nBOOT1 option bit are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- · Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using SPI1(PA4, PA5, PA6, PA7) or SPI2 (PB12, PB13, PB14, PB15), USART1(PA9, PA10) or USART2(PA2, PA3). See STM32™ microcontroller system memory boot mode AN2606 for details.

PB7 PB6 PB5 PB4 PB3 32 31 30 29 28 27 26 25 24 PA14 VDD ☐1 PC14-OSC32\_IN 2 23 PA13 PC15-OSC32\_OUT 3 22 PA12 21 PA11 NRST ☐4 LQFP32 20 PA10 VDDA ☐ 5 19 PA9 PA0 🗆 6 18 PA8 17 VDD PA1 ☐ 7 MSv35429V3

Figure 7. STM32L051x6/8 LQFP32 pinout

1. The above figure shows the package top view.

Figure 8. STM32L051x6/8 UFQFPN32 pinout

1. The above figure shows the package top view.

5/

Table 15. STM32L051x6/8 pin definitions (continued)

|        |         | Pin Nu | umber                  |        |          |                                       | -        |               |       | ,                                                     |                                                |

|--------|---------|--------|------------------------|--------|----------|---------------------------------------|----------|---------------|-------|-------------------------------------------------------|------------------------------------------------|

| LQFP64 | TFBGA64 | LQFP48 | WLCSP36 <sup>(1)</sup> | LQFP32 | UFQFPN32 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                   | Additional<br>functions                        |

| 5      | C1      | 5      | -                      | -      | -        | PH0-OSC_IN<br>(PH0)                   | I/O      | TC            | -     | -                                                     | OSC_IN                                         |

| 6      | D1      | 6      | -                      | -      | -        | PH1-<br>OSC_OUT<br>(PH1)              | I/O      | тс            | 1     | -                                                     | OSC_OUT                                        |

| 7      | E1      | 7      | C6                     | 4      | 4        | NRST                                  | I/O      | RST           | -     | -                                                     | -                                              |

| 8      | E3      | -      | -                      | -      | -        | PC0                                   | I/O      | FT            | -     | LPTIM1_IN1,<br>EVENTOUT                               | ADC_IN10                                       |

| 9      | E2      | -      | -                      | -      | -        | PC1                                   | I/O      | FT            | -     | LPTIM1_OUT,<br>EVENTOUT                               | ADC_IN11                                       |

| 10     | F2      | -      | -                      | -      | -        | PC2                                   | I/O      | FT            | -     | LPTIM1_IN2,<br>SPI2_MISO/I2S2_M<br>CK                 | ADC_IN12                                       |

| 11     | -       | -      | -                      | ı      | -        | PC3                                   | I/O      | FT            | 1     | LPTIM1_ETR,<br>SPI2_MOSI/I2S2_SD                      | ADC_IN13                                       |

| 12     | F1      | 8      | -                      | -      | -        | VSSA                                  | S        |               | -     | -                                                     | -                                              |

| -      | G1      | -      | E6                     | ı      | ı        | VREF+                                 | S        |               | 1     | -                                                     | -                                              |

| 13     | H1      | 9      | D5                     | 5      | 5        | VDDA                                  | S        |               | ı     | -                                                     | -                                              |

| 14     | G2      | 10     | D4                     | 6      | 6        | PA0                                   | I/O      | TC            | 1     | TIM2_CH1,<br>USART2_CTS,<br>TIM2_ETR,<br>COMP1_OUT    | COMP1_INM6,<br>ADC_IN0,<br>RTC_TAMP2/WKU<br>P1 |

| 15     | H2      | 11     | F6                     | 7      | 7        | PA1                                   | I/O      | FT            | 1     | EVENTOUT,<br>TIM2_CH2,<br>USART2_RTS_DE,<br>TIM21_ETR | COMP1_INP,<br>ADC_IN1                          |

| 16     | F3      | 12     | E5                     | 8      | 8        | PA2                                   | I/O      | FT            | -     | TIM21_CH1,<br>TIM2_CH3,<br>USART2_TX,<br>COMP2_OUT    | COMP2_INM6,<br>ADC_IN2                         |

| 17     | G3      | 13     | F5                     | 9      | 9        | PA3                                   | I/O      | FT            | -     | TIM21_CH2,<br>TIM2_CH4,<br>USART2_RX                  | COMP2_INP,<br>ADC_IN3                          |

| 18     | C2      | -      | -                      | -      | -        | VSS                                   | S        |               | -     | -                                                     | -                                              |

| Symbol                                  | Parameter                                                     | Conditions | Min | Тур | Max  | Unit                     |

|-----------------------------------------|---------------------------------------------------------------|------------|-----|-----|------|--------------------------|

| I <sub>LPBUF</sub> <sup>(4)</sup>       | Consumption of reference voltage buffer for VREF_OUT and COMP | -          | -   | 730 | 1200 | nA                       |

| V <sub>REFINT_DIV1</sub> <sup>(4)</sup> | 1/4 reference voltage                                         | -          | 24  | 25  | 26   |                          |

| V <sub>REFINT_DIV2</sub> <sup>(4)</sup> | 1/2 reference voltage                                         | -          | 49  | 50  | 51   | %<br>V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(4)</sup> | 3/4 reference voltage                                         | -          | 74  | 75  | 76   | IXEI IIVI                |

Table 26. Embedded internal reference voltage<sup>(1)</sup> (continued)

- Refer to Table 38: Peripheral current consumption in Stop and Standby mode for the value of the internal reference current consumption (I<sub>REFINT</sub>).

- 2. Guaranteed by test in production.

- 3. The internal V<sub>REF</sub> value is individually measured in production and stored in dedicated EEPROM bytes.

- 4. Guaranteed by design.

- 5. Shortest sampling time can be determined in the application by multiple iterations.

- 6. To guarantee less than 1% VREF\_OUT deviation.

#### 6.3.4 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code. The current consumption is measured as described in *Figure 13: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code if not specified otherwise

The current consumption values are derived from the tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 23: General operating conditions* unless otherwise specified.

The MCU is placed under the following conditions:

- All I/O pins are configured in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time and prefetch is adjusted depending on fHCLK frequency and voltage range to provide the best CPU performance unless otherwise specified.

- When the peripherals are enabled f<sub>APB1</sub> = f<sub>APB2</sub> = f<sub>APB</sub>

- When PLL is ON, the PLL inputs are equal to HSI = 16 MHz (if internal clock is used) or HSE = 16 MHz (if HSE bypass mode is used)

- The HSE user clock applied to OSCI\_IN input follows the characteristic specified in Table 40: High-speed external user clock characteristics

- For maximum current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.6 V is applied to all supply pins

- For typical current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.0 V is applied to all supply pins if not specified otherwise

The parameters given in *Table 47*, *Table 23* and *Table 24* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 23*.

#### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- $\bullet$   $\,$  all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked OFF

- with only one peripheral clocked on

Table 37. Peripheral current consumption in Run or Sleep mode<sup>(1)</sup>

| Peripheral           |                     | Typical                                               | consumption, V                                        | / <sub>DD</sub> = 3.0 V, T <sub>A</sub> =             | 25 °C                         |                                |

|----------------------|---------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------|--------------------------------|

|                      |                     | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                           |

|                      | I2C1                | 11                                                    | 9.5                                                   | 7.5                                                   | 9                             |                                |

|                      | I2C2                | 4                                                     | 3.5                                                   | 3                                                     | 2.5                           |                                |

|                      | LPTIM1              | 10                                                    | 8.5                                                   | 6.5                                                   | 8                             |                                |

|                      | LPUART1             | 8                                                     | 6.5                                                   | 5.5                                                   | 6                             |                                |

| APB1                 | SPI2                | 9                                                     | 4.5                                                   | 3.5                                                   | 4                             | μΑ/MHz<br>(f <sub>HCLK</sub> ) |

|                      | USART2              | 14.5                                                  | 12                                                    | 9.5                                                   | 11                            | ('HCLK)                        |

|                      | TIM2                | 10.5                                                  | 8.5                                                   | 7                                                     | 9                             |                                |

|                      | TIM6                | 3.5                                                   | 3                                                     | 2.5                                                   | 2                             |                                |

|                      | WWDG                | 3                                                     | 2                                                     | 2                                                     | 2                             |                                |

|                      | ADC1 <sup>(2)</sup> | 5.5                                                   | 5                                                     | 3.5                                                   | 4                             |                                |

|                      | SPI1                | 4                                                     | 3                                                     | 3                                                     | 2.5                           |                                |

|                      | USART1              | 14.5                                                  | 11.5                                                  | 9.5                                                   | 12                            |                                |

| APB2                 | TIM21               | 7.5                                                   | 6                                                     | 5                                                     | 5.5                           | μΑ/MHz                         |

| APB2                 | TIM22               | 7                                                     | 6                                                     | 5                                                     | 6                             | (f <sub>HCLK</sub> )           |

|                      | FIREWALL            | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                                |

|                      | DBGMCU              | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                                |

|                      | SYSCFG              | 2.5                                                   | 2                                                     | 2                                                     | 1.5                           |                                |

|                      | GPIOA               | 3.5                                                   | 3                                                     | 2.5                                                   | 2.5                           |                                |

| Cortex-              | GPIOB               | 3.5                                                   | 2.5                                                   | 2                                                     | 2.5                           | μΑ/MHz                         |

| M0+ core<br>I/O port | GPIOC               | 8.5                                                   | 6.5                                                   | 5.5                                                   | 7                             | (f <sub>HCLK</sub> )           |

|                      | GPIOD               | 1                                                     | 0.5                                                   | 0.5                                                   | 0.5                           |                                |

|                      | CRC                 | 1.5                                                   | 1                                                     | 1                                                     | 1                             |                                |

| AHB                  | FLASH               | 0(3)                                                  | 0(3)                                                  | 0(3)                                                  | 0 <sup>(3)</sup>              | μΑ/MHz<br>(f <sub>HCLK</sub> ) |

|                      | DMA1                | 10                                                    | 8                                                     | 6.5                                                   | 8.5                           | ('HCLK)                        |

#### 6.3.6 **External clock source characteristics**

### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in Section 6.3.12. However, the recommended clock input waveform is shown in Figure 19.

Table 40. High-speed external user clock characteristics<sup>(1)</sup>

| Symbol                    | Parameter                           | Conditions                       | Min                | Тур | Max                | Unit |

|---------------------------|-------------------------------------|----------------------------------|--------------------|-----|--------------------|------|

| f                         | User external clock source          | CSS is ON or<br>PLL is used      | 1                  | 8   | 32                 | MHz  |

| f <sub>HSE_ext</sub>      | frequency                           | CSS is OFF,<br>PLL not used      | 0                  | 8   | 32                 | MHz  |

| V <sub>HSEH</sub>         | OSC_IN input pin high level voltage |                                  | 0.7V <sub>DD</sub> | -   | $V_{DD}$           | V    |

| V <sub>HSEL</sub>         | OSC_IN input pin low level voltage  |                                  | V <sub>SS</sub>    | ı   | 0.3V <sub>DD</sub> | V    |

| $t_{w(HSE)} \ t_{w(HSE)}$ | OSC_IN high or low time             |                                  | 12                 | ı   | -                  | ns   |

| t <sub>r(HSE)</sub>       | OSC_IN rise or fall time            | -                                | -                  | -   | 20                 | 113  |

| C <sub>in(HSE)</sub>      | OSC_IN input capacitance            |                                  | -                  | 2.6 | -                  | pF   |

| DuCy <sub>(HSE)</sub>     | Duty cycle                          |                                  | 45                 | ı   | 55                 | %    |

| ΙL                        | OSC_IN Input leakage current        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | ı   | ±1                 | μΑ   |

<sup>1.</sup> Guaranteed by design.

$V_{\mathsf{HSEH}}$ 90% 10%  $V_{HSEL}$ -T<sub>HSE</sub>  $f_{\mathsf{HSE\_ext}}$ EXTERNAL CLOCK SOURCE OSC\_IN STM32Lxx ai18232c

Figure 19. High-speed external clock source AC timing diagram

Figure 26. I/O AC characteristics definition

### 6.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub>, except when it is internally driven low (see *Table 59*).

Unless otherwise specified, the parameters given in *Table 59* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 23*.

| Symbol                                | Parameter                                       | Conditions                                                   | Min      | Тур                               | Max      | Unit |

|---------------------------------------|-------------------------------------------------|--------------------------------------------------------------|----------|-----------------------------------|----------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST input low level voltage                    | -                                                            | $V_{SS}$ | -                                 | 8.0      |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST input high level voltage                   | -                                                            | 1.4      | -                                 | $V_{DD}$ |      |

| V(1)                                  | NRST output low level                           | I <sub>OL</sub> = 2 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V    | -        | -                                 | 0.4      | ٧    |

| V <sub>OL(NRST)</sub> <sup>(1)</sup>  | voltage                                         | I <sub>OL</sub> = 1.5 mA<br>1.65 V < V <sub>DD</sub> < 2.7 V | -        | -                                 | 0.4      |      |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage hysteresis         | -                                                            | ı        | 10%V <sub>DD</sub> <sup>(2)</sup> | ı        | mV   |

| R <sub>PU</sub>                       | Weak pull-up equivalent resistor <sup>(3)</sup> | $V_{IN} = V_{SS}$                                            | 30       | 45                                | 60       | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST input filtered pulse                       | -                                                            | 1        | -                                 | 50       | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup>  | NRST input not filtered pulse                   | -                                                            | 350      | -                                 | -        | ns   |

Table 59. NRST pin characteristics

577

<sup>1.</sup> Guaranteed by design.

<sup>2. 200</sup> mV minimum value

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is around 10%.

Figure 34. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

Table 75. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid array package mechanical data (continued)

| Symbol |     | millimeters |       |     | inches <sup>(1)</sup> |        |

|--------|-----|-------------|-------|-----|-----------------------|--------|

| Symbol | Min | Тур         | Max   | Min | Тур                   | Max    |

| ddd    | -   | -           | 0.080 | -   | -                     | 0.0031 |

| eee    | -   | -           | 0.150 | -   | -                     | 0.0059 |

| fff    | -   | -           | 0.050 | -   | -                     | 0.0020 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

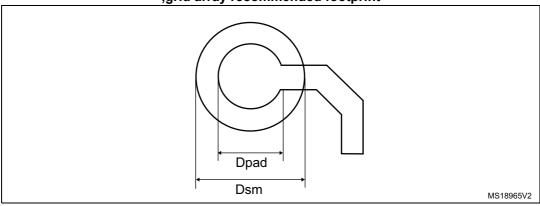

Figure 41. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball ,grid array recommended footprint

Table 76. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension    | Recommended values                                              |

|--------------|-----------------------------------------------------------------|

| Pitch        | 0.5                                                             |

| Dpad         | 0.27 mm                                                         |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |

| Solder paste | 0.27 mm aperture diameter.                                      |

Note: Non solder mask defined (NSMD) pads are recommended.

4 to 6 mils solder paste screen printing process.

#### **Device marking for LQFP48**

The following figure gives an example of topside marking versus pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 45. LQFP48 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

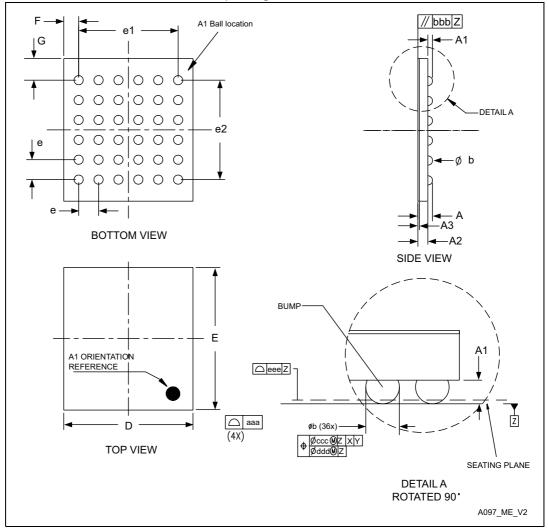

Table 78. Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale mechanical data (continued)

| Symbol | millimeters |                      |       |     | inches <sup>(1)</sup> |       |

|--------|-------------|----------------------|-------|-----|-----------------------|-------|

| Symbol | Min         | Тур                  | Max   | Min | Тур                   | Max   |

| F      | -           | 0.305 <sup>(3)</sup> | -     | -   | 0.012                 | -     |

| G      | -           | 0.440 <sup>(3)</sup> | -     | -   | 0.017                 | -     |

| aaa    | -           | -                    | 0.100 | -   | -                     | 0.004 |

| bbb    | -           | -                    | 0.100 | -   | -                     | 0.004 |

| ccc    | -           | -                    | 0.100 | -   | -                     | 0.004 |

| ddd    | -           | -                    | 0.050 | -   | -                     | 0.002 |

| eee    | -           | -                    | 0.050 | -   | -                     | 0.002 |

- 1. Values in inches are converted from mm and rounded to the 3rd decimal place.

- 2. Nominal dimension rounded to the 3rd decimal place results from process capability.

- 3. Calculated dimensions are rounded to the 3rd decimal place.

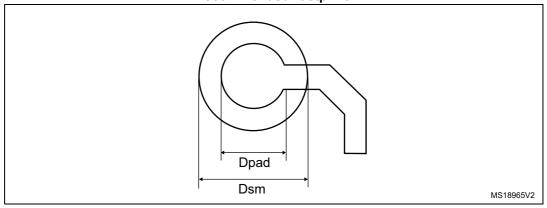

Figure 47. Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale recommended footprint

Table 79. Standard WLCSP36 recommended PCB design rules

| Dimension      | Recommended values                            |

|----------------|-----------------------------------------------|

| Pitch          | 0.4 mm                                        |

| Dpad           | 260 µm max. (circular)<br>220 µm recommended  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)         |

| PCB pad design | Non-solder mask defined via underbump allowed |

## 7.5 Thin WLCSP36 package information

Figure 49. Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale package outline

- 1. Drawing is not to scale.

- 2. b dimensions is measured at the maximum bump diameter parallel to primary datum Z.

- 3. Primary datum Z and seating plane are defined by the spherical crowns of the bump.

- 4. Bump position designation per JESD 95-1, SPP-010.

#### **Device marking for LQFP32**

The following figure gives an example of topside marking versus pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 53. LQFP32 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

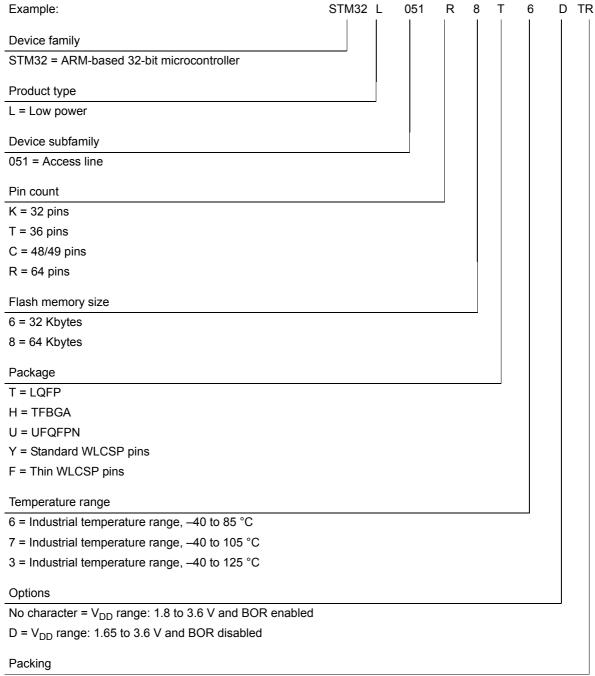

## 8 Part numbering

Table 85. STM32L051x6/8 ordering information scheme

TR = tape and reel

No character = tray or tube

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

130/131

Table 86. Document revision history (continued)

| Date                    | Revision   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Date</b> 07-Mar-2017 | Revision 7 | Changes  Added thin WLCSP36 package  Updated number of I2S interfaces in Table 2: Ultra-low-power STM32L051x6/x8 device features and peripheral counts.  Removed note 2 related to PA4 in Table 15: STM32L051x6/8 pin definitions  Added mission profile compliance with JEDEC JESD47 in Section 6.2: Absolute maximum ratings.  Removed CRS from Table 37: Peripheral current consumption in Run or Sleep mode.  Added note 2. related to the position of the external capacitor below Figure 27: Recommended NRST pin protection.  Updated R <sub>L</sub> in Table 60: ADC characteristics.  Updated t <sub>AF</sub> maximum value for range 1 in Table 68: I2C analog filter characteristics.  Updated t <sub>WUUSART</sub> description in Table 69: USART/LPUART characteristics. |

|                         |            | . , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                         |            | Added reference to optional marking or inset/upset marks in all package device marking sections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                         |            | Previous WLCSP36 package renamed "Standard" WLCSP36; added Note 2. below Figure 46: Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale package outline and updated Table 78: Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale mechanical data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |