Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 29                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 2K x 8                                                                   |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                             |

| Data Converters            | A/D 10x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 36-UFBGA, WLCSP                                                          |

| Supplier Device Package    | 36-WLCSP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l051t8y6dtr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 42. | TFBGA64 marking example (package top view)                              | 107 |

|------------|-------------------------------------------------------------------------|-----|

| Figure 43. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline         | 108 |

| Figure 44. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint   | 109 |

| Figure 45. | LQFP48 marking example (package top view)                               |     |

| Figure 46. | Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale  |     |

| -          | package outline.                                                        | 111 |

| Figure 47. | Standard WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale  |     |

| -          | recommended footprint.                                                  | 112 |

| Figure 48. | Standard WLCSP36 marking example (package top view)                     | 113 |

| Figure 49. | Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale      |     |

| -          | package outline.                                                        | 114 |

| Figure 50. | Thin WLCSP36 - 2.61 x 2.88 mm, 0.4 mm pitch wafer level chip scale      |     |

|            | package recommended footprint                                           | 115 |

| Figure 51. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline         | 116 |

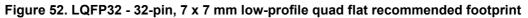

| Figure 52. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat recommended footprint   | 117 |

| Figure 53. | LQFP32 marking example (package top view)                               |     |

| Figure 54. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |     |

| -          | package outline.                                                        | 119 |

| Figure 55. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |     |

| -          | recommended footprint.                                                  | 120 |

| Figure 56. | UFQFPN32 marking example (package top view)                             |     |

| Figure 57. | Thermal resistance                                                      |     |

|            |                                                                         |     |

# 2.1 Device overview

| Table 2. Ultra-low-power | STM32L051x6 | 6/x8 device | features and | periphera | al counts |  |

|--------------------------|-------------|-------------|--------------|-----------|-----------|--|

|                          |             |             |              |           |           |  |

| Peripheral                    |                     | STM32<br>L051K6                                                                                     | STM32L<br>051T6        | STM32<br>L051C6        | STM32<br>L051R6        | STM32<br>L051K8              | STM32L<br>051T8        | STM32<br>L051C8        | STM32<br>L051R8        |

|-------------------------------|---------------------|-----------------------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|------------------------------|------------------------|------------------------|------------------------|

| Flash (Kbyte                  | s)                  |                                                                                                     | 32                     | 2                      |                        |                              | 64                     | 4                      |                        |

| Data EEPROI                   | M (Kbytes)          |                                                                                                     | 2                      |                        |                        |                              | 2                      |                        |                        |

| RAM (Kbytes                   | i)                  |                                                                                                     | 8                      |                        |                        |                              | 8                      | }                      |                        |

|                               | General-<br>purpose |                                                                                                     | 3                      |                        |                        |                              | 3                      | 5                      |                        |

| Timers                        | Basic               |                                                                                                     | 1                      |                        |                        |                              | 1                      |                        |                        |

|                               | LPTIMER             |                                                                                                     | 1                      |                        |                        |                              | 1                      |                        |                        |

|                               | ICK/IWDG/<br>/DG    |                                                                                                     | 1/1/                   | 1/1                    |                        |                              | 1/1/                   | 1/1                    |                        |

|                               | SPI/I2S             | 3(2) <sup>(1)</sup> /0                                                                              | 3(2) <sup>(1)</sup> /0 | 4(2) <sup>(1)</sup> /1 | 4(2) <sup>(1)</sup> /1 | 3(2) <sup>(1)</sup> /0       | 3(2) <sup>(1)</sup> /0 | 4(2) <sup>(1)</sup> /1 | 4(2) <sup>(1)</sup> /1 |

| Communi-                      | l <sup>2</sup> C    | 1                                                                                                   | 2                      | 2                      | 2                      | 1                            | 2                      | 2                      | 2                      |

| cation<br>interfaces          | USART               |                                                                                                     | 2                      |                        |                        | 2                            |                        |                        |                        |

|                               | LPUART              | 0                                                                                                   | 1                      | 1                      | 1                      | 0                            | 1                      | 1                      | 1                      |

| GPIOs                         |                     | 27 <sup>(2)</sup>                                                                                   | 29                     | 37                     | 51 <sup>(3)</sup>      | 27 <sup>(2)</sup>            | 29                     | 37                     | 51 <sup>(3)</sup>      |

| Clocks:<br>HSE/LSE/HSI        | I/MSI/LSI           | 0/1/1/1/1                                                                                           | 0/1/1/1/1              | 1/1/1/1/1              | 1/1/1/1/1              | 0/1/1/1/1                    | 0/1/1/1/1              | 1/1/1/1/1              | 1/1/1/1/1              |

| 12-bit synchr<br>Number of ch |                     | 1<br>10                                                                                             | 1<br>10                | 1<br>10                | 1<br>16 <sup>(3)</sup> | 1<br>10                      | 1<br>10                | 1<br>10                | 1<br>16 <sup>(3)</sup> |

| Comparators                   | i                   |                                                                                                     | 2                      | L                      | L                      |                              | 2                      |                        |                        |

| Max. CPU fre                  | quency              | 32 MHz                                                                                              |                        |                        |                        |                              |                        |                        |                        |

| Operating vo                  | Itage               | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option<br>1.65 V to 3.6 V without BOR option |                        |                        |                        |                              |                        |                        |                        |

| Operating ter                 | mperatures          |                                                                                                     |                        |                        |                        | re: –40 to +<br>re: –40 to + |                        |                        |                        |

| Packages                      |                     | LQFP32,<br>UFQFPN<br>32                                                                             | WLCSP<br>36            | LQFP48                 | LQFP64<br>TFBGA<br>64  | LQFP32,<br>UFQFPN<br>32      | WLCSP<br>36            | LQFP48                 | LQFP64<br>TFBGA<br>64  |

$1. \ \ 2 \ SPI \ interfaces \ are \ USARTs \ operating \ in \ SPI \ master \ mode.$

2. LQFP32 has two GPIOs, less than UFQFPN32 (27).

3. TFBGA64 has one GPIO, one ADC input and one capacitive sensing channel less than LQFP64.

# 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM<sup>®</sup> Cortex<sup>®</sup>-M4, including ARM<sup>®</sup> Cortex<sup>®</sup>-M3 and ARM<sup>®</sup> Cortex<sup>®</sup>-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 ultra-low-power series are the best solution for applications such as gaz/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

### Table 5. Functionalities depending on the working mode (from Run/active down to standby) (continued)<sup>(1)</sup>

|                                                     |                        |                        | Low-            | Low-           | Stop |                                    | Standby |                                        |

|-----------------------------------------------------|------------------------|------------------------|-----------------|----------------|------|------------------------------------|---------|----------------------------------------|

| IPs                                                 | Run/Active             | Sleep                  | power<br>run    | power<br>sleep |      | Wakeup<br>capability               |         | Wakeup<br>capability                   |

|                                                     |                        |                        | Down to<br>8 µA |                |      | ↓ μΑ (No<br>V <sub>DD</sub> =1.8 V |         | 28 µA (No<br>) V <sub>DD</sub> =1.8 V  |

| Consumption $V_{-} = 1.8 \text{ to } 3.6 \text{ V}$ | Down to<br>140 µA/MHz  | Down to<br>37 µA/MHz   |                 | Down to        |      | µA (with<br>V <sub>DD</sub> =1.8 V |         | 5 µA (with<br>) V <sub>DD</sub> =1.8 V |

| V <sub>DD</sub> =1.8 to 3.6 V<br>(Typ)              | (from Flash<br>memory) | (from Flash<br>memory) |                 | 4.5 µA         |      | ↓μΑ (No<br>V <sub>DD</sub> =3.0 V  |         | 29 µA (No<br>) V <sub>DD</sub> =3.0 V  |

|                                                     |                        |                        |                 |                |      | (with RTC)<br><sub>9D</sub> =3.0 V |         | 5 μΑ (with<br>) V <sub>DD</sub> =3.0 V |

1. Legend:

"Y" = Yes (enable). "O" = Optional can be enabled/disabled by software)

"-" = Not available

- Some peripherals with wakeup from Stop capability can request HSI to be enabled. In this case, HSI is woken up by the peripheral, and only feeds the peripheral which requested it. HSI is automatically put off when the peripheral does not need it anymore.

- 3. UART and LPUART reception is functional in Stop mode. It generates a wakeup interrupt on Start. To generate a wakeup on address match or received frame event, the LPUART can run on LSE clock while the UART has to wake up or keep running the HSI clock.

- 4. I2C address detection is functional in Stop mode. It generates a wakeup interrupt in case of address match. It will wake up the HSI during reception.

#### 3.2 Interconnect matrix

Several peripherals are directly interconnected. This allows autonomous communication between peripherals, thus saving CPU resources and power consumption. In addition, these hardware connections allow fast and predictable latency.

Depending on peripherals, these interconnections can operate in Run, Sleep, Low-power run, Low-power sleep and Stop modes.

| Interconnect<br>source | Interconnect destination Interconnect action R |                                                                   | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | Stop |  |

|------------------------|------------------------------------------------|-------------------------------------------------------------------|-----|-------|----------------------|------------------------|------|--|

| COMPx                  | TIM2,TIM21,<br>TIM22                           | Timer input channel,<br>trigger from analog<br>signals comparison | Y   | Y     | Y                    | Y                      | -    |  |

|                        | LPTIM                                          | Timer input channel,<br>trigger from analog<br>signals comparison | Y   | Y     | Y                    | Y                      | Y    |  |

| TIMx                   | TIMx                                           | Timer triggered by other timer                                    | Y   | Y     | Y                    | Y                      | -    |  |

Table 6. STM32L0xx peripherals interconnect matrix

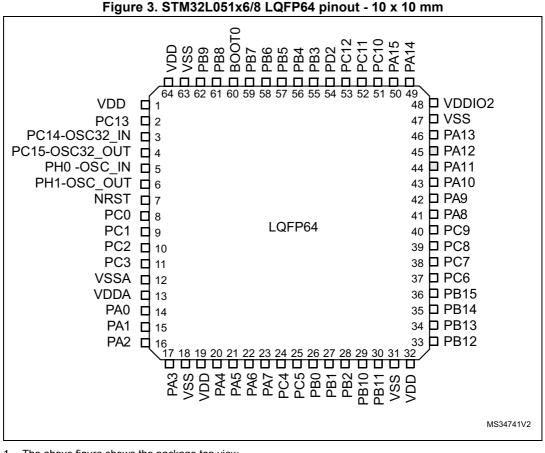

# 4 Pin descriptions

1. The above figure shows the package top view.

2. I/O supplied by VDDIO2.

|        |         | Pin Nu | umber                  |        |          |                                       |          |               |       |                                                       |                                                |  |  |

|--------|---------|--------|------------------------|--------|----------|---------------------------------------|----------|---------------|-------|-------------------------------------------------------|------------------------------------------------|--|--|

| LQFP64 | TFBGA64 | LQFP48 | WLCSP36 <sup>(1)</sup> | LQFP32 | UFQFPN32 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                   | Additional<br>functions                        |  |  |

| 5      | C1      | 5      | -                      | -      | -        | PH0-OSC_IN<br>(PH0)                   | I/O      | тс            | -     | -                                                     | OSC_IN                                         |  |  |

| 6      | D1      | 6      | -                      | -      | -        | PH1-<br>OSC_OUT<br>(PH1)              | I/O      | тс            | -     | -                                                     | OSC_OUT                                        |  |  |

| 7      | E1      | 7      | C6                     | 4      | 4        | NRST                                  | I/O      | RST           | -     | -                                                     | -                                              |  |  |

| 8      | E3      | -      | -                      | -      | -        | PC0                                   | I/O      | FT            | -     | LPTIM1_IN1,<br>EVENTOUT                               | ADC_IN10                                       |  |  |

| 9      | E2      | -      | -                      | -      | -        | PC1                                   | I/O      | FT            | -     | LPTIM1_OUT,<br>EVENTOUT                               | ADC_IN11                                       |  |  |

| 10     | F2      | -      | -                      | -      | -        | PC2                                   | I/O      | FT            | -     | LPTIM1_IN2,<br>SPI2_MISO/I2S2_M<br>CK                 | ADC_IN12                                       |  |  |

| 11     | -       | -      | -                      | -      | -        | PC3                                   | I/O      | FT            | -     | LPTIM1_ETR,<br>SPI2_MOSI/I2S2_SD                      | ADC_IN13                                       |  |  |

| 12     | F1      | 8      | -                      | -      | -        | VSSA                                  | S        |               | -     | -                                                     | -                                              |  |  |

| -      | G1      | -      | E6                     | -      | -        | VREF+                                 | S        |               | -     | -                                                     | -                                              |  |  |

| 13     | H1      | 9      | D5                     | 5      | 5        | VDDA                                  | S        |               | -     | -                                                     | -                                              |  |  |

| 14     | G2      | 10     | D4                     | 6      | 6        | PA0                                   | I/O      | тс            | -     | TIM2_CH1,<br>USART2_CTS,<br>TIM2_ETR,<br>COMP1_OUT    | COMP1_INM6,<br>ADC_IN0,<br>RTC_TAMP2/WKU<br>P1 |  |  |

| 15     | H2      | 11     | F6                     | 7      | 7        | PA1                                   | I/O      | FT            | -     | EVENTOUT,<br>TIM2_CH2,<br>USART2_RTS_DE,<br>TIM21_ETR | COMP1_INP,<br>ADC_IN1                          |  |  |

| 16     | F3      | 12     | E5                     | 8      | 8        | PA2                                   | I/O      | FT            | -     | TIM21_CH1,<br>TIM2_CH3,<br>USART2_TX,<br>COMP2_OUT    | COMP2_INM6,<br>ADC_IN2                         |  |  |

| 17     | G3      | 13     | F5                     | 9      | 9        | PA3                                   | I/O      | FT            | -     | TIM21_CH2,<br>TIM2_CH4,<br>USART2_RX                  | COMP2_INP,<br>ADC_IN3                          |  |  |

| 18     | C2      | -      | -                      | -      | -        | VSS                                   | S        |               | -     | -                                                     | -                                              |  |  |

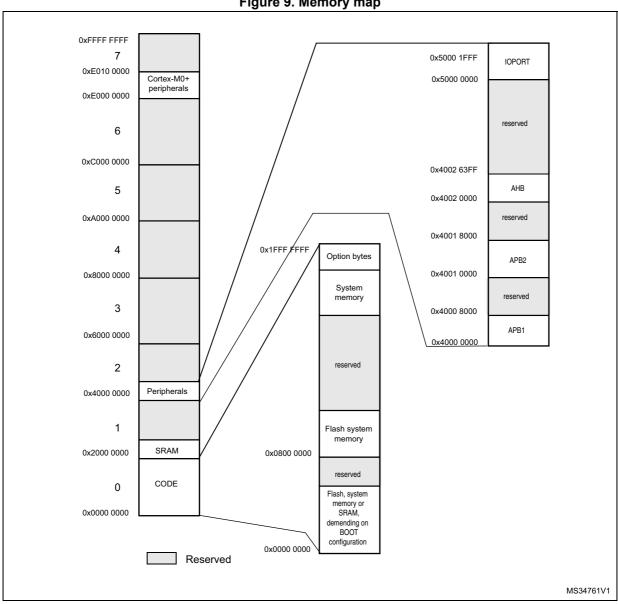

#### Memory mapping 5

Figure 9. Memory map

| Symbol            | Parameter          | Conditions                                | Min  | Тур  | Max  | Unit |

|-------------------|--------------------|-------------------------------------------|------|------|------|------|

| M                 | PVD threshold 6    | Falling edge                              | 2.97 | 3.05 | 3.09 | V    |

| V <sub>PVD6</sub> |                    | Rising edge                               | 3.08 | 3.15 | 3.20 | v    |

|                   |                    | BOR0 threshold                            | -    | 40   | -    |      |

| V <sub>hyst</sub> | Hysteresis voltage | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

Table 24. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

# 6.3.3 Embedded internal reference voltage

The parameters given in *Table 26* are based on characterization results, unless otherwise specified.

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

|                        | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

| Symbol                                   | Parameter                                                            | Conditions                                                                              | Min   | Тур   | Max   | Unit   |

|------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                           | – 40 °C < T <sub>J</sub> < +125 °C                                                      | 1.202 | 1.224 | 1.242 | V      |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                      | -                                                                                       | -     | 2     | 3     | ms     |

| V <sub>VREF_MEAS</sub>                   | $V_{DDA}$ and $V_{REF+}$ voltage during $V_{REFINT}$ factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V      |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured $V_{REFINT}$ value <sup>(3)</sup>       | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV     |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                              | –40 °C < T <sub>J</sub> < +125 °C                                                       | -     | 25    | 100   | ppm/°C |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                  | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm    |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                  | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V  |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage  | -                                                                                       | 5     | 10    | -     | μs     |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                     | -                                                                                       | -     | -     | 10    | μs     |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                      | -                                                                                       | -     | 13.5  | 25    | μA     |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                               | -                                                                                       | -     | -     | 1     | μA     |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                 | -                                                                                       | -     | -     | 50    | pF     |

# Table 26. Embedded internal reference voltage<sup>(1)</sup>

| Symbol                  | Parameter               | Conditions                                                                                                       |                                                      | f <sub>HCLK</sub> | Тур  | Max <sup>(1)</sup> | Unit                |

|-------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------|------|--------------------|---------------------|

|                         |                         |                                                                                                                  | Range 3,                                             | 1 MHz             | 43.5 | 90                 |                     |

|                         |                         |                                                                                                                  | V <sub>CORE</sub> =1.2 V,                            | 2 MHz             | 72   | 120                |                     |

|                         |                         |                                                                                                                  | VOS[1:0]=11                                          | 4 MHz             | 130  | 180                |                     |

|                         |                         | f <sub>HSE</sub> = f <sub>HCLK</sub> up to                                                                       | Range 2,                                             | 4 MHz             | 160  | 210                |                     |

|                         |                         | 16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above                                                | V <sub>CORE</sub> =1.5 V,                            | 8 MHz             | 305  | 370                |                     |

|                         |                         | 16 MHz (PLL ON) <sup>(2)</sup>                                                                                   | VOS[1:0]=10                                          | 16 MHz            | 590  | 710                |                     |

|                         |                         |                                                                                                                  | Range 1,                                             | 8 MHz             | 370  | 430                |                     |

|                         | Supply current          |                                                                                                                  | V <sub>CORE</sub> =1.8 V,                            | 16 MHz            | 715  | 860                |                     |

|                         | in Sleep<br>mode, Flash |                                                                                                                  | VOS[1:0]=01                                          | 32 MHz            | 1650 | 1900               |                     |

|                         | OFF                     |                                                                                                                  | Range 3,                                             | 65 kHz            | 18   | 65                 |                     |

|                         |                         | MSI clock                                                                                                        | V <sub>CORE</sub> =1.2 V,                            | 524 kHz           | 31.5 | 75                 |                     |

|                         |                         |                                                                                                                  | VOS[1:0]=11                                          | 4.2 MHz           | 140  | 210                |                     |

|                         |                         | HSI16 clock source<br>(16 MHz)                                                                                   | Range 2,<br>V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10 | 16 MHz            | 665  | 830                |                     |

|                         |                         |                                                                                                                  | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 32 MHz            | 1750 | 2100               |                     |

| I <sub>DD</sub> (Sleep) |                         | $f_{HSE} = f_{HCLK}$ up to<br>16 MHz included,<br>$f_{HSE} = f_{HCLK}/2$ above<br>16 MHz (PLL ON) <sup>(2)</sup> | Range 3,<br>V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11 | 1 MHz             | 57.5 | 130                | - μΑ<br>-<br>-<br>- |

|                         |                         |                                                                                                                  |                                                      | 2 MHz             | 84   | 170                |                     |

|                         |                         |                                                                                                                  |                                                      | 4 MHz             | 150  | 280                |                     |

|                         |                         |                                                                                                                  | Range 2,<br><sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10   | 4 MHz             | 170  | 310                |                     |

|                         |                         |                                                                                                                  |                                                      | 8 MHz             | 315  | 420                |                     |

|                         |                         |                                                                                                                  |                                                      | 16 MHz            | 605  | 770                |                     |

|                         |                         |                                                                                                                  | Range 1,                                             | 8 MHz             | 380  | 460                |                     |

|                         | Supply current          |                                                                                                                  | V <sub>CORE</sub> =1.8 V,                            | 16 MHz            | 730  | 950                |                     |

|                         | in Sleep<br>mode, Flash |                                                                                                                  | VOS[1:0]=01                                          | 32 MHz            | 1650 | 2400               |                     |

|                         | ON                      |                                                                                                                  | Range 3,                                             | 65 kHz            | 29.5 | 110                |                     |

|                         |                         | MSI clock                                                                                                        | V <sub>CORE</sub> =1.2 V,                            | 524 kHz           | 44.5 | 130                |                     |

|                         |                         |                                                                                                                  | VOS[1:0]=11                                          | 4.2 MHz           | 150  | 270                |                     |

|                         |                         | HSI16 clock source                                                                                               | Range 2,<br>V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10 | 16 MHz            | 680  | 950                |                     |

|                         |                         | (16 MHz)                                                                                                         | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 32 MHz            | 1750 | 2100               |                     |

Table 31. Current consumption in Sleep mode

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

#### 2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol          | Parameter             |                                            | Conditions                                         |                                            | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------|-----------------------|--------------------------------------------|----------------------------------------------------|--------------------------------------------|------|--------------------|------|

|                 |                       |                                            |                                                    | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 8.5  | 10                 |      |

|                 |                       |                                            | MSI clock = 65 kHz,                                | T <sub>A</sub> = 85 °C                     | 11.5 | 48                 |      |

|                 |                       |                                            | f <sub>HCLK</sub> = 32 kHz                         | T <sub>A</sub> = 105 °C                    | 15.5 | 53                 |      |

|                 |                       |                                            |                                                    | T <sub>A</sub> = 125 °C                    | 27.5 | 130                |      |

|                 |                       | All peripherals                            |                                                    | $T_A = -40 \text{ °C to } 25 \text{ °C}$   | 10   | 15                 |      |

|                 |                       | OFF, code<br>executed from                 | MSI clock= 65 kHz,                                 | T <sub>A</sub> = 85 °C                     | 15.5 | 50                 |      |

|                 |                       | RAM, Flash                                 | f <sub>HCLK</sub> = 65 kHz                         | T <sub>A</sub> = 105 °C                    | 19.5 | 54                 |      |

|                 |                       | switched off,<br>V <sub>DD</sub> from 1.65 |                                                    | T <sub>A</sub> = 125 °C                    | 31.5 | 130                |      |

|                 |                       | to 3.6 V                                   |                                                    | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 20   | 25                 |      |

|                 |                       |                                            |                                                    | T <sub>A</sub> = 55 °C                     | 23   | 50                 | - μΑ |

|                 |                       |                                            | MSI clock= 131 kHz,<br>f <sub>HCLK</sub> = 131 kHz | T <sub>A</sub> = 85 °C                     | 25.5 | 55                 |      |

|                 | Supply                |                                            |                                                    | T <sub>A</sub> = 105 °C                    | 29.5 | 64                 |      |

| I <sub>DD</sub> | current in            |                                            |                                                    | T <sub>A</sub> = 125 °C                    | 40   | 140                |      |

| (LP Run)        | Low-power<br>run mode |                                            | MSI clock= 65 kHz,<br>f <sub>HCLK</sub> = 32 kHz   | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 22   | 28                 |      |

|                 | Turi mode             |                                            |                                                    | T <sub>A</sub> = 85 °C                     | 26   | 68                 |      |

|                 |                       |                                            |                                                    | T <sub>A</sub> = 105 °C                    | 31   | 75                 |      |

|                 |                       |                                            |                                                    | T <sub>A</sub> = 125 °C                    | 44   | 95                 |      |

|                 |                       | All peripherals                            |                                                    | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 27.5 | 33                 |      |

|                 |                       | OFF, code                                  | MSI clock = 65 kHz,                                | T <sub>A</sub> = 85 °C                     | 31.5 | 73                 |      |

|                 |                       | executed from<br>Flash, V <sub>DD</sub>    | f <sub>HCLK</sub> = 65 kHz                         | T <sub>A</sub> = 105 °C                    | 36.5 | 80                 | 1    |

|                 |                       | from 1.65 V to                             |                                                    | T <sub>A</sub> = 125 °C                    | 49   | 100                |      |

|                 |                       | 3.6 V                                      |                                                    | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 39   | 46                 |      |

|                 |                       |                                            | MSI clock =                                        | T <sub>A</sub> = 55 °C                     | 41   | 80                 | 1    |

|                 |                       |                                            | 131 kHz,                                           | T <sub>A</sub> = 85 °C                     | 44   | 86                 |      |

|                 |                       |                                            | f <sub>HCLK</sub> = 131 kHz                        | T <sub>A</sub> = 105 °C                    | 49.5 | 100                |      |

|                 |                       |                                            |                                                    | T <sub>A</sub> = 125 °C                    | 60   | 120                |      |

#### Table 32. Current consumption in Low-power run mode

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked OFF

- with only one peripheral clocked on

## Table 37. Peripheral current consumption in Run or Sleep mode<sup>(1)</sup>

|                     |                     | Typical consumption, $V_{DD}$ = 3.0 V, T <sub>A</sub> = 25 °C |                                                       |                                                       |                               |                                |  |  |

|---------------------|---------------------|---------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------|--------------------------------|--|--|

| Peripheral          |                     | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01         | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                           |  |  |

|                     | I2C1                | 11                                                            | 9.5                                                   | 7.5                                                   | 9                             |                                |  |  |

|                     | I2C2                | 4                                                             | 3.5                                                   | 3                                                     | 2.5                           |                                |  |  |

|                     | LPTIM1              | 10                                                            | 8.5                                                   | 6.5                                                   | 8                             |                                |  |  |

|                     | LPUART1             | 8                                                             | 6.5                                                   | 5.5                                                   | 6                             |                                |  |  |

| APB1                | SPI2                | 9                                                             | 4.5                                                   | 3.5                                                   | 4                             | µA/MHz<br>(f <sub>HCLK</sub> ) |  |  |

|                     | USART2              | 14.5                                                          | 12                                                    | 9.5                                                   | 11                            | (HOLK)                         |  |  |

|                     | TIM2                | 10.5                                                          | 8.5                                                   | 7                                                     | 9                             |                                |  |  |

|                     | TIM6                | 3.5                                                           | 3                                                     | 2.5                                                   | 2                             |                                |  |  |

|                     | WWDG                | 3                                                             | 2                                                     | 2                                                     | 2                             |                                |  |  |

|                     | ADC1 <sup>(2)</sup> | 5.5                                                           | 5                                                     | 3.5                                                   | 4                             |                                |  |  |

|                     | SPI1                | 4                                                             | 3                                                     | 3                                                     | 2.5                           |                                |  |  |

|                     | USART1              | 14.5                                                          | 11.5                                                  | 9.5                                                   | 12                            |                                |  |  |

| APB2                | TIM21               | 7.5                                                           | 6                                                     | 5                                                     | 5.5                           | µA/MHz                         |  |  |

| AFDZ                | TIM22               | 7                                                             | 6                                                     | 5                                                     | 6                             | (f <sub>HCLK</sub> )           |  |  |

|                     | FIREWALL            | 1.5                                                           | 1                                                     | 1                                                     | 0.5                           |                                |  |  |

|                     | DBGMCU              | 1.5                                                           | 1                                                     | 1                                                     | 0.5                           |                                |  |  |

|                     | SYSCFG              | 2.5                                                           | 2                                                     | 2                                                     | 1.5                           |                                |  |  |

|                     | GPIOA               | 3.5                                                           | 3                                                     | 2.5                                                   | 2.5                           |                                |  |  |

| Cortex-<br>M0+ core | GPIOB               | 3.5                                                           | 2.5                                                   | 2                                                     | 2.5                           | µA/MHz                         |  |  |

| I/O port            | GPIOC               | 8.5                                                           | 6.5                                                   | 5.5                                                   | 7                             | (f <sub>HCLK</sub> )           |  |  |

|                     | GPIOD               | 1                                                             | 0.5                                                   | 0.5                                                   | 0.5                           |                                |  |  |

|                     | CRC                 | 1.5                                                           | 1                                                     | 1                                                     | 1                             |                                |  |  |

| AHB                 | FLASH               | 0 <sup>(3)</sup>                                              | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>              | µA/MHz<br>(f <sub>HCLK</sub> ) |  |  |

|                     | DMA1                | 10                                                            | 8                                                     | 6.5                                                   | 8.5                           | VIICLK/                        |  |  |

## 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 23*.

| Symbol               | Parameter                                                                     | Conditions                                                        | Тур | Max | Unit               |  |

|----------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-----|--------------------|--|

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode                                                        | f <sub>HCLK</sub> = 32 MHz                                        | 7   | 8   |                    |  |

| +                    | Wakeup from Low-power sleep mode,                                             | f <sub>HCLK</sub> = 262 kHz<br>Flash memory enabled               | 7 8 |     | Number<br>of clock |  |

| twusleep_lp          | f <sub>HCLK</sub> = 262 kHz                                                   | f <sub>HCLK</sub> = 262 kHz<br>Flash memory switched OFF          | 9   | 10  | cycles             |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 5.0 | 8   |                    |  |

|                      | Wakeup from Stop mode, regulator in Run mode                                  | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |                    |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.0 | 11  |                    |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 1 | 5.0 | 8   |                    |  |

|                      | Wakeup from Stop mode, regulator in low-<br>power mode                        | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 2 | 5.0 | 8   |                    |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3 | 5.0 | 8   |                    |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 7.3 | 13  |                    |  |

| t <sub>WUSTOP</sub>  |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                   | 13  | 23  | μs                 |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                    | 28  | 38  |                    |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                    | 51  | 65  |                    |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                    | 100 | 120 |                    |  |

|                      |                                                                               | f <sub>HCLK</sub> = MSI = 65 kHz                                  | 190 | 260 |                    |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |                    |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.0 | 11  |                    |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7   |                    |  |

|                      | Wakeup from Stop mode, regulator in low-<br>power mode, code running from RAM | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 7.9 | 10  |                    |  |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 4.7 | 8   |                    |  |

| turiotoci            | Wakeup from Standby mode, FWU bit = 1                                         | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 65  | 130 | μs                 |  |

| t <sub>WUSTDBY</sub> | Wakeup from Standby mode, FWU bit = 0                                         | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 2.2 | 3   | ms                 |  |

| Table 39. | Low-power | mode | wakeup | timinas |

|-----------|-----------|------|--------|---------|

|           |           |      |        |         |

DocID025938 Rev 7

# 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 51*. They are based on the EMS levels and classes defined in application note AN1709.

| s | Symbol | Parameter                                                                                                                         | Conditions                                                                                           | Level/<br>Class |

|---|--------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------|

| v | FESD   | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP64, $T_A$ = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2 | 3B              |

| V | EFTB   | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3$ V, LQFP64, $T_A = +25$ °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4 | 4A              |

#### Table 51. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

## 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence oscillator frequency deviation).

The test results are given in the Table 55.

|                  |                                                                     | Functional s       |                    |      |  |

|------------------|---------------------------------------------------------------------|--------------------|--------------------|------|--|

| Symbol           | Description                                                         | Negative injection | Positive injection | Unit |  |

| I <sub>INJ</sub> | Injected current on BOOT0                                           | -0                 | NA                 |      |  |

|                  | Injected current on PA0, PA4, PA5, PA11,<br>PA12, PC15, PH0 and PH1 | -5                 | 0                  | mA   |  |

|                  | Injected current on any other FT, FTf pins                          | -5 <sup>(1)</sup>  | NA                 |      |  |

|                  | Injected current on any other pins                                  | -5 <sup>(1)</sup>  | +5                 |      |  |

#### Table 55. I/O current injection susceptibility

1. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 23*. All I/Os are CMOS and TTL compliant.

| Symbol                               | Parameter                                | Conditions                                                                                 | Min                   | Max  | Unit |

|--------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup> ,<br>I <sub>IO</sub> = +8 mA                                      | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)</sup>       | Output high level voltage for an I/O pin | $1_{O} = +0.01 \text{ M/A}$<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                   | V <sub>DD</sub> -0.4  | -    |      |

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin  | TTL port <sup>(2)</sup> ,<br>$I_{IO}$ =+ 8 mA<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin | TTL port <sup>(2)</sup> ,<br>$I_{IO}$ = -6 mA<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V | 2.4                   | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin  | $I_{IO}$ = +15 mA<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                             | -                     | 1.3  | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin | I <sub>IO</sub> = -15 mA<br>2.7 V ≤V <sub>DD</sub> ≤ 3.6 V                                 | V <sub>DD</sub> -1.3  | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +4 mA<br>1.65 V ≤V <sub>DD</sub> < 3.6 V                                 | -                     | 0.45 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin | $I_{IO}$ = -4 mA<br>1.65 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                             | V <sub>DD</sub> -0.45 | -    |      |

| V <sub>OLFM+</sub> <sup>(1)(4)</sup> | Output low level voltage for an FTf      | $I_{IO} = 20 \text{ mA}$ $2.7 \text{ V} \leq V_{DD} \leq 3.6 \text{ V}$                    | -                     | 0.4  |      |

| VOLFM+                               | I/O pin in Fm+ mode                      | $I_{IO}$ = 10 mA<br>1.65 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                             | -                     | 0.4  |      |

| Table 57. | Output voltage | characteristics |

|-----------|----------------|-----------------|

|-----------|----------------|-----------------|

The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 21*. The sum of the currents sunk by all the I/Os (I/O ports and control pins) must always be respected and must not exceed ΣI<sub>IO(PIN)</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 21. The sum of the currents sourced by all the I/Os (I/O ports and control pins) must always be respected and must not exceed  $\Sigma I_{IO(PIN)}$ .

4. Guaranteed by characterization results.

| Symbol                                | Parameter                          | Conditions                                            | Min                                                                        | Тур  | Max                                               | Unit                       |

|---------------------------------------|------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|------|---------------------------------------------------|----------------------------|

| R <sub>AIN</sub> <sup>(3)</sup>       | External input impedance           | See <i>Equation 1</i> and <i>Table 61</i> for details | -                                                                          | -    | 50                                                | kΩ                         |

| R <sub>ADC</sub> <sup>(3)(4)</sup>    | Sampling switch resistance         | -                                                     | -                                                                          | -    | 1                                                 | kΩ                         |

| C <sub>ADC</sub> <sup>(3)</sup>       | Internal sample and hold capacitor | -                                                     | -                                                                          | -    | 8                                                 | pF                         |

| t <sub>CAL</sub> <sup>(3)(5)</sup>    | Calibration time                   | f <sub>ADC</sub> = 16 MHz                             |                                                                            | 5.2  |                                                   | μs                         |

| <sup>L</sup> CAL CAL                  |                                    | -                                                     |                                                                            | 83   |                                                   | 1/f <sub>ADC</sub>         |

|                                       |                                    | ADC clock = HSI16                                     | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles                          | -    | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

| W <sub>LATENCY</sub> <sup>(6)</sup>   | ADC_DR register write<br>latency   | ADC clock = PCLK/2                                    | -                                                                          | 4.5  | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                       |                                    | ADC clock = PCLK/4                                    | -                                                                          | 8.5  | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                       |                                    | $f_{ADC} = f_{PCLK}/2 = 16 \text{ MHz}$               | 0.266                                                                      |      |                                                   | μs                         |

|                                       | Trigger conversion latency         | $f_{ADC} = f_{PCLK}/2$                                | 8.5                                                                        |      | 1/f <sub>PCLK</sub>                               |                            |

| t <sub>latr</sub> (3)                 |                                    | $f_{ADC} = f_{PCLK}/4 = 8 \text{ MHz}$                | 0.516                                                                      |      | μs                                                |                            |

|                                       |                                    | $f_{ADC} = f_{PCLK}/4$                                |                                                                            | 16.5 |                                                   | 1/f <sub>PCLK</sub>        |

|                                       |                                    | $f_{ADC} = f_{HSI16} = 16 \text{ MHz}$                | 0.252                                                                      | -    | 0.260                                             | μs                         |

| Jitter <sub>ADC</sub>                 | ADC jitter on trigger conversion   | f <sub>ADC</sub> = f <sub>HSI16</sub>                 | -                                                                          | 1    | -                                                 | 1/f <sub>HSI16</sub>       |

| ts <sup>(3)</sup>                     | Sampling time                      | f <sub>ADC</sub> = 16 MHz                             | 0.093                                                                      | -    | 10.03                                             | μs                         |

| ıs' '                                 |                                    | -                                                     | 1.5                                                                        | -    | 160.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>UP_LDO</sub> <sup>(3)(5)</sup> | Internal LDO power-up time         | -                                                     | -                                                                          | -    | 10                                                | μs                         |

| t <sub>STAB</sub> <sup>(3)(5)</sup>   | ADC stabilization time             | -                                                     |                                                                            | 14   |                                                   | 1/f <sub>ADC</sub>         |

| t <sub>ConV</sub> <sup>(3)</sup>      | Total conversion time              | f <sub>ADC</sub> = 16 MHz,<br>12-bit resolution       | 0.875                                                                      | -    | 10.81                                             | μs                         |

| <sup>L</sup> ConV`´                   | (including sampling time)          | 12-bit resolution                                     | 14 to 173 (t <sub>S</sub> for sampling +12.5 for successive approximation) |      | 1/f <sub>ADC</sub>                                |                            |

Table 60. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value can be decreased in specific temperature conditions. Refer to Table 61: RAIN max for fADC = 16 MHz.

2. A current consumption proportional to the APB clock frequency has to be added (see *Table 37: Peripheral current consumption in Run or Sleep mode*).

3. Guaranteed by design.

Standard channels have an extra protection resistance which depends on supply voltage. Refer to Table 61: RAIN max for fADC = 16 MHz.

5. This parameter only includes the ADC timing. It does not take into account register access latency.

6. This parameter specifies the latency to transfer the conversion result into the ADC\_DR register. EOC bit is set to indicate the conversion is complete and has the same latency.

# 6.3.17 Comparators

| Symbol                   | Parameter                                                      | Conditions                                                                                                                                                                                       | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |

|--------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|

| $V_{DDA}$                | Analog supply voltage                                          | -                                                                                                                                                                                                | 1.65               |     | 3.6                | V         |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                        | -                                                                                                                                                                                                | -                  | 400 | -                  | - kΩ      |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                         | -                                                                                                                                                                                                | -                  | 10  | -                  | - K32     |

| V <sub>IN</sub>          | Comparator 1 input voltage range                               | -                                                                                                                                                                                                | 0.6                | -   | V <sub>DDA</sub>   | V         |

| t <sub>START</sub>       | Comparator startup time                                        | -                                                                                                                                                                                                | -                  | 7   | 10                 | 110       |

| td                       | Propagation delay <sup>(2)</sup>                               | -                                                                                                                                                                                                | -                  | 3   | 10                 | - μs      |

| Voffset                  | Comparator offset                                              | -                                                                                                                                                                                                | -                  | ±3  | ±10                | mV        |

| d <sub>Voffset</sub> /dt | Comparator offset variation in worst voltage stress conditions | $\label{eq:VDDA} \begin{split} V_{DDA} &= 3.6 \text{ V},  \text{V}_{\text{IN+}} = 0 \text{ V}, \\ V_{\text{IN-}} &= V_{\text{REFINT}},  \text{T}_{\text{A}} = 25 \ ^{\circ}\text{C} \end{split}$ | 0                  | 1.5 | 10                 | mV/1000 h |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                             | -                                                                                                                                                                                                | -                  | 160 | 260                | nA        |

1. Guaranteed by characterization.