Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | -                                                           |

| Number of Logic Elements/Cells | 6000                                                        |

| Total RAM Bits                 | 184320                                                      |

| Number of I/O                  | 100                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 0.95V ~ 1.05V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 196-LBGA, CSPBGA                                            |

| Supplier Device Package        | 196-CSBGA (15x15)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc7s6-2ftgb196c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 3: DC Characteristics Over Recommended Operating Conditions

| Symbol                              | Description                                                                                             | Min  | Typ <sup>(1)</sup> | Max | Units |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|------|--------------------|-----|-------|

| V <sub>DRINT</sub>                  | Data retention $V_{\text{CCINT}}$ voltage (below which configuration data might be lost).               | 0.75 | _                  | -   | V     |

| V <sub>DRI</sub>                    | Data retention $V_{\text{CCAUX}}$ voltage (below which configuration data might be lost).               | 1.5  | _                  | _   | V     |

| I <sub>REF</sub>                    | V <sub>REF</sub> leakage current per pin.                                                               | _    | _                  | 15  | μΑ    |

| IL                                  | Input or output leakage current per pin (sample-tested).                                                | _    | _                  | 15  | μA    |

| C <sub>IN</sub> <sup>(2)</sup>      | Die input capacitance at the pad.                                                                       | _    | _                  | 8   | pF    |

|                                     | Pad pull-up (when selected) at $V_{IN} = 0V$ , $V_{CCO} = 3.3V$ .                                       | 90   | _                  | 330 | μΑ    |

|                                     | Pad pull-up (when selected) at $V_{IN} = 0V$ , $V_{CCO} = 2.5V$ .                                       | 68   | _                  | 250 | μΑ    |

| I <sub>RPU</sub>                    | Pad pull-up (when selected) at $V_{IN} = 0V$ , $V_{CCO} = 1.8V$ .                                       | 34   | _                  | 220 | μΑ    |

|                                     | Pad pull-up (when selected) at $V_{IN} = 0V$ , $V_{CCO} = 1.5V$ .                                       | 23   | _                  | 150 | μΑ    |

|                                     | Pad pull-up (when selected) at $V_{IN} = 0V$ , $V_{CCO} = 1.2V$ .                                       | 12   | _                  | 120 | μΑ    |

| I <sub>RPD</sub>                    | Pad pull-down (when selected) at V <sub>IN</sub> = 3.3V.                                                | 68   | _                  | 330 | μΑ    |

| I <sub>CCADC</sub>                  | Analog supply current, analog circuits in powered up state.                                             | _    | _                  | 25  | mA    |

| I <sub>BATT</sub> (3)               | Battery supply current.                                                                                 | _    | _                  | 150 | nA    |

|                                     | Thevenin equivalent resistance of programmable input termination to $V_{\rm CCO}/2$ (UNTUNED_SPLIT_40). | 28   | 40                 | 55  | Ω     |

| R <sub>IN_TERM</sub> <sup>(4)</sup> | Thevenin equivalent resistance of programmable input termination to $V_{\rm CCO}/2$ (UNTUNED_SPLIT_50). | 35   | 50                 | 65  | Ω     |

|                                     | Thevenin equivalent resistance of programmable input termination to $V_{\rm CCO}/2$ (UNTUNED_SPLIT_60). | 44   | 60                 | 83  | Ω     |

| n                                   | Temperature diode ideality factor.                                                                      | _    | 1.010              | -   | _     |

| r                                   | Temperature diode series resistance.                                                                    | _    | 2                  | _   | Ω     |

- 1. Typical values are specified at nominal voltage, 25°C.

- 2. This measurement represents the die capacitance at the pad, not including the package.

- 3. Maximum value specified for worst case process at 25°C.

- 4. Termination resistance to a V<sub>CCO</sub>/2 level.

Table 4: V<sub>IN</sub> Maximum Allowed AC Voltage Overshoot and Undershoot for HR I/O Banks<sup>(1)(2)</sup>

| AC Voltage Overshoot    | % of UI at -40°C to 125°C | AC Voltage Undershoot | % of UI at -40°C to 125°C |

|-------------------------|---------------------------|-----------------------|---------------------------|

|                         |                           | -0.40                 | 100                       |

| V . 0.55                | 100                       | -0.45                 | 61.7                      |

| V <sub>CCO</sub> + 0.55 | 100                       | -0.50                 | 25.8                      |

|                         |                           | -0.55                 | 11.0                      |

| V <sub>CCO</sub> + 0.60 | 46.6                      | -0.60                 | 4.77                      |

| V <sub>CCO</sub> + 0.65 | 21.2                      | -0.65                 | 2.10                      |

| V <sub>CCO</sub> + 0.70 | 9.75                      | -0.70                 | 0.94                      |

| V <sub>CCO</sub> + 0.75 | 4.55                      | -0.75                 | 0.43                      |

| V <sub>CCO</sub> + 0.80 | 2.15                      | -0.80                 | 0.20                      |

| V <sub>CCO</sub> + 0.85 | 1.02                      | -0.85                 | 0.09                      |

| V <sub>CCO</sub> + 0.90 | 0.49                      | -0.90                 | 0.04                      |

| V <sub>CCO</sub> + 0.95 | 0.24                      | -0.95                 | 0.02                      |

Table 5: Typical Quiescent Supply Current(1)(2)(3)

|         |                                              |         | Speed Grade |     |      |     |     |       |       |

|---------|----------------------------------------------|---------|-------------|-----|------|-----|-----|-------|-------|

| Symbol  | Description                                  | Device  |             |     | 1.0V |     |     | 0.95V | Units |

|         |                                              |         | -2C         | -21 | -1C  | -11 | -1Q | -1LI  |       |

|         |                                              | XC7S6   | 36          | 36  | 36   | 36  | 36  | 32    | mA    |

|         |                                              | XC7S15  | 36          | 36  | 36   | 36  | 36  | 32    | mA    |

|         |                                              | XC7S25  | 48          | 48  | 48   | 48  | 48  | 43    | mA    |

|         |                                              | XC7S50  | 95          | 95  | 95   | 95  | 95  | 59    | mA    |

|         |                                              | XC7S75  | 148         | 148 | 148  | 148 | 148 | 134   | mA    |

|         | Quiescent V supply current                   | XC7S100 | 148         | 148 | 148  | 148 | 148 | 134   | mA    |

| ICCINTQ | Quiescent V <sub>CCINT</sub> supply current. | XA7S6   | N/A         | 36  | N/A  | 36  | 36  | N/A   | mA    |

|         |                                              | XA7S15  | N/A         | 36  | N/A  | 36  | 36  | N/A   | mA    |

|         |                                              | XA7S25  | N/A         | 48  | N/A  | 48  | 48  | N/A   | mA    |

|         |                                              | XA7S50  | N/A         | 95  | N/A  | 95  | 95  | N/A   | mA    |

|         |                                              | XA7S75  | N/A         | 148 | N/A  | 148 | 148 | N/A   | mA    |

|         |                                              | XA7S100 | N/A         | 148 | N/A  | 148 | 148 | N/A   | mA    |

<sup>1.</sup> A total of 200 mA per bank should not be exceeded.

<sup>2.</sup> The peak voltage of the overshoot or undershoot, and the duration above V<sub>CCO</sub> + 0.20V or below GND – 0.20V, must not exceed the values in this table.

## **DC Input and Output Levels**

Values for  $V_{IL}$  and  $V_{IH}$  are recommended input voltages. Values for  $I_{OL}$  and  $I_{OH}$  are guaranteed over the recommended operating conditions at the  $V_{OL}$  and  $V_{OH}$  test points. Only selected standards are tested. These are chosen to ensure that all standards meet their specifications. The selected standards are tested at a minimum  $V_{CCO}$  with the respective  $V_{OL}$  and  $V_{OH}$  voltage levels shown. Other standards are sample tested.

Table 8: SelectIO DC Input and Output Levels(1)(2)(3)

| I/O Standard |        | V <sub>IL</sub>          | V                        | V <sub>IH</sub>          |                             | V <sub>OH</sub>          | I <sub>OL</sub> | I <sub>OH</sub> |

|--------------|--------|--------------------------|--------------------------|--------------------------|-----------------------------|--------------------------|-----------------|-----------------|

| i/O Standard | V, Min | V, Max                   | V, Min                   | V, Max                   | V, Max                      | V, Min                   | mA, Max         | mA, Min         |

| HSTL_I       | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | $V_{CCO} + 0.300$        | 0.400                       | V <sub>CCO</sub> - 0.400 | 8.00            | -8.00           |

| HSTL_I_18    | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | V <sub>CCO</sub> + 0.300 | 0.400                       | V <sub>CCO</sub> - 0.400 | 8.00            | -8.00           |

| HSTL_II      | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | $V_{CCO} + 0.300$        | 0.400                       | V <sub>CCO</sub> - 0.400 | 16.00           | -16.00          |

| HSTL_II_18   | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | $V_{CCO} + 0.300$        | 0.400                       | V <sub>CCO</sub> - 0.400 | 16.00           | -16.00          |

| HSUL_12      | -0.300 | V <sub>REF</sub> – 0.130 | V <sub>REF</sub> + 0.130 | $V_{CCO} + 0.300$        | 20% V <sub>CCO</sub>        | 80% V <sub>CCO</sub>     | 0.10            | -0.10           |

| LVCMOS12     | -0.300 | 35% V <sub>CCO</sub>     | 65% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.300 | 0.400                       | V <sub>CCO</sub> - 0.400 | Note 4          | Note 4          |

| LVCMOS15     | -0.300 | 35% V <sub>CCO</sub>     | 65% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.300 | 25% V <sub>CCO</sub>        | 75% V <sub>CCO</sub>     | Note 5          | Note 5          |

| LVCMOS18     | -0.300 | 35% V <sub>CCO</sub>     | 65% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.300 | 0.450                       | V <sub>CCO</sub> - 0.450 | Note 6          | Note 6          |

| LVCMOS25     | -0.300 | 0.7                      | 1.700                    | V <sub>CCO</sub> + 0.300 | 0.400                       | V <sub>CCO</sub> - 0.400 | Note 5          | Note 5          |

| LVCMOS33     | -0.300 | 0.8                      | 2.000                    | 3.450                    | 0.400                       | V <sub>CCO</sub> - 0.400 | Note 5          | Note 5          |

| LVTTL        | -0.300 | 0.8                      | 2.000                    | 3.450                    | 0.400                       | 2.400                    | Note 6          | Note 6          |

| MOBILE_DDR   | -0.300 | 20% V <sub>CCO</sub>     | 80% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.300 | 10% V <sub>CCO</sub>        | 90% V <sub>CCO</sub>     | 0.10            | -0.10           |

| PCI33_3      | -0.400 | 30% V <sub>CCO</sub>     | 50% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.500 | 10% V <sub>CCO</sub>        | 90% V <sub>CCO</sub>     | 1.50            | -0.50           |

| SSTL135      | -0.300 | V <sub>REF</sub> - 0.090 | V <sub>REF</sub> + 0.090 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2 – 0.150 | $V_{CCO}/2 + 0.150$      | 13.00           | -13.00          |

| SSTL135_R    | -0.300 | V <sub>REF</sub> - 0.090 | V <sub>REF</sub> + 0.090 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2 – 0.150 | $V_{CCO}/2 + 0.150$      | 8.90            | -8.90           |

| SSTL15       | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2 – 0.175 | $V_{CCO}/2 + 0.175$      | 13.00           | -13.00          |

| SSTL15_R     | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2 – 0.175 | $V_{CCO}/2 + 0.175$      | 8.90            | -8.90           |

| SSTL18_I     | -0.300 | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2 - 0.470 | $V_{CCO}/2 + 0.470$      | 8.00            | -8.00           |

| SSTL18_II    | -0.300 | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | $V_{CCO} + 0.300$        | V <sub>CCO</sub> /2 - 0.600 | $V_{CCO}/2 + 0.600$      | 13.40           | -13.40          |

- Tested according to relevant specifications.

- 2. 3.3V and 2.5V standards are only supported in HR I/O banks.

- 3. For detailed interface specific DC voltage levels, see the 7 Series FPGAs SelectIO Resources User Guide (UG471) [Ref 3].

- 4. Supported drive strengths of 4, 8, or 12 mA in HR I/O banks.

- 5. Supported drive strengths of 4, 8, 12, or 16 mA in HR I/O banks.

- 6. Supported drive strengths of 4, 8, 12, 16, or 24 mA in HR I/O banks.

# **AC Switching Characteristics**

All values represented in this data sheet are based on the speed specifications from the Vivado® Design Suite as outlined in Table 12.

Table 12: Speed Specification Version By Device

| 2018.2.1 | Device                                         |

|----------|------------------------------------------------|

| 1.23     | XC7S6, XC7S15, XC7S25, XC7S50, XC7S75, XC7S100 |

| 1.16     | XA7S6, XA7S15, XA7S25, XA7S50, XA7S75, XA7S100 |

Switching characteristics are specified on a per-speed-grade basis and can be designated as Advance, Preliminary, or Production. Each designation is defined as follows.

### **Advance Product Specification**

These specifications are based on simulations only and are typically available soon after device design specifications are frozen. Although speed grades with this designation are considered relatively stable and conservative, some under-reporting might still occur.

### **Preliminary Product Specification**

These specifications are based on complete ES (engineering sample) silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting delays is greatly reduced as compared to Advance data.

### **Production Product Specification**

These specifications are released once enough production silicon of a particular device family member has been characterized to provide full correlation between specifications and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

## **Testing of AC Switching Characteristics**

Internal timing parameters are derived from measuring internal test patterns. All AC switching characteristics are representative of worst-case supply voltage and junction temperature conditions.

For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer and back-annotate to the simulation net list. Unless otherwise noted, values apply to all Spartan-7 FPGAs.

Table 15: Networking Applications Interface Performances (Cont'd)

|                                  | V <sub>CCINT</sub> O <sub>l</sub><br>Grade, a |             |      |       |

|----------------------------------|-----------------------------------------------|-------------|------|-------|

| Description                      | 1.0V                                          |             |      | Units |

|                                  | -2C/-2I                                       | -1C/-1I/-1Q | -1LI |       |

| DDR LVDS receiver <sup>(1)</sup> | 1250                                          | 950         | 950  | Mb/s  |

Table 16: Maximum Physical Interface (PHY) Rate for Memory Interface IP available with the Memory Interface Generator (1)

|                        | V <sub>CCINT</sub> Oper<br>and |             |       |       |

|------------------------|--------------------------------|-------------|-------|-------|

| Memory Standard        | 1                              | .0V         | 0.95V | Units |

|                        | -2C/-2I                        | -1C/-1I/-1Q | -1LI  |       |

| 4:1 Memory Controllers |                                |             |       |       |

| DDR3                   | 800(2)                         | 667         | 667   | Mb/s  |

| DDR3L                  | 800(2)                         | 667         | 667   | Mb/s  |

| DDR2                   | 800(2)                         | 667         | 667   | Mb/s  |

| 2:1 Memory Controllers |                                |             |       |       |

| DDR3                   | 800(2)                         | 667         | 667   | Mb/s  |

| DDR3L                  | 800(2)                         | 667         | 667   | Mb/s  |

| DDR2                   | 800(2)                         | 667         | 667   | Mb/s  |

| LPDDR2                 | 667                            | 533         | 533   | Mb/s  |

### Notes:

## IOB Pad Input/Output/3-State

Table 17 summarizes the values of standard-specific data input delay adjustments, output delays terminating at pads (based on standard) and 3-state delays.

- T<sub>IOPI</sub> is described as the delay from IOB pad through the input buffer to the I-pin of an IOB pad. The

delay varies depending on the capability of the SelectIO input buffer.

- T<sub>IOOP</sub> is described as the delay from the O pin to the IOB pad through the output buffer of an IOB pad. The delay varies depending on the capability of the SelectIO output buffer.

- T<sub>IOTP</sub> is described as the delay from the T pin to the IOB pad through the output buffer of an IOB pad, when 3-state is disabled. The delay varies depending on the SelectIO capability of the output buffer. In HR I/O banks, the IN\_TERM termination turn-on time is always faster than T<sub>IOTP</sub> when the INTERMDISABLE pin is used.

LVDS receivers are typically bounded with certain applications where specific dynamic phase-alignment (DPA) algorithms dominate deterministic performance.

<sup>1.</sup> V<sub>REF</sub> tracking is required. For more information, see the *Zynq-7000 AP SoC and 7 Series FPGAs Memory Interface Solutions User Guide* (UG586) [Ref 7].

<sup>2.</sup> The maximum PHY rate is 667 Mb/s in the FTGB196 package.

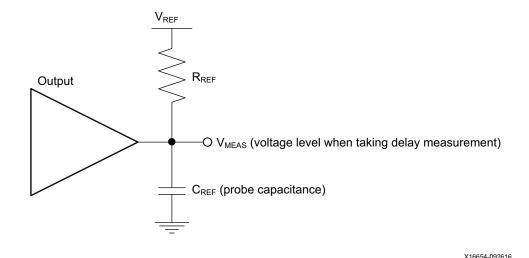

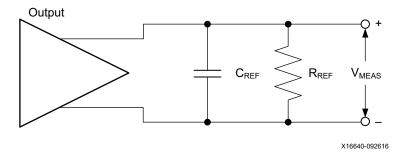

### **Output Delay Measurements**

Output delays are measured with short output traces. Standard termination was used for all testing. The propagation delay of the trace is characterized separately and subtracted from the final measurement, and is therefore not included in the generalized test setups shown in Figure 1 and Figure 2.

Figure 1: Single-ended Test Setup

Figure 2: Differential Test Setup

Parameters  $V_{REF}$ ,  $R_{REF}$ ,  $C_{REF}$ , and  $V_{MEAS}$  fully describe the test conditions for each I/O standard. The most accurate prediction of propagation delay in any given application can be obtained through IBIS simulation, using this method:

- 1. Simulate the output driver of choice into the generalized test setup using values from Table 20.

- 2. Record the time to V<sub>MEAS</sub>.

- 3. Simulate the output driver of choice into the actual PCB trace and load using the appropriate IBIS model or capacitance value to represent the load.

- 4. Record the time to  $V_{MFAS}$ .

- 5. Compare the results of step 2 and step 4. The increase or decrease in delay yields the actual propagation delay of the PCB trace.

# **Input Serializer/Deserializer Switching Characteristics**

Table 23: ISERDES Switching Characteristics

|                                                              |                                                                        | V <sub>CCINT</sub> Ope |            |            |       |

|--------------------------------------------------------------|------------------------------------------------------------------------|------------------------|------------|------------|-------|

| Symbol                                                       | Description                                                            | 1.                     | 0V         | 0.95V      | Units |

|                                                              |                                                                        | -2                     | -1         | -1L        |       |

| Setup/Hold for Cor                                           | ntrol Lines                                                            |                        |            |            |       |

| T <sub>ISCCK_BITSLIP</sub> /<br>T <sub>ISCKC_BITSLIP</sub>   | BITSLIP pin setup/hold with respect to CLKDIV.                         | 0.02/0.15              | 0.02/0.17  | 0.02/0.17  | ns    |

| T <sub>ISCCK_CE</sub> /<br>T <sub>ISCKC_CE</sub>             | CE pin setup/hold with respect to CLK (for CE1).                       | 0.50/-0.01             | 0.72/-0.01 | 0.72/–0.01 | ns    |

| T <sub>ISCCK_CE2</sub> /<br>T <sub>ISCKC_CE2</sub>           | CE pin setup/hold with respect to CLKDIV (for CE2).                    | -0.10/0.36             | -0.10/0.40 | -0.10/0.40 | ns    |

| Setup/Hold for Dat                                           | ta Lines                                                               |                        |            |            |       |

| T <sub>ISDCK_D</sub> /<br>T <sub>ISCKD_D</sub>               | D pin setup/hold with respect to CLK.                                  | -0.02/0.14             | -0.02/0.17 | -0.02/0.17 | ns    |

| T <sub>ISDCK_DDLY</sub> /<br>T <sub>ISCKD_DDLY</sub>         | DDLY pin setup/hold with respect to CLK (using IDELAY). <sup>(1)</sup> | -0.02/0.14             | -0.02/0.17 | -0.02/0.17 | ns    |

| T <sub>ISDCK_D_DDR</sub> /<br>T <sub>ISCKD_D_DDR</sub>       | D pin setup/hold with respect to CLK at DDR mode.                      | -0.02/0.14             | -0.02/0.17 | -0.02/0.17 | ns    |

| T <sub>ISDCK_DDLY_DDR</sub> /<br>T <sub>ISCKD_DDLY_DDR</sub> | D pin setup/hold with respect to CLK at DDR mode (using IDELAY). (1)   | 0.14/0.14              | 0.17/0.17  | 0.17/0.17  | ns    |

| Sequential Delays                                            |                                                                        | <u> </u>               |            |            |       |

| T <sub>ISCKO_Q</sub>                                         | CLKDIV to out at Q pin.                                                | 0.54                   | 0.66       | 0.66       | ns    |

| Propagation Delays                                           | S                                                                      |                        |            |            |       |

| T <sub>ISDO_DO</sub>                                         | D input to DO output pin.                                              | 0.11                   | 0.13       | 0.13       | ns    |

### Notes:

1. Recorded at 0 tap value.

## **Input/Output Delay Switching Characteristics**

Table 25: Input/Output Delay Switching Characteristics

|                                                    |                                                                                       | V <sub>CCINT</sub> O |                          |                  |               |

|----------------------------------------------------|---------------------------------------------------------------------------------------|----------------------|--------------------------|------------------|---------------|

| Symbol                                             | Description                                                                           | 1.0V                 |                          | 0.95V            | Units         |

|                                                    |                                                                                       | -2                   | -1                       | -1L              |               |

| IDELAYCTRL                                         |                                                                                       |                      |                          |                  |               |

| T <sub>DLYCCO_RDY</sub>                            | Reset to ready for IDELAYCTRL.                                                        | 3.67                 | 3.67                     | 3.67             | μs            |

|                                                    | Attribute REFCLK frequency = 200.00. <sup>(1)</sup>                                   | 200.00               | 200.00                   | 200.00           | MHz           |

| F <sub>IDELAYCTRL_REF</sub>                        | Attribute REFCLK frequency = 300.00. <sup>(1)</sup>                                   | 300.00               | 300.00                   | 300.00           | MHz           |

|                                                    | Attribute REFCLK frequency = 400.00. <sup>(1)</sup>                                   | 400.00               | N/A                      | N/A              | MHz           |

| IDELAYCTRL_REF_<br>PRECISION                       | REFCLK precision                                                                      | ±10                  | ±10                      | ±10              | MHz           |

| T <sub>IDELAYCTRL_RPW</sub>                        | Minimum reset pulse width.                                                            | 59.28                | 59.28                    | 59.28            | ns            |

| IDELAY                                             |                                                                                       | ı                    | ,                        | ,                |               |

| T <sub>IDELAYRESOLUTION</sub>                      | IDELAY chain delay resolution.                                                        | 1/                   | (32 x 2 x F <sub>R</sub> | <sub>lEF</sub> ) | μs            |

|                                                    | Pattern dependent period jitter in delay chain for clock pattern. (2)                 | 0                    | 0                        | 0                | ps<br>per tap |

| T <sub>IDELAYPAT_JIT</sub>                         | Pattern dependent period jitter in delay chain for random data pattern (PRBS 23). (3) | ±5                   | ±5                       | ±5               | ps<br>per tap |

|                                                    | Pattern dependent period jitter in delay chain for random data pattern (PRBS 23). (4) | ±9                   | ±9                       | ±9               | ps<br>per tap |

| T <sub>IDELAY_CLK_MAX</sub>                        | Maximum frequency of CLK input to IDELAY.                                             | 680.00               | 600.00                   | 600.00           | MHz           |

| T <sub>IDCCK_CE</sub> / T <sub>IDCKC_CE</sub>      | CE pin setup/hold with respect to C for IDELAY.                                       | 0.16/0.13            | 0.21/0.16                | 0.21/0.16        | ns            |

| T <sub>IDCCK_INC</sub> /<br>T <sub>IDCKC_INC</sub> | INC pin setup/hold with respect to C for IDELAY.                                      | 0.14/0.18            | 0.16/0.22                | 0.16/0.22        | ns            |

| T <sub>IDCCK_RST</sub> /<br>T <sub>IDCKC_RST</sub> | RST pin setup/hold with respect to C for IDELAY.                                      | 0.16/0.11            | 0.18/0.14                | 0.18/0.14        | ns            |

| T <sub>IDDO_IDATAIN</sub>                          | Propagation delay through IDELAY.                                                     | Note 5               | Note 5                   | Note 5           | ps            |

- 1. Average tap delay at 200 MHz = 78 ps, at 300 MHz = 52 ps, and at 400 MHz = 39 ps.

- 2. When HIGH\_PERFORMANCE mode is set to TRUE or FALSE.

- 3. When HIGH\_PERFORMANCE mode is set to TRUE.

- 4. When HIGH\_PERFORMANCE mode is set to FALSE.

- 5. Delay depends on IDELAY tap setting. See the timing report for actual values.

# **CLB Switching Characteristics**

Table 27: CLB Switching Characteristics

| Symbol                                           |                                                                           | V <sub>CCINT</sub> Oper |           |           |         |

|--------------------------------------------------|---------------------------------------------------------------------------|-------------------------|-----------|-----------|---------|

|                                                  | Description                                                               | 1.0V                    |           | 0.95V     | Units   |

|                                                  |                                                                           | -2                      | -1        | -1L       | -       |

| Combinatorial                                    | Delays                                                                    |                         |           |           |         |

| T <sub>ILO</sub>                                 | An – Dn LUT address to A.                                                 | 0.11                    | 0.13      | 0.13      | ns, Max |

| T <sub>ILO_2</sub>                               | An - Dn LUT address to AMUX/CMUX.                                         | 0.30                    | 0.36      | 0.36      | ns, Max |

| T <sub>ILO_3</sub>                               | An – Dn LUT address to BMUX_A.                                            | 0.46                    | 0.55      | 0.55      | ns, Max |

| T <sub>ITO</sub>                                 | An – Dn inputs to A – D Q outputs.                                        | 1.05                    | 1.27      | 1.27      | ns, Max |

| T <sub>AXA</sub>                                 | AX inputs to AMUX output.                                                 | 0.69                    | 0.84      | 0.84      | ns, Max |

| T <sub>AXB</sub>                                 | AX inputs to BMUX output.                                                 | 0.66                    | 0.83      | 0.83      | ns, Max |

| T <sub>AXC</sub>                                 | AX inputs to CMUX output.                                                 | 0.68                    | 0.82      | 0.82      | ns, Max |

| T <sub>AXD</sub>                                 | AX inputs to DMUX output.                                                 | 0.75                    | 0.90      | 0.90      | ns, Max |

| T <sub>BXB</sub>                                 | BX inputs to BMUX output.                                                 | 0.57                    | 0.69      | 0.69      | ns, Max |

| T <sub>BXD</sub>                                 | BX inputs to DMUX output.                                                 | 0.69                    | 0.82      | 0.82      | ns, Max |

| T <sub>CXC</sub>                                 | CX inputs to CMUX output.                                                 | 0.48                    | 0.58      | 0.58      | ns, Max |

| T <sub>CXD</sub>                                 | CX inputs to DMUX output.                                                 | 0.59                    | 0.71      | 0.71      | ns, Max |

| T <sub>DXD</sub>                                 | DX inputs to DMUX output.                                                 | 0.58                    | 0.70      | 0.70      | ns, Max |

| Sequential De                                    | lays                                                                      |                         |           |           |         |

| T <sub>CKO</sub>                                 | Clock to AQ – DQ outputs.                                                 | 0.44                    | 0.53      | 0.53      | ns, Max |

| T <sub>SHCKO</sub>                               | Clock to AMUX – DMUX outputs.                                             | 0.53                    | 0.66      | 0.66      | ns, Max |

| Setup and Hol                                    | d Times of CLB Flip-Flops Before/After Clock CLK                          | <u>"</u>                | ,         | ,         | 1       |

| T <sub>AS</sub> /T <sub>AH</sub>                 | AN – DN input to CLK on A – D flip-flops.                                 | 0.09/0.14               | 0.11/0.18 | 0.11/0.18 | ns, Min |

|                                                  | AX – DX input to CLK on A – D flip-flops.                                 | 0.07/0.21               | 0.09/0.26 | 0.09/0.26 | ns, Min |

| T <sub>DICK</sub> /T <sub>CKDI</sub>             | AX – DX input through MUXs and/or carry logic to CLK on A – D flip-flops. | 0.66/0.09               | 0.81/0.11 | 0.81/0.11 | ns, Min |

| T <sub>CECK_CLB</sub> /<br>T <sub>CKCE_CLB</sub> | CE input to CLK on A – D flip-flops.                                      | 0.17/0.00               | 0.21/0.01 | 0.21/0.01 | ns, Min |

| T <sub>SRCK</sub> /T <sub>CKSR</sub>             | SR input to CLK on A – D flip-flops.                                      | 0.43/0.04               | 0.53/0.05 | 0.53/0.05 | ns, Min |

| Set/Reset                                        |                                                                           | •                       |           |           |         |

| T <sub>SRMIN</sub>                               | SR input minimum pulse width.                                             | 0.78                    | 1.04      | 1.04      | ns, Min |

| T <sub>RQ</sub>                                  | Delay from SR input to AQ – DQ flip-flops.                                | 0.59                    | 0.71      | 0.71      | ns, Max |

| T <sub>CEO</sub>                                 | Delay from CE input to AQ – DQ flip-flops.                                | 0.58                    | 0.70      | 0.70      | ns, Max |

| F <sub>TOG</sub>                                 | Toggle frequency (for export control).                                    | 1286                    | 1098      | 1098      | MHz     |

Table 30: Block RAM and FIFO Switching Characteristics (Cont'd)

|                                                                  |                                                                                                                                           | V <sub>CCINT</sub> Ope |            |            |         |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|------------|---------|

| Symbol                                                           | Description                                                                                                                               | 1.                     | 0V         | 0.95V      | Units   |

|                                                                  |                                                                                                                                           | -2                     | -1         | -1L        |         |

| T <sub>RDCK_DI_ECC_FIFO</sub> /<br>T <sub>RCKD_DI_ECC_FIFO</sub> | DIN inputs with FIFO ECC in standard mode. (8)                                                                                            | 1.15/0.59              | 1.32/0.64  | 1.32/0.64  | ns, Min |

| T <sub>RCCK_INJECTBITERR</sub> / T <sub>RCKC_INJECTBITERR</sub>  | Inject single/double bit error in ECC mode.                                                                                               | 0.64/0.37              | 0.74/0.40  | 0.74/0.40  | ns, Min |

| T <sub>RCCK_EN</sub> /T <sub>RCKC_EN</sub>                       | Block RAM enable (EN) input.                                                                                                              | 0.39/0.21              | 0.45/0.23  | 0.45/0.23  | ns, Min |

| T <sub>RCCK_REGCE</sub> /<br>T <sub>RCKC_REGCE</sub>             | CE input of output register.                                                                                                              | 0.29/0.15              | 0.36/0.16  | 0.36/0.16  | ns, Min |

| T <sub>RCCK_RSTREG</sub> /<br>T <sub>RCKC_RSTREG</sub>           | Synchronous RSTREG input.                                                                                                                 | 0.32/0.07              | 0.35/0.07  | 0.35/0.07  | ns, Min |

| T <sub>RCCK_RSTRAM</sub> /<br>T <sub>RCKC_RSTRAM</sub>           | Synchronous RSTRAM input.                                                                                                                 | 0.34/0.43              | 0.36/0.46  | 0.36/0.46  | ns, Min |

| T <sub>RCCK_WEA</sub> /T <sub>RCKC_WEA</sub>                     | Write enable (WE) input (block RAM only).                                                                                                 | 0.48/0.19              | 0.54/0.20  | 0.54/0.20  | ns, Min |

| T <sub>RCCK_WREN</sub> /<br>T <sub>RCKC_WREN</sub>               | WREN FIFO inputs.                                                                                                                         | 0.46/0.35              | 0.47/0.43  | 0.47/0.43  | ns, Min |

| T <sub>RCCK_RDEN</sub> /<br>T <sub>RCKC_RDEN</sub>               | RDEN FIFO inputs.                                                                                                                         | 0.43/0.35              | 0.43/0.43  | 0.43/0.43  | ns, Min |

| Reset Delays                                                     |                                                                                                                                           | <u> </u>               | ,          | ı          | 1       |

| T <sub>RCO_FLAGS</sub>                                           | Reset RST to FIFO flags/pointers. (9)                                                                                                     | 0.98                   | 1.10       | 1.10       | ns, Max |

| T <sub>RREC_RST</sub> /T <sub>RREM_RST</sub>                     | FIFO reset recovery and removal timing. (10)                                                                                              | 2.07/–0.81             | 2.37/–0.81 | 2.37/–0.81 | ns, Max |

| Maximum Frequency                                                |                                                                                                                                           |                        |            |            |         |

| F <sub>MAX_BRAM_WF_NC</sub>                                      | Block RAM (write first and no change modes) when not in SDP RF mode.                                                                      | 460.83                 | 388.20     | 388.20     | MHz     |

| F <sub>MAX_BRAM_RF</sub> _<br>PERFORMANCE                        | Block RAM (read first, performance mode) when in SDP RF mode but no address overlap between port A and port B.                            | 460.83                 | 388.20     | 388.20     | MHz     |

| F <sub>MAX_BRAM_RF</sub> _<br>DELAYED_WRITE                      | Block RAM (read first, delayed write mode) when in SDP RF mode and there is possibility of overlap between port A and port B addresses.   | 404.53                 | 339.67     | 339.67     | MHz     |

| F <sub>MAX_CAS_WF_NC</sub>                                       | Block RAM cascade (write first, no change mode) when cascade but not in RF mode.                                                          | 418.59                 | 345.78     | 345.78     | MHz     |

| F <sub>MAX_CAS_RF_</sub><br>PERFORMANCE                          | Block RAM cascade (read first, performance mode) when in cascade with RF mode and no possibility of address overlap/one port is disabled. | 418.59                 | 345.78     | 345.78     | MHz     |

### **Clock Buffers and Networks**

Table 32: Global Clock Switching Characteristics (Including BUFGCTRL)

|                                                            |                                 | V <sub>CCINT</sub> O |           |           |       |

|------------------------------------------------------------|---------------------------------|----------------------|-----------|-----------|-------|

| Symbol                                                     | Description                     | 1.0V 0.9             |           | 0.95V     | Units |

|                                                            |                                 | -2                   | -1        | -1L       |       |

| T <sub>BCCCK_CE</sub> /T <sub>BCCKC_CE</sub> (1)           | CE pins setup/hold.             | 0.13/0.40            | 0.16/0.41 | 0.16/0.41 | ns    |

| T <sub>BCCCK_S</sub> / T <sub>BCCKC_S</sub> <sup>(1)</sup> | S pins setup/hold.              | 0.13/0.40            | 0.16/0.41 | 0.16/0.41 | ns    |

| T <sub>BCCKO_O</sub> <sup>(2)</sup>                        | BUFGCTRL delay from I0/I1 to O. | 0.09                 | 0.10      | 0.10      | ns    |

| Maximum Frequency                                          |                                 |                      |           |           |       |

| F <sub>MAX_BUFG</sub>                                      | Global clock tree (BUFG).       | 628.00 464.00 464.00 |           |           | MHz   |

### **Notes:**

Table 33: Input/Output Clock Switching Characteristics (BUFIO)

| Symbol                 |                                 | V <sub>CCINT</sub> O |      |       |       |

|------------------------|---------------------------------|----------------------|------|-------|-------|

|                        | Description                     | 1.0                  | 0V   | 0.95V | Units |

|                        |                                 | -2                   | -1   | -1L   |       |

| T <sub>BIOCKO_O</sub>  | Clock to out delay from I to O. | 1.26                 | 1.54 | 1.54  | ns    |

| Maximum Freque         | ency                            |                      |      |       |       |

| F <sub>MAX_BUFIO</sub> | I/O clock tree (BUFIO).         | 680.00 600.00 600.00 |      |       | MHz   |

Table 34: Regional Clock Buffer Switching Characteristics (BUFR)

|                                      |                                                                  | V <sub>CCINT</sub> O |      |       |       |

|--------------------------------------|------------------------------------------------------------------|----------------------|------|-------|-------|

| Symbol                               | Description                                                      | 1.0                  | OV   | 0.95V | Units |

|                                      |                                                                  | -2                   | -1   | -1L   |       |

| T <sub>BRCKO_O</sub>                 | Clock to out delay from I to O.                                  | 0.76                 | 0.99 | 0.99  | ns    |

| T <sub>BRCKO_O_BYP</sub>             | Clock to out delay from I to O with Divide Bypass attribute set. | 0.39                 | 0.52 | 0.52  | ns    |

| T <sub>BRDO_O</sub>                  | Propagation delay from CLR to O.                                 | 0.85                 | 1.09 | 1.09  | ns    |

| Maximum Frequ                        | ency                                                             |                      |      |       |       |

| F <sub>MAX_BUFR</sub> <sup>(1)</sup> | Regional clock tree (BUFR).                                      | 375.00 315.00 315.00 |      | MHz   |       |

### Notes:

1. The maximum input frequency to the BUFR is the BUFIO F<sub>MAX</sub> frequency.

<sup>1.</sup> T<sub>BCCCK\_CE</sub> and T<sub>BCCKC\_CE</sub> must be satisfied to assure glitch-free operation of the global clock when switching between clocks. These parameters do not apply to the BUFGMUX primitive that assures glitch-free operation. The other global clock setup and hold times are optional; only needing to be satisfied if device operation requires simulation matches on a cycle-for-cycle basis when switching between clocks.

<sup>2.</sup>  $T_{BGCKO\ O}$  (BUFG delay from I0 to O) values are the same as  $T_{BCCKO\ O}$  values.

Table 37: MMCM Specification (Cont'd)

|                                                               |                                                    | V <sub>CCINT</sub> Oper |           |           |          |  |

|---------------------------------------------------------------|----------------------------------------------------|-------------------------|-----------|-----------|----------|--|

| Symbol                                                        | Description                                        | 1.                      | 1.0V      |           | Units    |  |

|                                                               |                                                    | -2                      | -1        | -1L       |          |  |

| T <sub>MMCMDCK_PSINCDEC</sub> / T <sub>MMCMCKD_PSINCDEC</sub> | Setup and hold of phase-shift increment/decrement. | 1.04/0.00               | 1.04/0.00 | 1.04/0.00 | ns       |  |

| T <sub>MMCMCKO_PSDONE</sub>                                   | Phase shift clock-to-out of PSDONE.                | 0.68                    | 0.81      | 0.81      | ns       |  |

| Dynamic Reconfiguration                                       | Port (DRP) for MMCM Before and After DC            | CLK                     |           |           |          |  |

| T <sub>MMCMDCK_DADDR</sub> / T <sub>MMCMCKD_DADDR</sub>       | DADDR setup/hold.                                  | 1.40/0.15               | 1.63/0.15 | 1.63/0.15 | ns, Min  |  |

| T <sub>MMCMDCK_DI</sub> / T <sub>MMCMCKD_DI</sub>             | DI setup/hold.                                     | 1.40/0.15               | 1.63/0.15 | 1.63/0.15 | ns, Min  |  |

| T <sub>MMCMDCK_DEN</sub> / T <sub>MMCMCKD_DEN</sub>           | DEN setup/hold.                                    | 1.97/0.00               | 2.29/0.00 | 2.29/0.00 | ns, Min  |  |

| T <sub>MMCMDCK_DWE</sub> / T <sub>MMCMCKD_DWE</sub>           | DWE setup/hold.                                    | 1.40/0.15               | 1.63/0.15 | 1.63/0.15 | ns, Min  |  |

| T <sub>MMCMCKO_DRDY</sub>                                     | CLK to out of DRDY.                                | 0.72                    | 0.99      | 0.99      | ns, Max  |  |

| F <sub>DCK</sub>                                              | DCLK frequency.                                    | 200.00                  | 200.00    | 200.00    | MHz, Max |  |

- 1. The MMCM does not filter typical spread-spectrum input clocks because they are usually far below the bandwidth filter frequencies.

- 2. The static offset is measured between any MMCM outputs with identical phase.

- 3. Values for this parameter are available in the Clocking Wizard [Ref 8].

- 4. Includes global clock buffer.

- 5. Calculated as F<sub>VCO</sub>/128 assuming output duty cycle is 50%.

- 5. When CLKOUT4\_CASCADE = TRUE,  $MMCM_F_{OUTMIN}$  is 0.036 MHz.

## **PLL Switching Characteristics**

**Table 38: PLL Specification**

|                                       |                                          | V <sub>CCINT</sub> Oper                 |         |         |       |

|---------------------------------------|------------------------------------------|-----------------------------------------|---------|---------|-------|

| Symbol                                | Description                              | 1.0V                                    |         | 0.95V   | Units |

|                                       |                                          | -2                                      | -1      | -1L     |       |

| PLL_F <sub>INMAX</sub>                | Maximum input clock frequency.           | 800.00                                  | 800.00  | 800.00  | MHz   |

| PLL_F <sub>INMIN</sub>                | Minimum input clock frequency.           | 19.00                                   | MHz     |         |       |

| PLL_F <sub>INJITTER</sub>             | Maximum input clock period jitter.       | < 20% of clock input period or 1 ns Max |         |         |       |

|                                       | Allowable input duty cycle: 19—49 MHz.   | 25                                      | 25      | 25      | %     |

|                                       | Allowable input duty cycle: 50—199 MHz.  | 30                                      | 30      | 30      | %     |

| PLL_F <sub>INDUTY</sub>               | Allowable input duty cycle: 200—399 MHz. | 35                                      | 35      | 35      | %     |

|                                       | Allowable input duty cycle: 400—499 MHz. | 40                                      | 40      | 40      | %     |

| Allowable input duty cycle: >500 MHz. |                                          | 45                                      | 45      | 45      | %     |

| PLL_F <sub>VCOMIN</sub>               | Minimum PLL VCO frequency.               | 800.00 800.00 800.00                    |         |         | MHz   |

| PLL_F <sub>VCOMAX</sub>               | Maximum PLL VCO frequency.               | 1866.00                                 | 1600.00 | 1600.00 | MHz   |

Table 42: Clock-Capable Clock Input to Output Delay With PLL(1)

|                         | Description                                   | Device          | V <sub>CCINT</sub> O |               |       |       |

|-------------------------|-----------------------------------------------|-----------------|----------------------|---------------|-------|-------|

| Symbol                  |                                               |                 | 1.0V                 |               | 0.95V | Units |

|                         |                                               |                 | -2                   | -1            | -1L   |       |

| SSTL15 Clock-Ca         | pable Clock Input to Output Delay using Outpu | ut Flip-Flop, F | ast Slew Ra          | te, with PLL. |       |       |

| T <sub>ICKOFPLLCC</sub> | Clock-capable clock input and OUTFF with      | XC7S6           | 0.85                 | 0.85          | 0.85  | ns    |

|                         | PLL. <sup>(2)</sup>                           | XC7S15          | 0.85                 | 0.85          | 0.85  | ns    |

|                         |                                               | XC7S25          | 0.83                 | 0.83          | 0.83  | ns    |

|                         |                                               | XC7S50          | 0.83                 | 0.83          | 0.83  | ns    |

|                         |                                               | XC7S75          | 0.83                 | 0.83          | 0.83  | ns    |

|                         |                                               | XC7S100         | 0.83                 | 0.83          | 0.83  | ns    |

|                         |                                               | XA7S6           | 0.85                 | 0.85          | N/A   | ns    |

|                         |                                               | XA7S15          | 0.85                 | 0.85          | N/A   | ns    |

|                         |                                               | XA7S25          | 0.83                 | 0.83          | N/A   | ns    |

|                         |                                               | XA7S50          | 0.83                 | 0.83          | N/A   | ns    |

|                         |                                               | XA7S75          | 0.83                 | 0.83          | N/A   | ns    |

|                         |                                               | XA7S100         | 0.83                 | 0.83          | N/A   | ns    |

Table 43: Pin-to-Pin, Clock-to-Out using BUFIO

|                      | Symbol Description                                        | V <sub>CCINT</sub> Operating Voltage and Speed<br>Grade |              |       |       |  |

|----------------------|-----------------------------------------------------------|---------------------------------------------------------|--------------|-------|-------|--|

| Symbol               |                                                           | 1.0V                                                    |              | 0.95V | Units |  |

|                      |                                                           | -2                                                      | -1           | -1L   |       |  |

| SSTL15 Clock-Ca      | apable Clock Input to Output Delay using Output Flip-Flop | o, Fast Slew R                                          | ate, with BU | FIO.  |       |  |

| T <sub>ICKOFCS</sub> | Clock to out of I/O clock.                                | 5.61 6.64 6.64                                          |              |       | ns    |  |

This table lists representative values where one global clock input drives one vertical clock line in each accessible column, and where all

accessible IOB and CLB flip-flops are clocked by the global clock net.

<sup>2.</sup> PLL output jitter is already included in the timing calculation.

Table 45: Clock-Capable Clock Input Setup and Hold With MMCM

|                         |                                            |               | V <sub>CCINT</sub> Ope |                        |            |       |

|-------------------------|--------------------------------------------|---------------|------------------------|------------------------|------------|-------|

| Symbol                  | Description                                | Device        | 1.0                    | OV                     | 0.95V      | Units |

|                         |                                            |               | -2                     | -1                     | -1L        |       |

| Input Setup a           | and Hold Time Relative to Global Clock Inp | ut Signal for | SSTL15 Standa          | ırd. <sup>(1)(2)</sup> |            |       |

| T <sub>PSMMCMCC</sub> / | No delay clock-capable clock input and     | XC7S6         | 2.73/-0.59             | 3.27/-0.59             | 3.27/-0.59 | ns    |

| T <sub>PHMMCMCC</sub>   | IFF <sup>(3)</sup> with MMCM.              | XC7S15        | 2.73/-0.59             | 3.27/-0.59             | 3.27/-0.59 | ns    |

|                         |                                            | XC7S25        | 2.69/-0.61             | 3.21/-0.61             | 3.21/-0.61 | ns    |

|                         |                                            | XC7S50        | 2.81/-0.62             | 3.35/-0.62             | 3.35/-0.62 | ns    |

|                         |                                            | XC7S75        | 2.81/-0.62             | 3.36/-0.62             | 3.36/-0.62 | ns    |

|                         |                                            | XC7S100       | 2.81/-0.62             | 3.36/-0.62             | 3.36/-0.62 | ns    |

|                         |                                            | XA7S6         | 2.73/-0.59             | 3.27/-0.59             | N/A        | ns    |

|                         |                                            | XA7S15        | 2.73/-0.59             | 3.27/-0.59             | N/A        | ns    |

|                         |                                            | XA7S25        | 2.69/-0.61             | 3.21/-0.61             | N/A        | ns    |

|                         |                                            | XA7S50        | 2.81/-0.62             | 3.35/-0.62             | N/A        | ns    |

|                         |                                            | XA7S75        | 2.81/-0.62             | 3.36/-0.62             | N/A        | ns    |

|                         |                                            | XA7S100       | 2.81/-0.62             | 3.36/-0.62             | N/A        | ns    |

Setup and hold times are measured over worst case conditions (process, voltage, temperature). Setup time is measured relative to the global clock input signal using the slowest process, highest temperature, and lowest voltage. Hold time is measured relative to the global clock input signal using the fastest process, lowest temperature, and highest voltage.

<sup>2.</sup> Use IBIS to determine any duty-cycle distortion incurred using various standards.

<sup>3.</sup> IFF = Input flip-flop or latch.

Table 46: Clock-Capable Clock Input Setup and Hold With PLL

|                        |                                           |               | V <sub>CCINT</sub> Ope |                            |            |       |

|------------------------|-------------------------------------------|---------------|------------------------|----------------------------|------------|-------|

| Symbol                 | Description                               | Device        | 1.0                    | OV                         | 0.95V      | Units |

|                        |                                           |               | -2                     | -1                         | -1L        |       |

| Input Setup            | and Hold Time Relative to Clock-Capable C | lock Input Si | gnal for SSTL15        | Standard. <sup>(1)(2</sup> | )          |       |

| T <sub>PSPLLCC</sub> / | (0)                                       | XC7S6         | 3.07/-0.17             | 3.69/-0.17                 | 3.69/-0.17 | ns    |

| T <sub>PHPLLCC</sub>   |                                           | XC7S15        | 3.07/-0.17             | 3.69/-0.17                 | 3.69/-0.17 | ns    |

|                        |                                           | XC7S25        | 3.04/-0.19             | 3.64/-0.19                 | 3.64/-0.19 | ns    |

|                        |                                           | XC7S50        | 3.15/-0.19             | 3.77/-0.19                 | 3.77/-0.19 | ns    |

|                        |                                           | XC7S75        | 3.15/-0.19             | 3.78/-0.19                 | 3.78/-0.19 | ns    |

|                        |                                           | XC7S100       | 3.15/-0.19             | 3.78/-0.19                 | 3.78/-0.19 | ns    |

|                        |                                           | XA7S6         | 3.07/-0.17             | 3.69/-0.17                 | N/A        | ns    |

|                        |                                           | XA7S15        | 3.07/-0.17             | 3.69/-0.17                 | N/A        | ns    |

|                        |                                           | XA7S25        | 3.04/-0.19             | 3.64/-0.19                 | N/A        | ns    |

|                        |                                           | XA7S50        | 3.15/-0.19             | 3.77/-0.19                 | N/A        | ns    |

|                        |                                           | XA7S75        | 3.15/-0.19             | 3.78/-0.19                 | N/A        | ns    |

|                        |                                           | XA7S100       | 3.15/-0.19             | 3.78/-0.19                 | N/A        | ns    |

- 1. Setup and hold times are measured over worst case conditions (process, voltage, temperature). Setup time is measured relative to the global clock input signal using the slowest process, highest temperature, and lowest voltage. Hold time is measured relative to the global clock input signal using the fastest process, lowest temperature, and highest voltage.

- 2. Use IBIS to determine any duty-cycle distortion incurred using various standards.

- 3. IFF = Input flip-flop or latch.

Table 47: Data Input Setup and Hold Times Relative to a Forwarded Clock Input Pin Using BUFIO

| Symbol                               |                                                                                                    | V <sub>CCINT</sub> Ope | rating Voltage<br>Grade | and Speed |       |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------|------------------------|-------------------------|-----------|-------|--|--|--|

|                                      | Description                                                                                        | 1.0                    | OV                      | 0.95V     | Units |  |  |  |

|                                      |                                                                                                    | -2                     | -1                      | -1L       |       |  |  |  |

| Input Setup a                        | Input Setup and Hold Time Relative to a Forwarded Clock Input Pin Using BUFIO for SSTL15 Standard. |                        |                         |           |       |  |  |  |

| T <sub>PSCS</sub> /T <sub>PHCS</sub> | Setup and hold of I/O clock.                                                                       | -0.38/1.46             | -0.38/1.76              | ns        |       |  |  |  |

Table 48: Sample Window

|                         |                                                  | V <sub>CCINT</sub> Ope | rating Voltage<br>Grade | and Speed |       |

|-------------------------|--------------------------------------------------|------------------------|-------------------------|-----------|-------|

| Symbol                  | Description                                      | 1.0V                   |                         | 0.95V     | Units |

|                         |                                                  | -2                     | -1                      | -1L       |       |

| T <sub>SAMP</sub>       | Sampling error at receiver pins. (1)             | 0.64                   | 0.70                    | 0.70      | ns    |

| T <sub>SAMP_BUFIO</sub> | Sampling error at receiver pins using BUFIO. (2) | 0.40 0.46 0.46         |                         | 0.46      | ns    |

- 1. This parameter indicates the total sampling error of the Spartan-7 FPGAs DDR input registers, measured across voltage, temperature, and process. The characterization methodology uses the MMCM to capture the DDR input registers' edges of operation. These measurements include:

- CLK0 MMCM jitter

- MMCM accuracy (phase offset)

- MMCM phase shift resolution

These measurements do not include package or clock tree skew.

2. This parameter indicates the total sampling error of the Spartan-7 FPGAs DDR input registers, measured across voltage, temperature, and process. The characterization methodology uses the BUFIO clock network and IDELAY to capture the DDR input registers' edges of operation. These measurements do not include package or clock tree skew.

# **XADC Specifications**

The 7 Series FPGAs Overview (DS180) [Ref 1] and XA Spartan-7 Automotive FPGA Data Sheet: Overview (DS171) [Ref 2] list the devices that contain a 7 series XADC dual 12-Bit 1 MSPS analog-to-digital converter.

Table 50: XADC Specifications

| Parameter                                                                        | Symbol   | Comments/Conditions                                                                                                                      | Min                  | Тур | Max                | Units |

|----------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|--------------------|-------|

| $V_{CCADC} = 1.8V \pm 5\%$ , $V_{REFF}$<br>Typical values at $T_j = +40^{\circ}$ |          | $V_{REFN} = 0V$ , ADCCLK = 26 MHz, $-55$ °C $\leq T$                                                                                     | <sub>j</sub> ≤ 125°( | C.  |                    |       |

| ADC Accuracy <sup>(1)</sup>                                                      |          |                                                                                                                                          |                      |     |                    |       |

| Resolution                                                                       |          |                                                                                                                                          | 12                   | _   | _                  | Bits  |

| Integral nonlinearity <sup>(2)</sup>                                             | INL      | $-40^{\circ}\text{C} \le \text{T}_{j} \le 100^{\circ}\text{C}$                                                                           | _                    | _   | ±2                 | LSBs  |

| mtegrai nonlinearity(2)                                                          | IINL     | $-55^{\circ}\text{C} \le \text{T}_{j} < -40^{\circ}\text{C}; \ 100^{\circ}\text{C} < \text{T}_{j} \le 125^{\circ}\text{C}$               | _                    | _   | ±3                 | LSBs  |

| Differential nonlinearity                                                        | DNL      | No missing codes, guaranteed monotonic.                                                                                                  | _                    | _   | ±1                 | LSBs  |

|                                                                                  | Uninglar | $-40^{\circ}\text{C} \le \text{T}_{j} \le 100^{\circ}\text{C}$                                                                           | _                    | _   | ±8                 | LSBs  |

| Offset error                                                                     | Unipolar | $-55^{\circ}\text{C} \le \text{T}_{j} < -40^{\circ}\text{C}; \ 100^{\circ}\text{C} < \text{T}_{j} \le 125^{\circ}\text{C}$               | _                    | _   | ±12                | LSBs  |

|                                                                                  | Bipolar  | –55°C ≤ T <sub>j</sub> ≤ 125°C                                                                                                           | _                    | _   | ±4                 | LSBs  |

| Gain error                                                                       |          |                                                                                                                                          | _                    | _   | ±0.5               | %     |

| Offset matching                                                                  |          |                                                                                                                                          | _                    | _   | 4                  | LSBs  |

| Gain matching                                                                    |          |                                                                                                                                          | _                    | _   | 0.3                | %     |

| Sample rate                                                                      |          |                                                                                                                                          | _                    | _   | 1                  | MS/s  |

| Signal to noise ratio <sup>(2)</sup>                                             | SNR      | $F_{SAMPLE} = 500 \text{ KS/s}, F_{IN} = 20 \text{ kHz}$                                                                                 | 60                   | _   | _                  | dB    |

| RMS code noise                                                                   |          | External 1.25V reference.                                                                                                                | _                    | _   | 2                  | LSBs  |

| RIVIS Code Hoise                                                                 |          | On-chip reference.                                                                                                                       | _                    | 3   | _                  | LSBs  |

| Total harmonic distortion <sup>(2)</sup>                                         | THD      | $F_{SAMPLE} = 500 \text{ KS/s}, F_{IN} = 20 \text{ kHz}$                                                                                 | 70                   | _   | _                  | dB    |

| Analog Inputs <sup>(3)</sup>                                                     |          |                                                                                                                                          |                      |     |                    |       |

|                                                                                  |          | Unipolar operation.                                                                                                                      | 0                    | _   | 1                  | V     |

| ADC inner to manage                                                              |          | Bipolar operation.                                                                                                                       | -0.5                 | _   | +0.5               | V     |

| ADC input ranges                                                                 |          | Unipolar common mode range (FS input).                                                                                                   | 0                    | _   | +0.5               | V     |

|                                                                                  |          | Bipolar common mode range (FS input).                                                                                                    | +0.5                 | _   | +0.6               | V     |

| Maximum external channel ranges                                                  | input    | Adjacent analog channels set within these ranges should not corrupt measurements on adjacent channels.                                   | -0.1                 | _   | V <sub>CCADC</sub> | V     |

| Full-resolution bandwidth                                                        | FRBW     | Auxiliary channel full resolution bandwidth.                                                                                             | 250                  | _   | -                  | kHz   |

| On-chip Sensors                                                                  |          |                                                                                                                                          |                      |     |                    |       |

| Tomorotumo                                                                       |          | $-40^{\circ}\text{C} \le \text{T}_{j} \le 100^{\circ}\text{C}$                                                                           | -                    | _   | ±4                 | °C    |

| Temperature sensor error                                                         |          | $-55^{\circ}\text{C} \le \text{T}_{\text{j}} < -40^{\circ}\text{C}; \ 100^{\circ}\text{C} < \text{T}_{\text{j}} \le 125^{\circ}\text{C}$ | _                    | _   | ±6                 | °C    |

| Cumply concor arran                                                              |          | $-40^{\circ}\text{C} \le \text{T}_{\text{j}} \le 100^{\circ}\text{C}$                                                                    | _                    | _   | ±1                 | %     |

| Supply sensor error                                                              |          | $-55^{\circ}\text{C} \le \text{T}_{j} < -40^{\circ}\text{C}; \ 100^{\circ}\text{C} < \text{T}_{j} \le 125^{\circ}\text{C}$               | _                    | _   | ±2                 | %     |

### Table 50: XADC Specifications (Cont'd)

| Parameter                      | Symbol            | Comments/Conditions                                                                                                                                   | Min    | Тур  | Max    | Units  |  |  |  |

|--------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--------|--------|--|--|--|

| Conversion Rate <sup>(4)</sup> |                   |                                                                                                                                                       |        |      |        |        |  |  |  |

| Conversion time: continuous    | t <sub>CONV</sub> | Number of ADCCLK cycles.                                                                                                                              | 26     | _    | 32     | Cycles |  |  |  |

| Conversion time: event         | t <sub>CONV</sub> | Number of CLK cycles.                                                                                                                                 | _      | -    | 21     | Cycles |  |  |  |

| DRP clock frequency            | DCLK              | DRP clock frequency.                                                                                                                                  | 8      | -    | 250    | MHz    |  |  |  |