#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | C251                                                                       |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 24MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, Microwire, SPI, UART/USART                      |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | ·                                                                          |

| Program Memory Type        | ROMIess                                                                    |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | ·                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIL                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at80251g2d-3csum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

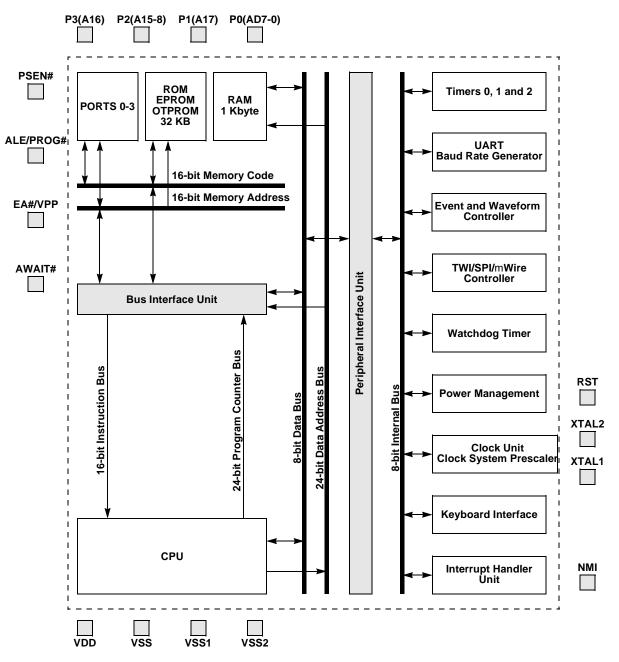

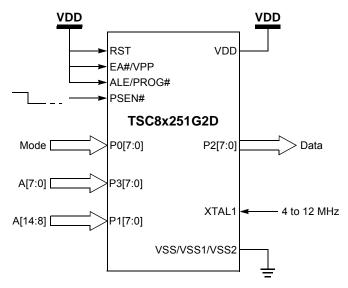

## **Block Diagram**

### Table 1. TSC80251G2D Pin Assignment

| DIP | PLCC | VQFP | Name                        | DIP | PLCC | VQFP | Name      |

|-----|------|------|-----------------------------|-----|------|------|-----------|

|     | 1    | 39   | VSS1                        |     | 23   | 17   | VSS2      |

| 1   | 2    | 40   | P1.0/T2                     | 21  | 24   | 18   | P2.0/A8   |

| 2   | 3    | 41   | P1.1/T2EX                   | 22  | 25   | 19   | P2.1/A9   |

| 3   | 4    | 42   | P1.2/ECI                    | 23  | 26   | 20   | P2.2/A10  |

| 4   | 5    | 43   | P1.3/CEX0                   | 24  | 27   | 21   | P2.3/A11  |

| 5   | 6    | 44   | P1.4/CEX1/SS#               | 25  | 28   | 22   | P2.4/A12  |

| 6   | 7    | 1    | P1.5/CEX2/MISO              | 26  | 29   | 23   | P2.5/A13  |

| 7   | 8    | 2    | P1.6/CEX3/SCL/SCK/WAIT#     | 27  | 30   | 24   | P2.6/A14  |

| 8   | 9    | 3    | P1.7/A17/CEX4/SDA/MOSI/WCLK | 28  | 31   | 25   | P2.7/A15  |

| 9   | 10   | 4    | RST                         | 29  | 32   | 26   | PSEN#     |

| 10  | 11   | 5    | P3.0/RXD                    | 30  | 33   | 27   | ALE/PROG# |

|     | 12   | 6    | AWAIT#                      |     | 34   | 28   | NMI       |

| 11  | 13   | 7    | P3.1/TXD                    | 31  | 35   | 29   | EA#/VPP   |

| 12  | 14   | 8    | P3.2/INT0#                  | 32  | 36   | 30   | P0.7/AD7  |

| 13  | 15   | 9    | P3.3/INT1#                  | 33  | 37   | 31   | P0.6/AD6  |

| 14  | 16   | 10   | P3.4/T0                     | 34  | 38   | 32   | P0.5/AD5  |

| 15  | 17   | 11   | P3.5/T1                     | 35  | 39   | 33   | P0.4/AD4  |

| 16  | 18   | 12   | P3.6/WR#                    | 36  | 40   | 34   | P0.3/AD3  |

| 17  | 19   | 13   | P3.7/A16/RD#                | 37  | 41   | 35   | P0.2/AD2  |

| 18  | 20   | 14   | XTAL2                       | 38  | 42   | 36   | P0.1/AD1  |

| 19  | 21   | 15   | XTAL1                       | 39  | 43   | 37   | P0.0/AD0  |

| 20  | 22   | 16   | VSS                         | 40  | 44   | 38   | VDD       |

| Table 2. | Product Name Signal Description | (Continued) |

|----------|---------------------------------|-------------|

|----------|---------------------------------|-------------|

| Signal<br>Name | Туре | Description                                                                                                                                                                                                  | Alternate<br>Function |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| XTAL2          | ο    | Output of the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected to this<br>pin. If an external oscillator is used, leave XTAL2 unconnected. | _                     |

Note: The description of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the Non-Page mode chip configuration. If the chip is configured in Page mode operation, port 0 carries the lower address bits (A7:0) while port 2 carries the upper address bits (A15:8) and the data (D7:0).

### **Address Spaces**

The TSC80251G2D derivatives implement four different address spaces:

- On-chip ROM program/code memory (not present in ROMless devices)

- On-chip RAM data memory

- Special Function Registers (SFRs)

- Configuration array

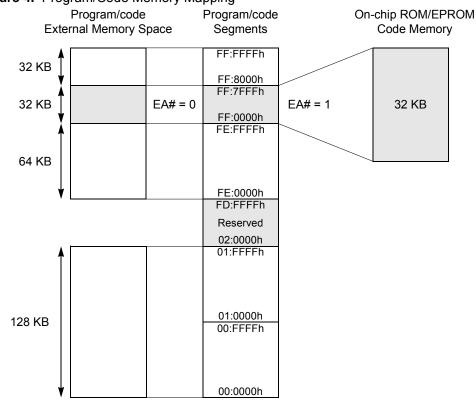

#### **Program/Code Memory** The TSC83251G2D and TSC87251G2D implement 32 KB of on-chip program/code memory. Figure 4 shows the split of the internal and external program/code memory spaces. If EA# is tied to a high level, the 32-Kbyte on-chip program memory is mapped in the lower part of segment FF: where the C251 core jumps after reset. The rest of the program/code memory space is mapped to the external memory. If EA# is tied to a low level, the internal program/code memory is not used and all the accesses are directed to the external memory.

The TSC83251G2D products provide the internal program/code memory in a masked ROM memory while the TSC87251G2D products provide it in an EPROM memory. For the TSC80251G2D products, there is no internal program/code memory and EA# must be tied to a low level.

Note:

Special care should be taken when the Program Counter (PC) increments:

If the program executes exclusively from on-chip code memory (not from external memory), beware of executing code from the upper eight bytes of the on-chip ROM (FF:7FF8h-FF:7FFh). Because of its pipeline capability, the TSC80251G2D derivative may attempt to prefetch code from external memory (at an address above FF:7FFFh) and thereby disrupt I/O Ports 0 and 2. Fetching code constants from these 8 bytes does not affect Ports 0 and 2.

When PC reaches the end of segment FF:, it loops to the reset address FF:0000h (for

compatibility with the C51 Architecture). When PC increments beyond the end of seqment FE:, it continues at the reset address FF:0000h (linearity). When PC increments beyond the end of segment 01:, it loops to the beginning of segment 00: (this prevents from its going into the reserved area).

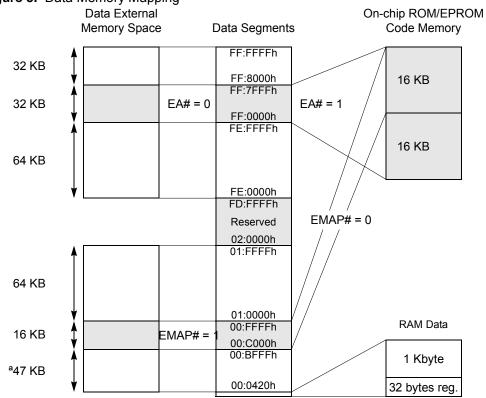

Data Memory The TSC80251G2D derivatives implement 1 Kbyte of on-chip data RAM. Figure 5 shows the split of the internal and external data memory spaces. This memory is mapped in the data space just over the 32 bytes of registers area (see TSC80251 Programmers' Guide). Hence, the part of the on-chip RAM located from 20h to FFh is bit addressable. This on-chip RAM is not accessible through the program/code memory space.

> For faster computation with the on-chip ROM/EPROM code of the TSC83251G2D/TSC87251G2D, its upper 16 KB are also mapped in the upper part of the region 00: if the On-Chip Code Memory Map configuration bit is cleared (EMAP# bit in UCONFIG1 byte, see Figure ). However, if EA# is tied to a low level, the TSC80251G2D derivative is running as a ROMless product and the code is actually fetched in the corresponding external memory (i.e. the upper 16 KB of the lower 32 KB of the segment FF:). If EMAP# bit is set, the on-chip ROM is not accessible through the region 00:.

> All the accesses to the portion of the data space with no on-chip memory mapped onto are redirected to the external memory.

Figure 5. Data Memory Mapping

### Table 7. System Management SFRs

| Mnemonic | Name             |

|----------|------------------|

| PCON     | Power Control    |

| POWM     | Power Management |

| Mnemonic | Name                                     |

|----------|------------------------------------------|

| CKRL     | Clock Reload                             |

| WCON     | Synchronous Real-Time Wait State Control |

### Table 8. Interrupt SFRs

| Mnemonic | Name                              |

|----------|-----------------------------------|

| IE0      | Interrupt Enable Control 0        |

| IE1      | Interrupt Enable Control 1        |

| IPH0     | Interrupt Priority Control High 0 |

| Table 9. Keyb | oard Interface | SFRs |

|---------------|----------------|------|

|---------------|----------------|------|

| Mnemonic | Name                          |

|----------|-------------------------------|

| P1IE     | Port 1 Input Interrupt Enable |

| P1F      | Port 1 Flag                   |

| IPH1 | Interrupt Priority Control High 1 |

|------|-----------------------------------|

| IPL1 | Interrupt Priority Control Low 1  |

|      |                                   |

|      |                                   |

Interrupt Priority Control Low 0

Mnemonic Name

IPL0

| Mnemonic | Name                   |

|----------|------------------------|

| P1LS     | Port 1 Level Selection |

| Register                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C251 | C51 |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| at Ri                                                       | A memory location (00h-FFh) addressed indirectly via byte registers<br>R0 or R1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _    | 3   |

| Rn<br>n                                                     | Byte register R0-R7 of the currently selected register bank<br>Byte register index: n = 0-7                                                                                                                                                                                                                                                                                                                                                                                                                                      | _    | 3   |

| Rm<br>Rmd<br>Rms<br>m, md, ms                               | Byte register R0-R15 of the currently selected register file<br>Destination register<br>Source register<br>Byte register index: m, md, ms = 0-15                                                                                                                                                                                                                                                                                                                                                                                 | 3    | -   |

| WRj<br>WRjd<br>WRjs<br>at WRj<br>at WRj +dis16<br>j, jd, js | Word register WR0, WR2,, WR30 of the currently selected register<br>file<br>Destination register<br>Source register<br>A memory location (00:0000h-00:FFFFh) addressed indirectly<br>through word register WR0-WR30, is the target address for jump<br>instructions.<br>A memory location (00:0000h-00:FFFFh) addressed indirectly<br>through word register (WR0-WR30) + 16-bit signed (two's<br>complement) displacement value<br>Word register index: j, jd, js = 0-30                                                         | 3    | _   |

| DRk<br>DRkd<br>DRks<br>at DRk<br>at DRk +dis16<br>k, kd, ks | Dword register DR0, DR4,, DR28, DR56, DR60 of the currently<br>selected register file<br>Destination register<br>Source register<br>A memory location (00:0000h-FF:FFFFh) addressed indirectly<br>through dword register DR0-DR28, DR56 and DR60, is the target<br>address for jump instruction<br>A memory location (00:0000h-FF:FFFFh) addressed indirectly<br>through dword register (DR0-DR28, DR56, DR60) + 16-bit (two's<br>complement) signed displacement value<br>Dword register index: k, kd, ks = 0, 4, 8, 28, 56, 60 | 3    | _   |

### Table 19. Notation for Register Operands

4. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

$IncrementINC < dest>dest opnd \leftarrow dest opnd + 1$

IncrementINC <dest>, <src>dest opnd  $\leftarrow$  dest opnd + src opnd

$DecrementDEC < dest>dest opnd \leftarrow dest opnd - 1$

$\texttt{DecrementDEC <dest>, <src>dest opnd \leftarrow dest opnd - src opnd}$

|                           |             |                                          | Binary | Mode             | Source Mode |                  |

|---------------------------|-------------|------------------------------------------|--------|------------------|-------------|------------------|

| <pre></pre>               |             | Comments                                 | Bytes  | States           | Bytes       | States           |

| A ACC b                   |             | ACC by 1                                 | 1      | 1                | 1           | 1                |

| INC                       | Rn          | Register by 1                            | 1      | 1                | 2           | 2                |

| DEC                       | dir8        | Direct address (on-chip RAM or SFR) by 1 | 2      | 2 <sup>(2)</sup> | 2           | 2 <sup>(2)</sup> |

| at Ri Indirect address by |             | Indirect address by 1                    | 1      | 3                | 2           | 4                |

| INC                       | Rm, #short  | n, #short Byte register by 1, 2, or 4    |        | 2                | 2           | 1                |

| DEC                       | WRj, #short | ort Word register by 1, 2, or 4          |        | 2                | 2           | 1                |

| INC                       | DRk, #short | Double word register by 1, 2, or 4       | 3      | 4                | 2           | 3                |

| DEC                       | DRk, #short | Double word register by 1, 2, or 4       | 3      | 5                | 2           | 4                |

| INC                       | DPTR        | Data pointer by 1                        | 1      | 1                | 1           | 1                |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

| Table 30. Summary of Conditional Jump Instructions (2 | Table 30. | ummary of Conditional Jump Instructions (2/2) |

|-------------------------------------------------------|-----------|-----------------------------------------------|

|-------------------------------------------------------|-----------|-----------------------------------------------|

| Jump if bitJB <src>, rel(PC) <math>\leftarrow</math> (PC) + size (instr);<br/>IF [src opnd = 1] THEN (PC) <math>\leftarrow</math> (PC) + rel</src>                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jump if not bitJNB <src>, rel(PC) <math>\leftarrow</math> (PC) + size (instr);<br/>IF [src opnd = 0] THEN (PC) <math>\leftarrow</math> (PC) + rel</src>                                                      |

| Jump if bit and clearJBC <dest>, rel(PC) <math>\leftarrow</math> (PC) + size (instr);<br/>IF [dest opnd = 1] THEN<br/>dest opnd <math>\leftarrow</math> 0<br/>(PC) <math>\leftarrow</math> (PC) + rel</dest> |

| Jump if accumulator is zeroJZ rel(PC) $\leftarrow$ (PC) + size (instr);<br>IF [(A) = 0] THEN (PC) $\leftarrow$ (PC) + rel                                                                                    |

| Jump if accumulator is not zeroJNZ rel(PC) $\leftarrow$ (PC) + size (instr);                                                                                                                                 |

IF [(A)  $\neq$  0] THEN (PC)  $\leftarrow$  (PC) + rel

Compare and jump if not equalCJNE <src1>, <src2>, rel(PC)  $\leftarrow$  (PC) + size (instr);

IF [src opnd1 < src opnd2] THEN (CY)  $\leftarrow$  1

IF [src opnd1  $\geq$  src opnd2] THEN (CY)  $\leftarrow$  0 IF [src opnd1  $\neq$  src opnd2] THEN (PC)  $\leftarrow$  (PC) + rel

Decrement and jump if not zeroDJNZ <dest>, rel(PC)  $\leftarrow$  (PC) + size (instr); dest opnd  $\leftarrow$  dest opnd -1; IF  $[\phi(Z)]$  THEN (PC)  $\leftarrow$  (PC) + rel

|                                                                       |                                                                  |                                                               | Binary             | Mode <sup>(2)</sup>        | Source             | Mode <sup>(2)</sup>   |

|-----------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------|--------------------|----------------------------|--------------------|-----------------------|

| Mnemonic                                                              | <dest>, <src><sup>(1)</sup></src></dest>                         | Comments                                                      | Bytes              | States                     | Bytes              | States                |

|                                                                       | bit51, rel                                                       | Jump if direct bit is set                                     | 3                  | 2/5 <sup>(3)(6)</sup>      | 3                  | 2/5 <sup>(3)(6)</sup> |

| JB                                                                    | bit, rel                                                         | Jump if direct bit of 8-bit address location is set           | 5                  | 4/7 <sup>(3)(6)</sup>      | 4                  | 3/6 <sup>(3)(6)</sup> |

|                                                                       | bit51, rel Jump if direct bit is not set                         |                                                               | 3                  | 2/5 <sup>(3)(6)</sup>      | 3                  | 2/5 <sup>(3)(6)</sup> |

| JNB                                                                   | bit, rel                                                         | Jump if direct bit of 8-bit address location is not set       | 5                  | 4/7 <sup>(3)(6)</sup>      | 4                  | 3/6 <sup>(3)</sup>    |

|                                                                       | bit51, rel                                                       | Jump if direct bit is set & clear bit                         | 3                  | 4/7 <sup>(5)(6)</sup>      | 3                  | 4/7 <sup>(5)(6)</sup> |

| JBC                                                                   | bit, rel                                                         | Jump if direct bit of 8-bit address location is set and clear | 5                  | 7/10 <sup>(5)(</sup><br>6) | 4                  | 6/9 <sup>(5)(6)</sup> |

| JZ                                                                    | rel                                                              | Jump if ACC is zero                                           | 2                  | 2/5 <sup>(6)</sup>         | 2                  | 2/5 <sup>(6)</sup>    |

| JNZ                                                                   | rel                                                              | Jump if ACC is not zero                                       | 2                  | 2/5 <sup>(6)</sup>         | 2                  | 2/5 <sup>(6)</sup>    |

|                                                                       | A, dir8, rel Compare direct address to ACC and jump if not equal |                                                               | 3                  | 2/5 <sup>(3)(6)</sup>      | 3                  | 2/5 <sup>(3)(6)</sup> |

| CJNE                                                                  | A, #data, rel                                                    | Compare immediate to ACC and jump if not equal                | 3                  | 2/5 <sup>(6)</sup>         | 3                  | 2/5 <sup>(6)</sup>    |

| CJINE                                                                 | Rn, #data, rel                                                   | Compare immediate to register and jump if not equal           | 3                  | 2/5 <sup>(6)</sup>         | 4                  | 3/6 <sup>(6)</sup>    |

| at Ri, #data, rel Compare immediate to indirect and jump if not equal |                                                                  | 3                                                             | 3/6 <sup>(6)</sup> | 4                          | 4/7 <sup>(6)</sup> |                       |

| DJNZ                                                                  | Rn, rel                                                          | Decrement register and jump if not zero                       | 2                  | 2/5 <sup>(6)</sup>         | 3                  | 3/6 <sup>(6)</sup>    |

| DJINZ                                                                 | dir8, rel                                                        | Decrement direct address and jump if not zero                 | 3                  | 3/6 <sup>(4)(6)</sup>      | 3                  | 3/6 <sup>(4)(6)</sup> |

1. A shaded cell denotes an instruction in the C51 Architecture. Notes:

2. States are given as jump not-taken/taken.

- 3. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 4. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states.

| Table 32. | Summar | of Call and | Return | Instructions |

|-----------|--------|-------------|--------|--------------|

|-----------|--------|-------------|--------|--------------|

|                                | ACALL <src><br/><math>\leftarrow</math> src opnd</src> | $(PC) \leftarrow (PC)$ +2; push $(PC)_{15:0}$ ;                                                                                                                                                           |                            |                                                                                                                 |                            |                                                                                                                                     |

|--------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Extended ca                    |                                                        | $P(PC) \leftarrow (PC) + size (instr); push (PC)_2$                                                                                                                                                       | 3:0,                       |                                                                                                                 |                            |                                                                                                                                     |

| Long callLCA                   |                                                        | ) $\leftarrow$ (PC) + size (instr); push (PC) <sub>15:0</sub> ;                                                                                                                                           |                            |                                                                                                                 |                            |                                                                                                                                     |

| Return from                    | subroutineRE                                           | Tpop (PC) <sub>15:0</sub>                                                                                                                                                                                 |                            |                                                                                                                 |                            |                                                                                                                                     |

|                                |                                                        | outineERETpop(PC) <sub>23:0</sub>                                                                                                                                                                         |                            |                                                                                                                 |                            |                                                                                                                                     |

|                                |                                                        | IF [INTR = 0] THEN pop (PC) <sub>15:0</sub><br>pop (PC) <sub>23:0</sub> ; pop (PSW1)                                                                                                                      |                            |                                                                                                                 |                            |                                                                                                                                     |

| Trap interrup<br>IF [INTF      | tTRAP(PC) ←<br>R = 0] THEN p                           | - (PC) + size (instr);                                                                                                                                                                                    |                            |                                                                                                                 |                            |                                                                                                                                     |

|                                |                                                        |                                                                                                                                                                                                           | Binary                     | / Mode                                                                                                          | Source                     | e Mode                                                                                                                              |

|                                | <dest>,</dest>                                         |                                                                                                                                                                                                           |                            |                                                                                                                 | <b>.</b>                   | _                                                                                                                                   |

| Mnemonic                       | <src><sup>(1)</sup></src>                              | Comments                                                                                                                                                                                                  | Bytes                      | States                                                                                                          | Bytes                      | States                                                                                                                              |

| Mnemonic<br>ACALL              | <src>(")<br/>addr11</src>                              | Comments           Absolute subroutine call                                                                                                                                                               | Bytes<br>2                 | 9 <sup>(2)(3)</sup>                                                                                             | Bytes<br>2                 |                                                                                                                                     |

| ACALL                          |                                                        |                                                                                                                                                                                                           | -                          |                                                                                                                 | ,                          | States<br>9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                                                                                 |

| ACALL                          | addr11                                                 | Absolute subroutine call                                                                                                                                                                                  | 2                          | 9 <sup>(2)(3)</sup>                                                                                             | 2                          | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                                                                                           |

| ACALL                          | addr11<br>at DRk                                       | Absolute subroutine call<br>Extended subroutine call (indirect)                                                                                                                                           | 2 3                        | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup>                                                                     | 2<br>2                     | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                                                                    |

| ACALL                          | addr11<br>at DRk<br>addr24                             | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call                                                                                                     | 2<br>3<br>5                | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup>                                             | 2<br>2<br>4                | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>9 <sup>(2)(3</sup>                                              |

| ACALL                          | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call<br>Extended subroutine call (indirect)<br>Extended subroutine call<br>Long subroutine call (indirect)                                                                            | 2<br>3<br>5<br>3           | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>10 <sup>(2)(3)</sup>                     | 2<br>2<br>4<br>2           | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>9 <sup>(2)(3</sup>                                              |

| ACALL<br>ECALL<br>LCALL<br>RET | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call         Long subroutine call (indirect)         Long subroutine call                                | 2<br>3<br>5<br>3<br>3      | $\begin{array}{c} 9^{(2)(3)} \\ 14^{(2)(3)} \\ 14^{(2)(3)} \\ 10^{(2)(3)} \\ 9^{(2)(3)} \end{array}$            | 2<br>2<br>4<br>2<br>3      | $9^{(2)(3)}$ $13^{(2)(3)}$ $13^{(2)(3)}$ $9^{(2)(3)}$ $9^{(2)(3)}$                                                                  |

| ACALL<br>ECALL<br>LCALL        | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call         Long subroutine call (indirect)         Long subroutine call         Return from subroutine | 2<br>3<br>5<br>3<br>3<br>1 | $\begin{array}{c} 9^{(2)(3)} \\ 14^{(2)(3)} \\ 14^{(2)(3)} \\ 10^{(2)(3)} \\ 9^{(2)(3)} \\ 7^{(2)} \end{array}$ | 2<br>2<br>4<br>2<br>3<br>1 | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3)</sup><br>9 <sup>(2)(3)</sup><br>9 <sup>(2)(3)</sup><br>7 <sup>(2)</sup> |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. In internal execution only, add 1 to the number of states if the destination/return address is internal and odd.

- 3. Add 2 to the number of states if the destination address is external.

- 4. Add 5 to the number of states if INTR = 1.

### Lock Bit System

The TSC87251G2D products implement 3 levels of security for User's program as described in Table 33. The TSC83251G2D products implement only the first level of security.

Level 0 is the level of an erased part and does not enable any security features.

Level 1 locks the programming of the User's internal Code Memory, the Configuration Bytes and the Encryption Array.

Level 2 locks the verifying of the User's internal Code Memory. It is always possible to verify the Configuration Bytes and the Lock Bits. It is not possible to verify the Encryption Array.

Level 3 locks the external execution.

| Level | Lock bits<br>LB[2:0] | Internal<br>Execution | External<br>Execution | Verification          | Programming | External<br>PROM read<br>(MOVC) |

|-------|----------------------|-----------------------|-----------------------|-----------------------|-------------|---------------------------------|

| 0     | 000                  | Enable                | Enable                | Enable <sup>(1)</sup> | Enable      | Enable <sup>(2)</sup>           |

| 1     | 001                  | Enable                | Enable                | Enable <sup>(1)</sup> | Disable     | Disable                         |

| 2     | 01x <sup>(3)</sup>   | Enable                | Enable                | Disable               | Disable     | Disable                         |

| 3     | 1xx <sup>(3)</sup>   | Enable                | Disable               | Disable               | Disable     | Disable                         |

Table 33. Lock Bits Programming

Notes: 1. Returns encrypted data if Encryption Array is programmed.

2. Returns non encrypted data.

3. x means don't care. Level 2 always enables level 1, and level 3 always enables levels 1 and 2.

The security level may be verified according to Table 34.

#### Table 34. Lock Bits Verifying

| Level | Lock bits Data <sup>(1)</sup> |

|-------|-------------------------------|

| 0     | xxxxx000                      |

| 1     | xxxxx001                      |

| 2     | xxxxx01x                      |

| 3     | xxxxx1xx                      |

Note: 1. x means don't care.

### **Encryption Array**

The TSC83251G2D and TSC87251G2D products include a 128-byte Encryption Array located in non-volatile memory outside the memory address space. During verification of the on-chip code memory, the seven low-order address bits also address the Encryption Array. As the byte of the code memory is read, it is exclusive-NOR'ed (XNOR) with the key byte from the Encryption Array. If the Encryption Array is not programmed (still all 1s), the user program code is placed on the data bus in its original, unencrypted form. If the Encryption Array is programmed with key bytes, the user program code is encrypted and cannot be used without knowledge of the key byte sequence.

- Then device is driving the data on Port 2.

- It is possible to alternate programming and verification operation (see Paragraph Programming Algorithm). Please make sure the voltage on the EA# pin has actually been lowered to V<sub>DD</sub> before performing the verifying operation.

- PSEN# and the other control signals have to be released to complete a sequence of verifying operations or a sequence of programming and verifying operations.

| Table 37. | Verifying | Modes |

|-----------|-----------|-------|

|-----------|-----------|-------|

| ROM Area <sup>(1)</sup> | RST | EA#/VPP | PSEN# | ALE/PROG# | P0  | P2   | P1(MSB) P3(LSB)                                 |

|-------------------------|-----|---------|-------|-----------|-----|------|-------------------------------------------------|

| On-chip code<br>memory  | 1   | 1       | 0     | 1         | 28h | Data | 16-bit Address<br>0000h-7FFFh (32<br>kilobytes) |

| Configuration Bytes     | 1   | 1       | 0     | 1         | 29h | Data | CONFIG0: FFF8h<br>CONFIG1: FFF9h                |

| Lock Bits               | 1   | 1       | 0     | 1         | 2Bh | Data | 0000h                                           |

| Signature Bytes         | 1   | 1       | 0     | 1         | 29h | Data | 0030h, 0031h, 0060h,<br>0061h                   |

Notes: 1. To preserve the secrecy of on-chip code memory when encrypted, the Encryption Array can not be verified.

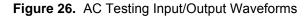

## **AC Characteristics - Commercial & Industrial**

## **AC Characteristics - External Bus Cycles**

**Definition of Symbols**

Table 38. External Bus Cycles Timing Symbol Definitions

| Signals   |  |  |  |  |  |

|-----------|--|--|--|--|--|

| Address   |  |  |  |  |  |

| Data In   |  |  |  |  |  |

| ALE       |  |  |  |  |  |

| Data Out  |  |  |  |  |  |

| RD#/PSEN# |  |  |  |  |  |

| WR#       |  |  |  |  |  |

|           |  |  |  |  |  |

| Conditions      |  |  |  |

|-----------------|--|--|--|

| High            |  |  |  |

| Low             |  |  |  |

| Valid           |  |  |  |

| No Longer Valid |  |  |  |

| Floating        |  |  |  |

|                 |  |  |  |

Timings

Test conditions: capacitive load on all pins = 50 pF.

Table 39 and Table 40 list the AC timing parameters for the TSC80251G2D derivatives with no wait states. External wait states can be added by extending PSEN#/RD#/WR# and or by extending ALE. In these tables, Note 2 marks parameters affected by one ALE wait state, and Note 3 marks parameters affected by PSEN#/RD#/WR# wait states.

Figure 8 to Figure 13 show the bus cycles with the timing parameters.

## **AC Characteristics - SSLC: SPI Interface**

### Definition of Symbols

### Table 48. SPI Interface Timing Symbol Definitions

| Signals |          |  |

|---------|----------|--|

| С       | Clock    |  |

| I       | Data In  |  |

| 0       | Data Out |  |

| S       | SS#      |  |

|   | Conditions      |  |  |  |

|---|-----------------|--|--|--|

| Н | High            |  |  |  |

| L | Low             |  |  |  |

| V | Valid           |  |  |  |

| Х | No Longer Valid |  |  |  |

| Z | Floating        |  |  |  |

### Timings

### **Table 49.** SPI Interface AC Timing; $V_{DD}$ = 2.7 to 5.5 V, $T_A$ = -40 to 85°C

| Symbol                                | Parameter                              | Min | Max | Unit             |

|---------------------------------------|----------------------------------------|-----|-----|------------------|

|                                       | Slave Mode <sup>(</sup>                | 1)  |     | 1                |

| Тснсн                                 | Clock Period                           | 8   |     | T <sub>OSC</sub> |

| T <sub>CHCX</sub>                     | Clock High Time                        | 3.2 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 3.2 |     | T <sub>osc</sub> |

| T <sub>SLCH</sub> , T <sub>SLCL</sub> | SS# Low to Clock edge                  | 200 |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 100 | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>CLSH</sub> , T <sub>CHSH</sub> | SS# High after Clock Edge              | 0   |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>SLOV</sub>                     | SS# Low to Output Data Valid           |     | 130 | ns               |

| Т <sub>знох</sub>                     | Output Data Hold after SS# High        |     | 130 | ns               |

| T <sub>SHSL</sub>                     | SS# High to SS# Low                    | (2) |     |                  |

| T <sub>ILIH</sub>                     | Input Rise Time                        |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Fall Time                        |     | 2   | μs               |

| T <sub>OLOH</sub> Output Rise time    |                                        |     | 100 | ns               |

| Т <sub>оног</sub>                     | Output Fall Time                       |     | 100 | ns               |

|                                       | Master Mode                            | (3) |     |                  |

| T <sub>CHCH</sub> Clock Period        |                                        | 4   |     | T <sub>osc</sub> |

| Т <sub>снсх</sub>                     | Clock High Time                        | 1.6 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 1.6 |     | T <sub>osc</sub> |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 50  |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 50  |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 65  | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>ILIH</sub>                     | Input Data Rise Time                   |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Data Fall Time                   |     | 2   | μs               |

| T <sub>OLOH</sub>                     | Output Data Rise time                  |     | 50  | ns               |

| T <sub>OHOL</sub>                     | Output Data Fall Time                  |     | 50  | ns               |

Notes: 1. Capacitive load on all pins = 200 pF in slave mode.

2. The value of this parameter depends on software.

3. Capacitive load on all pins = 100 pF in master mode.

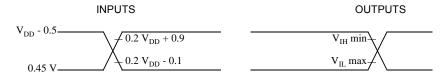

Note: For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loading  $V_{OH}/V_{OL}$  level occurs with  $I_{OL}/I_{OH} = \pm 20$  mA.

Figure 27. Float Waveforms

## Low Voltage Versions - Commercial & Industrial

| Table 56. | DC Characteristics; | V <sub>DD</sub> = 2.7 to | 5.5 V, T <sub>A</sub> : | = -40 to +85°C |

|-----------|---------------------|--------------------------|-------------------------|----------------|

|-----------|---------------------|--------------------------|-------------------------|----------------|

| Symbol              | Parameter                                                                                   | Min                       | Typical <sup>(4)</sup> | Max                       | Units | Test Conditions                                                                                                                                                                                                                    |

|---------------------|---------------------------------------------------------------------------------------------|---------------------------|------------------------|---------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>     | Input Low Voltage<br>(except EA#, SCL, SDA)                                                 | -0.5                      |                        | 0.2·V <sub>DD</sub> - 0.1 | V     |                                                                                                                                                                                                                                    |

| $V_{IL1}^{(5)}$     | Input Low Voltage<br>(SCL, SDA)                                                             | -0.5                      |                        | 0.3·V <sub>DD</sub>       | v     |                                                                                                                                                                                                                                    |

| V <sub>IL2</sub>    | Input Low Voltage<br>(EA#)                                                                  | 0                         |                        | 0.2·V <sub>DD</sub> - 0.3 | V     |                                                                                                                                                                                                                                    |

| V <sub>IH</sub>     | Input high Voltage<br>(except XTAL1, RST, SCL, SDA)                                         | 0.2·V <sub>DD</sub> + 0.9 |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                                                                                                                                    |

| $V_{\rm IH1}^{(5)}$ | Input high Voltage<br>(XTAL1, RST, SCL, SDA)                                                | 0.7·V <sub>DD</sub>       |                        | V <sub>DD</sub> + 0.5     | v     |                                                                                                                                                                                                                                    |

| V <sub>OL</sub>     | Output Low Voltage<br>(Ports 1, 2, 3)                                                       |                           |                        | 0.45                      | v     | $I_{OL} = 0.8 \text{ mA}^{(1)(2)}$                                                                                                                                                                                                 |

| V <sub>OL1</sub>    | Output Low Voltage<br>(Ports 0, ALE, PSEN#, Port 2 in Page<br>Mode during External Address) |                           |                        | 0.45                      | v     | I <sub>OL</sub> = 1.6 mA <sup>(1)(2)</sup>                                                                                                                                                                                         |

| V <sub>OH</sub>     | Output high Voltage<br>(Ports 1, 2, 3, ALE, PSEN#)                                          | 0.9·V <sub>DD</sub>       |                        |                           | V     | I <sub>OH</sub> = -10 μA <sup>(3)</sup>                                                                                                                                                                                            |

| V <sub>OH1</sub>    | Output high Voltage<br>(Port 0, Port 2 in Page Mode during<br>External Address)             | 0.9·V <sub>DD</sub>       |                        |                           | v     | Ι <sub>ΟΗ</sub> = -40 μΑ                                                                                                                                                                                                           |

| $V_{RET}$           | V <sub>DD</sub> data retention limit                                                        |                           |                        | 1.8                       | V     |                                                                                                                                                                                                                                    |

| I <sub>ILO</sub>    | Logical 0 Input Current<br>(Ports 1, 2, 3 - AWAIT#)                                         |                           |                        | - 50                      | μA    | V <sub>IN</sub> = 0.45 V                                                                                                                                                                                                           |

| I <sub>IL1</sub>    | Logical 1 Input Current<br>(NMI)                                                            |                           |                        | + 50                      | μA    | V <sub>IN</sub> = V <sub>DD</sub>                                                                                                                                                                                                  |

| I <sub>LI</sub>     | Input Leakage Current<br>(Port 0)                                                           |                           |                        | ± 10                      | μΑ    | 0.45 V < V <sub>IN</sub> < V <sub>DD</sub>                                                                                                                                                                                         |

| I <sub>TL</sub>     | Logical 1-to-0 Transition Current<br>(Ports 1, 2, 3)                                        |                           |                        | - 650                     | μA    | V <sub>IN</sub> = 2.0 V                                                                                                                                                                                                            |

| R <sub>RST</sub>    | RST Pull-Down Resistor                                                                      | 40                        | 110                    | 225                       | kΩ    |                                                                                                                                                                                                                                    |

| C <sub>IO</sub>     | Pin Capacitance                                                                             |                           | 10                     |                           | pF    | T <sub>A</sub> = 25°C                                                                                                                                                                                                              |

| I <sub>DD</sub>     | Operating Current                                                                           |                           | 4<br>8<br>9<br>11      | 8<br>11<br>12<br>14       | mA    | $\begin{array}{l} 5 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 10 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 12 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 16 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \end{array}$ |

| I <sub>DL</sub>     | Idle Mode Current                                                                           |                           | 0.5<br>1.5<br>2<br>3   | 1<br>4<br>5<br>7          | mA    | $\begin{array}{c} 5 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 10 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 12 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 16 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \end{array}$ |

| I <sub>PD</sub>     | Power-Down Current                                                                          |                           | 1                      | 10                        | μA    | V <sub>RET</sub> < V <sub>DD</sub> < 3.6 V                                                                                                                                                                                         |

Notes: 1. Under steady-state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum IOL per port pin: 10 mA

Maximum IOL per 8-bit port: Port 0 26 mA

Ports 1-315 mA

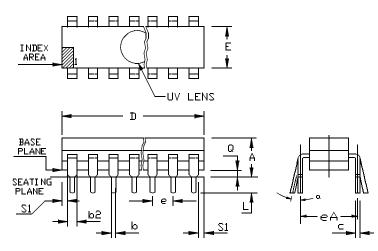

CDIL 40 with Window -Mechanical Outline

Figure 34. Ceramic Dual In Line

Table 58. CDIL Package Size

|    | ММ           |       | In          | ch     |

|----|--------------|-------|-------------|--------|

|    | Min          | Max   | Min         | Мах    |

| A  | -            | 5.71  | -           | .225   |

| b  | 0.36         | 0.58  | .014        | .023   |

| b2 | 1.14         | 1.65  | .045        | .065   |

| с  | 0.20         | 0.38  | .008        | .015   |

| D  | -            | 53.47 | -           | 2.105  |

| E  | 13.06        | 15.37 | .514        | .605   |

| e  | 2.54 B.S.C.  |       | .100 B.S.C. |        |

| eA | 15.24 B.S.C. |       | .600        | B.S.C. |

| L  | 3.18         | 5.08  | .125        | .200   |

| Q  | 0.38         | 1.40  | .015        | .055   |

| S1 | 0.13         | -     | .005        | -      |

| а  | 0 - 15       |       | 0 -         | 15     |

| Ν  |              |       | 40          |        |

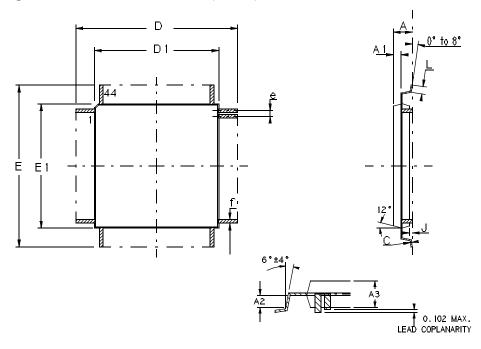

## VQFP 44 (10x10) -Mechanical Outline

Figure 37. Shrink Quad Flat Pack (Plastic)

| Table 61. | VQFP | Package Size |

|-----------|------|--------------|

|-----------|------|--------------|

|    | М        | М     | In    | ch    |

|----|----------|-------|-------|-------|

|    | Min      | Мах   | Min   | Max   |

| A  | -        | 1.60  | -     | .063  |

| A1 | 0.64     | REF   | .025  | REF   |

| A2 | 0.64     | REF   | .025  | iREF  |

| A3 | 1.35     | 1.45  | .053  | .057  |

| D  | 11.90    | 12.10 | .468  | .476  |

| D1 | 9.90     | 10.10 | .390  | .398  |

| E  | 11.90    | 12.10 | .468  | .476  |

| E1 | 9.90     | 10.10 | .390  | .398  |

| J  | 0.05     | -     | .002  | 6     |

| L  | 0.45     | 0.75  | .018  | .030  |

| е  | 0.80 BSC |       | .0315 | 5 BSC |

| f  | 0.35 BSC |       | .014  | BSC   |

### AT/TSC87251G2D OTPROM

| Part Number        | ROM                                                         | Description                                      |  |  |  |

|--------------------|-------------------------------------------------------------|--------------------------------------------------|--|--|--|

| High               | High Speed Versions 4.5 to 5.5 V, Commercial and Industrial |                                                  |  |  |  |

| TSC87251G2D-16CB   | 32K OTPROM                                                  | 16 MHz, Commercial 0° to 70°C, PLCC 44           |  |  |  |

| TSC87251G2D-24CB   | 32K OTPROM                                                  | 24 MHz, Commercial 0° to 70°C, PLCC 44           |  |  |  |

| TSC87251G2D-24CED  | 32K OTPROM                                                  | 24 MHz, Commercial 0° to 70°C, VQFP 44           |  |  |  |

| TSC87251G2D-24IA   | 32K OTPROM                                                  | 24 MHz, Industrial -40° to 85°C, PDIL 40         |  |  |  |

| TSC87251G2D-24IB   | 32K OTPROM                                                  | 24 MHz, Industrial -40° to 85°C, PLCC 44         |  |  |  |

| AT87251G2D-SLSUM   | 32K OTPROM                                                  | 24 MHz, Industrial & Green -40° to 85°C, PLCC 44 |  |  |  |

| AT87251G2D-3CSUM   | 32K OTPROM                                                  | 24 MHz, Industrial & Green -40° to 85°C, PDIL 40 |  |  |  |

| AT87251G2D-RLTUM   | 32K OTPROM                                                  | 24 MHz, Industrial & Green -40° to 85°C, VQFP 44 |  |  |  |

|                    | Low Volta                                                   | ge Versions 2.7 to 5.5 V                         |  |  |  |

| TSC87251G2D-L16CB  | 32K OTPROM                                                  | 16 MHz, Commercial 0° to 70°C, PLCC 44           |  |  |  |

| TSC87251G2D-L16CED | 32K OTPROM                                                  | 16 MHz, Commercial 0° to 70°C, VQFP 44           |  |  |  |

| AT87251G2D-SLSUL   | 32K OTPROM                                                  | 16 MHz, Industrial & Green, 0° to 70°C, PLCC 44  |  |  |  |

| AT87251G2D-RLTUL   | 32K OTPROM                                                  | 16 MHz, Industrial & Green, 0° to 70°C, VQFP 44  |  |  |  |

## **Document Revision History**

**Changes from** 1. Added automotive qualification, and ordering information for ROM product version.

- 4135D to 4135E

- 1. Absolute Maximum Ratings added for automotive product version.

Changes from 4135E to 4135F

AIMEL