# E·XFL

### Atmel - AT80251G2D-SLRUM Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | C251                                                        |

| Core Size                  | 8/16-Bit                                                    |

| Speed                      | 24MHz                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, Microwire, SPI, UART/USART       |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 32                                                          |

| Program Memory Size        | -                                                           |

| Program Memory Type        | ROMIess                                                     |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 44-LCC (J-Lead)                                             |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at80251g2d-slrum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

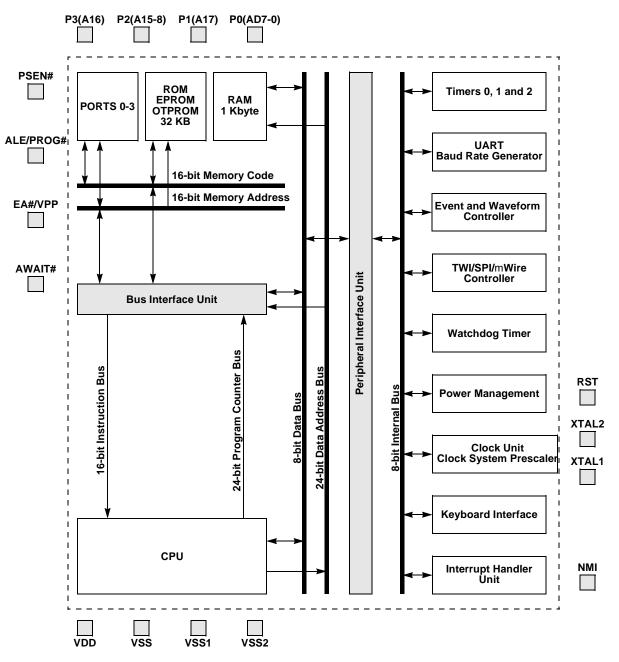

### **Block Diagram**

| Table 2 | Product Name | Signal Description | (Continued) |

|---------|--------------|--------------------|-------------|

|---------|--------------|--------------------|-------------|

|                | Tiouu | ct Name Signal Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |

|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Signal<br>Name | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Alternate<br>Function |

| NMI            | I     | Non Maskable Interrupt<br>Holding this pin high for 24 oscillator periods triggers an interrupt.<br>When using the Product Name as a pin-for-pin replacement for a 8xC51<br>product, NMI can be unconnected without loss of compatibility or power<br>consumption increase (on-chip pull-down).<br>Not available on DIP package.                                                                                                                                                                                                               | -                     |

| P0.0:7         | I/O   | <b>Port 0</b><br>P0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs. To avoid any paraitic current consumption, Floating P0 inputs must be polarized to $V_{DD}$ or $V_{SS}$ .                                                                                                                                                                                                                                                                          | AD7:0                 |

| P1.0:7         | I/O   | <b>Port 1</b><br>P1 is an 8-bit bidirectional I/O port with internal pull-ups. P1 provides interrupt capability for a keyboard interface.                                                                                                                                                                                                                                                                                                                                                                                                      | _                     |

| P2.0:7         | I/O   | Port 2<br>P2 is an 8-bit bidirectional I/O port with internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A15:8                 |

| P3.0:7         | I/O   | <b>Port 3</b><br>P3 is an 8-bit bidirectional I/O port with internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                     |

| PROG#          | I     | <b>Programming Pulse input</b><br>The programming pulse is applied to this input for programming the on-chip<br>EPROM/OTPROM.                                                                                                                                                                                                                                                                                                                                                                                                                  | Ι                     |

| PSEN#          | 0     | Program Store Enable/Read signal output<br>PSEN# is asserted for a memory address range that depends on bits RD0<br>and RD1 in UCONFIG0 byte (see ).                                                                                                                                                                                                                                                                                                                                                                                           | _                     |

| RD#            | 0     | Read or 17 <sup>th</sup> Address Bit (A16)<br>Read signal output to external data memory depending on the values of<br>bits RD0 and RD1 in UCONFIG0 byte (see Table 13, Page 20).                                                                                                                                                                                                                                                                                                                                                              | P3.7                  |

| RST            | I     | <b>Reset input to the chip</b><br>Holding this pin high for 64 oscillator periods while the oscillator is running<br>resets the device. The Port pins are driven to their reset conditions when a<br>voltage greater than $V_{IH1}$ is applied, whether or not the oscillator is running.<br>This pin has an internal pull-down resistor which allows the device to be<br>reset by connecting a capacitor between this pin and VDD.<br>Asserting RST when the chip is in Idle mode or Power-Down mode returns<br>the chip to normal operation. | _                     |

| RXD            | I/O   | <b>Receive Serial Data</b><br>RXD sends and receives data in serial I/O mode 0 and receives data in<br>serial I/O modes 1, 2 and 3.                                                                                                                                                                                                                                                                                                                                                                                                            | P3.0                  |

| SCL            | I/O   | TWI Serial Clock<br>When TWI controller is in master mode, SCL outputs the serial clock to<br>slave peripherals. When TWI controller is in slave mode, SCL receives<br>clock from the master controller.                                                                                                                                                                                                                                                                                                                                       | P1.6                  |

| SCK            | I/O   | <b>SPI Serial Clock</b><br>When SPI is in master mode, SCK outputs clock to the slave peripheral.<br>When SPI is in slave mode, SCK receives clock from the master controller.                                                                                                                                                                                                                                                                                                                                                                 | P1.6                  |

| SDA            | I/O   | TWI Serial Data<br>SDA is the bidirectional TWI data line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P1.7                  |

| SS#            | I     | SPI Slave Select Input<br>When in Slave mode, SS# enables the slave mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P1.4                  |

### Special Function Registers

The Special Function Registers (SFRs) of the TSC80251G2D derivatives fall into the categories detailed in Table 1 to Table 9.

SFRs are placed in a reserved on-chip memory region S: which is not represented in the data memory mapping (Figure 5). The relative addresses within S: of these SFRs are provided together with their reset values in Table . They are upward compatible with the SFRs of the standard 80C51 and the Intel's 80C251Sx family. In this table, the C251 core registers are identified by Note 1 and are described in the TSC80251 Programmer's Guide. The other SFRs are described in the TSC80251G1D Design Guide. All the SFRs are bit-addressable using the C251 instruction set.

#### Table 1. C251 Core SFRs

| Mnemonic           | Name                       |

|--------------------|----------------------------|

| ACC <sup>(1)</sup> | Accumulator                |

| B <sup>(1)</sup>   | B Register                 |

| PSW                | Program Status Word        |

| PSW1               | Program Status Word 1      |

| SP <sup>(1)</sup>  | Stack Pointer - LSB of SPX |

| Mnemonic            | Name                                                     |

|---------------------|----------------------------------------------------------|

| SPH <sup>(1)</sup>  | Stack Pointer High - MSB of<br>SPX                       |

| DPL <sup>(1)</sup>  | Data Pointer Low byte - LSB of DPTR                      |

| DPH <sup>(1)</sup>  | Data Pointer High byte - MSB of DPTR                     |

| DPXL <sup>(1)</sup> | Data Pointer Extended Low<br>byte of DPX - Region number |

Note: 1. These SFRs can also be accessed by their corresponding registers in the register file.

### Table 2. I/O Port SFRs

| Mnemonic | Name   |

|----------|--------|

| P0       | Port 0 |

| P1       | Port 1 |

# MnemonicNameP2Port 2P3Port 3

### Table 3. Timers SFRs

| Mnemonic | Name                             |

|----------|----------------------------------|

| TL0      | Timer/Counter 0 Low<br>Byte      |

| TH0      | Timer/Counter 0 High<br>Byte     |

| TL1      | Timer/Counter 1 Low<br>Byte      |

| TH1      | Timer/Counter 1 High<br>Byte     |

| TL2      | Timer/Counter 2 Low<br>Byte      |

| TH2      | Timer/Counter 2 High<br>Byte     |

| TCON     | Timer/Counter 0 and 1<br>Control |

| Mnemonic | Name                                           |

|----------|------------------------------------------------|

| TMOD     | Timer/Counter 0 and 1<br>Modes                 |

| T2CON    | Timer/Counter 2<br>Control                     |

| T2MOD    | Timer/Counter 2 Mode                           |

| RCAP2L   | Timer/Counter 2<br>Reload/Capture Low<br>Byte  |

| RCAP2H   | Timer/Counter 2<br>Reload/Capture High<br>Byte |

| WDTRST   | WatchDog Timer Reset                           |

### Table 7. System Management SFRs

| Mnemonic | Name             |

|----------|------------------|

| PCON     | Power Control    |

| POWM     | Power Management |

| Mnemonic | Name                                        |

|----------|---------------------------------------------|

| CKRL     | Clock Reload                                |

| WCON     | Synchronous Real-Time Wait State<br>Control |

### Table 8. Interrupt SFRs

| Mnemonic | Name                              |

|----------|-----------------------------------|

| IE0      | Interrupt Enable Control 0        |

| IE1      | Interrupt Enable Control 1        |

| IPH0     | Interrupt Priority Control High 0 |

| Table 9. Keyb | oard Interface | SFRs |

|---------------|----------------|------|

|---------------|----------------|------|

| Mnemonic | Name                          |

|----------|-------------------------------|

| P1IE     | Port 1 Input Interrupt Enable |

| P1F      | Port 1 Flag                   |

| IPH1                                  | Interrupt Priority Control High 1 |

|---------------------------------------|-----------------------------------|

| IPL1 Interrupt Priority Control Low 1 |                                   |

|                                       |                                   |

|                                       |                                   |

Interrupt Priority Control Low 0

Mnemonic Name

IPL0

| Mnemonic | Name                   |

|----------|------------------------|

| P1LS     | Port 1 Level Selection |

### **Configuration Bytes**

The TSC80251G2D derivatives provide user design flexibility by configuring certain operating features at device reset. These features fall into the following categories:

- external memory interface (Page mode, address bits, programmed wait states and the address range for RD#, WR#, and PSEN#)

- source mode/binary mode opcodes

- selection of bytes stored on the stack by an interrupt

- mapping of the upper portion of on-chip code memory to region 00:

Two user configuration bytes UCONFIG0 (see Table 11) and UCONFIG1 (see Table 12) provide the information.

When EA# is tied to a low level, the configuration bytes are fetched from the external address space. The TSC80251G2D derivatives reserve the top eight bytes of the memory address space (FF:FFF8h-FF:FFFh) for an external 8-byte configuration array. Only two bytes are actually used: UCONFIG0 at FF:FFF8h and UCONFIG1 at FF:FFF9h.

For the mask ROM devices, configuration information is stored in on-chip memory (see ROM Verifying). When EA# is tied to a high level, the configuration information is retrieved from the on-chip memory instead of the external address space and there is no restriction in the usage of the external memory.

### **Configuration Byte 1**

### Table 13. Address Ranges and Usage of RD#, WR# and PSEN# Signals

| RD1 | RD0 | P1.7    | P3.7/RD#                                     | PSEN#                                               | WR#                                                  | External<br>Memory       |

|-----|-----|---------|----------------------------------------------|-----------------------------------------------------|------------------------------------------------------|--------------------------|

| 0   | 0   | A17     | A16                                          | Read signal for all<br>external memory<br>locations | Write signal for all<br>external memory<br>locations | 256 KB                   |

| 0   | 1   | I/O pin | A16                                          | Read signal for all external memory locations       | Write signal for all<br>external memory<br>locations | 128 KB                   |

| 1   | 0   | I/O pin | I/O pin                                      | Read signal for all external memory locations       | Write signal for all external memory locations       | 64 KB                    |

| 1   | 1   | I/O pin | Read<br>signal for<br>regions 00:<br>and 01: | Read signal for<br>regions FE: and FF:              | Write signal for all<br>external memory<br>locations | 2 × 64 KB <sup>(1)</sup> |

Notes: 1. This selection provides compatibility with the standard 80C51 hardware which has separate external memory spaces for data and code.

| Register                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C251 | C51 |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| at Ri                                                       | A memory location (00h-FFh) addressed indirectly via byte registers<br>R0 or R1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _    | 3   |

| Rn<br>n                                                     | Byte register R0-R7 of the currently selected register bank<br>Byte register index: n = 0-7                                                                                                                                                                                                                                                                                                                                                                                                                                      | _    | 3   |

| Rm<br>Rmd<br>Rms<br>m, md, ms                               | Byte register R0-R15 of the currently selected register file<br>Destination register<br>Source register<br>Byte register index: m, md, ms = 0-15                                                                                                                                                                                                                                                                                                                                                                                 |      | -   |

| WRj<br>WRjd<br>WRjs<br>at WRj<br>at WRj +dis16<br>j, jd, js | Word register WR0, WR2,, WR30 of the currently selected register<br>file<br>Destination register<br>Source register<br>A memory location (00:0000h-00:FFFFh) addressed indirectly<br>through word register WR0-WR30, is the target address for jump<br>instructions.<br>A memory location (00:0000h-00:FFFFh) addressed indirectly<br>through word register (WR0-WR30) + 16-bit signed (two's<br>complement) displacement value<br>Word register index: j, jd, js = 0-30                                                         | 3    | _   |

| DRk<br>DRkd<br>DRks<br>at DRk<br>at DRk +dis16<br>k, kd, ks | Dword register DR0, DR4,, DR28, DR56, DR60 of the currently<br>selected register file<br>Destination register<br>Source register<br>A memory location (00:0000h-FF:FFFFh) addressed indirectly<br>through dword register DR0-DR28, DR56 and DR60, is the target<br>address for jump instruction<br>A memory location (00:0000h-FF:FFFFh) addressed indirectly<br>through dword register (DR0-DR28, DR56, DR60) + 16-bit (two's<br>complement) signed displacement value<br>Dword register index: k, kd, ks = 0, 4, 8, 28, 56, 60 | 3    | _   |

#### Table 19. Notation for Register Operands

## Size and Execution Time for Instruction Families

### Table 20. Summary of Add and Subtract Instructions

| AddADD <dest>, <src>dest opnd <math>\leftarrow</math> dest opnd + src opnd</src></dest>                       |

|---------------------------------------------------------------------------------------------------------------|

| SubtractSUB <dest>, <src>dest opnd <math display="inline">\leftarrow</math> dest opnd - src opnd</src></dest> |

| Add with CarryADDC <dest>, <src>(A) <math>\leftarrow</math> (A) + src opnd + (CY)</src></dest>                |

| Subtract with BorrowSUBB <dest>, <src>(A) <math>\leftarrow</math> (A) - src opnd - (CY)</src></dest>          |

|               | -dost>                                       |                                                               | Binary | Mode             | Source Mode |                  |

|---------------|----------------------------------------------|---------------------------------------------------------------|--------|------------------|-------------|------------------|

| Mnemonic      | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                                      | Bytes  | States           | Bytes       | States           |

|               | A, Rn                                        | Register to ACC                                               | 1      | 1                | 2           | 2                |

|               | A, dir8                                      | Direct address to ACC                                         | 2      | 1 <sup>(2)</sup> | 2           | 1 <sup>(2)</sup> |

| ADD           | A, at Ri                                     | Indirect address to ACC                                       | 1      | 2                | 2           | 3                |

|               | A, #data                                     | Immediate data to ACC                                         | 2      | 1                | 2           | 1                |

|               | Rmd, Rms                                     | Byte register to/from byte register                           | 3      | 2                | 2           | 1                |

|               | WRjd, WRjs                                   | Word register to/from word register                           | 3      | 3                | 2           | 2                |

|               | DRkd, DRks                                   | Dword register to/from dword register                         | 3      | 5                | 2           | 4                |

|               | Rm, #data                                    | Immediate 8-bit data to/from byte register                    | 4      | 3                | 3           | 2                |

|               | WRj, #data16                                 | Immediate 16-bit data to/from word register                   | 5      | 4                | 4           | 3                |

|               | DRk,<br>#0data16                             | 16-bit unsigned immediate data to/from dword register         | 5      | 6                | 4           | 5                |

| ADD/SUB       | Rm, dir8                                     | Direct address (on-chip RAM or SFR)<br>to/from byte register  | 4      | 3 <sup>(2)</sup> | 3           | 2 <sup>(2)</sup> |

|               | WRj, dir8                                    | Direct address (on-chip RAM or SFR) to/from word register     | 4      | 4                | 3           | 3                |

|               | Rm, dir16                                    | Direct address (64K) to/from byte<br>register                 | 5      | 3 <sup>(3)</sup> | 4           | 2 <sup>(3)</sup> |

|               | WRj, dir16                                   | Direct address (64K) to/from word register                    | 5      | 4 <sup>(4)</sup> | 4           | 3 <sup>(4)</sup> |

|               | Rm, at WRj                                   | Indirect address (64K) to/from byte register                  | 4      | 3 <sup>(3)</sup> | 3           | 2 <sup>(3)</sup> |

|               | Rm, at DRk                                   | Indirect address (16M) to/from byte register                  | 4      | 4 <sup>(3)</sup> | 3           | 3 <sup>(3)</sup> |

|               | A, Rn                                        | Register to/from ACC with carry                               | 1      | 1                | 2           | 2                |

| ADDC/SU<br>BB | A, dir8                                      | Direct address (on-chip RAM or SFR)<br>to/from ACC with carry | 2      | 1 <sup>(2)</sup> | 2           | 1 <sup>(2)</sup> |

|               | A, at Ri                                     | Indirect address to/from ACC with carry                       | 1      | 2                | 2           | 3                |

|               | A, #data                                     | Immediate data to/from ACC with carry                         | 2      | 1                | 2           | 1                |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

3. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

4. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

$IncrementINC < dest>dest opnd \leftarrow dest opnd + 1$

IncrementINC <dest>, <src>dest opnd  $\leftarrow$  dest opnd + src opnd

$DecrementDEC < dest>dest opnd \leftarrow dest opnd - 1$

$\texttt{DecrementDEC <dest>, <src>dest opnd \leftarrow dest opnd - src opnd}$

|            |                                              |                                          | Binary Mode |                  | Source Mode |                  |

|------------|----------------------------------------------|------------------------------------------|-------------|------------------|-------------|------------------|

| Mnemonic   | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                 | Bytes       | States           | Bytes       | States           |

|            | A                                            | ACC by 1                                 | 1           | 1                | 1           | 1                |

|            | Rn                                           | Register by 1                            | 1           | 1                | 2           | 2                |

| INC<br>DEC | dir8                                         | Direct address (on-chip RAM or SFR) by 1 | 2           | 2 <sup>(2)</sup> | 2           | 2 <sup>(2)</sup> |

|            | at Ri                                        | Indirect address by 1                    | 1           | 3                | 2           | 4                |

| INC        | Rm, #short                                   | Byte register by 1, 2, or 4              | 3           | 2                | 2           | 1                |

| DEC        | WRj, #short                                  | Word register by 1, 2, or 4              | 3           | 2                | 2           | 1                |

| INC        | DRk, #short                                  | Double word register by 1, 2, or 4       | 3           | 4                | 2           | 3                |

| DEC        | DRk, #short                                  | Double word register by 1, 2, or 4       | 3           | 5                | 2           | 4                |

| INC        | DPTR                                         | Data pointer by 1                        | 1           | 1                | 1           | 1                |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

$\texttt{Logical AND}^{(1)}\texttt{ANL <dest>, <src>dest opnd \leftarrow dest opnd \Lambda \ src opnd$ Logical OR<sup>(1)</sup>ORL <dest>, <src>dest opnd  $\leftarrow$  dest opnd  $\varsigma$  src opnd  $\texttt{Logical Exclusive OR^{(1)}XRL <dest>, <src>dest opnd \leftarrow dest opnd \forall src opnd }$ Clear<sup>(1)</sup>CLR A(A)  $\leftarrow$  0 Complement<sup>(1)</sup>CPL A(A)  $\leftarrow \emptyset$  (A) Rotate LeftRL  $A(A)_{n+1} \leftarrow (A)_n$ , n = 0..6  $(\mathsf{A})_0 \gets (\mathsf{A})_7$ Rotate Left CarryRLC  $A(A)_{n+1} \leftarrow (A)_n$ , n = 0..6  $(CY) \leftarrow (A)_7$  $(A)_0 \leftarrow (CY)$ Rotate RightRR  $A(A)_{n-1} \leftarrow (A)_n$ , n = 7..1  $(A)_7 \leftarrow (A)_0$ Rotate Right CarryRRC  $A(A)_{n-1} \leftarrow (A)_n$ , n = 7..1  $(CY) \leftarrow (A)_0$  $(A)_7 \leftarrow (CY)$

|          |                                          |                                                      | Binary | Mode             | Source Mode |                  |  |

|----------|------------------------------------------|------------------------------------------------------|--------|------------------|-------------|------------------|--|

| Mnemonic | <dest>, <src><sup>(1)</sup></src></dest> | Comments                                             | Bytes  | States           | Bytes       | States           |  |

|          | A, Rn                                    | register to ACC                                      | 1      | 1                | 2           | 2                |  |

|          | A, dir8                                  | Direct address (on-chip RAM or SFR) to ACC           | 2      | 1 <sup>(3)</sup> | 2           | 1 <sup>(3)</sup> |  |

|          | A, at Ri                                 | Indirect address to ACC                              | 1      | 2                | 2           | 3                |  |

|          | A, #data                                 | Immediate data to ACC                                | 2      | 1                | 2           | 1                |  |

|          | dir8, A                                  | ACC to direct address                                | 2      | 2 <sup>(4)</sup> | 2           | 2 <sup>(4)</sup> |  |

|          | dir8, #data                              | Immediate 8-bit data to direct address               | 3      | 3(4)             | 3           | 3(4)             |  |

|          | Rmd, Rms                                 | Byte register to byte register                       | 3      | 2                | 2           | 1                |  |

| ANL      | WRjd, WRjs                               | Word register to word register                       | 3      | 3                | 2           | 2                |  |

| ORL      | Rm, #data                                | Immediate 8-bit data to byte register                | 4      | 3                | 3           | 2                |  |

| XRL      | WRj, #data16                             | Immediate 16-bit data to word register               | 5      | 4                | 4           | 3                |  |

|          | Rm, dir8                                 | Direct address (on-chip RAM or SFR) to byte register | 4      | 3 <sup>(3)</sup> | 3           | 2 <sup>(3)</sup> |  |

|          | WRj, dir8                                | Direct address (on-chip RAM or SFR) to word register | 4      | 4                | 3           | 3                |  |

|          | Rm, dir16                                | Direct address (64K) to byte register                | 5      | 3 <sup>(5)</sup> | 4           | 2 <sup>(5)</sup> |  |

|          | WRj, dir16                               | Direct address (64K) to word register                | 5      | 4 <sup>(6)</sup> | 4           | 3 <sup>(6)</sup> |  |

|          | Rm, at WRj                               | Indirect address (64K) to byte register              | 4      | 3 <sup>(5)</sup> | 3           | 2 <sup>(5)</sup> |  |

|          | Rm, at DRk                               | Indirect address (16M) to byte register              | 4      | 4 <sup>(5)</sup> | 3           | 3 <sup>(5)</sup> |  |

| CLR      | А                                        | Clear ACC                                            | 1      | 1                | 1           | 1                |  |

| CPL      | A                                        | Complement ACC                                       | 1      | 1                | 1           | 1                |  |

| RL       | A                                        | Rotate ACC left                                      | 1      | 1                | 1           | 1                |  |

| RLC      | A                                        | Rotate ACC left through CY                           | 1      | 1                | 1           | 1                |  |

| RR       | A                                        | Rotate ACC right                                     | 1      | 1                | 1           | 1                |  |

| RRC      | A                                        | Rotate ACC right through CY                          | 1      | 1                | 1           | 1                |  |

5

5

11

10

10

20

1

| Table 24. | Summary of Multiply | y, Divide and Decimal-adjust Instructions |

|-----------|---------------------|-------------------------------------------|

|-----------|---------------------|-------------------------------------------|

MultiplyMUL AB(B:A)  $\leftarrow$  (A)×(B) MUL <dest>, <src>extended dest opnd  $\leftarrow$  dest opnd  $\times$  src opnd DivideDIV AB(A)  $\leftarrow$  Quotient ((A)/(B)) (B)  $\leftarrow$  Remainder ((A)/(B)) DivideDIV <dest>, <src>ext. dest opnd high ← Quotient (dest opnd / src opnd) ext. dest opnd low ← Remainder (dest opnd / src opnd) Decimal-adjust ACCDA AIF [[(A)<sub>3:0</sub> > 9]  $\vee$  [(AC) = 1]] for Addition (BCD) THEN  $(A)_{3:0} \leftarrow (A)_{3:0} + 6$  laffects CY;  $\mathsf{IF} [[(A)_{7:4} > 9] \lor [(CY) = 1]]$ THEN  $(A)_{7:4} \leftarrow (A)_{7:4} + 6$ **Binary Mode** Source Mode <dest>, <src>(1) Bytes Mnemonic Comments Bytes States States AB Multiply A and B 1 5 1 MUL Rmd, Rms Multiply byte register and byte register 3 6 2 WRjd, WRjs Multiply word register and word register 3 12 2 AB 1 10 1 Divide A and B DIV Rmd, Rms Divide byte register and byte register 3 11 2 WRjd, WRjs 3 21 2 Divide word register and word register DA А Decimal adjust ACC 1 1 1

1. A shaded cell denotes an instruction in the C51 Architecture. Note:

### Table 25. Summary of Move Instructions (1/3)

| Move to High wordMOVH <dest>, <src>dest opnd<sub><math>31:16 \leftarrow src opnd</math></sub></src></dest>                          |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Move with Sign extensionMOVS <dest>, <src>dest opnd <math>\leftarrow</math> src opnd with sign extend</src></dest>                  |

| Move with Zero extensionMOVZ <dest>, <src>dest opnd <math display="inline">\leftarrow</math> src opnd with zero extend</src></dest> |

| Move CodeMOVC A, $<$ src>(A) $\leftarrow$ src opnd                                                                                  |

|                                                                                                                                     |

Move eXtendedMOVX <dest>, <src>dest opnd  $\leftarrow$  src opnd

|          | dosta                                        |                                                         | Binary | Mode             | Source Mode |                  |

|----------|----------------------------------------------|---------------------------------------------------------|--------|------------------|-------------|------------------|

| Mnemonic | <dest>,<br/><src><sup>(2)</sup></src></dest> | Comments                                                | Bytes  | States           | Bytes       | States           |

| MOVH     | DRk, #data16                                 | 16-bit immediate data into upper word of dword register | 5      | 3                | 4           | 2                |

| MOVS     | WRj, Rm                                      | Byte register to word register with sign extension      | 3      | 2                | 2           | 1                |

| MOVZ     | WRj, Rm                                      | Byte register to word register with zeros extension     | 3      | 2                | 2           | 1                |

| MOVC     | A, at A +DPTR                                | Code byte relative to DPTR to ACC                       | 1      | 6 <sup>(3)</sup> | 1           | 6 <sup>(3)</sup> |

|          | A, at A +PC                                  | Code byte relative to PC to ACC                         | 1      | 6 <sup>(3)</sup> | 1           | 6 <sup>(3)</sup> |

|          | A, at Ri                                     | Extended memory (8-bit address) to ACC <sup>(2)</sup>   | 1      | 4                | 1           | 5                |

| MOVX     | A, at DPTR                                   | Extended memory (16-bit address) to ACC <sup>(2)</sup>  | 1      | 3 <sup>(4)</sup> | 1           | 3 <sup>(4)</sup> |

|          | at Ri, A                                     | ACC to extended memory (8-bit address) <sup>(2)</sup>   | 1      | 4                | 1           | 4                |

|          | at DPTR, A                                   | ACC to extended memory (16-bit address) <sup>(2)</sup>  | 1      | 4 <sup>(3)</sup> | 1           | 4 <sup>(3)</sup> |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. Extended memory addressed is in the region specified by DPXL (reset value = 01h).

- 3. If this instruction addresses external memory location, add N+1 to the number of states (N: number of wait states).

- 4. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

| MOV | WRj, at WRj<br>+dis24 | Indirect with 16-bit displacement (16M) to word register | 5 | 8 <sup>(5)</sup> | 4 | 7 <sup>(5)</sup> |

|-----|-----------------------|----------------------------------------------------------|---|------------------|---|------------------|

| MOV | at WRj +dis16,<br>Rm  | Byte register to indirect with 16-bit displacement (64K) | 5 | 6 <sup>(4)</sup> | 4 | 5(4)             |

| MOV | at WRj +dis16,<br>WRj | Word register to indirect with 16-bit displacement (64K) | 5 | 7 <sup>(5)</sup> | 4 | 6 <sup>(5)</sup> |

| MOV | at DRk +dis24,<br>Rm  | Byte register to indirect with 16-bit displacement (16M) | 5 | 7 <sup>(4)</sup> | 4 | 6 <sup>(4)</sup> |

| MOV | at DRk +dis24,<br>WRj | Word register to indirect with 16-bit displacement (16M) | 5 | 8(5)             | 4 | 7 <sup>(5)</sup> |

Notes: 1. Instructions that move bits are in Table 27.

2. Move instructions unique to the C251 Architecture.

3. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

4. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

5. If this instruction addresses external memory location, add 2(N+1) to the number of states (N: number of wait states).

6. If this instruction addresses external memory location, add 4(N+2) to the number of states (N: number of wait states).

| Table 30. Summary of Conditional Jump Instructions (2 | Table 30. | Summary | f Conditiona | I Jump | Instructions | (2/2) |

|-------------------------------------------------------|-----------|---------|--------------|--------|--------------|-------|

|-------------------------------------------------------|-----------|---------|--------------|--------|--------------|-------|

| Jump if bitJB <src>, rel(PC) <math>\leftarrow</math> (PC) + size (instr);<br/>IF [src opnd = 1] THEN (PC) <math>\leftarrow</math> (PC) + rel</src>                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jump if not bitJNB <src>, rel(PC) ← (PC) + size (instr);<br/>IF [src opnd = 0] THEN (PC) ← (PC) + rel</src>                                                                                                                                                                                                            |

| Jump if bit and clearJBC <dest>, rel(PC) ← (PC) + size (instr);<br/>IF [dest opnd = 1] THEN<br/>dest opnd ← 0<br/>(PC) ← (PC) + rel</dest>                                                                                                                                                                             |

| Jump if accumulator is zeroJZ rel(PC) $\leftarrow$ (PC) + size (instr);<br>IF [(A) = 0] THEN (PC) $\leftarrow$ (PC) + rel                                                                                                                                                                                              |

| Jump if accumulator is not zeroJNZ rel(PC) ← (PC) + size (instr);<br>IF [(A) $\neq$ 0] THEN (PC) ← (PC) + rel                                                                                                                                                                                                          |

| $\begin{array}{l} \mbox{Compare and jump if not equalCJNE , , rel(PC) \leftarrow (PC) + size (instr);} \\ \mbox{IF [src opnd1 < src opnd2] THEN (CY) \leftarrow 1} \\ \mbox{IF [src opnd1 \geq src opnd2] THEN (CY) \leftarrow 0} \\ \mbox{IF [src opnd1 \neq src opnd2] THEN (PC) \leftarrow (PC) + rel} \end{array}$ |

| Decrement and jump if not zero $NZ < dect > rel(PC) < (PC) + size (instr); dect or$                                                                                                                                                                                                                                    |

Decrement and jump if not zeroDJNZ <dest>, rel(PC)  $\leftarrow$  (PC) + size (instr); dest opnd  $\leftarrow$  dest opnd -1; IF [ $\phi$  (Z)] THEN (PC)  $\leftarrow$  (PC) + rel

|          |                                          |                                                               | Binary | Mode <sup>(2)</sup>        | Source | Mode <sup>(2)</sup>   |

|----------|------------------------------------------|---------------------------------------------------------------|--------|----------------------------|--------|-----------------------|

| Mnemonic | <dest>, <src><sup>(1)</sup></src></dest> | Comments                                                      | Bytes  | States                     | Bytes  | States                |

|          | bit51, rel                               | Jump if direct bit is set                                     | 3      | 2/5 <sup>(3)(6)</sup>      | 3      | 2/5 <sup>(3)(6)</sup> |

| JB       | bit, rel                                 | Jump if direct bit of 8-bit address location is set           | 5      | 4/7 <sup>(3)(6)</sup>      | 4      | 3/6 <sup>(3)(6)</sup> |

|          | bit51, rel                               | Jump if direct bit is not set                                 | 3      | 2/5 <sup>(3)(6)</sup>      | 3      | 2/5 <sup>(3)(6)</sup> |

| JNB      | bit, rel                                 | Jump if direct bit of 8-bit address location is not set       | 5      | 4/7 <sup>(3)(6)</sup>      | 4      | 3/6 <sup>(3)</sup>    |

|          | bit51, rel                               | Jump if direct bit is set & clear bit                         | 3      | 4/7 <sup>(5)(6)</sup>      | 3      | 4/7 <sup>(5)(6)</sup> |

| JBC      | bit, rel                                 | Jump if direct bit of 8-bit address location is set and clear | 5      | 7/10 <sup>(5)(</sup><br>6) | 4      | 6/9 <sup>(5)(6)</sup> |

| JZ       | rel                                      | Jump if ACC is zero                                           | 2      | 2/5 <sup>(6)</sup>         | 2      | 2/5 <sup>(6)</sup>    |

| JNZ      | rel                                      | Jump if ACC is not zero                                       | 2      | 2/5 <sup>(6)</sup>         | 2      | 2/5 <sup>(6)</sup>    |

|          | A, dir8, rel                             | Compare direct address to ACC and jump if not equal           | 3      | 2/5 <sup>(3)(6)</sup>      | 3      | 2/5 <sup>(3)(6)</sup> |

| CJNE     | A, #data, rel                            | Compare immediate to ACC and jump if not equal                | 3      | 2/5 <sup>(6)</sup>         | 3      | 2/5 <sup>(6)</sup>    |

| CONC     | Rn, #data, rel                           | Compare immediate to register and jump if not equal           | 3      | 2/5 <sup>(6)</sup>         | 4      | 3/6 <sup>(6)</sup>    |

|          | at Ri, #data, rel                        | Compare immediate to indirect and jump if not equal           | 3      | 3/6 <sup>(6)</sup>         | 4      | 4/7 <sup>(6)</sup>    |

| DJNZ     | Rn, rel                                  | Decrement register and jump if not zero                       | 2      | 2/5 <sup>(6)</sup>         | 3      | 3/6 <sup>(6)</sup>    |

| DJINZ    | dir8, rel                                | Decrement direct address and jump if not zero                 | 3      | 3/6 <sup>(4)(6)</sup>      | 3      | 3/6 <sup>(4)(6)</sup> |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. States are given as jump not-taken/taken.

- 3. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 4. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states.

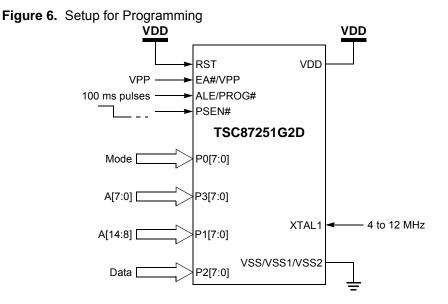

• PSEN# and the other control signals have to be released to complete a sequence of programming operations or a sequence of programming and verifying operations.

Table 36.

Programming Modes

| ROM Area <sup>(1)</sup> | RST | EA#/VPP         | PSEN<br># | ALE/PROG# <sup>(2)</sup> | P0  | P2   | P1(MSB) P3(LSB)                                 |

|-------------------------|-----|-----------------|-----------|--------------------------|-----|------|-------------------------------------------------|

| On-chip Code<br>Memory  | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 68h | Data | 16-bit Address<br>0000h-7FFFh (32<br>kilobytes) |

| Configuration<br>Bytes  | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 69h | Data | CONFIG0: FFF8h<br>CONFIG1: FFF9h                |

| Lock Bits               | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 6Bh | х    | LB0: 0001h<br>LB1: 0002h<br>LB2: 0003h          |

| Encryption Array        | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 6Ch | Data | 0000h-007Fh                                     |

Notes: 1. Signature Bytes are not user-programmable.

2. The ALE/PROG# pulse waveform is shown in Figure 23 page 59.

### **Verify Algorithm**

Figure 7 shows the hardware setup needed to verify the TSC87251G2D EPROM/OTPROM or TSC83251G2D ROM areas:

- The chip has to be put under reset and maintained in this state until the completion of the verifying sequence.

- PSEN# and the other control signals (ALE and Port 0) have to be set to a high level.

- Then PSEN# has to be to forced to a low level after two clock cycles or more and it

has to be maintained in this state until the completion of the verifying sequence (see

below).

- The voltage on the EA# pin must be set to V<sub>DD</sub> and ALE must be set to a high level.

- The Verifying Mode is selected according to the code applied on Port 0. It has to be applied until the completion of this verifying operation.

- The verifying address is applied on Ports 1 and 3 which are respectively the MSB and the LSB of the address.

### Timings

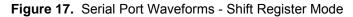

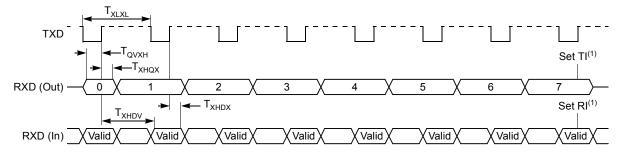

**Table 46.** Serial Port AC Timing -Shift Register Mode;  $V_{DD}$  = 2.7 to 5.5 V,  $T_A$  = -40 to 85°C

|                   |                                             | 12 MHz |     | 16 MHz |     | 24 MHz <sup>(1)</sup> |     |      |

|-------------------|---------------------------------------------|--------|-----|--------|-----|-----------------------|-----|------|

| Symbol            | Parameter                                   | Min    | Max | Min    | Max | Min                   | Max | Unit |

| T <sub>XLXL</sub> | Serial Port Clock Cycle Time                | 998    |     | 749    |     | 500                   |     | ns   |

| T <sub>QVXH</sub> | Output Data Setup to Clock Rising<br>Edge   | 833    |     | 625    |     | 417                   |     | ns   |

| T <sub>XHQX</sub> | Output Data hold after Clock Rising<br>Edge | 165    |     | 124    |     | 82                    |     | ns   |

| T <sub>XHDX</sub> | Input Data Hold after Clock Rising<br>Edge  | 0      |     | 0      |     | 0                     |     | ns   |

| T <sub>XHDV</sub> | Clock Rising Edge to Input Data<br>Valid    |        | 974 |        | 732 |                       | 482 | ns   |

Note: 1. For high speed versions only.

#### Waveforms

Note: 1. TI and RI are set during S1P1 of the peripheral cycle following the shift of the eight bit.

### **AC Characteristics - SSLC: SPI Interface**

### Definition of Symbols

### Table 48. SPI Interface Timing Symbol Definitions

|   | Signals  |

|---|----------|

| С | Clock    |

| I | Data In  |

| 0 | Data Out |

| S | SS#      |

|   | Conditions      |

|---|-----------------|

| Н | High            |

| L | Low             |

| V | Valid           |

| Х | No Longer Valid |

| Z | Floating        |

### Absolute Maximum Rating and Operating Conditions

### Absolute Maximum Ratings

| Storage Temperature65 to +150°C              | *NOTICE: Stressing the device beyond the "Absolute Maxi-<br>mum Ratings" may cause permanent damage. |

|----------------------------------------------|------------------------------------------------------------------------------------------------------|

| Voltage on any other Pin to VSS0.5 to +6.5 V | These are stress ratings only. Operation beyond                                                      |

| I <sub>OL</sub> per I/O Pin 15 mA            | the "operating conditions" is not recommended<br>and extended exposure beyond the "Operating         |

| Power Dissipation 1.5 W                      | Conditions" may affect device reliability.                                                           |

| Ambient Temperature Under Bias               |                                                                                                      |

| Commercial0 to +70°C                         |                                                                                                      |

| Industrial40 to +85°C                        |                                                                                                      |

| Automotive40 to +85°C                        |                                                                                                      |

| V <sub>DD</sub>                              |                                                                                                      |

| High Speed versions                          |                                                                                                      |

| Low Voltage versions 2.7 to 5.5 V            |                                                                                                      |

### **DC Characteristics**

### High Speed Versions - Commercial, Industrial, and Automotive

| Symbol           | Parameter                                                                                   | Min                                                                     | Typical <sup>(4)</sup> | Max                       | Units | Test Conditions                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------|---------------------------|-------|--------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage<br>(except EA#, SCL, SDA)                                                 | -0.5                                                                    |                        | 0.2·V <sub>DD</sub> - 0.1 | V     |                                                                                                                          |

| $V_{IL1}^{(5)}$  | Input Low Voltage<br>(SCL, SDA)                                                             | -0.5                                                                    |                        | 0.3·V <sub>DD</sub>       | V     |                                                                                                                          |

| $V_{\text{IL2}}$ | Input Low Voltage<br>(EA#)                                                                  | 0                                                                       |                        | 0.2·V <sub>DD</sub> - 0.3 | V     |                                                                                                                          |

| V <sub>IH</sub>  | Input high Voltage<br>(except XTAL1, RST, SCL, SDA)                                         | 0.2·V <sub>DD</sub> + 0.9                                               |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                          |

| $V_{IH1}^{(5)}$  | Input high Voltage<br>(XTAL1, RST, SCL, SDA)                                                | 0.7·V <sub>DD</sub>                                                     |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                          |

| V <sub>OL</sub>  | Output Low Voltage<br>(Ports 1, 2, 3)                                                       |                                                                         |                        | 0.3<br>0.45<br>1.0        | V     | $I_{OL} = 100 \ \mu A^{(1)(2)}$ $I_{OL} = 1.6 \ m A^{(1)(2)}$ $I_{OL} = 3.5 \ m A^{(1)(2)}$                              |

| V <sub>OL1</sub> | Output Low Voltage<br>(Ports 0, ALE, PSEN#, Port 2 in Page Mode during<br>External Address) |                                                                         |                        | 0.3<br>0.45<br>1.0        | V     | $I_{OL} = 200 \ \mu A^{(1)(2)}$ $I_{OL} = 3.2 \ m A^{(1)(2)}$ $I_{OL} = 7.0 \ m A^{(1)(2)}$                              |

| V <sub>OH</sub>  | Output high Voltage<br>(Ports 1, 2, 3, ALE, PSEN#)                                          | V <sub>DD</sub> - 0.3<br>V <sub>DD</sub> - 0.7<br>V <sub>DD</sub> - 1.5 |                        |                           | V     | $\begin{split} I_{OH} &= -10 \; \mu A^{(3)} \\ I_{OH} &= -30 \; \mu A^{(3)} \\ I_{OH} &= -60 \; \mu A^{(3)} \end{split}$ |

| V <sub>OH1</sub> | Output high Voltage<br>(Port 0, Port 2 in Page Mode during External Address)                | V <sub>DD</sub> - 0.3<br>V <sub>DD</sub> - 0.7<br>V <sub>DD</sub> - 1.5 |                        |                           | V     | I <sub>OH</sub> = -200 μA<br>I <sub>OH</sub> = -3.2 mA<br>I <sub>OH</sub> = -7.0 mA                                      |

| $V_{RET}$        | V <sub>DD</sub> data retention limit                                                        |                                                                         |                        | 1.8                       | V     |                                                                                                                          |

| I <sub>IL0</sub> | Logical 0 Input Current<br>(Ports 1, 2, 3)                                                  |                                                                         |                        | - 50                      | μA    | V <sub>IN</sub> = 0.45 V                                                                                                 |

| I <sub>IL1</sub> | Logical 1 Input Current<br>(NMI)                                                            |                                                                         |                        | + 50                      | μA    | V <sub>IN</sub> = V <sub>DD</sub>                                                                                        |

| I <sub>LI</sub>  | Input Leakage Current<br>(Port 0)                                                           |                                                                         |                        | ± 10                      | μA    | 0.45 V < V <sub>IN</sub> < V <sub>DD</sub>                                                                               |

| I <sub>TL</sub>  | Logical 1-to-0 Transition Current<br>(Ports 1, 2, 3 - AWAIT#)                               |                                                                         |                        | - 650                     | μA    | V <sub>IN</sub> = 2.0 V                                                                                                  |

| R <sub>RST</sub> | RST Pull-Down Resistor                                                                      | 40                                                                      | 110                    | 225                       | kΩ    |                                                                                                                          |

| CIO              | Pin Capacitance                                                                             |                                                                         | 10                     |                           | pF    | T <sub>A</sub> = 25°C                                                                                                    |

| I <sub>DD</sub>  | Operating Current                                                                           |                                                                         | 20<br>25<br>35         | 25<br>30<br>40            | mA    | $F_{OSC}$ = 12 MHz<br>$F_{OSC}$ = 16 MHz<br>$F_{OSC}$ = 24 MHz                                                           |

| I <sub>DL</sub>  | Idle Mode Current                                                                           |                                                                         | 5<br>6.5<br>9.5        | 8<br>10<br>14             | mA    | $F_{OSC}$ = 12 MHz<br>$F_{OSC}$ = 16 MHz<br>$F_{OSC}$ = 24 MHz                                                           |

| I <sub>PD</sub>  | Power-Down Current                                                                          |                                                                         | 2                      | 20                        | μA    | $V_{RET} < V_{DD} < 5.5 V$                                                                                               |

| $V_{PP}$         | Programming supply voltage                                                                  | 12.5                                                                    |                        | 13                        | V     | $T_A = 0$ to +40°C                                                                                                       |

| I <sub>PP</sub>  | Programming supply current                                                                  | 1                                                                       |                        | 75                        | mA    | T <sub>A</sub> = 0 to +40°C                                                                                              |

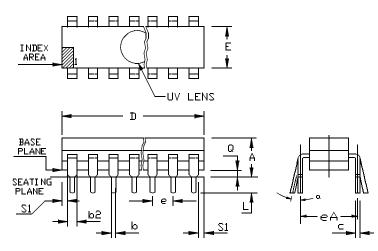

CDIL 40 with Window -Mechanical Outline

Figure 34. Ceramic Dual In Line

Table 58. CDIL Package Size

|    | ММ           |       | Inch        |       |

|----|--------------|-------|-------------|-------|

|    | Min          | Max   | Min         | Мах   |

| A  | -            | 5.71  | -           | .225  |

| b  | 0.36         | 0.58  | .014        | .023  |

| b2 | 1.14         | 1.65  | .045        | .065  |

| с  | 0.20         | 0.38  | .008        | .015  |

| D  | -            | 53.47 | -           | 2.105 |

| E  | 13.06        | 15.37 | .514        | .605  |

| e  | 2.54 B.S.C.  |       | .100 B.S.C. |       |

| eA | 15.24 B.S.C. |       | .600 B.S.C. |       |

| L  | 3.18         | 5.08  | .125        | .200  |

| Q  | 0.38         | 1.40  | .015        | .055  |

| S1 | 0.13         | -     | .005        | -     |

| а  | 0 - 15       |       | 0 - 15      |       |

| Ν  | 40           |       |             |       |