Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | C251                                                                       |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 16MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, Microwire, SPI, UART/USART                      |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | -                                                                          |

| Program Memory Type        | ROMIess                                                                    |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at80251g2d-slsul |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

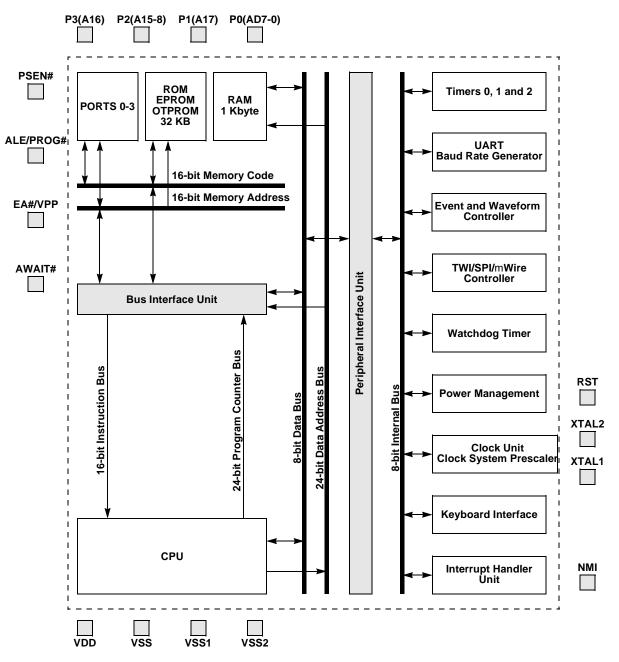

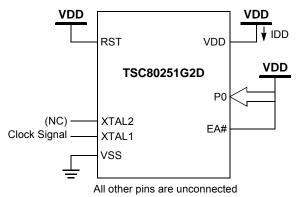

## **Block Diagram**

| Table 2 | Product Name | Signal Description | (Continued) |

|---------|--------------|--------------------|-------------|

|---------|--------------|--------------------|-------------|

|                | 2. Product Name Signal Description (Continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |  |  |

|----------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|

| Signal<br>Name | Туре                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Alternate<br>Function |  |  |

| NMI            | I                                              | Non Maskable Interrupt<br>Holding this pin high for 24 oscillator periods triggers an interrupt.<br>When using the Product Name as a pin-for-pin replacement for a 8xC51<br>product, NMI can be unconnected without loss of compatibility or power<br>consumption increase (on-chip pull-down).<br>Not available on DIP package.                                                                                                                                                                                                               | -                     |  |  |

| P0.0:7         | I/O                                            | <b>Port 0</b><br>P0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs. To avoid any paraitic current consumption, Floating P0 inputs must be polarized to $V_{DD}$ or $V_{SS}$ .                                                                                                                                                                                                                                                                          |                       |  |  |

| P1.0:7         | I/O                                            | <b>Port 1</b><br>P1 is an 8-bit bidirectional I/O port with internal pull-ups. P1 provides interrupt capability for a keyboard interface.                                                                                                                                                                                                                                                                                                                                                                                                      | _                     |  |  |

| P2.0:7         | I/O                                            | Port 2<br>P2 is an 8-bit bidirectional I/O port with internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A15:8                 |  |  |

| P3.0:7         | I/O                                            | <b>Port 3</b><br>P3 is an 8-bit bidirectional I/O port with internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                     |  |  |

| PROG#          | I                                              | <b>Programming Pulse input</b><br>The programming pulse is applied to this input for programming the on-chip<br>EPROM/OTPROM.                                                                                                                                                                                                                                                                                                                                                                                                                  | Ι                     |  |  |

| PSEN#          | 0                                              | Program Store Enable/Read signal output<br>PSEN# is asserted for a memory address range that depends on bits RD0<br>and RD1 in UCONFIG0 byte (see ).                                                                                                                                                                                                                                                                                                                                                                                           | _                     |  |  |

| RD#            | 0                                              | Read or 17 <sup>th</sup> Address Bit (A16)<br>Read signal output to external data memory depending on the values of<br>bits RD0 and RD1 in UCONFIG0 byte (see Table 13, Page 20).                                                                                                                                                                                                                                                                                                                                                              | P3.7                  |  |  |

| RST            | I                                              | <b>Reset input to the chip</b><br>Holding this pin high for 64 oscillator periods while the oscillator is running<br>resets the device. The Port pins are driven to their reset conditions when a<br>voltage greater than $V_{IH1}$ is applied, whether or not the oscillator is running.<br>This pin has an internal pull-down resistor which allows the device to be<br>reset by connecting a capacitor between this pin and VDD.<br>Asserting RST when the chip is in Idle mode or Power-Down mode returns<br>the chip to normal operation. | _                     |  |  |

| RXD            | I/O                                            | <b>Receive Serial Data</b><br>RXD sends and receives data in serial I/O mode 0 and receives data in<br>serial I/O modes 1, 2 and 3.                                                                                                                                                                                                                                                                                                                                                                                                            | P3.0                  |  |  |

| SCL            | I/O                                            | TWI Serial Clock<br>When TWI controller is in master mode, SCL outputs the serial clock to<br>slave peripherals. When TWI controller is in slave mode, SCL receives<br>clock from the master controller.                                                                                                                                                                                                                                                                                                                                       | P1.6                  |  |  |

| SCK            | I/O                                            | <b>SPI Serial Clock</b><br>When SPI is in master mode, SCK outputs clock to the slave peripheral.<br>When SPI is in slave mode, SCK receives clock from the master controller.                                                                                                                                                                                                                                                                                                                                                                 | P1.6                  |  |  |

| SDA            | I/O                                            | TWI Serial Data<br>SDA is the bidirectional TWI data line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P1.7                  |  |  |

| SS#            | I                                              | SPI Slave Select Input<br>When in Slave mode, SS# enables the slave mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P1.4                  |  |  |

| Table 2. Product Name Signal Description (Continued) |      |                                                                                                                                                                                                                                                                                                                                                   |                       |

|------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Signal<br>Name                                       | Туре | Description                                                                                                                                                                                                                                                                                                                                       | Alternate<br>Function |

| T1:0                                                 | I/O  | <b>Timer 1:0 External Clock Inputs</b><br>When timer 1:0 operates as a counter, a falling edge on the T1:0 pin increments the count.                                                                                                                                                                                                              | -                     |

| T2                                                   | I/O  | <b>Timer 2 Clock Input/Output</b><br>For the timer 2 capture mode, T2 is the external clock input. For the Timer 2 clock-out mode, T2 is the clock output.                                                                                                                                                                                        | P1.0                  |

| T2EX                                                 | I    | <b>Timer 2 External Input</b><br>In timer 2 capture mode, a falling edge initiates a capture of the timer 2<br>registers. In auto-reload mode, a falling edge causes the timer 2 register to<br>be reloaded. In the up-down counter mode, this signal determines the<br>count direction: 1 = up, 0 = down.                                        | P1.1                  |

| тхр                                                  | 0    | <b>Transmit Serial Data</b><br>TXD outputs the shift clock in serial I/O mode 0 and transmits data in serial<br>I/O modes 1, 2 and 3.                                                                                                                                                                                                             | P3.1                  |

| VDD                                                  | PWR  | <b>Digital Supply Voltage</b><br>Connect this pin to +5V or +3V supply voltage.                                                                                                                                                                                                                                                                   | -                     |

| VPP                                                  | I    | <b>Programming Supply Voltage</b><br>The programming supply voltage is applied to this input for programming<br>the on-chip EPROM/OTPROM.                                                                                                                                                                                                         | -                     |

| VSS                                                  | GND  | Circuit Ground<br>Connect this pin to ground.                                                                                                                                                                                                                                                                                                     | -                     |

| VSS1                                                 | GND  | Secondary Ground 1<br>This ground is provided to reduce ground bounce and improve power<br>supply bypassing. Connection of this pin to ground is recommended.<br>However, when using the TSC80251G2D as a pin-for-pin replacement for a<br>8xC51 product, VSS1 can be unconnected without loss of compatibility.<br>Not available on DIP package. | Ι                     |

| VSS2                                                 | GND  | Secondary Ground 2<br>This ground is provided to reduce ground bounce and improve power<br>supply bypassing. Connection of this pin to ground is recommended.<br>However, when using the TSC80251G2D as a pin-for-pin replacement for a<br>8xC51 product, VSS2 can be unconnected without loss of compatibility.<br>Not available on DIP package. | _                     |

| WAIT#                                                | I    | <b>Real-time Synchronous Wait States Input</b><br>The real-time WAIT# input is enabled by setting RTWE bit in WCON<br>(S:A7h). During bus cycles, the external memory system can signal<br>'system ready' to the microcontroller in real time by controlling the WAIT#<br>input signal.                                                           | P1.6                  |

| WCLK                                                 | 0    | Wait Clock Output<br>The real-time WCLK output is enabled by setting RTWCE bit in WCON<br>(S:A7h). When enabled, the WCLK output produces a square wave signal<br>with a period of one half the oscillator frequency.                                                                                                                             | P1.7                  |

| WR#                                                  | 0    | <b>Write</b><br>Write signal output to external memory.                                                                                                                                                                                                                                                                                           | P3.6                  |

| XTAL1                                                | I    | Input to the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected to this<br>pin. If an external oscillator is used, its output is connected to this pin.<br>XTAL1 is the clock source for internal timing.                                                                         | -                     |

Table 2.

Product Name Signal Description (Continued)

# Table 11.Configuration Byte 0UCONFIG0

| 7          | 6               | 5                        | 4                                                       | 3                                                          | 2                                             | 1              | 0              |

|------------|-----------------|--------------------------|---------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------|----------------|----------------|

| -          | WSA1#           | WSA0#                    | XALE#                                                   | RD1                                                        | RD0                                           | PAGE#          | SRC            |

| Bit Number | Bit<br>Mnemonic | Descriptio               | n                                                       |                                                            |                                               |                |                |

| 7          | -               | Reserved<br>Set this bit | when writing                                            | to UCONFIG0                                                | ).                                            |                |                |

| 6          | WSA1#           | Wait State               |                                                         |                                                            |                                               |                | fan ar fam al  |

| 5          | WSA0#           |                          | cesses (all re<br><u>VSA0#</u> <u>Nu</u><br>3<br>2<br>1 | it states for RL<br>gions except (<br><u>umber of Wait</u> | ,                                             | -SEN# signals  | s for external |

| 4          | XALE#           |                          | tend the dura                                           |                                                            | E pulse from T<br>E pulse to 1·T <sub>o</sub> |                |                |

| 3          | RD1             | -                        | gnal Select                                             |                                                            |                                               |                |                |

| 2          | RD0             |                          |                                                         | s (see Table 1                                             | al address bu<br>3).                          | s and the usag | ge of RD#,     |

| 1          | PAGE#           | Clear to sel<br>Port 0.  |                                                         | Page mode v                                                | vith A15:8/D7:<br>h A15:8 on Po               |                |                |

| 0          | SRC             | Clear to set             | de/Binary M<br>lect the binary<br>ct the source         |                                                            | t                                             |                |                |

Notes: 1. UCONFIG0 is fetched twice so it can be properly read both in Page or Non-Page modes. If P2.1 is cleared during the first data fetch, a Page mode configuration is used, otherwise the subsequent fetches are performed in Non-Page mode.

2. This selection provides compatibility with the standard 80C51 hardware which is multiplexing the address LSB and the data on Port 0.

|          | <dest>,</dest>            | dest                                                    |       | Mode             | Source Mode |                  |

|----------|---------------------------|---------------------------------------------------------|-------|------------------|-------------|------------------|

| Mnemonic | <src><sup>(2)</sup></src> | Comments                                                | Bytes | States           | Bytes       | States           |

|          | Rmd, Rms                  | Register with register                                  | 3     | 2                | 2           | 1                |

|          | WRjd,<br>WRjs             | Word register with word register                        | 3     | 3                | 2           | 2                |

|          | DRkd,<br>DRks             | Dword register with dword register                      | 3     | 5                | 2           | 4                |

|          | Rm, #data                 | Register with immediate data                            | 4     | 3                | 3           | 2                |

|          | WRj,<br>#data16           | Word register with immediate 16-bit data                | 5     | 4                | 4           | 3                |

|          | DRk,<br>#0data16          | Dword register with zero-extended 16-bit immediate data | 5     | 6                | 4           | 5                |

| CMP      | DRk,<br>#1data16          | Dword register with one-extended 16-bit immediate data  | 5     | 6                | 4           | 5                |

|          | Rm, dir8                  | Direct address (on-chip RAM or SFR) with byte register  | 4     | 3 <sup>(1)</sup> | 3           | 2 <sup>(1)</sup> |

|          | WRj, dir8                 | Direct address (on-chip RAM or SFR) with word register  | 4     | 4                | 3           | 3                |

|          | Rm, dir16                 | Direct address (64K) with byte register                 | 5     | 3 <sup>(2)</sup> | 4           | 2 <sup>(2)</sup> |

|          | WRj, dir16                | Direct address (64K) with word register                 | 5     | 4 <sup>(3)</sup> | 4           | 3 <sup>(3)</sup> |

|          | Rm, at WRj                | Indirect address (64K) with byte register               | 4     | 3 <sup>(2)</sup> | 3           | 2 <sup>(2)</sup> |

|          | Rm, at DRk                | Indirect address (16M) with byte register               | 4     | 4 <sup>(2)</sup> | 3           | 3(2)             |

#### Table 22. Summary of Compare Instructions

Notes: 1. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 2. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

- 3. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

- Notes: 1. Logical instructions that affect a bit are in Table 27.

- 2. A shaded cell denotes an instruction in the C51 Architecture.

- 3. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 4. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

- 5. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

- 6. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

| Table 23. | Summar | of Logical | Instructions | (2/2) |

|-----------|--------|------------|--------------|-------|

|           |        |            |              |       |

| (CY) ← <des<br>Shift Right Arithme<br/><dest><sub>n-1</sub> ←<br/>(CY) ← <des<br>Shift Right Logical</des<br></dest></des<br> | <dest><sub>n</sub>, n =<br/>tt&gt;<sub>msb</sub><br/>eticSRA <des<br><dest><sub>n</sub>, n = n<br/>tt&gt;<sub>0</sub><br/>SRL <dest>&lt;<br/><dest><sub>n</sub>, n = n<br/>tt&gt;<sub>0</sub></dest></dest></dest></des<br></dest> | 0msb-1<br>t> <dest><sub>msb</sub> ← <dest><sub>msb</sub><br/>msb1<br/>dest&gt;<sub>msb</sub> ← 0</dest></dest> |        |        |        |        |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|

|                                                                                                                               | <dest>,</dest>                                                                                                                                                                                                                     |                                                                                                                | Binary | Mode   | Source | e Mode |

| Mnemonic                                                                                                                      | <src><sup>(1)</sup></src>                                                                                                                                                                                                          | Comments                                                                                                       | Bytes  | States | Bytes  | States |

|                                                                                                                               | Rm                                                                                                                                                                                                                                 | Shift byte register left through the MSB                                                                       | 3      | 2      | 2      | 1      |

| SLL                                                                                                                           | WRj                                                                                                                                                                                                                                | Shift word register left through the MSB                                                                       | 3      | 2      | 2      | 1      |

| SRA                                                                                                                           | Rm                                                                                                                                                                                                                                 | Shift byte register right                                                                                      | 3      | 2      | 2      | 1      |

| SKA                                                                                                                           | WRj                                                                                                                                                                                                                                | Shift word register right 3 2 2                                                                                |        | 1      |        |        |

| SRL                                                                                                                           | Rm                                                                                                                                                                                                                                 | Shift byte register left                                                                                       | 3      | 2      | 2      | 1      |

| JRL                                                                                                                           | WRj                                                                                                                                                                                                                                | Shift word register left                                                                                       | 3      | 2      | 2      | 1      |

| SWAP                                                                                                                          | А                                                                                                                                                                                                                                  | Swap nibbles within ACC                                                                                        | 1      | 2      | 1      | 2      |

Note: 1. A shaded cell denotes an instruction in the C51 Architecture.

|     |                       |                                                          |       | Binary Mode      |       | Source Mode      |  |

|-----|-----------------------|----------------------------------------------------------|-------|------------------|-------|------------------|--|

|     |                       | Comments                                                 | Bytes | States           | Bytes | States           |  |

| MOV | Rmd, Rms              | Byte register to byte register                           | 3     | 2                | 2     | 1                |  |

| MOV | WRjd, WRjs            | Word register to word register                           | 3     | 2                | 2     | 1                |  |

| MOV | DRkd, DRks            | Dword register to dword register                         | 3     | 3                | 2     | 2                |  |

| MOV | Rm, #data             | Immediate 8-bit data to byte register                    | 4     | 3                | 3     | 2                |  |

| MOV | WRj, #data16          | Immediate 16-bit data to word register                   | 5     | 3                | 4     | 2                |  |

| MOV | DRk, #0data16         | zero-ext 16bit immediate data to dword register          | 5     | 5                | 4     | 4                |  |

| MOV | DRk, #1data16         | one-ext 16bit immediate data to dword register           | 5     | 5                | 4     | 4                |  |

| MOV | Rm, dir8              | Direct address (on-chip RAM or SFR) to byte register     | 4     | 3 <sup>(3)</sup> | 3     | 2 <sup>(3)</sup> |  |

| MOV | WRj, dir8             | Direct address (on-chip RAM or SFR) to word register     | 4     | 4                | 3     | 3                |  |

| MOV | DRk, dir8             | Direct address (on-chip RAM or SFR) to dword register    | 4     | 6                | 3     | 5                |  |

| MOV | Rm, dir16             | Direct address (64K) to byte register                    | 5     | 3 <sup>(4)</sup> | 4     | 2 <sup>(4)</sup> |  |

| MOV | WRj, dir16            | Direct address (64K) to word register                    | 5     | 4 <sup>(5)</sup> | 4     | 3 <sup>(5)</sup> |  |

| MOV | DRk, dir16            | Direct address (64K) to dword register                   | 5     | 6 <sup>(6)</sup> | 4     | 5 <sup>(6)</sup> |  |

| MOV | Rm, at WRj            | Indirect address (64K) to byte register                  | 4     | 3 <sup>(4)</sup> | 3     | 2(4)             |  |

| MOV | Rm, at DRk            | Indirect address (16M) to byte register                  | 4     | 4 <sup>(4)</sup> | 3     | 3(4)             |  |

| MOV | WRjd, at WRjs         | Indirect address (64K) to word register                  | 4     | 4 <sup>(5)</sup> | 3     | 3 <sup>(5)</sup> |  |

| MOV | WRj, at DRk           | Indirect address (16M) to word register                  | 4     | 5 <sup>(5)</sup> | 3     | 4 <sup>(5)</sup> |  |

| MOV | dir8, Rm              | Byte register to direct address (on-chip RAM or SFR)     | 4     | 4 <sup>(3)</sup> | 3     | 3 <sup>(3)</sup> |  |

| MOV | dir8, WRj             | Word register to direct address (on-chip RAM or SFR)     | 4     | 5                | 3     | 4                |  |

| MOV | dir8, DRk             | Dword register to direct address (on-chip RAM or SFR)    | 4     | 7                | 3     | 6                |  |

| MOV | dir16, Rm             | Byte register to direct address (64K)                    | 5     | 4 <sup>(4)</sup> | 4     | 3(4)             |  |

| MOV | dir16, WRj            | Word register to direct address (64K)                    | 5     | 5 <sup>(5)</sup> | 4     | 4 <sup>(5)</sup> |  |

| MOV | dir16, DRk            | Dword register to direct address (64K)                   | 5     | 7 <sup>(6)</sup> | 4     | 6 <sup>(6)</sup> |  |

| MOV | at WRj, Rm            | Byte register to indirect address (64K)                  | 4     | 4 <sup>(4)</sup> | 3     | 3(4)             |  |

| MOV | at DRk, Rm            | Byte register to indirect address (16M)                  | 4     | 5 <sup>(4)</sup> | 3     | 4 <sup>(4)</sup> |  |

| MOV | at WRjd, WRjs         | Word register to indirect address (64K)                  | 4     | 5 <sup>(5)</sup> | 3     | 4 <sup>(5)</sup> |  |

| MOV | at DRk, WRj           | Word register to indirect address (16M)                  | 4     | 6 <sup>(5)</sup> | 3     | 5 <sup>(5)</sup> |  |

| MOV | Rm, at WRj<br>+dis16  | Indirect with 16-bit displacement (64K) to byte register | 5     | 6 <sup>(4)</sup> | 4     | 5 <sup>(4)</sup> |  |

| MOV | WRj, at WRj<br>+dis16 | Indirect with 16-bit displacement (64K) to word register | 5     | 7 <sup>(5)</sup> | 4     | 6 <sup>(5)</sup> |  |

| MOV | Rm, at DRk<br>+dis24  | Indirect with 16-bit displacement (16M) to byte register | 5     | 7 <sup>(4)</sup> | 4     | 6 <sup>(4)</sup> |  |

| Table 32. | Summar | of Call and | Return | Instructions |

|-----------|--------|-------------|--------|--------------|

|-----------|--------|-------------|--------|--------------|

|                                | ACALL <src><br/><math>\leftarrow</math> src opnd</src> | $(PC) \leftarrow (PC)$ +2; push $(PC)_{15:0}$ ;                                                                                                                                                           |                            |                                                                                                                 |                            |                                                                                                                                     |

|--------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Extended ca                    |                                                        | $P(PC) \leftarrow (PC) + size (instr); push (PC)_2$                                                                                                                                                       | 3:0,                       |                                                                                                                 |                            |                                                                                                                                     |

| Long callLCA                   |                                                        | ) $\leftarrow$ (PC) + size (instr); push (PC) <sub>15:0</sub> ;                                                                                                                                           |                            |                                                                                                                 |                            |                                                                                                                                     |

| Return from                    | subroutineRE                                           | Tpop (PC) <sub>15:0</sub>                                                                                                                                                                                 |                            |                                                                                                                 |                            |                                                                                                                                     |

|                                |                                                        | outineERETpop(PC) <sub>23:0</sub>                                                                                                                                                                         |                            |                                                                                                                 |                            |                                                                                                                                     |

|                                |                                                        | IF [INTR = 0] THEN pop (PC) <sub>15:0</sub><br>pop (PC) <sub>23:0</sub> ; pop (PSW1)                                                                                                                      |                            |                                                                                                                 |                            |                                                                                                                                     |

| Trap interrup<br>IF [INTF      | tTRAP(PC) ←<br>R = 0] THEN p                           | - (PC) + size (instr);                                                                                                                                                                                    |                            |                                                                                                                 |                            |                                                                                                                                     |

|                                |                                                        |                                                                                                                                                                                                           | Binary                     | / Mode                                                                                                          | Source                     | e Mode                                                                                                                              |

|                                | <dest>,</dest>                                         |                                                                                                                                                                                                           |                            |                                                                                                                 | <b>.</b>                   | _                                                                                                                                   |

| Mnemonic                       | <src><sup>(1)</sup></src>                              | Comments                                                                                                                                                                                                  | Bytes                      | States                                                                                                          | Bytes                      | States                                                                                                                              |

| Mnemonic<br>ACALL              | <src>(")<br/>addr11</src>                              | Comments           Absolute subroutine call                                                                                                                                                               | Bytes<br>2                 | 9 <sup>(2)(3)</sup>                                                                                             | Bytes<br>2                 |                                                                                                                                     |

| ACALL                          |                                                        |                                                                                                                                                                                                           | -                          |                                                                                                                 | ,                          | States<br>9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                                                                                 |

| ACALL                          | addr11                                                 | Absolute subroutine call                                                                                                                                                                                  | 2                          | 9 <sup>(2)(3)</sup>                                                                                             | 2                          | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                                                                                           |

| ACALL                          | addr11<br>at DRk                                       | Absolute subroutine call<br>Extended subroutine call (indirect)                                                                                                                                           | 2 3                        | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup>                                                                     | 2<br>2                     | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                                                                    |

| ACALL                          | addr11<br>at DRk<br>addr24                             | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call                                                                                                     | 2<br>3<br>5                | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup>                                             | 2<br>2<br>4                | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>9 <sup>(2)(3</sup>                                              |

| ACALL                          | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call<br>Extended subroutine call (indirect)<br>Extended subroutine call<br>Long subroutine call (indirect)                                                                            | 2<br>3<br>5<br>3           | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>10 <sup>(2)(3)</sup>                     | 2<br>2<br>4<br>2           | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>9 <sup>(2)(3</sup>                                              |

| ACALL<br>ECALL<br>LCALL<br>RET | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call         Long subroutine call (indirect)         Long subroutine call                                | 2<br>3<br>5<br>3<br>3      | $\begin{array}{c} 9^{(2)(3)} \\ 14^{(2)(3)} \\ 14^{(2)(3)} \\ 10^{(2)(3)} \\ 9^{(2)(3)} \end{array}$            | 2<br>2<br>4<br>2<br>3      | $9^{(2)(3)}$ $13^{(2)(3)}$ $13^{(2)(3)}$ $9^{(2)(3)}$ $9^{(2)(3)}$                                                                  |

| ACALL<br>ECALL<br>LCALL        | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call         Long subroutine call (indirect)         Long subroutine call         Return from subroutine | 2<br>3<br>5<br>3<br>3<br>1 | $\begin{array}{c} 9^{(2)(3)} \\ 14^{(2)(3)} \\ 14^{(2)(3)} \\ 10^{(2)(3)} \\ 9^{(2)(3)} \\ 7^{(2)} \end{array}$ | 2<br>2<br>4<br>2<br>3<br>1 | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3)</sup><br>9 <sup>(2)(3)</sup><br>9 <sup>(2)(3)</sup><br>7 <sup>(2)</sup> |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. In internal execution only, add 1 to the number of states if the destination/return address is internal and odd.

- 3. Add 2 to the number of states if the destination address is external.

- 4. Add 5 to the number of states if INTR = 1.

## **AC Characteristics - Commercial & Industrial**

### **AC Characteristics - External Bus Cycles**

**Definition of Symbols**

Table 38. External Bus Cycles Timing Symbol Definitions

| Signals   |

|-----------|

| Address   |

| Data In   |

| ALE       |

| Data Out  |

| RD#/PSEN# |

| WR#       |

|           |

| Conditions      |  |  |  |  |

|-----------------|--|--|--|--|

| High            |  |  |  |  |

| Low             |  |  |  |  |

| Valid           |  |  |  |  |

| No Longer Valid |  |  |  |  |

| Floating        |  |  |  |  |

|                 |  |  |  |  |

Timings

Test conditions: capacitive load on all pins = 50 pF.

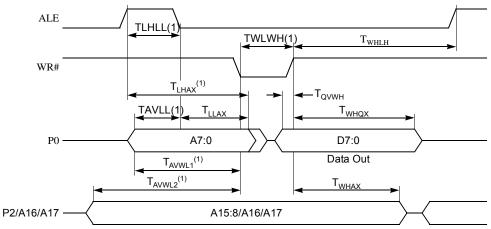

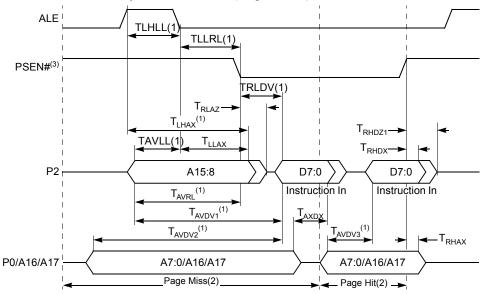

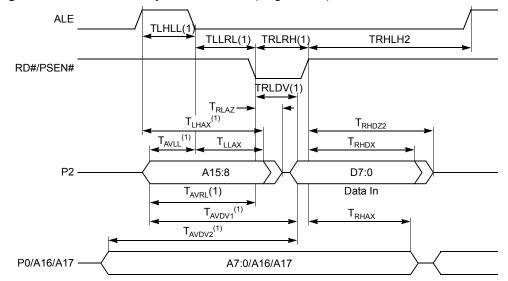

Table 39 and Table 40 list the AC timing parameters for the TSC80251G2D derivatives with no wait states. External wait states can be added by extending PSEN#/RD#/WR# and or by extending ALE. In these tables, Note 2 marks parameters affected by one ALE wait state, and Note 3 marks parameters affected by PSEN#/RD#/WR# wait states.

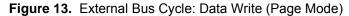

Figure 8 to Figure 13 show the bus cycles with the timing parameters.

Figure 10. External Bus Cycle: Data Write (Non-Page Mode)

Waveforms in Page Mode

Figure 11. External Bus Cycle: Code Fetch (Page Mode)

- Note: 1. The value of this parameter depends on wait states. See Table 39 and Table 40.

- A page hit (i.e., a code fetch to the same 256-byte "page" as the previous code fetch) requires one state (2·T<sub>OSC</sub>);

a page miss requires two states ( $4 \cdot T_{OSC}$ ).

During a sequence of page hits, PSEN# remains low until the end of the last page-hit cycle.

Figure 12. External Bus Cycle: Data Read (Page Mode)

### AC Characteristics - Real-Time Synchronous Wait State

### **Definition of Symbols**

**Table 41.** Real-Time Synchronous Wait Timing Symbol Definitions

| Signals |           |  |  |  |

|---------|-----------|--|--|--|

| С       | WCLK      |  |  |  |

| R       | RD#/PSEN# |  |  |  |

| W       | WR#       |  |  |  |

| Y       | WAIT#     |  |  |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| L          | Low             |  |  |  |

| V          | Valid           |  |  |  |

| Х          | No Longer Valid |  |  |  |

# 50 AT/TSC8x251G2D

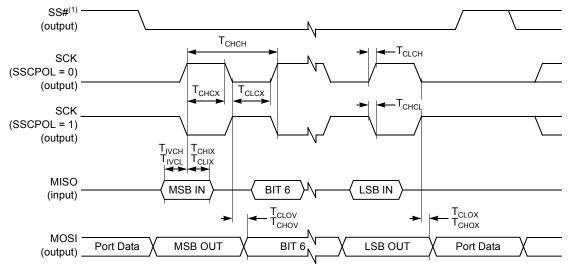

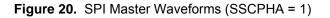

Note: 1. SS# handled by software.

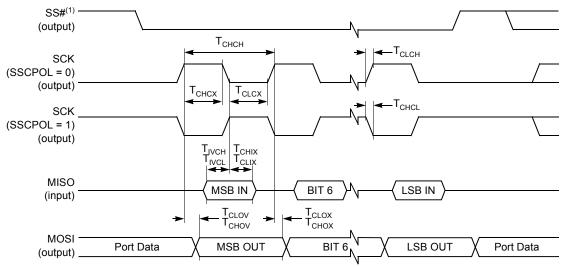

Note: 1. Not Defined but normally MSB of character just received.

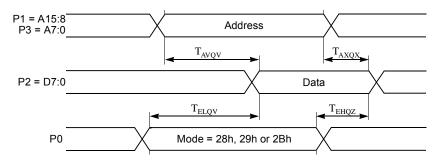

#### Figure 24. EPROM Verifying Waveforms

### AC Characteristics - External Clock Drive and Logic Level References

**Definition of Symbols**

Table 53. External Clock Timing Symbol Definitions

|   | Signals |  |  |  |

|---|---------|--|--|--|

| С | Clock   |  |  |  |

|   |         |  |  |  |

|   |         |  |  |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| Н          | High            |  |  |  |

| L          | Low             |  |  |  |

| Х          | No Longer Valid |  |  |  |

#### Timings

### **Table 54.** External Clock AC Timings; $V_{DD}$ = 4.5 to 5.5 V, $T_A$ = -40 to +85°C

| Symbol                                | Parameter | Min | Max | Unit |

|---------------------------------------|-----------|-----|-----|------|

| F <sub>OSC</sub> Oscillator Frequency |           |     | 24  | MHz  |

| T <sub>CHCX</sub>                     | High Time | 10  |     | ns   |

| T <sub>CLCX</sub>                     | Low Time  | 10  |     | ns   |

| T <sub>CLCH</sub>                     | Rise Time | 3   |     | ns   |

| T <sub>CHCL</sub>                     | Fall Time | 3   |     | ns   |

#### Waveforms

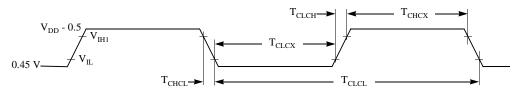

Figure 25. External Clock Waveform

- Notes: 1. During AC testing, all inputs are driven at  $V_{DD}$  -0.5 V for a logic 1 and 0.45 V for a logic 0.

- 2. Timing measurements are made on all outputs at  $V_{\rm IH}$  min for a logic 1 and  $V_{\rm IL}$  max for a logic 0.

## **DC Characteristics**

## High Speed Versions - Commercial, Industrial, and Automotive

| Symbol           | Parameter                                                                                   | Min                                                                     | Typical <sup>(4)</sup> | Max                       | Units | Test Conditions                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------|---------------------------|-------|-----------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage<br>(except EA#, SCL, SDA)                                                 | -0.5                                                                    |                        | 0.2·V <sub>DD</sub> - 0.1 | V     |                                                                                                                       |

| $V_{IL1}^{(5)}$  | Input Low Voltage<br>(SCL, SDA)                                                             | -0.5                                                                    |                        | 0.3·V <sub>DD</sub>       | V     |                                                                                                                       |

| $V_{\text{IL2}}$ | Input Low Voltage<br>(EA#)                                                                  | 0                                                                       |                        | 0.2·V <sub>DD</sub> - 0.3 | V     |                                                                                                                       |

| V <sub>IH</sub>  | Input high Voltage<br>(except XTAL1, RST, SCL, SDA)                                         | 0.2·V <sub>DD</sub> + 0.9                                               |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                       |

| $V_{IH1}^{(5)}$  | Input high Voltage<br>(XTAL1, RST, SCL, SDA)                                                | 0.7·V <sub>DD</sub>                                                     |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                       |

| V <sub>OL</sub>  | Output Low Voltage<br>(Ports 1, 2, 3)                                                       |                                                                         |                        | 0.3<br>0.45<br>1.0        | V     | $I_{OL} = 100 \ \mu A^{(1)(2)}$ $I_{OL} = 1.6 \ m A^{(1)(2)}$ $I_{OL} = 3.5 \ m A^{(1)(2)}$                           |

| V <sub>OL1</sub> | Output Low Voltage<br>(Ports 0, ALE, PSEN#, Port 2 in Page Mode during<br>External Address) |                                                                         |                        | 0.3<br>0.45<br>1.0        | V     | $I_{OL} = 200 \ \mu A^{(1)(2)}$ $I_{OL} = 3.2 \ m A^{(1)(2)}$ $I_{OL} = 7.0 \ m A^{(1)(2)}$                           |

| V <sub>OH</sub>  | Output high Voltage<br>(Ports 1, 2, 3, ALE, PSEN#)                                          | V <sub>DD</sub> - 0.3<br>V <sub>DD</sub> - 0.7<br>V <sub>DD</sub> - 1.5 |                        |                           | V     | $\begin{split} I_{OH} &= -10 \ \mu A^{(3)} \\ I_{OH} &= -30 \ \mu A^{(3)} \\ I_{OH} &= -60 \ \mu A^{(3)} \end{split}$ |

| V <sub>OH1</sub> | Output high Voltage<br>(Port 0, Port 2 in Page Mode during External Address)                | V <sub>DD</sub> - 0.3<br>V <sub>DD</sub> - 0.7<br>V <sub>DD</sub> - 1.5 |                        |                           | V     | I <sub>OH</sub> = -200 μA<br>I <sub>OH</sub> = -3.2 mA<br>I <sub>OH</sub> = -7.0 mA                                   |

| $V_{RET}$        | V <sub>DD</sub> data retention limit                                                        |                                                                         |                        | 1.8                       | V     |                                                                                                                       |

| I <sub>IL0</sub> | Logical 0 Input Current<br>(Ports 1, 2, 3)                                                  |                                                                         |                        | - 50                      | μA    | V <sub>IN</sub> = 0.45 V                                                                                              |

| I <sub>IL1</sub> | Logical 1 Input Current<br>(NMI)                                                            |                                                                         |                        | + 50                      | μA    | V <sub>IN</sub> = V <sub>DD</sub>                                                                                     |

| I <sub>LI</sub>  | Input Leakage Current<br>(Port 0)                                                           |                                                                         |                        | ± 10                      | μA    | 0.45 V < V <sub>IN</sub> < V <sub>DD</sub>                                                                            |

| I <sub>TL</sub>  | Logical 1-to-0 Transition Current<br>(Ports 1, 2, 3 - AWAIT#)                               |                                                                         |                        | - 650                     | μA    | V <sub>IN</sub> = 2.0 V                                                                                               |

| R <sub>RST</sub> | RST Pull-Down Resistor                                                                      | 40                                                                      | 110                    | 225                       | kΩ    |                                                                                                                       |

| CIO              | Pin Capacitance                                                                             |                                                                         | 10                     |                           | pF    | T <sub>A</sub> = 25°C                                                                                                 |

| I <sub>DD</sub>  | Operating Current                                                                           |                                                                         | 20<br>25<br>35         | 25<br>30<br>40            | mA    | $F_{OSC}$ = 12 MHz<br>$F_{OSC}$ = 16 MHz<br>$F_{OSC}$ = 24 MHz                                                        |

| I <sub>DL</sub>  | Idle Mode Current                                                                           |                                                                         | 5<br>6.5<br>9.5        | 8<br>10<br>14             | mA    | $F_{OSC}$ = 12 MHz<br>$F_{OSC}$ = 16 MHz<br>$F_{OSC}$ = 24 MHz                                                        |

| I <sub>PD</sub>  | Power-Down Current                                                                          |                                                                         | 2                      | 20                        | μA    | $V_{RET} < V_{DD} < 5.5 V$                                                                                            |

| $V_{PP}$         | Programming supply voltage                                                                  | 12.5                                                                    |                        | 13                        | V     | $T_A = 0$ to +40°C                                                                                                    |

| I <sub>PP</sub>  | Programming supply current                                                                  | 1                                                                       |                        | 75                        | mA    | T <sub>A</sub> = 0 to +40°C                                                                                           |

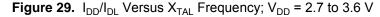

## Low Voltage Versions - Commercial & Industrial

| Table 56. | DC Characteristics; | V <sub>DD</sub> = 2.7 to | 5.5 V, T <sub>A</sub> | = -40 to +85°C |

|-----------|---------------------|--------------------------|-----------------------|----------------|

|-----------|---------------------|--------------------------|-----------------------|----------------|

| Symbol              | Parameter                                                                                   | Min                       | Typical <sup>(4)</sup> | Max                       | Units | Test Conditions                                                                                                                                                                                                                    |

|---------------------|---------------------------------------------------------------------------------------------|---------------------------|------------------------|---------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>     | Input Low Voltage<br>(except EA#, SCL, SDA)                                                 | -0.5                      |                        | 0.2·V <sub>DD</sub> - 0.1 | V     |                                                                                                                                                                                                                                    |

| $V_{IL1}^{(5)}$     | Input Low Voltage<br>(SCL, SDA)                                                             | -0.5                      |                        | 0.3·V <sub>DD</sub>       | v     |                                                                                                                                                                                                                                    |

| V <sub>IL2</sub>    | Input Low Voltage<br>(EA#)                                                                  | 0                         |                        | 0.2·V <sub>DD</sub> - 0.3 | V     |                                                                                                                                                                                                                                    |

| V <sub>IH</sub>     | Input high Voltage<br>(except XTAL1, RST, SCL, SDA)                                         | 0.2·V <sub>DD</sub> + 0.9 |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                                                                                                                                    |

| $V_{\rm IH1}^{(5)}$ | Input high Voltage<br>(XTAL1, RST, SCL, SDA)                                                | 0.7·V <sub>DD</sub>       |                        | V <sub>DD</sub> + 0.5     | v     |                                                                                                                                                                                                                                    |

| V <sub>OL</sub>     | Output Low Voltage<br>(Ports 1, 2, 3)                                                       |                           |                        | 0.45                      | v     | $I_{OL} = 0.8 \text{ mA}^{(1)(2)}$                                                                                                                                                                                                 |

| V <sub>OL1</sub>    | Output Low Voltage<br>(Ports 0, ALE, PSEN#, Port 2 in Page<br>Mode during External Address) |                           |                        | 0.45                      | v     | I <sub>OL</sub> = 1.6 mA <sup>(1)(2)</sup>                                                                                                                                                                                         |

| V <sub>OH</sub>     | Output high Voltage<br>(Ports 1, 2, 3, ALE, PSEN#)                                          | 0.9·V <sub>DD</sub>       |                        |                           | V     | I <sub>OH</sub> = -10 μA <sup>(3)</sup>                                                                                                                                                                                            |

| V <sub>OH1</sub>    | Output high Voltage<br>(Port 0, Port 2 in Page Mode during<br>External Address)             | 0.9·V <sub>DD</sub>       |                        |                           | v     | Ι <sub>ΟΗ</sub> = -40 μΑ                                                                                                                                                                                                           |

| $V_{RET}$           | V <sub>DD</sub> data retention limit                                                        |                           |                        | 1.8                       | V     |                                                                                                                                                                                                                                    |

| I <sub>ILO</sub>    | Logical 0 Input Current<br>(Ports 1, 2, 3 - AWAIT#)                                         |                           |                        | - 50                      | μA    | V <sub>IN</sub> = 0.45 V                                                                                                                                                                                                           |

| I <sub>IL1</sub>    | Logical 1 Input Current<br>(NMI)                                                            |                           |                        | + 50                      | μA    | V <sub>IN</sub> = V <sub>DD</sub>                                                                                                                                                                                                  |

| I <sub>LI</sub>     | Input Leakage Current<br>(Port 0)                                                           |                           |                        | ± 10                      | μA    | 0.45 V < V <sub>IN</sub> < V <sub>DD</sub>                                                                                                                                                                                         |

| I <sub>TL</sub>     | Logical 1-to-0 Transition Current<br>(Ports 1, 2, 3)                                        |                           |                        | - 650                     | μA    | V <sub>IN</sub> = 2.0 V                                                                                                                                                                                                            |

| R <sub>RST</sub>    | RST Pull-Down Resistor                                                                      | 40                        | 110                    | 225                       | kΩ    |                                                                                                                                                                                                                                    |

| C <sub>IO</sub>     | Pin Capacitance                                                                             |                           | 10                     |                           | pF    | T <sub>A</sub> = 25°C                                                                                                                                                                                                              |

| I <sub>DD</sub>     | Operating Current                                                                           |                           | 4<br>8<br>9<br>11      | 8<br>11<br>12<br>14       | mA    | $\begin{array}{l} 5 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 10 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 12 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 16 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \end{array}$ |

| I <sub>DL</sub>     | Idle Mode Current                                                                           |                           | 0.5<br>1.5<br>2<br>3   | 1<br>4<br>5<br>7          | mA    | $\begin{array}{c} 5 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 10 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 12 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 16 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \end{array}$ |

| I <sub>PD</sub>     | Power-Down Current                                                                          |                           | 1                      | 10                        | μA    | V <sub>RET</sub> < V <sub>DD</sub> < 3.6 V                                                                                                                                                                                         |

Notes: 1. Under steady-state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum IOL per port pin: 10 mA

Maximum IOL per 8-bit port: Port 0 26 mA

Ports 1-315 mA

Maximum Total IOL for all:Output Pins71 mA

If IOL exceeds the test conditions, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 2. Capacitive loading on Ports 0 and 2 may cause spurious noise pulses above 0.4 V on the low-level outputs of ALE and Ports 1, 2, and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins change from high to low. In applications where capacitive loading exceeds 100 pF, the noise pulses on these signals may exceed 0.8 V. It may be desirable to qualify ALE or other signals with a Schmitt Trigger or CMOS-level input logic.

- Capacitive loading on Ports 0 and 2 causes the V<sub>OH</sub> on ALE and PSEN# to drop below the specification when the address lines are stabilizing.

- 4. Typical values are obtained using  $V_{DD}$  = 3 V and  $T_A$  = 25°C. They are not tested and there is not guarantee on these values.

- The input threshold voltage of SCL and SDA meets the TWI specification, so an input voltage below 0.3 V<sub>DD</sub> will be recognized as a logic 0 while an input voltage above 0.7 V<sub>DD</sub> will be recognized as a logic 1.

Note: 1.The clock prescaler is not used:  $F_{OSC} = F_{XTAL}$ .

### $I_{DD}$ , $I_{DL}$ and $I_{PD}$ Test Conditions

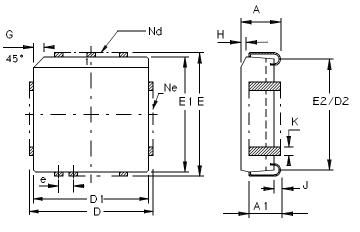

## PLCC 44 - Mechanical Outline

#### Table 59. PLCC Package Size

|    | м     | М     | Inc      | ch   |

|----|-------|-------|----------|------|

|    | Min   | Max   | Min      | Max  |

| А  | 4.20  | 4.57  | .165     | .180 |

| A1 | 2.29  | 3.04  | .090     | .120 |

| D  | 17.40 | 17.65 | .685     | .695 |

| D1 | 16.44 | 16.66 | .647     | .656 |

| D2 | 14.99 | 16.00 | .590     | .630 |

| E  | 17.40 | 17.65 | .685     | .695 |

| E1 | 16.44 | 16.66 | .647     | .656 |

| E2 | 14.99 | 16.00 | .590     | .630 |

| е  | 1.27  | BSC   | .050 BSC |      |

| G  | 1.07  | 1.22  | .042     | .048 |

| Н  | 1.07  | 1.42  | .042     | .056 |

| J  | 0.51  | -     | .020     | -    |

| К  | 0.33  | 0.53  | .013     | .021 |

| Nd | 11    |       | 1        | 1    |

| Ne | 11    |       | 1        | 1    |

| Part Number <sup>(1)</sup>        | ROM         | Description                            |  |  |  |

|-----------------------------------|-------------|----------------------------------------|--|--|--|

| Low Voltage Versions 2.7 to 5.5 V |             |                                        |  |  |  |

| TSC251G2Dxxx-L16CB                | 32K MaskROM | 16 MHz, Commercial 0° to 70°C, PLCC 44 |  |  |  |

| TSC251G2Dxxx-L16CE                | 32K MaskROM | 16 MHz, Commercial 0° to 70°C, VQFP 44 |  |  |  |

| AT251G2Dxxx-SLSUL                 | 32K MaskROM | 16 MHz, Industrial & Green, PLCC 44    |  |  |  |

| AT251G2Dxxx-RLTUL                 | 32K MaskROM | 16 MHz, Industrial & Green, VQFP 44    |  |  |  |

Note: 1. xxx: means ROM code, is Cxxx in case of encrypted code.

### AT/TSC87251G2D OTPROM

| Part Number                                                 | ROM        | Description                                      |

|-------------------------------------------------------------|------------|--------------------------------------------------|

| High Speed Versions 4.5 to 5.5 V, Commercial and Industrial |            |                                                  |

| TSC87251G2D-16CB                                            | 32K OTPROM | 16 MHz, Commercial 0° to 70°C, PLCC 44           |

| TSC87251G2D-24CB                                            | 32K OTPROM | 24 MHz, Commercial 0° to 70°C, PLCC 44           |

| TSC87251G2D-24CED                                           | 32K OTPROM | 24 MHz, Commercial 0° to 70°C, VQFP 44           |

| TSC87251G2D-24IA                                            | 32K OTPROM | 24 MHz, Industrial -40° to 85°C, PDIL 40         |

| TSC87251G2D-24IB                                            | 32K OTPROM | 24 MHz, Industrial -40° to 85°C, PLCC 44         |

| AT87251G2D-SLSUM                                            | 32K OTPROM | 24 MHz, Industrial & Green -40° to 85°C, PLCC 44 |

| AT87251G2D-3CSUM                                            | 32K OTPROM | 24 MHz, Industrial & Green -40° to 85°C, PDIL 40 |

| AT87251G2D-RLTUM                                            | 32K OTPROM | 24 MHz, Industrial & Green -40° to 85°C, VQFP 44 |

| Low Voltage Versions 2.7 to 5.5 V                           |            |                                                  |

| TSC87251G2D-L16CB                                           | 32K OTPROM | 16 MHz, Commercial 0° to 70°C, PLCC 44           |

| TSC87251G2D-L16CED                                          | 32K OTPROM | 16 MHz, Commercial 0° to 70°C, VQFP 44           |

| AT87251G2D-SLSUL                                            | 32K OTPROM | 16 MHz, Industrial & Green, 0° to 70°C, PLCC 44  |

| AT87251G2D-RLTUL                                            | 32K OTPROM | 16 MHz, Industrial & Green, 0° to 70°C, VQFP 44  |

## **Document Revision History**

**Changes from** 1. Added automotive qualification, and ordering information for ROM product version.

- 4135D to 4135E

- 1. Absolute Maximum Ratings added for automotive product version.