Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | C251                                                                       |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 24MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, Microwire, SPI, UART/USART                      |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at87251g2d-slsum |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

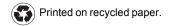

# **Block Diagram**

| Table 2 | Product Name | Signal Description | (Continued) |

|---------|--------------|--------------------|-------------|

|---------|--------------|--------------------|-------------|

|                | Tiouu | ct Name Signal Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |  |  |  |

|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| Signal<br>Name | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Alternate<br>Function |  |  |  |

| NMI            | I     | Non Maskable Interrupt<br>Holding this pin high for 24 oscillator periods triggers an interrupt.<br>When using the Product Name as a pin-for-pin replacement for a 8xC51<br>product, NMI can be unconnected without loss of compatibility or power<br>consumption increase (on-chip pull-down).<br>Not available on DIP package.                                                                                                                                                                                                               | -                     |  |  |  |

| P0.0:7         | I/O   | $\begin{array}{c} \mbox{Port 0} \\ \mbox{P0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s} \\ \mbox{I/O} & \mbox{written to them float and can be used as high impedance inputs. To avoid any paraitic current consumption, Floating P0 inputs must be polarized to $V_{DD}$ or $V_{SS}$.} \end{array}$                                                                                                                                                                                                              |                       |  |  |  |

| P1.0:7         | I/O   | I/O Port 1<br>P1 is an 8-bit bidirectional I/O port with internal pull-ups. P1 provides<br>interrupt capability for a keyboard interface.                                                                                                                                                                                                                                                                                                                                                                                                      |                       |  |  |  |

| P2.0:7         | I/O   | Port 2<br>P2 is an 8-bit bidirectional I/O port with internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A15:8                 |  |  |  |

| P3.0:7         | I/O   | <b>Port 3</b><br>P3 is an 8-bit bidirectional I/O port with internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                     |  |  |  |

| PROG#          | I     | <b>Programming Pulse input</b><br>The programming pulse is applied to this input for programming the on-chip<br>EPROM/OTPROM.                                                                                                                                                                                                                                                                                                                                                                                                                  | Ι                     |  |  |  |

| PSEN#          | 0     | O PSEN# is asserted for a memory address range that depends on bits RD0 and RD1 in UCONFIG0 byte (see ).                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |  |  |  |

| RD#            | 0     | Read or 17 <sup>th</sup> Address Bit (A16)         O         Read signal output to external data memory depending on the values of bits RD0 and RD1 in UCONFIG0 byte (see Table 13, Page 20).                                                                                                                                                                                                                                                                                                                                                  |                       |  |  |  |

| RST            | I     | <b>Reset input to the chip</b><br>Holding this pin high for 64 oscillator periods while the oscillator is running<br>resets the device. The Port pins are driven to their reset conditions when a<br>voltage greater than $V_{IH1}$ is applied, whether or not the oscillator is running.<br>This pin has an internal pull-down resistor which allows the device to be<br>reset by connecting a capacitor between this pin and VDD.<br>Asserting RST when the chip is in Idle mode or Power-Down mode returns<br>the chip to normal operation. | _                     |  |  |  |

| RXD            | I/O   | <b>Receive Serial Data</b><br>RXD sends and receives data in serial I/O mode 0 and receives data in<br>serial I/O modes 1, 2 and 3.                                                                                                                                                                                                                                                                                                                                                                                                            | P3.0                  |  |  |  |

| SCL            | I/O   | TWI Serial Clock<br>When TWI controller is in master mode, SCL outputs the serial clock to<br>slave peripherals. When TWI controller is in slave mode, SCL receives<br>clock from the master controller.                                                                                                                                                                                                                                                                                                                                       | P1.6                  |  |  |  |

| SCK            | I/O   | <b>SPI Serial Clock</b><br>When SPI is in master mode, SCK outputs clock to the slave peripheral.<br>When SPI is in slave mode, SCK receives clock from the master controller.                                                                                                                                                                                                                                                                                                                                                                 | P1.6                  |  |  |  |

| SDA            | I/O   | TWI Serial Data<br>SDA is the bidirectional TWI data line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P1.7                  |  |  |  |

| SS#            | I     | SPI Slave Select Input<br>When in Slave mode, SS# enables the slave mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P1.4                  |  |  |  |

| Table 2. Product Name Signal Description (Continued) |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                   |                       |  |  |  |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| Signal<br>Name                                       | Туре                                                                                                                                                                                                                                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                                       | Alternate<br>Function |  |  |  |

| T1:0                                                 | I/O                                                                                                                                                                                                                                                                                                                                          | <b>Timer 1:0 External Clock Inputs</b><br>When timer 1:0 operates as a counter, a falling edge on the T1:0 pin increments the count.                                                                                                                                                                                                              | -                     |  |  |  |

| T2                                                   | I/O                                                                                                                                                                                                                                                                                                                                          | <b>Timer 2 Clock Input/Output</b><br>For the timer 2 capture mode, T2 is the external clock input. For the Timer 2 clock-out mode, T2 is the clock output.                                                                                                                                                                                        | P1.0                  |  |  |  |

| T2EX                                                 | <ul> <li>Timer 2 External Input         In timer 2 capture mode, a falling edge initiates a capture of the timer 2         X         I registers. In auto-reload mode, a falling edge causes the timer 2 register to be reloaded. In the up-down counter mode, this signal determines the count direction: 1 = up, 0 = down.     </li> </ul> |                                                                                                                                                                                                                                                                                                                                                   |                       |  |  |  |

| тхр                                                  | O Transmit Serial Data<br>TXD outputs the shift clock in serial I/O mode 0 and transmits data in serial<br>I/O modes 1, 2 and 3.                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                   |                       |  |  |  |

| VDD                                                  | PWR                                                                                                                                                                                                                                                                                                                                          | Digital Supply Voltage           Connect this pin to +5V or +3V supply voltage.                                                                                                                                                                                                                                                                   |                       |  |  |  |

| VPP                                                  | VPP         I         Programming Supply Voltage<br>The programming supply voltage is applied to this input for programming<br>the on-chip EPROM/OTPROM.                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                   |                       |  |  |  |

| VSS                                                  | S GND Circuit Ground<br>Connect this pin to ground.                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                   |                       |  |  |  |

| VSS1                                                 | GND                                                                                                                                                                                                                                                                                                                                          | Secondary Ground 1<br>This ground is provided to reduce ground bounce and improve power<br>supply bypassing. Connection of this pin to ground is recommended.<br>However, when using the TSC80251G2D as a pin-for-pin replacement for a<br>8xC51 product, VSS1 can be unconnected without loss of compatibility.<br>Not available on DIP package. | Ι                     |  |  |  |

| VSS2                                                 | Secondary Ground 2<br>This ground is provided to reduce ground bounce and improve power<br>supply bypassing. Connection of this pin to ground is recommended.                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                   | _                     |  |  |  |

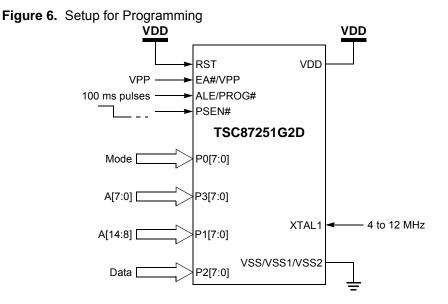

| WAIT#                                                | I                                                                                                                                                                                                                                                                                                                                            | <b>Real-time Synchronous Wait States Input</b><br>The real-time WAIT# input is enabled by setting RTWE bit in WCON<br>(S:A7h). During bus cycles, the external memory system can signal<br>'system ready' to the microcontroller in real time by controlling the WAIT#<br>input signal.                                                           | P1.6                  |  |  |  |

| WCLK                                                 | 0                                                                                                                                                                                                                                                                                                                                            | Wait Clock Output<br>The real-time WCLK output is enabled by setting RTWCE bit in WCON<br>(S:A7h). When enabled, the WCLK output produces a square wave signal<br>with a period of one half the oscillator frequency.                                                                                                                             | P1.7                  |  |  |  |

| WR#                                                  | 0                                                                                                                                                                                                                                                                                                                                            | <b>Write</b><br>Write signal output to external memory.                                                                                                                                                                                                                                                                                           | P3.6                  |  |  |  |

| XTAL1                                                | I                                                                                                                                                                                                                                                                                                                                            | Input to the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected to this<br>pin. If an external oscillator is used, its output is connected to this pin.<br>XTAL1 is the clock source for internal timing.                                                                         | -                     |  |  |  |

Table 2.

Product Name Signal Description (Continued)

| Table 2. | Product Name Signal Description | (Continued) |

|----------|---------------------------------|-------------|

|----------|---------------------------------|-------------|

| Signal<br>Name | Туре | Description                                                                                                                                                                                                  | Alternate<br>Function |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| XTAL2          | ο    | Output of the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected to this<br>pin. If an external oscillator is used, leave XTAL2 unconnected. | _                     |

Note: The description of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the Non-Page mode chip configuration. If the chip is configured in Page mode operation, port 0 carries the lower address bits (A7:0) while port 2 carries the upper address bits (A15:8) and the data (D7:0).

# **Configuration Bytes**

The TSC80251G2D derivatives provide user design flexibility by configuring certain operating features at device reset. These features fall into the following categories:

- external memory interface (Page mode, address bits, programmed wait states and the address range for RD#, WR#, and PSEN#)

- source mode/binary mode opcodes

- selection of bytes stored on the stack by an interrupt

- mapping of the upper portion of on-chip code memory to region 00:

Two user configuration bytes UCONFIG0 (see Table 11) and UCONFIG1 (see Table 12) provide the information.

When EA# is tied to a low level, the configuration bytes are fetched from the external address space. The TSC80251G2D derivatives reserve the top eight bytes of the memory address space (FF:FFF8h-FF:FFFh) for an external 8-byte configuration array. Only two bytes are actually used: UCONFIG0 at FF:FFF8h and UCONFIG1 at FF:FFF9h.

For the mask ROM devices, configuration information is stored in on-chip memory (see ROM Verifying). When EA# is tied to a high level, the configuration information is retrieved from the on-chip memory instead of the external address space and there is no restriction in the usage of the external memory.

# **Table 11.** Configuration Byte 0UCONFIG0

| 7          | 6               | 5                        | 4                                                       | 3                                                          | 2                                             | 1              | 0              |

|------------|-----------------|--------------------------|---------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------|----------------|----------------|

| -          | WSA1#           | WSA0#                    | XALE#                                                   | RD1                                                        | RD0                                           | PAGE#          | SRC            |

| Bit Number | Bit<br>Mnemonic | Descriptio               | n                                                       |                                                            |                                               |                |                |

| 7          | -               | Reserved<br>Set this bit | when writing                                            | to UCONFIG0                                                | ).                                            |                |                |

| 6          | WSA1#           | Wait State               |                                                         |                                                            |                                               |                | fan ar fam al  |

| 5          | WSA0#           |                          | cesses (all re<br><u>VSA0#</u> <u>Nu</u><br>3<br>2<br>1 | it states for RL<br>gions except (<br><u>umber of Wait</u> | ,                                             | -SEN# signals  | s for external |

| 4          | XALE#           |                          | tend the dura                                           |                                                            | E pulse from T<br>E pulse to 1·T <sub>o</sub> |                |                |

| 3          | RD1             | -                        | gnal Select                                             |                                                            |                                               |                |                |

| 2          | RD0             |                          |                                                         | s (see Table 1                                             | al address bu<br>3).                          | s and the usag | ge of RD#,     |

| 1          | PAGE#           | Clear to sel<br>Port 0.  |                                                         | Page mode v                                                | vith A15:8/D7:<br>h A15:8 on Po               |                |                |

| 0          | SRC             | Clear to set             | de/Binary M<br>lect the binary<br>ct the source         |                                                            | t                                             |                |                |

Notes: 1. UCONFIG0 is fetched twice so it can be properly read both in Page or Non-Page modes. If P2.1 is cleared during the first data fetch, a Page mode configuration is used, otherwise the subsequent fetches are performed in Non-Page mode.

2. This selection provides compatibility with the standard 80C51 hardware which is multiplexing the address LSB and the data on Port 0.

# **Configuration Byte 1**

# Table 13. Address Ranges and Usage of RD#, WR# and PSEN# Signals

| RD1 | RD0 | P1.7    | P3.7/RD#                                     | PSEN#                                               | WR#                                                  | External<br>Memory       |

|-----|-----|---------|----------------------------------------------|-----------------------------------------------------|------------------------------------------------------|--------------------------|

| 0   | 0   | A17     | A16                                          | Read signal for all<br>external memory<br>locations | Write signal for all<br>external memory<br>locations | 256 KB                   |

| 0   | 1   | I/O pin | A16                                          | Read signal for all<br>external memory<br>locations | Write signal for all<br>external memory<br>locations | 128 KB                   |

| 1   | 0   | I/O pin | I/O pin                                      | Read signal for all external memory locations       | Write signal for all external memory locations       | 64 KB                    |

| 1   | 1   | I/O pin | Read<br>signal for<br>regions 00:<br>and 01: | Read signal for<br>regions FE: and FF:              | Write signal for all<br>external memory<br>locations | 2 × 64 KB <sup>(1)</sup> |

Notes: 1. This selection provides compatibility with the standard 80C51 hardware which has separate external memory spaces for data and code.

# Size and Execution Time for Instruction Families

#### Table 20. Summary of Add and Subtract Instructions

| AddADD <dest>, <src>dest opnd <math>\leftarrow</math> dest opnd + src opnd</src></dest>                       |

|---------------------------------------------------------------------------------------------------------------|

| SubtractSUB <dest>, <src>dest opnd <math display="inline">\leftarrow</math> dest opnd - src opnd</src></dest> |

| Add with CarryADDC <dest>, <src>(A) <math>\leftarrow</math> (A) + src opnd + (CY)</src></dest>                |

| Subtract with BorrowSUBB <dest>, <src>(A) <math>\leftarrow</math> (A) - src opnd - (CY)</src></dest>          |

|               | -dost>                                       |                                                               | Binary | Mode             | Source | e Mode           |

|---------------|----------------------------------------------|---------------------------------------------------------------|--------|------------------|--------|------------------|

| Mnemonic      | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                                      | Bytes  | States           | Bytes  | States           |

|               | A, Rn                                        | Register to ACC                                               | 1      | 1                | 2      | 2                |

|               | A, dir8                                      | Direct address to ACC                                         | 2      | 1 <sup>(2)</sup> | 2      | 1 <sup>(2)</sup> |

| ADD           | A, at Ri                                     | Indirect address to ACC                                       | 1      | 2                | 2      | 3                |

|               | A, #data                                     | Immediate data to ACC                                         | 2      | 1                | 2      | 1                |

|               | Rmd, Rms                                     | Byte register to/from byte register                           | 3      | 2                | 2      | 1                |

|               | WRjd, WRjs                                   | Word register to/from word register                           | 3      | 3                | 2      | 2                |

|               | DRkd, DRks                                   | Dword register to/from dword register                         | 3      | 5                | 2      | 4                |

|               | Rm, #data                                    | Immediate 8-bit data to/from byte register                    | 4      | 3                | 3      | 2                |

|               | WRj, #data16                                 | Immediate 16-bit data to/from word register                   | 5      | 4                | 4      | 3                |

|               | DRk,<br>#0data16                             | 16-bit unsigned immediate data to/from dword register         | 5      | 6                | 4      | 5                |

| ADD/SUB       | Rm, dir8                                     | Direct address (on-chip RAM or SFR)<br>to/from byte register  | 4      | 3 <sup>(2)</sup> | 3      | 2 <sup>(2)</sup> |

|               | WRj, dir8                                    | Direct address (on-chip RAM or SFR) to/from word register     | 4      | 4                | 3      | 3                |

|               | Rm, dir16                                    | Direct address (64K) to/from byte<br>register                 | 5      | 3 <sup>(3)</sup> | 4      | 2 <sup>(3)</sup> |

|               | WRj, dir16                                   | Direct address (64K) to/from word register                    | 5      | 4 <sup>(4)</sup> | 4      | 3 <sup>(4)</sup> |

|               | Rm, at WRj                                   | Indirect address (64K) to/from byte register                  | 4      | 3 <sup>(3)</sup> | 3      | 2 <sup>(3)</sup> |

|               | Rm, at DRk                                   | k Indirect address (16M) to/from byte register                |        | 4 <sup>(3)</sup> | 3      | 3 <sup>(3)</sup> |

|               | A, Rn                                        | Register to/from ACC with carry                               | 1      | 1                | 2      | 2                |

|               | A, dir8                                      | Direct address (on-chip RAM or SFR)<br>to/from ACC with carry | 2      | 1 <sup>(2)</sup> | 2      | 1 <sup>(2)</sup> |

| ADDC/SU<br>BB | A, at Ri                                     | Indirect address to/from ACC with carry                       | 1      | 2                | 2      | 3                |

|               | A, #data                                     | Immediate data to/from ACC with carry                         | 2      | 1                | 2      | 1                |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

3. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

- Notes: 1. Logical instructions that affect a bit are in Table 27.

- 2. A shaded cell denotes an instruction in the C51 Architecture.

- 3. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 4. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

- 5. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

- 6. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

| Table 23. | Summar | of Logical | Instructions | (2/2) |

|-----------|--------|------------|--------------|-------|

|           |        |            |              |       |

| $ \begin{array}{l} \text{Shift Left LogicalSLL _{0} \leftarrow 0 \\ < dest>_{n+1} \leftarrow < dest>_{n}, n = 0msb-1 \\ (CY) \leftarrow < dest>_{msb} \end{array} \\ \text{Shift Right ArithmeticSRA _{msb} \leftarrow _{msb} \\ < dest>_{n-1} \leftarrow _{n}, n = msb1 \\ (CY) \leftarrow _{0} \end{array} \\ \text{Shift Right LogicalSRL _{msb} \leftarrow 0 \\ _{n-1} \leftarrow _{n}, n = msb1 \\ (CY) \leftarrow _{0} \end{array} \\ \text{SwapSWAP AA}_{3:0} A_{7:4} \end{array} $ |                           |                                          |       |        |       |        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------|-------|--------|-------|--------|--|

| <pre><dest>,</dest></pre> Binary Mode Source Mode                                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |                                          |       |        |       |        |  |

| Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <src><sup>(1)</sup></src> | Comments                                 | Bytes | States | Bytes | States |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Rm                        | Shift byte register left through the MSB | 3     | 2      | 2     | 1      |  |

| SLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | WRj                       | Shift word register left through the MSB | 3     | 2      | 2     | 1      |  |

| CDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Rm                        | Shift byte register right                | 3     | 2      | 2     | 1      |  |

| SRA WRj                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           | Shift word register right                | 3     | 2      | 2     | 1      |  |

| SRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Rm                        | Shift byte register left                 | 3     | 2      | 2     | 1      |  |

| JRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | WRj                       | Shift word register left                 | 3     | 2      | 2     | 1      |  |

| SWAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | А                         | Swap nibbles within ACC                  | 1     | 2      | 1     | 2      |  |

Note: 1. A shaded cell denotes an instruction in the C51 Architecture.

|          |                                              |                                                    | Binary Mode Source Mod |                  |       |                  |

|----------|----------------------------------------------|----------------------------------------------------|------------------------|------------------|-------|------------------|

| Mnemonic | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                           | Bytes                  | States           | Bytes | State            |

|          | A, Rn                                        | ACC and register                                   | 1                      | 3                | 2     | 4                |

| ХСН      | A, dir8                                      | ACC and direct address (on-chip RAM or SFR)        | 2                      | 3 <sup>(3)</sup> | 2     | 3 <sup>(3)</sup> |

|          | A, at Ri                                     | ACC and indirect address                           | 1                      | 4                | 2     | 5                |

| XCHD     | A, at Ri                                     | ACC low nibble and indirect address (256 bytes)    | 1                      | 4                | 2     | 5                |

|          | dir8                                         | Push direct address onto stack                     | 2                      | 2 <sup>(2)</sup> | 2     | 2(2              |

|          | #data                                        | Push immediate data onto stack                     | 4                      | 4                | 3     | 3                |

| PUSH     | #data16                                      | Push 16-bit immediate data onto stack              | 5                      | 5                | 4     | 5                |

| F 0311   | Rm                                           | Push byte register onto stack                      | 3                      | 4                | 2     | 3                |

|          | WRj                                          | Push word register onto stack                      | 3                      | 5                | 2     | 4                |

|          | DRk                                          | Push double word register onto stack               | 3                      | 9                | 2     | 8                |

|          | dir8                                         | Pop direct address (on-chip RAM or SFR) from stack | 2                      | 3 <sup>(2)</sup> | 2     | 3(2              |

| POP      | Rm                                           | Pop byte register from stack                       | 3                      | 3                | 2     | 2                |

|          | WRj                                          | Pop word register from stack                       | 3                      | 5                | 2     | 4                |

|          | DRk                                          | Pop double word register from stack                | 3                      | 9                | 2     | 8                |

#### Table 28. Summary of Exchange, Push and Pop Instructions

Exchange bytesXCH A, <src>(A)  $\leftrightarrow$  src opnd

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

3. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

| Table 29. | Summar | of Conditional Jump Instructions ( | (1/2) |

|-----------|--------|------------------------------------|-------|

|-----------|--------|------------------------------------|-------|

|          | onal on statu<br>HEN (PC) ← | sJcc rel(PC) $\leftarrow$ (PC) + size (instr);<br>- (PC) + rel |        |                    |        |                    |

|----------|-----------------------------|----------------------------------------------------------------|--------|--------------------|--------|--------------------|

|          | <dest>,</dest>              |                                                                | Binary | Mode               | Source | e Mode             |

| Mnemonic | <src><sup>(1)</sup></src>   | Comments                                                       | Bytes  | States             | Bytes  | States             |

| JC       | rel                         | Jump if carry                                                  | 2      | 1/4 <sup>(3)</sup> | 2      | 1/4 <sup>(3)</sup> |

| JNC      | rel                         | Jump if not carry                                              | 2      | 1/4 <sup>(3)</sup> | 2      | 1/4 <sup>(3)</sup> |

| JE       | rel                         | Jump if equal                                                  | 3      | 2/5 <sup>(3)</sup> | 2      | 1/4 <sup>(3)</sup> |

| JNE      | rel                         | Jump if not equal                                              | 3      | 2/5 <sup>(3)</sup> | 2      | 1/4 <sup>(3)</sup> |

| JG       | rel                         | Jump if greater than                                           | 3      | 2/5 <sup>(3)</sup> | 2      | 1/4 <sup>(3)</sup> |

| JLE      | rel                         | Jump if less than, or equal                                    | 3      | 2/5 <sup>(3)</sup> | 2      | 1/4 <sup>(3)</sup> |

| JSL      | rel                         | Jump if less than (signed)                                     | 3      | 2/5 <sup>(3)</sup> | 2      | 1/4 <sup>(3)</sup> |

| JSLE     | rel                         | Jump if less than, or equal (signed)                           | 3      | 2/5 <sup>(3)</sup> | 2      | 1/4 <sup>(3)</sup> |

| JSG      | rel                         | Jump if greater than (signed)                                  | 3      | 2/5 <sup>(3)</sup> | 2      | 1/4 <sup>(3)</sup> |

| JSGE     | rel                         | Jump if greater than or equal (signed)                         | 3      | 2/5 <sup>(3)</sup> | 2      | 1/4 <sup>(3)</sup> |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. States are given as jump not-taken/taken.

3. In internal execution only, add 1 to the number of states of the 'jump taken' if the destination address is internal and odd.

Add 3 if it addresses a Peripheral SFR.

- 5. If this instruction addresses an I/O Port (Px, x = 0-3), add 3 to the number of states. Add 5 if it addresses a Peripheral SFR.

- 6. In internal execution only, add 1 to the number of states of the 'jump taken' if the destination address is internal and odd.

#### Table 31. Summary of Unconditional Jump Instructions

Absolute jumpAJMP <src>(PC)  $\leftarrow$  (PC) +2; (PC)<sub>10:0</sub>  $\leftarrow$  src opnd Extended jumpEJMP <src>(PC)  $\leftarrow$  (PC) + size (instr); (PC)<sub>23:0</sub>  $\leftarrow$  src opnd Long jumpLJMP <src>(PC)  $\leftarrow$  (PC) + size (instr); (PC)<sub>15:0</sub>  $\leftarrow$  src opnd Short jumpSJMP rel(PC)  $\leftarrow$  (PC) +2; (PC)  $\leftarrow$  (PC) +rel Jump indirectJMP at A +DPTR(PC)<sub>23:16</sub>  $\leftarrow$  FFh; (PC)<sub>15:0</sub>  $\leftarrow$  (A) + (DPTR) No operationNOP(PC)  $\leftarrow$  (PC) +1

|          | <dest>,</dest>            |                                    | Binary | Mode                | Source | e Mode              |

|----------|---------------------------|------------------------------------|--------|---------------------|--------|---------------------|

| Mnemonic | <src><sup>(1)</sup></src> | Comments                           | Bytes  | States              | Bytes  | States              |

| AJMP     | addr11                    | Absolute jump                      | 2      | 3 <sup>(2)(3)</sup> | 2      | 3 <sup>(2)(3)</sup> |

| EJMP     | addr24                    | Extended jump                      | 5      | 6 <sup>(2)(4)</sup> | 4      | 5 <sup>(2)(4)</sup> |

| EJIVIP   | at DRk                    | Extended jump (indirect)           | 3      | 7 <sup>(2)(4)</sup> | 2      | 6 <sup>(2)(4)</sup> |

| LJMP     | at WRj                    | Long jump (indirect)               | 3      | 6 <sup>(2)(4)</sup> | 2      | 5 <sup>(2)(4)</sup> |

| LJIMP    | addr16                    | Long jump (direct address)         | 3      | 5 <sup>(2)(4)</sup> | 3      | 5 <sup>(2)(4)</sup> |

| SJMP     | rel                       | Short jump (relative address)      | 2      | 4 <sup>(2)(4)</sup> | 2      | 4 <sup>(2)(4)</sup> |

| JMP      | at A +DPTR                | Jump indirect relative to the DPTR | 1      | 5 <sup>(2)(4)</sup> | 1      | 5 <sup>(2)(4)</sup> |

| NOP      |                           | No operation (Jump never)          | 1      | 1                   | 1      | 1                   |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

- 2. In internal execution only, add 1 to the number of states if the destination address is internal and odd.

- 3. Add 2 to the number of states if the destination address is external.

- 4. Add 3 to the number of states if the destination address is external.

| Table 32. | Summar | of Call and | Return | Instructions |

|-----------|--------|-------------|--------|--------------|

|-----------|--------|-------------|--------|--------------|

|                                | ACALL <src><br/><math>\leftarrow</math> src opnd</src> | $(PC) \leftarrow (PC)$ +2; push $(PC)_{15:0}$ ;                                                                                                                                                           |                            |                                                                                                                 |                            |                                                                                                                                     |

|--------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Extended ca                    |                                                        | $P(PC) \leftarrow (PC) + size (instr); push (PC)_2$                                                                                                                                                       | 3:0,                       |                                                                                                                 |                            |                                                                                                                                     |

| Long callLCA                   |                                                        | ) $\leftarrow$ (PC) + size (instr); push (PC) <sub>15:0</sub> ;                                                                                                                                           |                            |                                                                                                                 |                            |                                                                                                                                     |

| Return from                    | subroutineRE                                           | Tpop (PC) <sub>15:0</sub>                                                                                                                                                                                 |                            |                                                                                                                 |                            |                                                                                                                                     |

|                                |                                                        | outineERETpop(PC) <sub>23:0</sub>                                                                                                                                                                         |                            |                                                                                                                 |                            |                                                                                                                                     |

|                                |                                                        | IF [INTR = 0] THEN pop (PC) <sub>15:0</sub><br>pop (PC) <sub>23:0</sub> ; pop (PSW1)                                                                                                                      |                            |                                                                                                                 |                            |                                                                                                                                     |

| Trap interrup<br>IF [INTF      | tTRAP(PC) ←<br>R = 0] THEN p                           | - (PC) + size (instr);                                                                                                                                                                                    |                            |                                                                                                                 |                            |                                                                                                                                     |

|                                |                                                        |                                                                                                                                                                                                           | Binary                     | / Mode                                                                                                          | Source                     | e Mode                                                                                                                              |

|                                | <dest>,</dest>                                         |                                                                                                                                                                                                           |                            |                                                                                                                 | <b>.</b>                   | _                                                                                                                                   |

| Mnemonic                       | <src><sup>(1)</sup></src>                              | Comments                                                                                                                                                                                                  | Bytes                      | States                                                                                                          | Bytes                      | States                                                                                                                              |

| Mnemonic<br>ACALL              | <src>(")<br/>addr11</src>                              | Comments           Absolute subroutine call                                                                                                                                                               | Bytes<br>2                 | 9 <sup>(2)(3)</sup>                                                                                             | Bytes<br>2                 |                                                                                                                                     |

| ACALL                          |                                                        |                                                                                                                                                                                                           | -                          |                                                                                                                 | -                          | States<br>9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                                                                                 |

| ACALL                          | addr11                                                 | Absolute subroutine call                                                                                                                                                                                  | 2                          | 9 <sup>(2)(3)</sup>                                                                                             | 2                          | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                                                                                           |

| ACALL                          | addr11<br>at DRk                                       | Absolute subroutine call<br>Extended subroutine call (indirect)                                                                                                                                           | 2 3                        | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup>                                                                     | 2<br>2                     | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                                                                    |

| ACALL                          | addr11<br>at DRk<br>addr24                             | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call                                                                                                     | 2<br>3<br>5                | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup>                                             | 2<br>2<br>4                | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>9 <sup>(2)(3</sup>                                              |

| ACALL                          | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call<br>Extended subroutine call (indirect)<br>Extended subroutine call<br>Long subroutine call (indirect)                                                                            | 2<br>3<br>5<br>3           | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>10 <sup>(2)(3)</sup>                     | 2<br>2<br>4<br>2           | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>9 <sup>(2)(3</sup>                                              |

| ACALL<br>ECALL<br>LCALL<br>RET | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call         Long subroutine call (indirect)         Long subroutine call                                | 2<br>3<br>5<br>3<br>3      | $\begin{array}{c} 9^{(2)(3)} \\ 14^{(2)(3)} \\ 14^{(2)(3)} \\ 10^{(2)(3)} \\ 9^{(2)(3)} \end{array}$            | 2<br>2<br>4<br>2<br>3      | $9^{(2)(3)}$ $13^{(2)(3)}$ $13^{(2)(3)}$ $9^{(2)(3)}$ $9^{(2)(3)}$                                                                  |

| ACALL<br>ECALL<br>LCALL        | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call         Long subroutine call (indirect)         Long subroutine call         Return from subroutine | 2<br>3<br>5<br>3<br>3<br>1 | $\begin{array}{c} 9^{(2)(3)} \\ 14^{(2)(3)} \\ 14^{(2)(3)} \\ 10^{(2)(3)} \\ 9^{(2)(3)} \\ 7^{(2)} \end{array}$ | 2<br>2<br>4<br>2<br>3<br>1 | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3)</sup><br>9 <sup>(2)(3)</sup><br>9 <sup>(2)(3)</sup><br>7 <sup>(2)</sup> |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. In internal execution only, add 1 to the number of states if the destination/return address is internal and odd.

- 3. Add 2 to the number of states if the destination address is external.

- 4. Add 5 to the number of states if INTR = 1.

# Programming and Verifying Non-volatile Memory

## Internal Features

The internal non-volatile memory of the TSC80251G2D derivatives contains five different areas:

- Code Memory

- Configuration Bytes

- Lock Bits

- Encryption Array

- Signature Bytes

# **EPROM/OTPROM Devices** All the internal non-volatile memory but the Signature Bytes of the TSC87251G2D products are made of EPROM cells. The Signature Bytes of the TSC87251G2D products are made of Mask ROM.

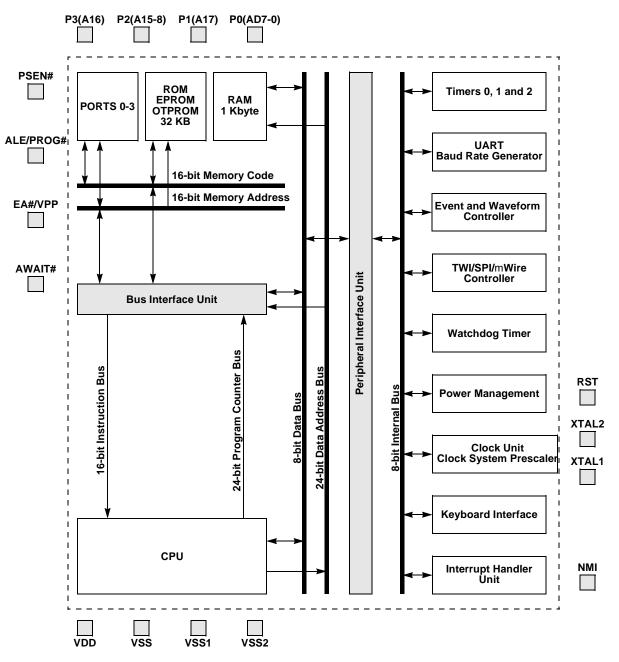

The TSC87251G2D products are programmed and verified in the same manner as Atmel's TSC87251G1A, using a SINGLE-PULSE algorithm, which programs at  $V_{PP}$  = 12.75V using only one 100µs pulse per byte. This results in a programming time of less than 10 seconds for the 32 kilobytes on-chip code memory.

The EPROM of the TSC87251G2D products in Window package is erasable by Ultra-Violet radiation<sup>(1)</sup> (UV). UV erasure set all the EPROM memory cells to one and allows reprogramming. The quartz window must be covered with an opaque label<sup>(2)</sup> when the device is in operation. This is not so much to protect the EPROM array from inadvertent erasure, as to protect the RAM and other on-chip logic. Allowing light to impinge on the silicon die during device operation may cause a logical malfunction.

The TSC87251G2D products in plastic packages are One Time Programmable (OTP). An EPROM cell cannot be reset by UV once programmed to zero.

- Notes: 1. The recommended erasure procedure is exposure to ultra-violet light (at 2537 Å) to an integrated dose of at least 20 W-sec/cm<sup>2</sup>. Exposing the EPROM to an ultra-violet lamp of 12000 μW/cm<sup>2</sup> rating for 30 minutes should be sufficient.

- 2. Erasure of the EPROM begins to occur when the chip is exposed to light wavelength shorter than 4000 Å. Since sunlight and fluorescent light have wavelength in this range, exposure to these light sources over an extended time (1 week in sunlight or 3 years in room-level fluorescent lighting) could cause inadvertent erasure.

- Mask ROM DevicesAll the internal non-volatile memory of TSC83251G2D products is made of Mask ROM<br/>cells. They can only be verified by the user, using the same algorithm as the<br/>EPROM/OTPROM devices.

**ROMIess Devices**The TSC80251G2D products do not include on-chip Configuration Bytes, Code Memory<br/>and Encryption Array. They only include Signature Bytes made of Mask ROM cells<br/>which can be read using the same algorithm as the EPROM/OTPROM devices.

- **Security Features** In some microcontroller applications, it is desirable that the user's program code be secured from unauthorized access. The TSC83251G2D and TSC87251G2D offer two kinds of protection for program code stored in the on-chip array:

- Program code in the on-chip Code Memory is encrypted when read out for verification if the Encryption Array isprogrammed.

- A three-level lock bit system restricts external access to the on-chip code memory.

#### Lock Bit System

The TSC87251G2D products implement 3 levels of security for User's program as described in Table 33. The TSC83251G2D products implement only the first level of security.

Level 0 is the level of an erased part and does not enable any security features.

Level 1 locks the programming of the User's internal Code Memory, the Configuration Bytes and the Encryption Array.

Level 2 locks the verifying of the User's internal Code Memory. It is always possible to verify the Configuration Bytes and the Lock Bits. It is not possible to verify the Encryption Array.

Level 3 locks the external execution.

| Level | Lock bits<br>LB[2:0] | Internal<br>Execution | External<br>Execution | Verification          | Programming | External<br>PROM read<br>(MOVC) |

|-------|----------------------|-----------------------|-----------------------|-----------------------|-------------|---------------------------------|

| 0     | 000                  | Enable                | Enable                | Enable <sup>(1)</sup> | Enable      | Enable <sup>(2)</sup>           |

| 1     | 001                  | Enable                | Enable                | Enable <sup>(1)</sup> | Disable     | Disable                         |

| 2     | 01x <sup>(3)</sup>   | Enable                | Enable                | Disable               | Disable     | Disable                         |

| 3     | 1xx <sup>(3)</sup>   | Enable                | Disable               | Disable               | Disable     | Disable                         |

Table 33. Lock Bits Programming

Notes: 1. Returns encrypted data if Encryption Array is programmed.

2. Returns non encrypted data.

3. x means don't care. Level 2 always enables level 1, and level 3 always enables levels 1 and 2.

The security level may be verified according to Table 34.

#### Table 34. Lock Bits Verifying

| Level | Lock bits Data <sup>(1)</sup> |

|-------|-------------------------------|

| 0     | xxxxx000                      |

| 1     | xxxxx001                      |

| 2     | xxxxx01x                      |

| 3     | xxxxx1xx                      |

Note: 1. x means don't care.

#### **Encryption Array**

The TSC83251G2D and TSC87251G2D products include a 128-byte Encryption Array located in non-volatile memory outside the memory address space. During verification of the on-chip code memory, the seven low-order address bits also address the Encryption Array. As the byte of the code memory is read, it is exclusive-NOR'ed (XNOR) with the key byte from the Encryption Array. If the Encryption Array is not programmed (still all 1s), the user program code is placed on the data bus in its original, unencrypted form. If the Encryption Array is programmed with key bytes, the user program code is encrypted and cannot be used without knowledge of the key byte sequence.

• PSEN# and the other control signals have to be released to complete a sequence of programming operations or a sequence of programming and verifying operations.

Table 36.

Programming Modes

| ROM Area <sup>(1)</sup> | RST | EA#/VPP         | PSEN<br># | ALE/PROG# <sup>(2)</sup> | P0  | P2   | P1(MSB) P3(LSB)                                 |

|-------------------------|-----|-----------------|-----------|--------------------------|-----|------|-------------------------------------------------|

| On-chip Code<br>Memory  | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 68h | Data | 16-bit Address<br>0000h-7FFFh (32<br>kilobytes) |

| Configuration<br>Bytes  | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 69h | Data | CONFIG0: FFF8h<br>CONFIG1: FFF9h                |

| Lock Bits               | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 6Bh | х    | LB0: 0001h<br>LB1: 0002h<br>LB2: 0003h          |

| Encryption Array        | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 6Ch | Data | 0000h-007Fh                                     |

Notes: 1. Signature Bytes are not user-programmable.

2. The ALE/PROG# pulse waveform is shown in Figure 23 page 59.

# **Verify Algorithm**

Figure 7 shows the hardware setup needed to verify the TSC87251G2D EPROM/OTPROM or TSC83251G2D ROM areas:

- The chip has to be put under reset and maintained in this state until the completion of the verifying sequence.

- PSEN# and the other control signals (ALE and Port 0) have to be set to a high level.

- Then PSEN# has to be to forced to a low level after two clock cycles or more and it

has to be maintained in this state until the completion of the verifying sequence (see

below).

- The voltage on the EA# pin must be set to V<sub>DD</sub> and ALE must be set to a high level.

- The Verifying Mode is selected according to the code applied on Port 0. It has to be applied until the completion of this verifying operation.

- The verifying address is applied on Ports 1 and 3 which are respectively the MSB and the LSB of the address.

|                                  |                                               | 12  | MHz | 16  | MHz | 24 1 | MHz |                     |

|----------------------------------|-----------------------------------------------|-----|-----|-----|-----|------|-----|---------------------|

| Symbol                           | Parameter                                     | Min | Max | Min | Max | Min  | Max | Unit                |

| T <sub>OSC</sub>                 | 1/F <sub>osc</sub>                            | 83  |     | 62  |     | 41   |     | ns                  |

| T <sub>LHLL</sub>                | ALE Pulse Width                               | 78  |     | 58  |     | 38   |     | ns <sup>(2)</sup>   |

| T <sub>AVLL</sub>                | Address Valid to ALE Low                      | 78  |     | 58  |     | 37   |     | ns <sup>(2)</sup>   |

| $T_{LLAX}$                       | Address hold after ALE Low                    | 19  |     | 11  |     | 3    |     | ns                  |

| $T_{RLRH}^{(1)}$                 | RD#/PSEN# Pulse Width                         | 162 |     | 121 |     | 78   |     | ns <sup>(3)</sup>   |

| T <sub>WLWH</sub>                | WR# Pulse Width                               | 165 |     | 124 |     | 81   |     | ns <sup>(3)</sup>   |

| $T_{LLRL}^{(1)}$                 | ALE Low to RD#/PSEN# Low                      | 22  |     | 14  |     | 6    |     | ns                  |

| T <sub>LHAX</sub>                | ALE High to Address Hold                      | 99  |     | 70  |     | 40   |     | ns <sup>(2)</sup>   |

| T <sub>RLDV</sub> <sup>(1)</sup> | RD#/PSEN# Low to Valid Data                   |     | 146 |     | 104 |      | 61  | ns <sup>(3)</sup>   |

| $T_{RHDX}^{(1)}$                 | Data Hold After RD#/PSEN# High                | 0   |     | 0   |     | 0    |     | ns                  |

| T <sub>RHAX</sub> <sup>(1)</sup> | Address Hold After RD#/PSEN#<br>High          | 0   |     | 0   |     | 0    |     | ns                  |

| T <sub>RLAZ</sub> <sup>(1)</sup> | RD#/PSEN# Low to Address Float                |     | 0   |     | 0   |      | 0   | ns                  |

| T <sub>RHDZ1</sub>               | Instruction Float After RD#/PSEN#<br>High     |     | 45  |     | 40  |      | 30  | ns                  |

| T <sub>RHDZ2</sub>               | Data Float After RD#/PSEN# High               |     | 215 |     | 165 |      | 115 | ns                  |

| T <sub>RHLH1</sub>               | RD#/PSEN# high to ALE High<br>(Instruction)   | 49  |     | 43  |     | 31   |     | ns                  |

| T <sub>RHLH2</sub>               | RD#/PSEN# high to ALE High<br>(Data)          | 215 |     | 169 |     | 115  |     | ns                  |

| T <sub>WHLH</sub>                | WR# High to ALE High                          | 215 |     | 169 |     | 115  |     | ns                  |

| T <sub>AVDV1</sub>               | Address (P0) Valid to Valid Data In           |     | 250 |     | 175 |      | 105 | ns <sup>(2)(3</sup> |

| T <sub>AVDV2</sub>               | Address (P2) Valid to Valid Data In           |     | 306 |     | 223 |      | 140 | ns <sup>(2)(3</sup> |

| T <sub>AVDV3</sub>               | Address (P0) Valid to Valid<br>Instruction In |     | 150 |     | 109 |      | 68  | ns <sup>(3)</sup>   |

| T <sub>AXDX</sub>                | Data Hold after Address Hold                  | 0   |     | 0   |     | 0    |     | ns                  |