Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | C251                                                                        |

| Core Size                  | 8/16-Bit                                                                    |

| Speed                      | 16MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, Microwire, SPI, UART/USART                       |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 32                                                                          |

| Program Memory Size        | -                                                                           |

| Program Memory Type        | ROMIess                                                                     |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-LCC (J-Lead)                                                             |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/tsc80251g2d-16cbr |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

compatibility with the C51 Architecture). When PC increments beyond the end of seqment FE:, it continues at the reset address FF:0000h (linearity). When PC increments beyond the end of segment 01:, it loops to the beginning of segment 00: (this prevents from its going into the reserved area).

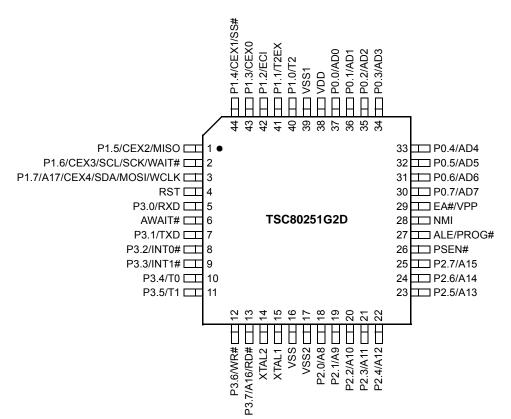

Data Memory The TSC80251G2D derivatives implement 1 Kbyte of on-chip data RAM. Figure 5 shows the split of the internal and external data memory spaces. This memory is mapped in the data space just over the 32 bytes of registers area (see TSC80251 Programmers' Guide). Hence, the part of the on-chip RAM located from 20h to FFh is bit addressable. This on-chip RAM is not accessible through the program/code memory space.

> For faster computation with the on-chip ROM/EPROM code of the TSC83251G2D/TSC87251G2D, its upper 16 KB are also mapped in the upper part of the region 00: if the On-Chip Code Memory Map configuration bit is cleared (EMAP# bit in UCONFIG1 byte, see Figure ). However, if EA# is tied to a low level, the TSC80251G2D derivative is running as a ROMless product and the code is actually fetched in the corresponding external memory (i.e. the upper 16 KB of the lower 32 KB of the segment FF:). If EMAP# bit is set, the on-chip ROM is not accessible through the region 00:.

> All the accesses to the portion of the data space with no on-chip memory mapped onto are redirected to the external memory.

Figure 5. Data Memory Mapping

## Instruction Set Summary

This section contains tables that summarize the instruction set. For each instruction there is a short description, its length in bytes, and its execution time in states (one state time is equal to two system clock cycles). There are two concurrent processes limiting the effective instruction throughput:

- Instruction Fetch

- Instruction Execution

Table 20 to Table 32 assume code executing from on-chip memory, then the CPU is fetching 16-bit at a time and this is never limiting the execution speed.

If the code is fetched from external memory, a pre-fetch queue will store instructions ahead of execution to optimize the memory bandwidth usage when slower instructions are executed. However, the effective speed may be limited depending on the average size of instructions (for the considered section of the program flow). The maximum average instruction throughput is provided by Table 14 depending on the external memory configuration (from Page Mode to Non-Page Mode and the maximum number of wait states). If the average size of instructions is not an integer, the maximum effective throughput is found by pondering the number of states for the neighbor integer values.

| Average size               |                       | Non-page Mode (states) |                 |               |               |               |  |

|----------------------------|-----------------------|------------------------|-----------------|---------------|---------------|---------------|--|

| of Instructions<br>(bytes) | Page Mode<br>(states) | 0 Wait<br>State        | 1 Wait<br>State | 2 Wait States | 3 Wait States | 4 Wait States |  |

| 1                          | 1                     | 2                      | 3               | 4             | 5             | 6             |  |

| 2                          | 2                     | 4                      | 6               | 8             | 10            | 12            |  |

| 3                          | 3                     | 6                      | 9               | 12            | 15            | 18            |  |

| 4                          | 4                     | 8                      | 12              | 16            | 20            | 24            |  |

| 5                          | 5                     | 10                     | 15              | 20            | 25            | 30            |  |

Table 14.

Minimum Number of States per Instruction for given Average Sizes

If the average execution time of the considered instructions is larger than the number of states given by Table 14, this larger value will prevail as the limiting factor. Otherwise, the value from Table 14 must be taken. This is providing a fair estimation of the execution speed but only the actual code execution can provide the final value.

### Table 15 to Table 19 provide notation for Instruction Operands.

### Notation for Instruction Operands

.

### Table 15. Notation for Direct Addressing

| Direct<br>Address | Description                                                                                                                                                            | C251 | C51 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| dir8              | A direct 8-bit address. This can be a memory address (00h-7Fh) or a SFR address (80h-FFh). It is a byte (default), word or double word depending on the other operand. | 3    | з   |

| dir16             | A 16-bit memory address (00:0000h-00:FFFFh) used in direct addressing.                                                                                                 | 3    | _   |

# Size and Execution Time for Instruction Families

### Table 20. Summary of Add and Subtract Instructions

| AddADD <dest>, <src>dest opnd <math>\leftarrow</math> dest opnd + src opnd</src></dest>                       |

|---------------------------------------------------------------------------------------------------------------|

| SubtractSUB <dest>, <src>dest opnd <math display="inline">\leftarrow</math> dest opnd - src opnd</src></dest> |

| Add with CarryADDC <dest>, <src>(A) <math>\leftarrow</math> (A) + src opnd + (CY)</src></dest>                |

| Subtract with BorrowSUBB <dest>, <src>(A) <math>\leftarrow</math> (A) - src opnd - (CY)</src></dest>          |

|               | -dost>                                       |                                                               | Binary | Mode             | Source                                                                                                                                                                                                                                                                                                                                                                                                            | e Mode           |

|---------------|----------------------------------------------|---------------------------------------------------------------|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Mnemonic      | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                                      | Bytes  | States           | Bytes                                                                                                                                                                                                                                                                                                                                                                                                             | States           |

|               | A, Rn                                        | Register to ACC                                               | 1      | 1                | 2                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                |

|               | A, dir8                                      | Direct address to ACC                                         | 2      | 1 <sup>(2)</sup> | 2                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 <sup>(2)</sup> |

| ADD           | A, at Ri                                     | Indirect address to ACC                                       | 1      | 2                | 2                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                |

|               | A, #data                                     | Immediate data to ACC                                         | 2      | 1                | 2                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                |

|               | Rmd, Rms                                     | Byte register to/from byte register                           | 3      | 2                | 2                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                |

|               | WRjd, WRjs                                   | Word register to/from word register                           | 3      | 3                | 2                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                |

|               | DRkd, DRks                                   | Dword register to/from dword register                         | 3      | 5                | 2                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                |

|               | Rm, #data                                    | Immediate 8-bit data to/from byte register                    | 4      | 3                | 3                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                |

|               | WRj, #data16                                 | Immediate 16-bit data to/from word register                   | 5      | 4                | 4                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                |

|               | DRk,<br>#0data16                             | 16-bit unsigned immediate data to/from dword register         | 5      | 6                | 4                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                |

| ADD/SUB       | Rm, dir8                                     | Direct address (on-chip RAM or SFR)<br>to/from byte register  | 4      | 3 <sup>(2)</sup> | 3                                                                                                                                                                                                                                                                                                                                                                                                                 | 2 <sup>(2)</sup> |

|               | WRj, dir8                                    | Direct address (on-chip RAM or SFR) to/from word register     | 4      | 4                | 3                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                |

|               | Rm, dir16                                    | Direct address (64K) to/from byte<br>register                 | 5      | 3 <sup>(3)</sup> | 4                                                                                                                                                                                                                                                                                                                                                                                                                 | 2 <sup>(3)</sup> |

|               | WRj, dir16                                   | Direct address (64K) to/from word register                    | 5      | 4 <sup>(4)</sup> | 4                                                                                                                                                                                                                                                                                                                                                                                                                 | 3 <sup>(4)</sup> |

|               | Rm, at WRj                                   | Indirect address (64K) to/from byte register                  | 4      | 3 <sup>(3)</sup> | 3                                                                                                                                                                                                                                                                                                                                                                                                                 | 2 <sup>(3)</sup> |

|               | Rm, at DRk                                   | Indirect address (16M) to/from byte register                  | 4      | 4 <sup>(3)</sup> | 3                                                                                                                                                                                                                                                                                                                                                                                                                 | 3 <sup>(3)</sup> |

|               | A, Rn                                        | Register to/from ACC with carry                               | 1      | 1                | 2                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                |

|               | A, dir8                                      | Direct address (on-chip RAM or SFR)<br>to/from ACC with carry | 2      | 1 <sup>(2)</sup> | 2                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 <sup>(2)</sup> |

| ADDC/SU<br>BB | A, at Ri                                     | Indirect address to/from ACC with carry                       | 1      | 2                | 2         2         2         2         2         2         2         2         3         4         4         3         3         4         4         3         3         4         3         3         4         3         3         3         3         3         3         3         3         3         2         2         2         2         2         2         2         2         2         2         2 | 3                |

|               | A, #data                                     | Immediate data to/from ACC with carry                         | 2      | 1                | 2                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

3. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

|          | <dest>,</dest>            |                                                         | Binary | Mode             | Source Mode |                  |

|----------|---------------------------|---------------------------------------------------------|--------|------------------|-------------|------------------|

| Mnemonic | <src><sup>(2)</sup></src> | Comments                                                | Bytes  | States           | Bytes       | States           |

|          | Rmd, Rms                  | Register with register                                  | 3      | 2                | 2           | 1                |

|          | WRjd,<br>WRjs             | Word register with word register                        | 3      | 3                | 2           | 2                |

|          | DRkd,<br>DRks             | Dword register with dword register                      | 3      | 5                | 2           | 4                |

|          | Rm, #data                 | Register with immediate data                            | 4      | 3                | 3           | 2                |

|          | WRj,<br>#data16           | Word register with immediate 16-bit data                | 5      | 4                | 4           | 3                |

|          | DRk,<br>#0data16          | Dword register with zero-extended 16-bit immediate data | 5      | 6                | 4           | 5                |

| CMP      | DRk,<br>#1data16          | Dword register with one-extended 16-bit immediate data  | 5      | 6                | 4           | 5                |

|          | Rm, dir8                  | Direct address (on-chip RAM or SFR) with byte register  | 4      | 3 <sup>(1)</sup> | 3           | 2 <sup>(1)</sup> |

|          | WRj, dir8                 | Direct address (on-chip RAM or SFR) with word register  | 4      | 4                | 3           | 3                |

|          | Rm, dir16                 | Direct address (64K) with byte register                 | 5      | 3 <sup>(2)</sup> | 4           | 2 <sup>(2)</sup> |

|          | WRj, dir16                | Direct address (64K) with word register                 | 5      | 4 <sup>(3)</sup> | 4           | 3 <sup>(3)</sup> |

|          | Rm, at WRj                | Indirect address (64K) with byte register               | 4      | 3 <sup>(2)</sup> | 3           | 2 <sup>(2)</sup> |

|          | Rm, at DRk                | Indirect address (16M) with byte register               | 4      | 4 <sup>(2)</sup> | 3           | 3(2)             |

### Table 22. Summary of Compare Instructions

Notes: 1. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 2. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

- 3. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

- Notes: 1. Logical instructions that affect a bit are in Table 27.

- 2. A shaded cell denotes an instruction in the C51 Architecture.

- 3. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 4. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

- 5. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

- 6. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

| Table 23. | Summar | of Logical | Instructions | (2/2) |

|-----------|--------|------------|--------------|-------|

|           |        |            |              |       |

| (CY) ← <des<br>Shift Right Arithme<br/><dest><sub>n-1</sub> ←<br/>(CY) ← <des<br>Shift Right Logical</des<br></dest></des<br> | <dest><sub>n</sub>, n =<br/>tt&gt;<sub>msb</sub><br/>eticSRA <des<br><dest><sub>n</sub>, n = n<br/>tt&gt;<sub>0</sub><br/>SRL <dest>&lt;<br/><dest><sub>n</sub>, n = n<br/>tt&gt;<sub>0</sub></dest></dest></dest></des<br></dest> | 0msb-1<br>t> <dest><sub>msb</sub> ← <dest><sub>msb</sub><br/>msb1<br/>:dest&gt;<sub>msb</sub> ← 0</dest></dest> |       |        |       |        |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------|--------|-------|--------|

|                                                                                                                               | Binary Mode Source Mod                                                                                                                                                                                                             |                                                                                                                 |       |        |       | e Mode |

| Mnemonic                                                                                                                      | <dest>,<br/><src><sup>(1)</sup></src></dest>                                                                                                                                                                                       | Comments                                                                                                        | Bytes | States | Bytes | States |

|                                                                                                                               | Rm                                                                                                                                                                                                                                 | Shift byte register left through the MSB                                                                        | 3     | 2      | 2     | 1      |

| SLL                                                                                                                           | WRj                                                                                                                                                                                                                                | Shift word register left through the MSB                                                                        | 3     | 2      | 2     | 1      |

| SRA                                                                                                                           | Rm                                                                                                                                                                                                                                 | Shift byte register right                                                                                       | 3     | 2      | 2     | 1      |

| SKA                                                                                                                           | WRj                                                                                                                                                                                                                                | Shift word register right                                                                                       | 3     | 2      | 2     | 1      |

| SRL                                                                                                                           | Rm                                                                                                                                                                                                                                 | Shift byte register left                                                                                        | 3     | 2      | 2     | 1      |

| SKL                                                                                                                           | WRj                                                                                                                                                                                                                                | Shift word register left                                                                                        | 3     | 2      | 2     | 1      |

| SWAP                                                                                                                          | А                                                                                                                                                                                                                                  | Swap nibbles within ACC                                                                                         | 1     | 2      | 1     | 2      |

Note: 1. A shaded cell denotes an instruction in the C51 Architecture.

### Table 27. Summary of Bit Instructions

Set BitSETB <dest>dest opnd  $\leftarrow$  1

$\textbf{Complement BitCPL <dest>dest opnd} \leftarrow \varnothing \textbf{ bit}$

AND Carry with BitANL CY,  $\langle src \rangle(CY) \leftarrow (CY) \land src opnd$

AND Carry with Complement of BitANL CY, /<src>(CY)  $\leftarrow$  (CY)  $\land \varnothing$  src opnd

OR Carry with BitORL CY, <src>(CY)  $\leftarrow$  (CY)  $\lor$  src opnd

OR Carry with Complement of BitORL CY, /<src>(CY)  $\leftarrow$  (CY)  $\vee \varnothing$  src opnd

Move Bit to CarryMOV CY,  $\langle crc \rangle$  (CY)  $\leftarrow$  src opnd

Move Bit from CarryMOV <dest>, CYdest opnd  $\leftarrow$  (CY)

|          | <dest>,</dest>            |                                      | Binary | Mode             | Source | e Mode           |

|----------|---------------------------|--------------------------------------|--------|------------------|--------|------------------|

| Mnemonic | <src><sup>(1)</sup></src> | Comments                             | Bytes  | States           | Bytes  | States           |

|          | CY                        | Clear carry                          | 1      | 1                | 1      | 1                |

| CLR      | bit51                     | Clear direct bit                     | 2      | 2 <sup>(3)</sup> | 2      | 2 <sup>(3)</sup> |

|          | bit                       | Clear direct bit                     | 4      | 4 <sup>(3)</sup> | 3      | 3 <sup>(3)</sup> |

|          | CY                        | Set carry                            | 1      | 1                | 1      | 1                |

| SETB     | bit51                     | Set direct bit                       | 2      | 2 <sup>(3)</sup> | 2      | 2 <sup>(3)</sup> |

|          | bit                       | Set direct bit                       | 4      | 4 <sup>(3)</sup> | 3      | 3 <sup>(3)</sup> |

|          | CY                        | Complement carry                     | 1      | 1                | 1      | 1                |

| CPL      | bit51                     | Complement direct bit                | 2      | 2 <sup>(3)</sup> | 2      | 2 <sup>(3)</sup> |

|          | bit                       | Complement direct bit                | 4      | 4 <sup>(3)</sup> | 3      | 3 <sup>(3)</sup> |

|          | CY, bit51                 | And direct bit to carry              | 2      | 1 <sup>(2)</sup> | 2      | 1 <sup>(2)</sup> |

|          | CY, bit                   | And direct bit to carry              | 4      | 3 <sup>(2)</sup> | 3      | 2 <sup>(2)</sup> |

| ANL      | CY, /bit51                | And complemented direct bit to carry | 2      | 1 <sup>(2)</sup> | 2      | 1 <sup>(2)</sup> |

|          | CY, /bit                  | And complemented direct bit to carry | 4      | 3 <sup>(2)</sup> | 2      | 2 <sup>(2)</sup> |

|          | CY, bit51                 | Or direct bit to carry               | 2      | 1 <sup>(2)</sup> | 2      | 1 <sup>(2)</sup> |

|          | CY, bit                   | Or direct bit to carry               | 4      | 3 <sup>(2)</sup> | 3      | 2 <sup>(2)</sup> |

| ORL      | CY, /bit51                | Or complemented direct bit to carry  | 2      | 1 <sup>(2)</sup> | 2      | 1 <sup>(2)</sup> |

|          | CY, /bit                  | Or complemented direct bit to carry  | 4      | 3 <sup>(2)</sup> | 3      | 2 <sup>(2)</sup> |

|          | CY, bit51                 | Move direct bit to carry             | 2      | 1 <sup>(2)</sup> | 2      | 1 <sup>(2)</sup> |

| MOV      | CY, bit                   | Move direct bit to carry             | 4      | 3 <sup>(2)</sup> | 3      | 2 <sup>(2)</sup> |

| MOV      | bit51, CY                 | Move carry to direct bit             | 2      | 2 <sup>(3)</sup> | 2      | 2 <sup>(3)</sup> |

|          | bit, CY                   | Move carry to direct bit             | 4      | 4 <sup>(3)</sup> | 3      | 3 <sup>(3)</sup> |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

3. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

| Binary Mode Source Mode |                                              |                                                    |       |                  |       |                  |  |

|-------------------------|----------------------------------------------|----------------------------------------------------|-------|------------------|-------|------------------|--|

| Mnemonic                | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                           | Bytes | States           | Bytes | State            |  |

|                         | A, Rn                                        | ACC and register                                   | 1     | 3                | 2     | 4                |  |

| ХСН                     | A, dir8                                      | ACC and direct address (on-chip RAM or SFR)        | 2     | 3 <sup>(3)</sup> | 2     | 3 <sup>(3)</sup> |  |

|                         | A, at Ri                                     | ACC and indirect address                           | 1     | 4                | 2     | 5                |  |

| XCHD                    | A, at Ri                                     | ACC low nibble and indirect address (256 bytes)    | 1     | 4                | 2     | 5                |  |

|                         | dir8                                         | Push direct address onto stack                     | 2     | 2 <sup>(2)</sup> | 2     | 2(2              |  |

|                         | #data                                        | Push immediate data onto stack                     | 4     | 4                | 3     | 3                |  |

| PUSH                    | #data16                                      | Push 16-bit immediate data onto stack              | 5     | 5                | 4     | 5                |  |

| F 0311                  | Rm                                           | Push byte register onto stack                      | 3     | 4                | 2     | 3                |  |

|                         | WRj                                          | Push word register onto stack                      | 3     | 5                | 2     | 4                |  |

|                         | DRk                                          | Push double word register onto stack               | 3     | 9                | 2     | 8                |  |

|                         | dir8                                         | Pop direct address (on-chip RAM or SFR) from stack | 2     | 3 <sup>(2)</sup> | 2     | 3(2              |  |

| POP                     | Rm                                           | Pop byte register from stack                       | 3     | 3                | 2     | 2                |  |

|                         | WRj                                          | Pop word register from stack                       | 3     | 5                | 2     | 4                |  |

|                         | DRk                                          | Pop double word register from stack                | 3     | 9                | 2     | 8                |  |

### Table 28. Summary of Exchange, Push and Pop Instructions

Exchange bytesXCH A, <src>(A)  $\leftrightarrow$  src opnd

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

3. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

Add 3 if it addresses a Peripheral SFR.

- 5. If this instruction addresses an I/O Port (Px, x = 0-3), add 3 to the number of states. Add 5 if it addresses a Peripheral SFR.

- 6. In internal execution only, add 1 to the number of states of the 'jump taken' if the destination address is internal and odd.

### Table 31. Summary of Unconditional Jump Instructions

Absolute jumpAJMP <src>(PC)  $\leftarrow$  (PC) +2; (PC)<sub>10:0</sub>  $\leftarrow$  src opnd Extended jumpEJMP <src>(PC)  $\leftarrow$  (PC) + size (instr); (PC)<sub>23:0</sub>  $\leftarrow$  src opnd Long jumpLJMP <src>(PC)  $\leftarrow$  (PC) + size (instr); (PC)<sub>15:0</sub>  $\leftarrow$  src opnd Short jumpSJMP rel(PC)  $\leftarrow$  (PC) +2; (PC)  $\leftarrow$  (PC) +rel Jump indirectJMP at A +DPTR(PC)<sub>23:16</sub>  $\leftarrow$  FFh; (PC)<sub>15:0</sub>  $\leftarrow$  (A) + (DPTR) No operationNOP(PC)  $\leftarrow$  (PC) +1

|          | <dest>,</dest>            | sta                                |       | Mode                | Source Mode |                     |

|----------|---------------------------|------------------------------------|-------|---------------------|-------------|---------------------|

| Mnemonic | <src><sup>(1)</sup></src> | Comments                           | Bytes | States              | Bytes       | States              |

| AJMP     | addr11                    | Absolute jump                      | 2     | 3 <sup>(2)(3)</sup> | 2           | 3 <sup>(2)(3)</sup> |

| EJMP     | addr24                    | Extended jump                      | 5     | 6 <sup>(2)(4)</sup> | 4           | 5 <sup>(2)(4)</sup> |

| EJIVIP   | at DRk                    | Extended jump (indirect)           | 3     | 7 <sup>(2)(4)</sup> | 2           | 6 <sup>(2)(4)</sup> |

| LJMP     | at WRj                    | Long jump (indirect)               | 3     | 6 <sup>(2)(4)</sup> | 2           | 5 <sup>(2)(4)</sup> |

| LJIMP    | addr16                    | Long jump (direct address)         | 3     | 5 <sup>(2)(4)</sup> | 3           | 5 <sup>(2)(4)</sup> |

| SJMP     | rel                       | Short jump (relative address)      | 2     | 4 <sup>(2)(4)</sup> | 2           | 4 <sup>(2)(4)</sup> |

| JMP      | at A +DPTR                | Jump indirect relative to the DPTR | 1     | 5 <sup>(2)(4)</sup> | 1           | 5 <sup>(2)(4)</sup> |

| NOP      |                           | No operation (Jump never)          | 1     | 1                   | 1           | 1                   |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

- 2. In internal execution only, add 1 to the number of states if the destination address is internal and odd.

- 3. Add 2 to the number of states if the destination address is external.

- 4. Add 3 to the number of states if the destination address is external.

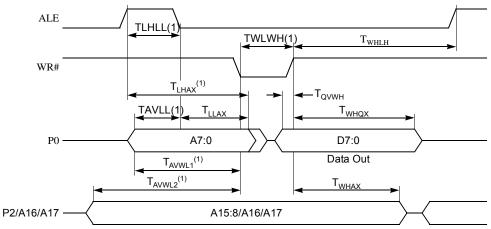

Figure 10. External Bus Cycle: Data Write (Non-Page Mode)

Waveforms in Page Mode

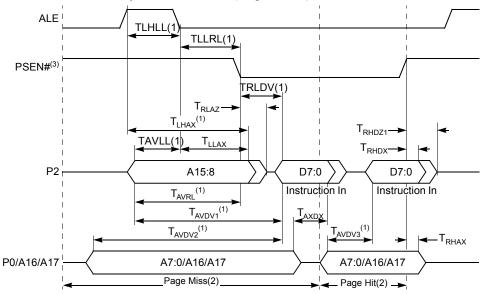

Figure 11. External Bus Cycle: Code Fetch (Page Mode)

- Note: 1. The value of this parameter depends on wait states. See Table 39 and Table 40.

- A page hit (i.e., a code fetch to the same 256-byte "page" as the previous code fetch) requires one state (2·T<sub>OSC</sub>);

a page miss requires two states ( $4 \cdot T_{OSC}$ ).

During a sequence of page hits, PSEN# remains low until the end of the last page-hit cycle.

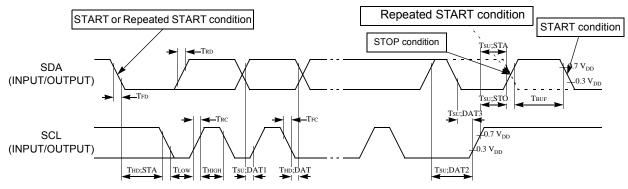

### AC Characteristics - SSLC: TWI Interface

### Timings

Table 47. TWI Interface AC Timing;  $V_{\text{DD}}$  = 2.7 to 5.5 V,  $T_{\text{A}}$  = -40 to 85°C

|           |                                                   | INPUT                   | OUTPUT                        |  |

|-----------|---------------------------------------------------|-------------------------|-------------------------------|--|

| Symbol    | Parameter                                         | Min Max                 | Min Max                       |  |

| THD; STA  | Start condition hold time                         | 14·Tclcl <sup>(4)</sup> | 4.0 μs <sup>(1)</sup>         |  |

| TLOW      | SCL low time                                      | 16·Tclcl <sup>(4)</sup> | 4.7 μs <sup>(1)</sup>         |  |

| Тнідн     | SCL high time                                     | 14·Tclcl <sup>(4)</sup> | 4.0 μs <sup>(1)</sup>         |  |

| Trc       | SCL rise time                                     | 1 μs                    | _(2)                          |  |

| TFC       | SCL fall time                                     | 0.3 μs                  | 0.3 μs <sup>(3)</sup>         |  |

| Tsu; DAT1 | Data set-up time                                  | 250 ns                  | 20.TCLCL <sup>(4)</sup> - TRD |  |

| Tsu; DAT2 | SDA set-up time (before repeated START condition) | 250 ns                  | 1 μs <sup>(1)</sup>           |  |

| Tsu; DAT3 | SDA set-up time (before STOP condition)           | 250 ns                  | 8.Tclcl <sup>(4)</sup>        |  |

| Thd; DAT  | Data hold time                                    | 0 ns                    | 8.TCLCL <sup>(4)</sup> - TFC  |  |

| Ts∪; STA  | Repeated START set-up time                        | 14·Tclcl <sup>(4)</sup> | 4.7 μs <sup>(1)</sup>         |  |

| Tsu; STO  | STOP condition set-up time                        | 14·Tclcl <sup>(4)</sup> | 4.0 μs <sup>(1)</sup>         |  |

| Твиғ      | Bus free time                                     | 14·Tclcl <sup>(4)</sup> | 4.7 μs <sup>(1)</sup>         |  |

| Trd       | SDA rise time                                     | 1 μs                    | _(2)                          |  |

| Tfd       | SDA fall time                                     | 0.3 μs                  | 0.3 μs <sup>(3)</sup>         |  |

Notes: 1. At 100 kbit/s. At other bit-rates this value is inversely proportional to the bit-rate of 100 kbit/s.

- 2. Determined by the external bus-line capacitance and the external bus-line pull-up resistor, this must be < 1  $\mu s.$

- Spikes on the SDA and SCL lines with a duration of less than 3. TCLCL will be filtered out. Maximum capacitance on bus-lines SDA and SCL = 400 pF.

- 4. TCLCL =  $T_{OSC}$  = one oscillator clock period.

### Waveforms

#### Figure 18. TWI Waveforms

## 54 AT/TSC8x251G2D

### Timings

### **Table 49.** SPI Interface AC Timing; $V_{DD}$ = 2.7 to 5.5 V, $T_A$ = -40 to 85°C

| Symbol                                | Parameter                              | Min | Max | Unit             |

|---------------------------------------|----------------------------------------|-----|-----|------------------|

|                                       | Slave Mode <sup>(</sup>                | 1)  |     | 1                |

| Тснсн                                 | Clock Period                           | 8   |     | T <sub>OSC</sub> |

| T <sub>CHCX</sub>                     | Clock High Time                        | 3.2 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 3.2 |     | T <sub>osc</sub> |

| T <sub>SLCH</sub> , T <sub>SLCL</sub> | SS# Low to Clock edge                  | 200 |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 100 | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>CLSH</sub> , T <sub>CHSH</sub> | SS# High after Clock Edge              | 0   |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>SLOV</sub>                     | SS# Low to Output Data Valid           |     | 130 | ns               |

| Т <sub>знох</sub>                     | Output Data Hold after SS# High        |     | 130 | ns               |

| T <sub>SHSL</sub>                     | SS# High to SS# Low                    | (2) |     |                  |

| T <sub>ILIH</sub>                     | Input Rise Time                        |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Fall Time                        |     | 2   | μs               |

| Т <sub>огон</sub>                     | Output Rise time                       |     | 100 | ns               |

| Т <sub>оног</sub>                     | Output Fall Time                       |     | 100 | ns               |

|                                       | Master Mode                            | (3) |     |                  |

| Тснсн                                 | Clock Period                           | 4   |     | T <sub>osc</sub> |

| Т <sub>снсх</sub>                     | Clock High Time                        | 1.6 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 1.6 |     | T <sub>osc</sub> |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 50  |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 50  |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 65  | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>ILIH</sub>                     | Input Data Rise Time                   |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Data Fall Time                   |     | 2   | μs               |

| T <sub>OLOH</sub>                     | Output Data Rise time                  |     | 50  | ns               |

| T <sub>OHOL</sub>                     | Output Data Fall Time                  |     | 50  | ns               |

Notes: 1. Capacitive load on all pins = 200 pF in slave mode.

2. The value of this parameter depends on software.

3. Capacitive load on all pins = 100 pF in master mode.

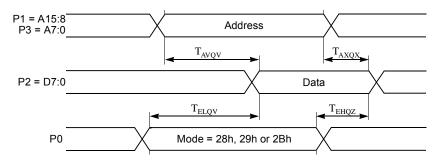

### Figure 24. EPROM Verifying Waveforms

### AC Characteristics - External Clock Drive and Logic Level References

**Definition of Symbols**

Table 53. External Clock Timing Symbol Definitions

| Signals |  |  |  |

|---------|--|--|--|

| C Clock |  |  |  |

|         |  |  |  |

|         |  |  |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| H High     |                 |  |  |  |

| L          | Low             |  |  |  |

| Х          | No Longer Valid |  |  |  |

#### Timings

### **Table 54.** External Clock AC Timings; $V_{DD}$ = 4.5 to 5.5 V, $T_A$ = -40 to +85°C

| Symbol            | Parameter            | Min | Max | Unit |

|-------------------|----------------------|-----|-----|------|

| F <sub>osc</sub>  | Oscillator Frequency |     | 24  | MHz  |

| T <sub>CHCX</sub> | High Time            | 10  |     | ns   |

| T <sub>CLCX</sub> | Low Time             | 10  |     | ns   |

| T <sub>CLCH</sub> | Rise Time            | 3   |     | ns   |

| T <sub>CHCL</sub> | Fall Time            | 3   |     | ns   |

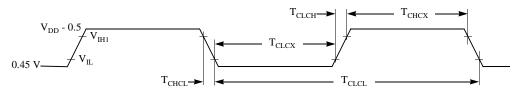

### Waveforms

Figure 25. External Clock Waveform

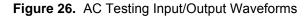

- Notes: 1. During AC testing, all inputs are driven at  $V_{DD}$  -0.5 V for a logic 1 and 0.45 V for a logic 0.

- 2. Timing measurements are made on all outputs at  $V_{\rm IH}$  min for a logic 1 and  $V_{\rm IL}$  max for a logic 0.

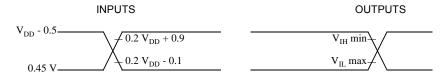

Note: For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loading  $V_{OH}/V_{OL}$  level occurs with  $I_{OL}/I_{OH} = \pm 20$  mA.

Figure 27. Float Waveforms

## Absolute Maximum Rating and Operating Conditions

## Absolute Maximum Ratings

| Storage Temperature65 to +150°C              | *NOTICE: Stressing the device beyond the "Absolute Maxi-<br>mum Ratings" may cause permanent damage. |

|----------------------------------------------|------------------------------------------------------------------------------------------------------|

| Voltage on any other Pin to VSS0.5 to +6.5 V | These are stress ratings only. Operation beyond                                                      |

| I <sub>OL</sub> per I/O Pin 15 mA            | the "operating conditions" is not recommended<br>and extended exposure beyond the "Operating         |

| Power Dissipation 1.5 W                      | Conditions" may affect device reliability.                                                           |

| Ambient Temperature Under Bias               |                                                                                                      |

| Commercial0 to +70°C                         |                                                                                                      |

| Industrial40 to +85°C                        |                                                                                                      |

| Automotive40 to +85°C                        |                                                                                                      |

| V <sub>DD</sub>                              |                                                                                                      |

| High Speed versions                          |                                                                                                      |

| Low Voltage versions                         |                                                                                                      |

Notes: 1. Under steady-state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum IOL per port pin: 10 mA

Maximum IOL per 8-bit port:Port 0 26 mA

Ports 1-3 15 mA

Maximum Total IOL for all: Output Pins 71 mA

If IOL exceeds the test conditions, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 2. Capacitive loading on Ports 0 and 2 may cause spurious noise pulses above 0.4 V on the low-level outputs of ALE and Ports 1, 2, and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins change from high to low. In applications where capacitive loading exceeds 100 pF, the noise pulses on these signals may exceed 0.8 V. It may be desirable to qualify ALE or other signals with a Schmitt Trigger or CMOS-level input logic.

- Capacitive loading on Ports 0 and 2 causes the V<sub>OH</sub> on ALE and PSEN# to drop below the specification when the address lines are stabilizing.

- 4. Typical values are obtained using  $V_{DD}$  = 5 V and  $T_A$  = 25°C. They are not tested and there is not guarantee on these values.

- The input threshold voltage of SCL and SDA meets the TWI specification, so an input voltage below 0.3 V<sub>DD</sub> will be recognized as a logic 0 while an input voltage above 0.7 V<sub>DD</sub> will be recognized as a logic 1.

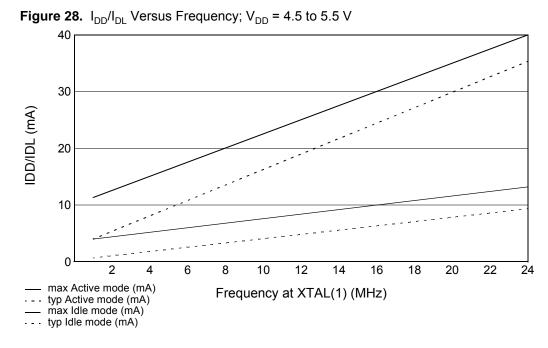

Note: 1. The clock prescaler is not used:  $F_{OSC} = F_{XTAL}$ .

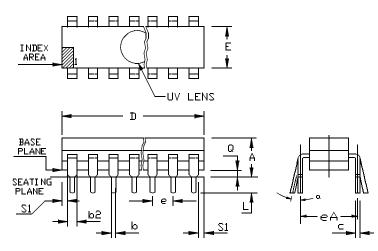

CDIL 40 with Window -Mechanical Outline

Figure 34. Ceramic Dual In Line

Table 58. CDIL Package Size

|    | ММ            |       | Inch        |       |

|----|---------------|-------|-------------|-------|

|    | Min           | Max   | Min         | Мах   |

| A  | -             | 5.71  | -           | .225  |

| b  | 0.36          | 0.58  | .014        | .023  |

| b2 | 1.14          | 1.65  | .045        | .065  |

| с  | 0.20          | 0.38  | .008        | .015  |

| D  | -             | 53.47 | -           | 2.105 |

| E  | 13.06         | 15.37 | .514        | .605  |

| e  | 2.54 B.S.C.   |       | .100 B.S.C. |       |

| eA | 15.24 B.S.C.  |       | .600 B.S.C. |       |

| L  | 3.18          | 5.08  | .125        | .200  |

| Q  | 0.38          | 1.40  | .015        | .055  |

| S1 | 0.13          | -     | .005        | -     |

| а  | 0 - 15 0 - 15 |       | 15          |       |

| Ν  | 40            |       |             |       |

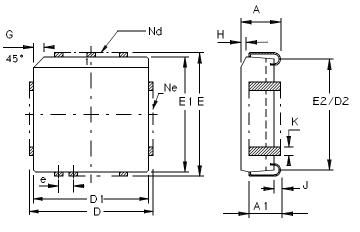

### PLCC 44 - Mechanical Outline

### Table 59. PLCC Package Size

|    | мм       |       | Inch              |      |

|----|----------|-------|-------------------|------|

|    | Min      | Max   | Min               | Max  |

| А  | 4.20     | 4.57  | .165              | .180 |

| A1 | 2.29     | 3.04  | .090              | .120 |

| D  | 17.40    | 17.65 | .685              | .695 |

| D1 | 16.44    | 16.66 | .647              | .656 |

| D2 | 14.99    | 16.00 | .590              | .630 |

| E  | 17.40    | 17.65 | .685              | .695 |

| E1 | 16.44    | 16.66 | .647              | .656 |

| E2 | 14.99    | 16.00 | .590              | .630 |

| е  | 1.27 BSC |       | 1.27 BSC .050 BSC |      |

| G  | 1.07     | 1.22  | .042              | .048 |

| Н  | 1.07     | 1.42  | .042              | .056 |

| J  | 0.51     | -     | .020              | -    |

| К  | 0.33     | 0.53  | .013              | .021 |

| Nd | 11       |       | 11                |      |

| Ne | 1        | 11 11 |                   | 1    |

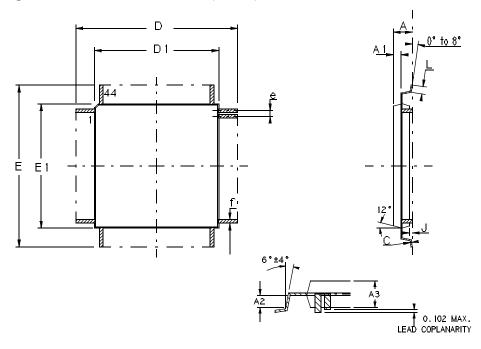

## VQFP 44 (10x10) -Mechanical Outline

Figure 37. Shrink Quad Flat Pack (Plastic)

| Table 61. | VQFP | Package Size |

|-----------|------|--------------|

|-----------|------|--------------|

|    | ММ                 |       | Inch     |      |

|----|--------------------|-------|----------|------|

|    | Min                | Мах   | Min      | Max  |

| A  | -                  | 1.60  | -        | .063 |

| A1 | 0.64               | REF   | .025 REF |      |

| A2 | 0.64 REF           |       | .025REF  |      |

| A3 | 1.35               | 1.45  | .053     | .057 |

| D  | 11.90              | 12.10 | .468     | .476 |

| D1 | 9.90               | 10.10 | .390     | .398 |

| E  | 11.90              | 12.10 | .468     | .476 |

| E1 | 9.90               | 10.10 | .390     | .398 |

| J  | 0.05               | -     | .002     | 6    |

| L  | 0.45               | 0.75  | .018     | .030 |

| е  | 0.80 BSC .0315 BSC |       | 5 BSC    |      |

| f  | 0.35 BSC           |       | .014 BSC |      |

### **Options** (Please

- ROM code encryption • consult Atmel sales)

- Tape & Reel or Dry Pack ٠

- Known good dice ٠

- Extended temperature range: -55°C to +125°C •

### **Product Markings**

**ROMIess versions**

ATMEL Part number Mask ROM versions

ATMEL Customer Part number Part Number YYWW . Lot Number

OTP versions

ATMEL Part number

YYWW . Lot Number

YYWW . Lot Number