Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | C251                                                                       |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 24MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, Microwire, SPI, UART/USART                      |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | -                                                                          |

| Program Memory Type        | ROMIess                                                                    |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/tsc80251g2d-24cb |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Signals

#### Table 2. Product Name Signal Description

| Table 2.             | Product Name Signal Description |                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |  |

|----------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| Signal<br>Name       | Туре                            | Description                                                                                                                                                                                                                                                                                                                                                                                                          | Alternate<br>Function |  |

| A17                  | 0                               | <b>18<sup>th</sup> Address Bit</b><br>Output to memory as 18th external address bit (A17) in extended bus<br>applications, depending on the values of bits RD0 and RD1 in UCONFIG0<br>byte (see Table 13, Page 20).                                                                                                                                                                                                  |                       |  |

| A16                  | 0                               | <b>17<sup>th</sup> Address Bit</b><br>Output to memory as 17th external address bit (A16) in extended bus<br>applications, depending on the values of bits RD0 and RD1 in UCONFIG0<br>byte (see Table 13, Page 20).                                                                                                                                                                                                  | P3.7                  |  |

| A15:8 <sup>(1)</sup> | 0                               | Address Lines<br>Upper address lines for the external bus.                                                                                                                                                                                                                                                                                                                                                           | P2.7:0                |  |

| AD7:0 <sup>(1)</sup> | I/O                             | Address/Data Lines<br>Multiplexed lower address lines and data for the external memory.                                                                                                                                                                                                                                                                                                                              | P0.7:0                |  |

| ALE                  | 0                               | Address Latch Enable<br>ALE signals the start of an external bus cycle and indicates that valid<br>address information are available on lines A16/A17 and A7:0. An external<br>latch can use ALE to demultiplex the address from address/data bus.                                                                                                                                                                   | -                     |  |

| AWAIT#               | I                               | <b>Real-time Asynchronous Wait States Input</b><br>When this pin is active (low level), the memory cycle is stretched until it<br>becomes high. When using the Product Name as a pin-for-pin replacement<br>for a 8xC51 product, AWAIT# can be unconnected without loss of<br>compatibility or power consumption increase (on-chip pull-up).<br>Not available on DIP package.                                        | _                     |  |

| CEX4:0               | I/O                             | PCA Input/Output pins<br>CEXx are input signals for the PCA capture mode and output signals for<br>the PCA compare and PWM modes.                                                                                                                                                                                                                                                                                    |                       |  |

| EA#                  | I                               | <b>External Access Enable</b><br>EA# directs program memory accesses to on-chip or off-chip code memory.<br>For EA# = 0, all program memory accesses are off-chip.<br>For EA# = 1, an access is on-chip ROM if the address is within the range of<br>the on-chip ROM; otherwise the access is off-chip. The value of EA# is<br>latched at reset.<br>For devices without ROM on-chip, EA# must be strapped to ground. | _                     |  |

| ECI                  | 0                               | PCA External Clock input<br>ECI is the external clock input to the 16-bit PCA timer.                                                                                                                                                                                                                                                                                                                                 | P1.2                  |  |

| MISO                 | I/O                             | SPI Master Input Slave Output line<br>When SPI is in master mode, MISO receives data from the slave<br>peripheral. When SPI is in slave mode, MISO outputs data to the master<br>controller.                                                                                                                                                                                                                         | P1.5                  |  |

| MOSI                 | I/O                             | SPI Master Output Slave Input line<br>When SPI is in master mode, MOSI outputs data to the slave peripheral.<br>When SPI is in slave mode, MOSI receives data from the master controller.                                                                                                                                                                                                                            | P1.7                  |  |

| INT1:0#              | I                               | <b>External Interrupts 0 and 1</b><br>INT1#/INT0# inputs set IE1:0 in the TCON register. If bits IT1:0 in the<br>TCON register are set, bits IE1:0 are set by a falling edge on INT1#/INT0#.<br>If bits IT1:0 are cleared, bits IE1:0 are set by a low level on INT1#/INT0#.                                                                                                                                         | P3.3:2                |  |

#### **Configuration Bytes**

The TSC80251G2D derivatives provide user design flexibility by configuring certain operating features at device reset. These features fall into the following categories:

- external memory interface (Page mode, address bits, programmed wait states and the address range for RD#, WR#, and PSEN#)

- source mode/binary mode opcodes

- selection of bytes stored on the stack by an interrupt

- mapping of the upper portion of on-chip code memory to region 00:

Two user configuration bytes UCONFIG0 (see Table 11) and UCONFIG1 (see Table 12) provide the information.

When EA# is tied to a low level, the configuration bytes are fetched from the external address space. The TSC80251G2D derivatives reserve the top eight bytes of the memory address space (FF:FFF8h-FF:FFFh) for an external 8-byte configuration array. Only two bytes are actually used: UCONFIG0 at FF:FFF8h and UCONFIG1 at FF:FFF9h.

For the mask ROM devices, configuration information is stored in on-chip memory (see ROM Verifying). When EA# is tied to a high level, the configuration information is retrieved from the on-chip memory instead of the external address space and there is no restriction in the usage of the external memory.

### **Configuration Byte 1**

#### Table 13. Address Ranges and Usage of RD#, WR# and PSEN# Signals

| RD1 | RD0 | P1.7    | P3.7/RD#                                     | PSEN#                                               | WR#                                                  | External<br>Memory       |

|-----|-----|---------|----------------------------------------------|-----------------------------------------------------|------------------------------------------------------|--------------------------|

| 0   | 0   | A17     | A16                                          | Read signal for all<br>external memory<br>locations | Write signal for all<br>external memory<br>locations | 256 KB                   |

| 0   | 1   | I/O pin | A16                                          | Read signal for all<br>external memory<br>locations | Write signal for all<br>external memory<br>locations | 128 KB                   |

| 1   | 0   | I/O pin | I/O pin                                      | Read signal for all external memory locations       | Write signal for all external memory locations       | 64 KB                    |

| 1   | 1   | I/O pin | Read<br>signal for<br>regions 00:<br>and 01: | Read signal for<br>regions FE: and FF:              | Write signal for all<br>external memory<br>locations | 2 × 64 KB <sup>(1)</sup> |

Notes: 1. This selection provides compatibility with the standard 80C51 hardware which has separate external memory spaces for data and code.

|          | <dest>,</dest>            |                                                         | Binary Mode |                  | Source Mode |                  |

|----------|---------------------------|---------------------------------------------------------|-------------|------------------|-------------|------------------|

| Mnemonic | <src><sup>(2)</sup></src> | Comments                                                | Bytes       | States           | Bytes       | States           |

|          | Rmd, Rms                  | Register with register                                  | 3           | 2                | 2           | 1                |

|          | WRjd,<br>WRjs             | Word register with word register                        | 3           | 3                | 2           | 2                |

|          | DRkd,<br>DRks             | Dword register with dword register                      | 3           | 5                | 2           | 4                |

|          | Rm, #data                 | Register with immediate data                            | 4           | 3                | 3           | 2                |

|          | WRj,<br>#data16           | Word register with immediate 16-bit data                | 5           | 4                | 4           | 3                |

| ,        | DRk,<br>#0data16          | Dword register with zero-extended 16-bit immediate data | 5           | 6                | 4           | 5                |

| CMP      | DRk,<br>#1data16          | Dword register with one-extended 16-bit immediate data  | 5           | 6                | 4           | 5                |

|          | Rm, dir8                  | Direct address (on-chip RAM or SFR) with byte register  | 4           | 3 <sup>(1)</sup> | 3           | 2 <sup>(1)</sup> |

|          | WRj, dir8                 | Direct address (on-chip RAM or SFR) with word register  | 4           | 4                | 3           | 3                |

|          | Rm, dir16                 | Direct address (64K) with byte register                 | 5           | 3 <sup>(2)</sup> | 4           | 2 <sup>(2)</sup> |

|          | WRj, dir16                | Direct address (64K) with word register                 | 5           | 4 <sup>(3)</sup> | 4           | 3 <sup>(3)</sup> |

|          | Rm, at WRj                | Indirect address (64K) with byte register               | 4           | 3 <sup>(2)</sup> | 3           | 2 <sup>(2)</sup> |

|          | Rm, at DRk                | Indirect address (16M) with byte register               | 4           | 4 <sup>(2)</sup> | 3           | 3(2)             |

#### Table 22. Summary of Compare Instructions

Notes: 1. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 2. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

- 3. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

5

5

11

10

10

20

1

| Table 24. | Summary of Multiply | y, Divide and Decimal-adjust Instructions |

|-----------|---------------------|-------------------------------------------|

|-----------|---------------------|-------------------------------------------|

MultiplyMUL AB(B:A)  $\leftarrow$  (A)×(B) MUL <dest>, <src>extended dest opnd  $\leftarrow$  dest opnd  $\times$  src opnd DivideDIV AB(A)  $\leftarrow$  Quotient ((A)/(B)) (B)  $\leftarrow$  Remainder ((A)/(B)) DivideDIV <dest>, <src>ext. dest opnd high ← Quotient (dest opnd / src opnd) ext. dest opnd low ← Remainder (dest opnd / src opnd) Decimal-adjust ACCDA AIF [[(A)<sub>3:0</sub> > 9]  $\vee$  [(AC) = 1]] for Addition (BCD) THEN  $(A)_{3:0} \leftarrow (A)_{3:0} + 6$  laffects CY;  $\mathsf{IF} [[(A)_{7:4} > 9] \lor [(CY) = 1]]$ THEN  $(A)_{7:4} \leftarrow (A)_{7:4} + 6$ **Binary Mode** Source Mode <dest>, <src>(1) Bytes Mnemonic Comments Bytes States States AB Multiply A and B 1 5 1 MUL Rmd, Rms Multiply byte register and byte register 3 6 2 WRjd, WRjs Multiply word register and word register 3 12 2 AB 1 10 1 Divide A and B DIV Rmd, Rms Divide byte register and byte register 3 11 2 WRjd, WRjs 3 21 2 Divide word register and word register DA А Decimal adjust ACC 1 1 1

1. A shaded cell denotes an instruction in the C51 Architecture. Note:

#### Table 25. Summary of Move Instructions (1/3)

| Move to High wordMOVH <dest>, <src>dest opnd<sub><math>31:16 \leftarrow src opnd</math></sub></src></dest>                          |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Move with Sign extensionMOVS <dest>, <src>dest opnd <math>\leftarrow</math> src opnd with sign extend</src></dest>                  |

| Move with Zero extensionMOVZ <dest>, <src>dest opnd <math display="inline">\leftarrow</math> src opnd with zero extend</src></dest> |

| Move CodeMOVC A, $<$ src>(A) $\leftarrow$ src opnd                                                                                  |

|                                                                                                                                     |

Move eXtendedMOVX <dest>, <src>dest opnd  $\leftarrow$  src opnd

|          | <dest>,</dest>                               |                                                         | Binary Mode |                  | Source Mode |                  |

|----------|----------------------------------------------|---------------------------------------------------------|-------------|------------------|-------------|------------------|

| Mnemonic | <uest>,<br/><src><sup>(2)</sup></src></uest> | Comments                                                | Bytes       | States           | Bytes       | States           |

| MOVH     | DRk, #data16                                 | 16-bit immediate data into upper word of dword register | 5           | 3                | 4           | 2                |

| MOVS     | WRj, Rm                                      | Byte register to word register with sign extension      | 3           | 2                | 2           | 1                |

| MOVZ     | WRj, Rm                                      | Byte register to word register with zeros extension     | 3           | 2                | 2           | 1                |

| MOVC     | A, at A +DPTR                                | Code byte relative to DPTR to ACC                       | 1           | 6 <sup>(3)</sup> | 1           | 6 <sup>(3)</sup> |

|          | A, at A +PC                                  | Code byte relative to PC to ACC                         | 1           | 6 <sup>(3)</sup> | 1           | 6 <sup>(3)</sup> |

|          | A, at Ri                                     | Extended memory (8-bit address) to ACC <sup>(2)</sup>   | 1           | 4                | 1           | 5                |

| MOVX     | A, at DPTR                                   | Extended memory (16-bit address) to ACC <sup>(2)</sup>  | 1           | 3 <sup>(4)</sup> | 1           | 3 <sup>(4)</sup> |

|          | at Ri, A                                     | ACC to extended memory (8-bit address) <sup>(2)</sup>   | 1           | 4                | 1           | 4                |

|          | at DPTR, A                                   | ACC to extended memory (16-bit address) <sup>(2)</sup>  | 1           | 4 <sup>(3)</sup> | 1           | 4 <sup>(3)</sup> |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. Extended memory addressed is in the region specified by DPXL (reset value = 01h).

- 3. If this instruction addresses external memory location, add N+1 to the number of states (N: number of wait states).

- 4. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

# Programming and Verifying Non-volatile Memory

#### Internal Features

The internal non-volatile memory of the TSC80251G2D derivatives contains five different areas:

- Code Memory

- Configuration Bytes

- Lock Bits

- Encryption Array

- Signature Bytes

# **EPROM/OTPROM Devices** All the internal non-volatile memory but the Signature Bytes of the TSC87251G2D products are made of EPROM cells. The Signature Bytes of the TSC87251G2D products are made of Mask ROM.

The TSC87251G2D products are programmed and verified in the same manner as Atmel's TSC87251G1A, using a SINGLE-PULSE algorithm, which programs at  $V_{PP}$  = 12.75V using only one 100µs pulse per byte. This results in a programming time of less than 10 seconds for the 32 kilobytes on-chip code memory.

The EPROM of the TSC87251G2D products in Window package is erasable by Ultra-Violet radiation<sup>(1)</sup> (UV). UV erasure set all the EPROM memory cells to one and allows reprogramming. The quartz window must be covered with an opaque label<sup>(2)</sup> when the device is in operation. This is not so much to protect the EPROM array from inadvertent erasure, as to protect the RAM and other on-chip logic. Allowing light to impinge on the silicon die during device operation may cause a logical malfunction.

The TSC87251G2D products in plastic packages are One Time Programmable (OTP). An EPROM cell cannot be reset by UV once programmed to zero.

- Notes: 1. The recommended erasure procedure is exposure to ultra-violet light (at 2537 Å) to an integrated dose of at least 20 W-sec/cm<sup>2</sup>. Exposing the EPROM to an ultra-violet lamp of 12000 μW/cm<sup>2</sup> rating for 30 minutes should be sufficient.

- 2. Erasure of the EPROM begins to occur when the chip is exposed to light wavelength shorter than 4000 Å. Since sunlight and fluorescent light have wavelength in this range, exposure to these light sources over an extended time (1 week in sunlight or 3 years in room-level fluorescent lighting) could cause inadvertent erasure.

- Mask ROM DevicesAll the internal non-volatile memory of TSC83251G2D products is made of Mask ROM<br/>cells. They can only be verified by the user, using the same algorithm as the<br/>EPROM/OTPROM devices.

**ROMIess Devices**The TSC80251G2D products do not include on-chip Configuration Bytes, Code Memory<br/>and Encryption Array. They only include Signature Bytes made of Mask ROM cells<br/>which can be read using the same algorithm as the EPROM/OTPROM devices.

- **Security Features** In some microcontroller applications, it is desirable that the user's program code be secured from unauthorized access. The TSC83251G2D and TSC87251G2D offer two kinds of protection for program code stored in the on-chip array:

- Program code in the on-chip Code Memory is encrypted when read out for verification if the Encryption Array isprogrammed.

- A three-level lock bit system restricts external access to the on-chip code memory.

# **AC Characteristics - Commercial & Industrial**

### **AC Characteristics - External Bus Cycles**

**Definition of Symbols**

Table 38. External Bus Cycles Timing Symbol Definitions

| Signals   |  |  |

|-----------|--|--|

| Address   |  |  |

| Data In   |  |  |

| ALE       |  |  |

| Data Out  |  |  |

| RD#/PSEN# |  |  |

| WR#       |  |  |

|           |  |  |

| Conditions      |  |  |

|-----------------|--|--|

| High            |  |  |

| Low             |  |  |

| Valid           |  |  |

| No Longer Valid |  |  |

| Floating        |  |  |

|                 |  |  |

Timings

Test conditions: capacitive load on all pins = 50 pF.

Table 39 and Table 40 list the AC timing parameters for the TSC80251G2D derivatives with no wait states. External wait states can be added by extending PSEN#/RD#/WR# and or by extending ALE. In these tables, Note 2 marks parameters affected by one ALE wait state, and Note 3 marks parameters affected by PSEN#/RD#/WR# wait states.

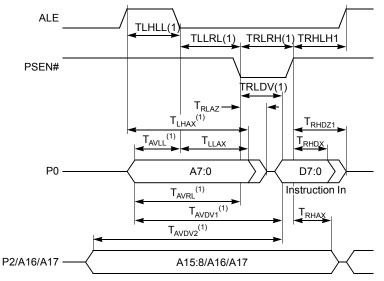

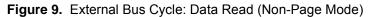

Figure 8 to Figure 13 show the bus cycles with the timing parameters.

Waveforms in Non-Page Mode Figure 8. External Bus Cycle: Code Fetch (Non-Page Mode)

Note: 1. The value of this parameter depends on wait states. See Table 39 and Table 40.

Note: 1. The value of this parameter depends on wait states. See Table 39 and Table 40.

**Table 42.** Real-Time Synchronous Wait AC Timings;  $V_{DD}$  = 2.7 to 5.5 V,  $T_A$  = -40 to 85°C

| Symbol            | Parameter                      | Min                     | Мах                          | Unit |

|-------------------|--------------------------------|-------------------------|------------------------------|------|

| T <sub>CLYV</sub> | Wait Clock Low to Wait Set-up  | 0                       | T <sub>OSC</sub> - 20        | ns   |

| T <sub>CLYX</sub> | Wait Hold after Wait Clock Low | 2W·T <sub>OSC</sub> + 5 | (1+2W)·T <sub>OSC</sub> - 20 | ns   |

| T <sub>RLYV</sub> | PSEN#/RD# Low to Wait Set-up   | 0                       | T <sub>OSC</sub> - 20        | ns   |

| T <sub>RLYX</sub> | Wait Hold after PSEN#/RD# Low  | 2W·T <sub>OSC</sub> + 5 | (1+2W)·T <sub>OSC</sub> - 20 | ns   |

| T <sub>WLYV</sub> | WR# Low to Wait Set-up         | 0                       | T <sub>OSC</sub> - 20        | ns   |

| T <sub>WLYX</sub> | Wait Hold after WR# Low        | 2W·T <sub>OSC</sub> + 5 | (1+2W)·T <sub>OSC</sub> - 20 | ns   |

#### Waveforms

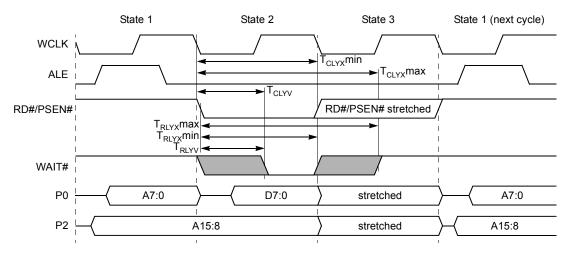

#### Figure 14. Real-time Synchronous Wait State: Code Fetch/Data Read

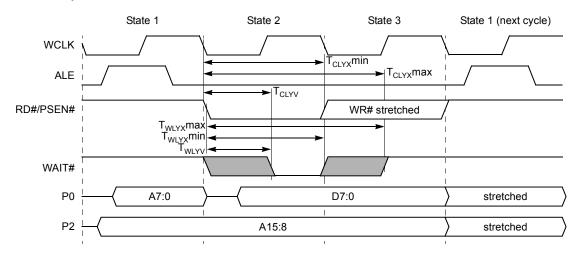

#### Figure 15. Real-time Synchronous Wait State: Data Write

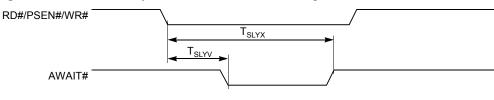

#### AC Characteristics - Real-Time Asynchronous Wait State

#### **Definition of Symbols**

**Table 43.** Real-Time Asynchronous Wait Timing Symbol Definitions

|   | Signals       |

|---|---------------|

| S | PSEN#/RD#/WR# |

| Y | AWAIT#        |

| Conditions |                 |  |

|------------|-----------------|--|

| L          | Low             |  |

| V          | Valid           |  |

| х          | No Longer Valid |  |

#### Timings

**Table 44.** Real-Time Asynchronous Wait AC Timings;  $V_{DD}$  = 2.7 to 5.5 V,  $T_A$  = -40 to 85°C

| Symbol            | Parameter                         | Min                          | Мах                   | Unit              |

|-------------------|-----------------------------------|------------------------------|-----------------------|-------------------|

| T <sub>SLYV</sub> | PSEN#/RD#/WR# Low to Wait Set-up  |                              | T <sub>OSC</sub> - 10 | ns                |

| T <sub>SLYX</sub> | Wait Hold after PSEN#/RD#/WR# Low | (2N-1)·T <sub>OSC</sub> + 10 |                       | ns <sup>(1)</sup> |

Note: 1. N is the number of wait states added (N $\geq$  1).

Waveforms

#### Figure 16. Real-time Asynchronous Wait State Timings

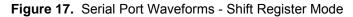

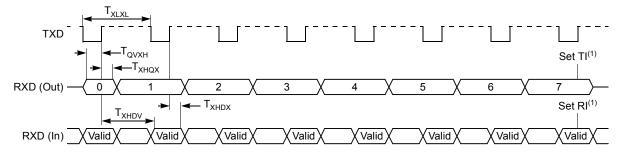

### AC Characteristics - Serial Port in Shift Register Mode

**Definition of Symbols**

#### Table 45. Serial Port Timing Symbol Definitions

| Signals |          |  |  |  |  |  |

|---------|----------|--|--|--|--|--|

| D       | Data In  |  |  |  |  |  |

| Q       | Data Out |  |  |  |  |  |

| Х       | Clock    |  |  |  |  |  |

| Conditions |                 |  |  |  |  |  |

|------------|-----------------|--|--|--|--|--|

| H High     |                 |  |  |  |  |  |

| L          | Low             |  |  |  |  |  |

| V          | Valid           |  |  |  |  |  |

| Х          | No Longer Valid |  |  |  |  |  |

**Table 46.** Serial Port AC Timing -Shift Register Mode;  $V_{DD}$  = 2.7 to 5.5 V,  $T_A$  = -40 to 85°C

|                   |                                             | 12  | MHz | 16  | ИНz | 24 M | Hz <sup>(1)</sup> |      |

|-------------------|---------------------------------------------|-----|-----|-----|-----|------|-------------------|------|

| Symbol            | Parameter                                   | Min | Max | Min | Max | Min  | Max               | Unit |

| T <sub>XLXL</sub> | Serial Port Clock Cycle Time                | 998 |     | 749 |     | 500  |                   | ns   |

| T <sub>QVXH</sub> | Output Data Setup to Clock Rising<br>Edge   | 833 |     | 625 |     | 417  |                   | ns   |

| T <sub>XHQX</sub> | Output Data hold after Clock Rising<br>Edge | 165 |     | 124 |     | 82   |                   | ns   |

| T <sub>XHDX</sub> | Input Data Hold after Clock Rising<br>Edge  | 0   |     | 0   |     | 0    |                   | ns   |

| T <sub>XHDV</sub> | Clock Rising Edge to Input Data<br>Valid    |     | 974 |     | 732 |      | 482               | ns   |

Note: 1. For high speed versions only.

#### Waveforms

Note: 1. TI and RI are set during S1P1 of the peripheral cycle following the shift of the eight bit.

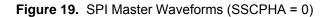

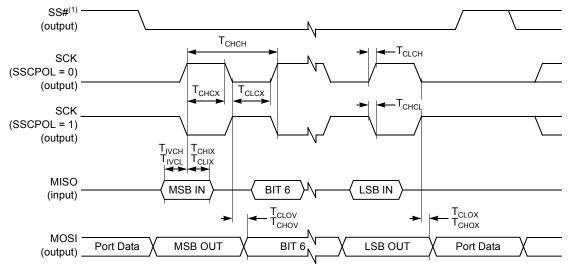

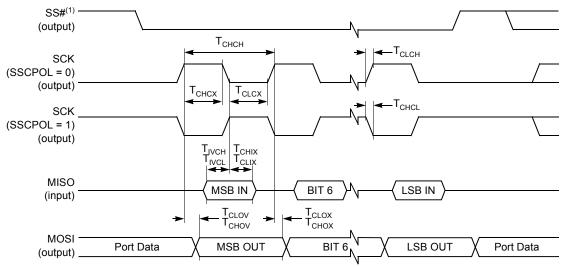

### **Table 49.** SPI Interface AC Timing; $V_{DD}$ = 2.7 to 5.5 V, $T_A$ = -40 to 85°C

| Symbol                                | Parameter                              | Min | Мах | Unit             |

|---------------------------------------|----------------------------------------|-----|-----|------------------|

|                                       | Slave Mode <sup>(1</sup>               | )   |     | 1                |

| Т <sub>снсн</sub>                     | Clock Period                           | 8   |     | T <sub>OSC</sub> |

| T <sub>CHCX</sub>                     | Clock High Time                        | 3.2 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 3.2 |     | T <sub>osc</sub> |

| T <sub>SLCH</sub> , T <sub>SLCL</sub> | SS# Low to Clock edge                  | 200 |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 100 | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>CLSH</sub> , T <sub>CHSH</sub> | SS# High after Clock Edge              | 0   |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>SLOV</sub>                     | SS# Low to Output Data Valid           |     | 130 | ns               |

| Т <sub>знох</sub>                     | Output Data Hold after SS# High        |     | 130 | ns               |

| T <sub>SHSL</sub>                     | SS# High to SS# Low                    | (2) |     |                  |

| T <sub>ILIH</sub>                     | Input Rise Time                        |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Fall Time                        |     | 2   | μs               |

| Т <sub>огон</sub>                     | Output Rise time                       |     | 100 | ns               |

| Т <sub>ОНОL</sub>                     | Output Fall Time                       |     | 100 | ns               |

|                                       | Master Mode                            | (3) |     |                  |

| Тснсн                                 | Clock Period                           | 4   |     | T <sub>osc</sub> |

| Т <sub>снсх</sub>                     | Clock High Time                        | 1.6 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 1.6 |     | T <sub>osc</sub> |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 50  |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 50  |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 65  | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>ILIH</sub>                     | Input Data Rise Time                   |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Data Fall Time                   |     | 2   | μs               |

| Т <sub>оloн</sub>                     | Output Data Rise time                  |     | 50  | ns               |

| Т <sub>оноь</sub>                     | Output Data Fall Time                  |     | 50  | ns               |

Notes: 1. Capacitive load on all pins = 200 pF in slave mode.

2. The value of this parameter depends on software.

3. Capacitive load on all pins = 100 pF in master mode.

Note: 1. SS# handled by software.

Note: 1. Not Defined but normally MSB of character just received.

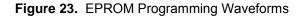

| Symbol            | Parameter                          | Min                  | Мах | Unit             |

|-------------------|------------------------------------|----------------------|-----|------------------|

| T <sub>osc</sub>  | XTAL1 Period                       | 83.5                 | 250 | ns               |

| T <sub>AVGL</sub> | Address Setup to PROG# low         | 48                   |     | T <sub>OSC</sub> |

| T <sub>GHAX</sub> | Address Hold after PROG# low       | 48                   |     | T <sub>OSC</sub> |

| T <sub>DVGL</sub> | Data Setup to PROG# low            | etup to PROG# low 48 |     | T <sub>OSC</sub> |

| T <sub>GHDX</sub> | Data Hold after PROG#              | 48                   |     | T <sub>OSC</sub> |

| T <sub>ELSH</sub> | ENABLE High to V <sub>PP</sub>     | 48                   |     | T <sub>OSC</sub> |

| T <sub>SHGL</sub> | V <sub>PP</sub> Setup to PROG# low | 10                   |     | μs               |

| T <sub>GHSL</sub> | V <sub>PP</sub> Hold after PROG#   | 10                   |     | μs               |

| T <sub>SLEH</sub> | ENABLE Hold after V <sub>PP</sub>  | 0                    |     | ns               |

| T <sub>GLGH</sub> | PROG# Width                        | 90                   | 110 | μs               |

### Table 51. EPROM Programming AC timings; $V_{DD}$ = 4.5 to 5.5 V, $T_A$ = 0 to 40°C

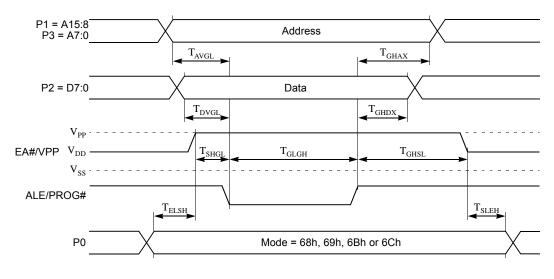

**Table 52.** EPROM Verifying AC timings;  $V_{DD}$  = 4.5 to 5.5 V,  $V_{DD}$  = 2.7 to 5.5 V,  $T_A$  = 0 to 40°C

| Symbol            | Parameter                | Min  | Мах | Unit             |

|-------------------|--------------------------|------|-----|------------------|

| T <sub>osc</sub>  | XTAL1 Period             | 83.5 | 250 | ns               |

| T <sub>AVQV</sub> | Address to Data Valid    |      | 48  | T <sub>osc</sub> |

| T <sub>AXQX</sub> | Address to Data Invalid  | 0    |     | ns               |

| T <sub>ELQV</sub> | ENABLE low to Data Valid | 0    | 48  | T <sub>osc</sub> |

| T <sub>EHQZ</sub> | Data Float after ENABLE  | 0    | 48  | T <sub>osc</sub> |

#### Waveforms

#### Figure 24. EPROM Verifying Waveforms

### AC Characteristics - External Clock Drive and Logic Level References

**Definition of Symbols**

Table 53. External Clock Timing Symbol Definitions

|   | Signals |  |  |  |  |

|---|---------|--|--|--|--|

| С | C Clock |  |  |  |  |

|   |         |  |  |  |  |

|   |         |  |  |  |  |

| Conditions        |     |  |  |  |  |

|-------------------|-----|--|--|--|--|

| H High            |     |  |  |  |  |

| L                 | Low |  |  |  |  |

| X No Longer Valid |     |  |  |  |  |

#### Timings

#### **Table 54.** External Clock AC Timings; $V_{DD}$ = 4.5 to 5.5 V, $T_A$ = -40 to +85°C

| Symbol            | Parameter            | Min | Max | Unit |

|-------------------|----------------------|-----|-----|------|

| F <sub>osc</sub>  | Oscillator Frequency |     | 24  | MHz  |

| T <sub>CHCX</sub> | High Time            | 10  |     | ns   |

| T <sub>CLCX</sub> | Low Time             | 10  |     | ns   |

| T <sub>CLCH</sub> | Rise Time            | 3   |     | ns   |

| T <sub>CHCL</sub> | Fall Time            | 3   |     | ns   |

#### Waveforms

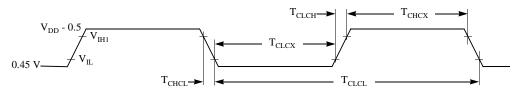

Figure 25. External Clock Waveform

- Notes: 1. During AC testing, all inputs are driven at  $V_{DD}$  -0.5 V for a logic 1 and 0.45 V for a logic 0.

- 2. Timing measurements are made on all outputs at  $V_{\rm IH}$  min for a logic 1 and  $V_{\rm IL}$  max for a logic 0.

# Absolute Maximum Rating and Operating Conditions

# Absolute Maximum Ratings

| Storage Temperature65 to +150°C              | *NOTICE: Stressing the device beyond the "Absolute Maxi-<br>mum Ratings" may cause permanent damage. |

|----------------------------------------------|------------------------------------------------------------------------------------------------------|

| Voltage on any other Pin to VSS0.5 to +6.5 V | These are stress ratings only. Operation beyond                                                      |

| I <sub>OL</sub> per I/O Pin 15 mA            | the "operating conditions" is not recommended<br>and extended exposure beyond the "Operating         |

| Power Dissipation 1.5 W                      | Conditions" may affect device reliability.                                                           |

| Ambient Temperature Under Bias               |                                                                                                      |

| Commercial0 to +70°C                         |                                                                                                      |

| Industrial40 to +85°C                        |                                                                                                      |

| Automotive40 to +85°C                        |                                                                                                      |

| V <sub>DD</sub>                              |                                                                                                      |

| High Speed versions                          |                                                                                                      |

| Low Voltage versions 2.7 to 5.5 V            |                                                                                                      |

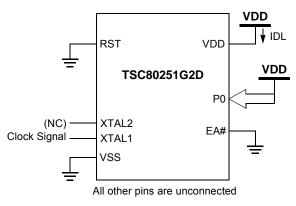

Figure 31.  $I_{DL}$  Test Condition, Idle Mode

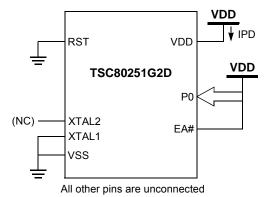

Figure 32.  $I_{PD}$  Test Condition, Power-Down Mode

CDIL 40 with Window -Mechanical Outline

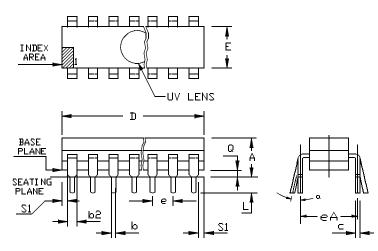

Figure 34. Ceramic Dual In Line

Table 58. CDIL Package Size

|    | ММ    |        | In          | ch    |

|----|-------|--------|-------------|-------|

|    | Min   | Мах    | Min         | Мах   |

| A  | -     | 5.71   | -           | .225  |

| b  | 0.36  | 0.58   | .014        | .023  |

| b2 | 1.14  | 1.65   | .045        | .065  |

| с  | 0.20  | 0.38   | .008        | .015  |

| D  | -     | 53.47  | -           | 2.105 |

| E  | 13.06 | 15.37  | .514        | .605  |

| e  | 2.54  | B.S.C. | .100 B.S.C. |       |

| eA | 15.24 | B.S.C. | .600 B.S.C. |       |

| L  | 3.18  | 5.08   | .125        | .200  |

| Q  | 0.38  | 1.40   | .015        | .055  |

| S1 | 0.13  | -      | .005        | -     |

| а  | 0 -   | 15     | 0 -         | 15    |

| Ν  | 40    |        |             |       |

# **Options** (Please

- ROM code encryption • consult Atmel sales)

- Tape & Reel or Dry Pack ٠

- Known good dice ٠

- Extended temperature range: -55°C to +125°C •

# **Product Markings**

**ROMIess versions**

ATMEL Part number Mask ROM versions

ATMEL Customer Part number Part Number YYWW . Lot Number

OTP versions

ATMEL Part number

YYWW . Lot Number

YYWW . Lot Number