Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | C251                                                                       |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 24MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, Microwire, SPI, UART/USART                      |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/tsc87251g2d-24ib |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Typical Operating Current:11 mA at 3V

- Typical Power-down Current: 1 μA

- Temperature Ranges: Commercial (0°C to +70°C), Industrial (-40°C to +85°C), Automotive ((-40°C to +85°C) ROM only)

- Option: Extended Range (-55°C to +125°C)

- Packages: PDIL 40, PLCC 44 and VQFP 44

- Options: Known Good Dice and Ceramic Packages

## Description

The TSC80251G2D products are derivatives of the Atmel Microcontroller family based on the 8/16-bit C251 Architecture. This family of products is tailored to 8/16-bit microcontroller applications requiring an increased instruction throughput, a reduced operating frequency or a larger addressable memory space. The architecture can provide a significant code size reduction when compiling C programs while fully preserving the legacy of C51 assembly routines.

The TSC80251G2D derivatives are pin and software compatible with standard 80C51/Fx/Rx/Rx+ with extended on-chip data memory (1 Kbyte RAM) and up to 256 kilobytes of external code and data. Additionally, the TSC83251G2D and TSC87251G2D provide on-chip code memory: 32 kilobytes ROM and 32 kilobytes EPROM/OTPROM respectively.

They provide transparent enhancements to Intel's xC251Sx family with an additional Synchronous Serial Link Controller (SSLC supporting TWI,  $\mu$ Wire and SPI protocols), a Keyboard interrupt interface, a dedicated Baud Rate Generator for UART, and Power Management features.

TSC80251G2D derivatives are optimized for speed and for low power consumption on a wide voltage range.

Note: 1. This Datasheet provides the technical description of the TSC80251G2D derivatives. For further information on the device usage, please request the TSC80251 Programmer's Guide and the TSC80251G1D Design Guide and errata sheet.

## Typical Applications • ISDN Terminals

- High-Speed Modems

- PABX (SOHO)

- Line Cards

- DVD ROM and Players

- Printers

- Plotters

- Scanners

- Banking Machines

- Barcode Readers

- Smart Cards Readers

- High-End Digital Monitors

- High-End Joysticks

- High-end TV's

| Table 2. Product Name Signal Description (Continued) |      |                                                                                                                                                                                                                                                                                                                                                          |                       |  |  |  |

|------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| Signal<br>Name                                       | Туре | Description                                                                                                                                                                                                                                                                                                                                              | Alternate<br>Function |  |  |  |

| T1:0                                                 | I/O  | <b>Timer 1:0 External Clock Inputs</b><br>When timer 1:0 operates as a counter, a falling edge on the T1:0 pin increments the count.                                                                                                                                                                                                                     | -                     |  |  |  |

| T2                                                   | I/O  | <b>Timer 2 Clock Input/Output</b><br>For the timer 2 capture mode, T2 is the external clock input. For the Timer 2 clock-out mode, T2 is the clock output.                                                                                                                                                                                               | P1.0                  |  |  |  |

| T2EX                                                 | I    | <b>Timer 2 External Input</b><br>In timer 2 capture mode, a falling edge initiates a capture of the timer 2<br>registers. In auto-reload mode, a falling edge causes the timer 2 register to<br>be reloaded. In the up-down counter mode, this signal determines the<br>count direction: 1 = up, 0 = down.                                               | P1.1                  |  |  |  |

| тхр                                                  | 0    | <b>Transmit Serial Data</b><br>TXD outputs the shift clock in serial I/O mode 0 and transmits data in serial<br>I/O modes 1, 2 and 3.                                                                                                                                                                                                                    | P3.1                  |  |  |  |

| VDD                                                  | PWR  | <b>Digital Supply Voltage</b><br>Connect this pin to +5V or +3V supply voltage.                                                                                                                                                                                                                                                                          | -                     |  |  |  |

| VPP                                                  | I    | <b>Programming Supply Voltage</b><br>The programming supply voltage is applied to this input for programming<br>the on-chip EPROM/OTPROM.                                                                                                                                                                                                                | -                     |  |  |  |

| VSS                                                  | GND  | Circuit Ground<br>Connect this pin to ground.                                                                                                                                                                                                                                                                                                            | -                     |  |  |  |

| VSS1                                                 | GND  | Secondary Ground 1<br>This ground is provided to reduce ground bounce and improve power<br>supply bypassing. Connection of this pin to ground is recommended.<br>However, when using the TSC80251G2D as a pin-for-pin replacement for a<br>8xC51 product, VSS1 can be unconnected without loss of compatibility.<br>Not available on DIP package.        | Ι                     |  |  |  |

| VSS2                                                 | GND  | <b>Secondary Ground 2</b><br>This ground is provided to reduce ground bounce and improve power<br>supply bypassing. Connection of this pin to ground is recommended.<br>However, when using the TSC80251G2D as a pin-for-pin replacement for a<br>8xC51 product, VSS2 can be unconnected without loss of compatibility.<br>Not available on DIP package. | _                     |  |  |  |

| WAIT#                                                | I    | <b>Real-time Synchronous Wait States Input</b><br>The real-time WAIT# input is enabled by setting RTWE bit in WCON<br>(S:A7h). During bus cycles, the external memory system can signal<br>'system ready' to the microcontroller in real time by controlling the WAIT#<br>input signal.                                                                  | P1.6                  |  |  |  |

| WCLK                                                 | 0    | Wait Clock Output<br>The real-time WCLK output is enabled by setting RTWCE bit in WCON<br>(S:A7h). When enabled, the WCLK output produces a square wave signal<br>with a period of one half the oscillator frequency.                                                                                                                                    | P1.7                  |  |  |  |

| WR#                                                  | 0    | <b>Write</b><br>Write signal output to external memory.                                                                                                                                                                                                                                                                                                  | P3.6                  |  |  |  |

| XTAL1                                                | I    | Input to the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected to this<br>pin. If an external oscillator is used, its output is connected to this pin.<br>XTAL1 is the clock source for internal timing.                                                                                | -                     |  |  |  |

Table 2.

Product Name Signal Description (Continued)

### Table 16. Notation for Immediate Addressing

| Immediate<br>Address | Description                                                                                                                           | C251 | C51 |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| #data                | An 8-bit constant that is immediately addressed in an instruction                                                                     | 3    | 3   |

| #data16              | A 16-bit constant that is immediately addressed in an instruction                                                                     | 3    | -   |

| #0data16<br>#1data16 | A 32-bit constant that is immediately addressed in an instruction. The upper word is filled with zeros (#0data16) or ones (#1data16). | 3    | _   |

| #short               | A constant, equal to 1, 2, or 4, that is immediately addressed in an instruction.                                                     | 3    | _   |

## Table 17. Notation for Bit Addressing

| Direct<br>Address | Description                                                                                                                                                                                                                                                            | C251 | C51 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| bit51             | A directly addressed bit (bit number = 00h-FFh) in memory or an SFR. Bits 00h-7Fh are the 128 bits in byte locations 20h-2Fh in the on-chip RAM. Bits 80h-FFh are the 128 bits in the 16 SFRs with addresses that end in 0h or 8h, S:80h, S:88h, S:90h,, S:F0h, S:F8h. | _    | 3   |

| bit               | A directly addressed bit in memory locations 00:0020h-00:007Fh or in any defined SFR.                                                                                                                                                                                  | 3    |     |

## Table 18. Notation for Destination in Control Instructions

| Direct<br>Address | Description                                                                                                                              | C251 | C51 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| rel               | A signed (two's complement) 8-bit relative address. The destination is -128 to +127 bytes relative to the next instruction's first byte. | 3    | 3   |

| addr11            | An 11-bit target address. The target is in the same 2-Kbyte block of memory as the next instruction's first byte.                        | _    | 3   |

| addr16            | A 16-bit target address. The target can be anywhere within the same 64-Kbyte region as the next instruction's first byte.                | _    | 3   |

| addr24            | A 24-bit target address. The target can be anywhere within the 16-<br>Mbyte address space.                                               | 3    | -   |

|          | <dest>,</dest>            |                                                         | Binary | Mode             | Source Mode |                  |

|----------|---------------------------|---------------------------------------------------------|--------|------------------|-------------|------------------|

| Mnemonic | <src><sup>(2)</sup></src> | Comments                                                | Bytes  | States           | Bytes       | States           |

|          | Rmd, Rms                  | Register with register                                  | 3      | 2                | 2           | 1                |

|          | WRjd,<br>WRjs             | Word register with word register                        | 3      | 3                | 2           | 2                |

|          | DRkd,<br>DRks             | Dword register with dword register                      | 3      | 5                | 2           | 4                |

|          | Rm, #data                 | Register with immediate data                            | 4      | 3                | 3           | 2                |

|          | WRj,<br>#data16           | Word register with immediate 16-bit data                | 5      | 4                | 4           | 3                |

|          | DRk,<br>#0data16          | Dword register with zero-extended 16-bit immediate data | 5      | 6                | 4           | 5                |

| CMP      | DRk,<br>#1data16          | Dword register with one-extended 16-bit immediate data  | 5      | 6                | 4           | 5                |

|          | Rm, dir8                  | Direct address (on-chip RAM or SFR) with byte register  | 4      | 3 <sup>(1)</sup> | 3           | 2 <sup>(1)</sup> |

|          | WRj, dir8                 | Direct address (on-chip RAM or SFR) with word register  | 4      | 4                | 3           | 3                |

|          | Rm, dir16                 | Direct address (64K) with byte register                 | 5      | 3 <sup>(2)</sup> | 4           | 2 <sup>(2)</sup> |

|          | WRj, dir16                | Direct address (64K) with word register                 | 5      | 4 <sup>(3)</sup> | 4           | 3 <sup>(3)</sup> |

|          | Rm, at WRj                | Indirect address (64K) with byte register               | 4      | 3 <sup>(2)</sup> | 3           | 2 <sup>(2)</sup> |

|          | Rm, at DRk                | Indirect address (16M) with byte register               | 4      | 4 <sup>(2)</sup> | 3           | 3(2)             |

## Table 22. Summary of Compare Instructions

Notes: 1. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 2. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

- 3. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

$\texttt{Logical AND}^{(1)}\texttt{ANL <dest>, <src>dest opnd \leftarrow dest opnd \Lambda \ src opnd$ Logical OR<sup>(1)</sup>ORL <dest>, <src>dest opnd  $\leftarrow$  dest opnd  $\varsigma$  src opnd  $\texttt{Logical Exclusive OR^{(1)}XRL <dest>, <src>dest opnd \leftarrow dest opnd \forall src opnd }$ Clear<sup>(1)</sup>CLR A(A)  $\leftarrow$  0 Complement<sup>(1)</sup>CPL A(A)  $\leftarrow \emptyset$  (A) Rotate LeftRL  $A(A)_{n+1} \leftarrow (A)_n$ , n = 0..6  $(\mathsf{A})_0 \gets (\mathsf{A})_7$ Rotate Left CarryRLC  $A(A)_{n+1} \leftarrow (A)_n$ , n = 0..6  $(CY) \leftarrow (A)_7$  $(A)_0 \leftarrow (CY)$ Rotate RightRR  $A(A)_{n-1} \leftarrow (A)_n$ , n = 7..1  $(A)_7 \leftarrow (A)_0$ Rotate Right CarryRRC  $A(A)_{n-1} \leftarrow (A)_n$ , n = 7..1  $(CY) \leftarrow (A)_0$  $(A)_7 \leftarrow (CY)$

|          |                                          |                                                      | Binary | Mode             | Source Mode |                  |  |

|----------|------------------------------------------|------------------------------------------------------|--------|------------------|-------------|------------------|--|

| Mnemonic | <dest>, <src><sup>(1)</sup></src></dest> | Comments                                             | Bytes  | States           | Bytes       | States           |  |

|          | A, Rn                                    | register to ACC                                      | 1      | 1                | 2           | 2                |  |

|          | A, dir8                                  | Direct address (on-chip RAM or SFR) to ACC           | 2      | 1 <sup>(3)</sup> | 2           | 1 <sup>(3)</sup> |  |

|          | A, at Ri                                 | Indirect address to ACC                              | 1      | 2                | 2           | 3                |  |

|          | A, #data                                 | Immediate data to ACC                                | 2      | 1                | 2           | 1                |  |

|          | dir8, A                                  | ACC to direct address                                | 2      | 2 <sup>(4)</sup> | 2           | 2 <sup>(4)</sup> |  |

|          | dir8, #data                              | Immediate 8-bit data to direct address               | 3      | 3(4)             | 3           | 3(4)             |  |

|          | Rmd, Rms                                 | Byte register to byte register                       | 3      | 2                | 2           | 1                |  |

| ANL      | WRjd, WRjs                               | Word register to word register                       | 3      | 3                | 2           | 2                |  |

| ORL      | Rm, #data                                | Immediate 8-bit data to byte register                | 4      | 3                | 3           | 2                |  |

| XRL      | WRj, #data16                             | Immediate 16-bit data to word register               | 5      | 4                | 4           | 3                |  |

|          | Rm, dir8                                 | Direct address (on-chip RAM or SFR) to byte register | 4      | 3 <sup>(3)</sup> | 3           | 2 <sup>(3)</sup> |  |

|          | WRj, dir8                                | Direct address (on-chip RAM or SFR) to word register | 4      | 4                | 3           | 3                |  |

|          | Rm, dir16                                | Direct address (64K) to byte register                | 5      | 3 <sup>(5)</sup> | 4           | 2 <sup>(5)</sup> |  |

|          | WRj, dir16                               | Direct address (64K) to word register                | 5      | 4 <sup>(6)</sup> | 4           | 3 <sup>(6)</sup> |  |

|          | Rm, at WRj                               | Indirect address (64K) to byte register              | 4      | 3 <sup>(5)</sup> | 3           | 2 <sup>(5)</sup> |  |

|          | Rm, at DRk                               | Indirect address (16M) to byte register              | 4      | 4 <sup>(5)</sup> | 3           | 3 <sup>(5)</sup> |  |

| CLR      | А                                        | Clear ACC                                            | 1      | 1                | 1           | 1                |  |

| CPL      | A                                        | Complement ACC                                       | 1      | 1                | 1           | 1                |  |

| RL       | A                                        | Rotate ACC left                                      | 1      | 1                | 1           | 1                |  |

| RLC      | A                                        | Rotate ACC left through CY                           | 1      | 1                | 1           | 1                |  |

| RR       | A                                        | Rotate ACC right                                     | 1      | 1                | 1           | 1                |  |

| RRC      | A                                        | Rotate ACC right through CY                          | 1      | 1                | 1           | 1                |  |

|          | <dest>,</dest>                               |                                                             | Binary Mode |                  | Source Mode |                  |

|----------|----------------------------------------------|-------------------------------------------------------------|-------------|------------------|-------------|------------------|

| Mnemonic | <uest>,<br/><src><sup>(2)</sup></src></uest> | Comments                                                    | Bytes       | States           | Bytes       | States           |

|          | A, Rn                                        | Register to ACC                                             | 1           | 1                | 2           | 2                |

|          | A, dir8                                      | Direct address (on-chip RAM or SFR) to ACC                  | 2           | 1 <sup>(3)</sup> | 2           | 1 <sup>(3)</sup> |

|          | A, at Ri                                     | Indirect address to ACC                                     | 1           | 2                | 2           | 3                |

|          | A, #data                                     | Immediate data to ACC                                       | 2           | 1                | 2           | 1                |

|          | Rn, A                                        | ACC to register                                             | 1           | 1                | 2           | 2                |

|          | Rn, dir8                                     | Direct address (on-chip RAM or SFR) to register             | 2           | 1 <sup>(3)</sup> | 3           | 2 <sup>(3)</sup> |

|          | Rn, #data                                    | Immediate data to register                                  | 2           | 1                | 3           | 2                |

|          | dir8, A                                      | ACC to direct address (on-chip RAM or SFR)                  | 2           | 2 <sup>(3)</sup> | 2           | 2 <sup>(3)</sup> |

| MOV      | dir8, Rn                                     | Register to direct address (on-chip<br>RAM or SFR)          | 2           | 2 <sup>(3)</sup> | 3           | 3(3)             |

|          | dir8, dir8                                   | Direct address to direct address (on-<br>chip RAM or SFR)   | 3           | 3 <sup>(4)</sup> | 3           | 3 <sup>(4)</sup> |

|          | dir8, at Ri                                  | Indirect address to direct address (on-<br>chip RAM or SFR) | 2           | 3 <sup>(3)</sup> | 3           | 4 <sup>(3)</sup> |

|          | dir8, #data                                  | Immediate data to direct address (on-<br>chip RAM or SFR)   | 3           | 3 <sup>(3)</sup> | 3           | 3(3)             |

|          | at Ri, A                                     | ACC to indirect address                                     | 1           | 3                | 2           | 4                |

|          | at Ri, dir8                                  | Direct address (on-chip RAM or SFR) to indirect address     | 2           | 3 <sup>(3)</sup> | 3           | 4 <sup>(3)</sup> |

|          | at Ri, #data                                 | Immediate data to indirect address                          | 2           | 3                | 3           | 4                |

|          | DPTR,<br>#data16                             | Load Data Pointer with a 16-bit constant                    | 3           | 2                | 3           | 2                |

| Table 26. | Summary | y of Move | Instructions | (2/3) | ) |

|-----------|---------|-----------|--------------|-------|---|

|-----------|---------|-----------|--------------|-------|---|

Notes: 1. Instructions that move bits are in Table 27.

2. Move instructions from the C51 Architecture.

- 3. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 4. Apply note 3 for each dir8 operand.

|          |                                          |                                                          | Binary Mode |                  | Source Mode |                  |

|----------|------------------------------------------|----------------------------------------------------------|-------------|------------------|-------------|------------------|

| Mnemonic | <dest>, <src><sup>(1)</sup></src></dest> | Comments                                                 | Bytes       | States           | Bytes       | States           |

| MOV      | Rmd, Rms                                 | Byte register to byte register                           | 3           | 2                | 2           | 1                |

| MOV      | WRjd, WRjs                               | Word register to word register                           | 3           | 2                | 2           | 1                |

| MOV      | DRkd, DRks                               | Dword register to dword register                         | 3           | 3                | 2           | 2                |

| MOV      | Rm, #data                                | Immediate 8-bit data to byte register                    | 4           | 3                | 3           | 2                |

| MOV      | WRj, #data16                             | Immediate 16-bit data to word register                   | 5           | 3                | 4           | 2                |

| MOV      | DRk, #0data16                            | zero-ext 16bit immediate data to dword register          | 5           | 5                | 4           | 4                |

| MOV      | DRk, #1data16                            | one-ext 16bit immediate data to dword register           | 5           | 5                | 4           | 4                |

| MOV      | Rm, dir8                                 | Direct address (on-chip RAM or SFR) to byte register     | 4           | 3 <sup>(3)</sup> | 3           | 2 <sup>(3)</sup> |

| MOV      | WRj, dir8                                | Direct address (on-chip RAM or SFR) to word register     | 4           | 4                | 3           | 3                |

| MOV      | DRk, dir8                                | Direct address (on-chip RAM or SFR) to dword register    | 4           | 6                | 3           | 5                |

| MOV      | Rm, dir16                                | Direct address (64K) to byte register                    | 5           | 3 <sup>(4)</sup> | 4           | 2 <sup>(4)</sup> |

| MOV      | WRj, dir16                               | Direct address (64K) to word register                    | 5           | 4 <sup>(5)</sup> | 4           | 3 <sup>(5)</sup> |

| MOV      | DRk, dir16                               | Direct address (64K) to dword register                   | 5           | 6 <sup>(6)</sup> | 4           | 5 <sup>(6)</sup> |

| MOV      | Rm, at WRj                               | Indirect address (64K) to byte register                  | 4           | 3 <sup>(4)</sup> | 3           | 2(4)             |

| MOV      | Rm, at DRk                               | Indirect address (16M) to byte register                  | 4           | 4 <sup>(4)</sup> | 3           | 3(4)             |

| MOV      | WRjd, at WRjs                            | Indirect address (64K) to word register                  | 4           | 4 <sup>(5)</sup> | 3           | 3 <sup>(5)</sup> |

| MOV      | WRj, at DRk                              | Indirect address (16M) to word register                  | 4           | 5 <sup>(5)</sup> | 3           | 4 <sup>(5)</sup> |

| MOV      | dir8, Rm                                 | Byte register to direct address (on-chip RAM or SFR)     | 4           | 4 <sup>(3)</sup> | 3           | 3 <sup>(3)</sup> |

| MOV      | dir8, WRj                                | Word register to direct address (on-chip RAM or SFR)     | 4           | 5                | 3           | 4                |

| MOV      | dir8, DRk                                | Dword register to direct address (on-chip RAM or SFR)    | 4           | 7                | 3           | 6                |

| MOV      | dir16, Rm                                | Byte register to direct address (64K)                    | 5           | 4 <sup>(4)</sup> | 4           | 3(4)             |

| MOV      | dir16, WRj                               | Word register to direct address (64K)                    | 5           | 5 <sup>(5)</sup> | 4           | 4 <sup>(5)</sup> |

| MOV      | dir16, DRk                               | Dword register to direct address (64K)                   | 5           | 7 <sup>(6)</sup> | 4           | 6 <sup>(6)</sup> |

| MOV      | at WRj, Rm                               | Byte register to indirect address (64K)                  | 4           | 4 <sup>(4)</sup> | 3           | 3(4)             |

| MOV      | at DRk, Rm                               | Byte register to indirect address (16M)                  | 4           | 5 <sup>(4)</sup> | 3           | 4 <sup>(4)</sup> |

| MOV      | at WRjd, WRjs                            | Word register to indirect address (64K)                  | 4           | 5 <sup>(5)</sup> | 3           | 4 <sup>(5)</sup> |

| MOV      | at DRk, WRj                              | Word register to indirect address (16M)                  | 4           | 6 <sup>(5)</sup> | 3           | 5 <sup>(5)</sup> |

| MOV      | Rm, at WRj<br>+dis16                     | Indirect with 16-bit displacement (64K) to byte register | 5           | 6 <sup>(4)</sup> | 4           | 5 <sup>(4)</sup> |

| MOV      | WRj, at WRj<br>+dis16                    | Indirect with 16-bit displacement (64K) to word register | 5           | 7 <sup>(5)</sup> | 4           | 6 <sup>(5)</sup> |

| MOV      | Rm, at DRk<br>+dis24                     | Indirect with 16-bit displacement (16M) to byte register | 5           | 7 <sup>(4)</sup> | 4           | 6 <sup>(4)</sup> |

| MOV | WRj, at WRj<br>+dis24 | Indirect with 16-bit displacement (16M) to word register | 5 | 8 <sup>(5)</sup> | 4 | 7 <sup>(5)</sup> |

|-----|-----------------------|----------------------------------------------------------|---|------------------|---|------------------|

| MOV | at WRj +dis16,<br>Rm  | Byte register to indirect with 16-bit displacement (64K) | 5 | 6 <sup>(4)</sup> | 4 | 5 <sup>(4)</sup> |

| MOV | at WRj +dis16,<br>WRj | Word register to indirect with 16-bit displacement (64K) | 5 | 7 <sup>(5)</sup> | 4 | 6 <sup>(5)</sup> |

| MOV | at DRk +dis24,<br>Rm  | Byte register to indirect with 16-bit displacement (16M) | 5 | 7 <sup>(4)</sup> | 4 | 6 <sup>(4)</sup> |

| MOV | at DRk +dis24,<br>WRj | Word register to indirect with 16-bit displacement (16M) | 5 | 8(5)             | 4 | 7 <sup>(5)</sup> |

Notes: 1. Instructions that move bits are in Table 27.

2. Move instructions unique to the C251 Architecture.

3. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

4. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

5. If this instruction addresses external memory location, add 2(N+1) to the number of states (N: number of wait states).

6. If this instruction addresses external memory location, add 4(N+2) to the number of states (N: number of wait states).

Add 3 if it addresses a Peripheral SFR.

- 5. If this instruction addresses an I/O Port (Px, x = 0-3), add 3 to the number of states. Add 5 if it addresses a Peripheral SFR.

- 6. In internal execution only, add 1 to the number of states of the 'jump taken' if the destination address is internal and odd.

## Table 31. Summary of Unconditional Jump Instructions

Absolute jumpAJMP <src>(PC)  $\leftarrow$  (PC) +2; (PC)<sub>10:0</sub>  $\leftarrow$  src opnd Extended jumpEJMP <src>(PC)  $\leftarrow$  (PC) + size (instr); (PC)<sub>23:0</sub>  $\leftarrow$  src opnd Long jumpLJMP <src>(PC)  $\leftarrow$  (PC) + size (instr); (PC)<sub>15:0</sub>  $\leftarrow$  src opnd Short jumpSJMP rel(PC)  $\leftarrow$  (PC) +2; (PC)  $\leftarrow$  (PC) +rel Jump indirectJMP at A +DPTR(PC)<sub>23:16</sub>  $\leftarrow$  FFh; (PC)<sub>15:0</sub>  $\leftarrow$  (A) + (DPTR) No operationNOP(PC)  $\leftarrow$  (PC) +1

|          | <dest>,</dest>            |                                    | Binary | Mode                | Source Mode |                     |

|----------|---------------------------|------------------------------------|--------|---------------------|-------------|---------------------|

| Mnemonic | <src><sup>(1)</sup></src> | Comments                           | Bytes  | States              | Bytes       | States              |

| AJMP     | addr11                    | Absolute jump                      | 2      | 3 <sup>(2)(3)</sup> | 2           | 3 <sup>(2)(3)</sup> |

| EJMP     | addr24                    | Extended jump                      | 5      | 6 <sup>(2)(4)</sup> | 4           | 5 <sup>(2)(4)</sup> |

| EJIVIP   | at DRk                    | Extended jump (indirect)           | 3      | 7 <sup>(2)(4)</sup> | 2           | 6 <sup>(2)(4)</sup> |

| LJMP     | at WRj                    | Long jump (indirect)               | 3      | 6 <sup>(2)(4)</sup> | 2           | 5 <sup>(2)(4)</sup> |

| LJIMP    | addr16                    | Long jump (direct address)         | 3      | 5 <sup>(2)(4)</sup> | 3           | 5 <sup>(2)(4)</sup> |

| SJMP     | rel                       | Short jump (relative address)      | 2      | 4 <sup>(2)(4)</sup> | 2           | 4 <sup>(2)(4)</sup> |

| JMP      | at A +DPTR                | Jump indirect relative to the DPTR | 1      | 5 <sup>(2)(4)</sup> | 1           | 5 <sup>(2)(4)</sup> |

| NOP      |                           | No operation (Jump never)          | 1      | 1                   | 1           | 1                   |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

- 2. In internal execution only, add 1 to the number of states if the destination address is internal and odd.

- 3. Add 2 to the number of states if the destination address is external.

- 4. Add 3 to the number of states if the destination address is external.

| Table 32. | Summar | of Call and | Return | Instructions |

|-----------|--------|-------------|--------|--------------|

|-----------|--------|-------------|--------|--------------|

|                                | ACALL <src><br/><math>\leftarrow</math> src opnd</src> | $(PC) \leftarrow (PC)$ +2; push $(PC)_{15:0}$ ;                                                                                                                                                           |                            |                                                                                                                 |                            |                                                                                           |

|--------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------|

| Extended ca                    |                                                        | $P(PC) \leftarrow (PC) + size (instr); push (PC)_2$                                                                                                                                                       | 3:0,                       |                                                                                                                 |                            |                                                                                           |

| Long callLCA                   |                                                        | ) $\leftarrow$ (PC) + size (instr); push (PC) <sub>15:0</sub> ;                                                                                                                                           |                            |                                                                                                                 |                            |                                                                                           |

| Return from                    | subroutineRE                                           | Tpop (PC) <sub>15:0</sub>                                                                                                                                                                                 |                            |                                                                                                                 |                            |                                                                                           |

|                                |                                                        | outineERETpop(PC) <sub>23:0</sub>                                                                                                                                                                         |                            |                                                                                                                 |                            |                                                                                           |

|                                |                                                        | IF [INTR = 0] THEN pop (PC) <sub>15:0</sub><br>pop (PC) <sub>23:0</sub> ; pop (PSW1)                                                                                                                      |                            |                                                                                                                 |                            |                                                                                           |

| Trap interrup<br>IF [INTF      | tTRAP(PC) ←<br>R = 0] THEN p                           | - (PC) + size (instr);                                                                                                                                                                                    |                            |                                                                                                                 |                            |                                                                                           |

|                                |                                                        |                                                                                                                                                                                                           | Binary                     | / Mode                                                                                                          | Source                     | e Mode                                                                                    |

|                                | <dest>,</dest>                                         |                                                                                                                                                                                                           |                            |                                                                                                                 | <b>.</b>                   | _                                                                                         |

| Mnemonic                       | <src><sup>(1)</sup></src>                              | Comments                                                                                                                                                                                                  | Bytes                      | States                                                                                                          | Bytes                      | States                                                                                    |

| Mnemonic<br>ACALL              | <src>(")<br/>addr11</src>                              | Comments           Absolute subroutine call                                                                                                                                                               | Bytes<br>2                 | 9 <sup>(2)(3)</sup>                                                                                             | Bytes<br>2                 |                                                                                           |

| ACALL                          |                                                        |                                                                                                                                                                                                           | -                          |                                                                                                                 | ,                          | States<br>9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                                       |

| ACALL                          | addr11                                                 | Absolute subroutine call                                                                                                                                                                                  | 2                          | 9 <sup>(2)(3)</sup>                                                                                             | 2                          | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                                                 |

| ACALL                          | addr11<br>at DRk                                       | Absolute subroutine call<br>Extended subroutine call (indirect)                                                                                                                                           | 2 3                        | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup>                                                                     | 2<br>2                     | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup>                          |

| ACALL                          | addr11<br>at DRk<br>addr24                             | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call                                                                                                     | 2<br>3<br>5                | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup>                                             | 2<br>2<br>4                | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>9 <sup>(2)(3</sup>    |

| ACALL                          | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call<br>Extended subroutine call (indirect)<br>Extended subroutine call<br>Long subroutine call (indirect)                                                                            | 2<br>3<br>5<br>3           | 9 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>14 <sup>(2)(3)</sup><br>10 <sup>(2)(3)</sup>                     | 2<br>2<br>4<br>2           | 9 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>13 <sup>(2)(3</sup><br>9 <sup>(2)(3</sup>    |

| ACALL<br>ECALL<br>LCALL<br>RET | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call         Long subroutine call (indirect)         Long subroutine call                                | 2<br>3<br>5<br>3<br>3      | $\begin{array}{c} 9^{(2)(3)} \\ 14^{(2)(3)} \\ 14^{(2)(3)} \\ 10^{(2)(3)} \\ 9^{(2)(3)} \end{array}$            | 2<br>2<br>4<br>2<br>3      | $9^{(2)(3)}$ $13^{(2)(3)}$ $13^{(2)(3)}$ $9^{(2)(3)}$ $9^{(2)(3)}$                        |

| ACALL<br>ECALL<br>LCALL        | addr11<br>at DRk<br>addr24<br>at WRj                   | Absolute subroutine call         Extended subroutine call (indirect)         Extended subroutine call         Long subroutine call (indirect)         Long subroutine call         Return from subroutine | 2<br>3<br>5<br>3<br>3<br>1 | $\begin{array}{c} 9^{(2)(3)} \\ 14^{(2)(3)} \\ 14^{(2)(3)} \\ 10^{(2)(3)} \\ 9^{(2)(3)} \\ 7^{(2)} \end{array}$ | 2<br>2<br>4<br>2<br>3<br>1 | $9^{(2)(3)}$ $13^{(2)(3)}$ $13^{(2)(3)}$ $9^{(2)(3)}$ $9^{(2)(3)}$ $9^{(2)(3)}$ $7^{(2)}$ |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. In internal execution only, add 1 to the number of states if the destination/return address is internal and odd.

- 3. Add 2 to the number of states if the destination address is external.

- 4. Add 5 to the number of states if INTR = 1.

To preserve the secrecy of the encryption key byte sequence, the Encryption Array can not be verified.

- Notes: 1. When a MOVC instruction is executed, the content of the ROM is not encrypted. In order to fully protect the user program code, the lock bit level 1 (see Table 33) must always be set when encryption is used.

- 2. If the encryption feature is implemented, the portion of the on-chip code memory that does not contain program code should be filled with "random" byte values to prevent the encryption key sequence from being revealed.

**Signature Bytes** The TSC80251G2D derivatives contain factory-programmed Signature Bytes. These bytes are located in non-volatile memory outside the memory address space at 30h, 31h, 60h and 61h. To read the Signature Bytes, perform the procedure described in section Verify Algorithm, using the verify signature mode (see Table 37). Signature byte values are listed in Table 35.

|              |                                    | Signature Address | Signature Data |

|--------------|------------------------------------|-------------------|----------------|

| Vendor       | Atmel                              | 30h               | 58h            |

| Architecture | C251                               | 31h               | 40h            |

| Memory       | 32 kilobytes EPROM or<br>OTPROM    | 60h               | F7h            |

| Niemory      | 32 kilobytes MaskROM<br>or ROMless | 0011              | 77h            |

| Revision     | TSC80251G2D<br>derivative          | 61h               | FDh            |

Table 35. Signature Bytes (Electronic ID)

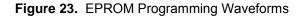

# **Programming Algorithm** Figure 6 shows the hardware setup needed to program the TSC87251G2D EPROM/OTPROM areas:

- The chip has to be put under reset and maintained in this state until completion of the programming sequence.

- PSEN# and the other control signals (ALE and Port 0) have to be set to a high level.

- Then PSEN# has to be to forced to a low level after two clock cycles or more and it

has to be maintained in this state until the completion of the programming sequence

(see below).

- The voltage on the EA# pin must be set to V<sub>DD</sub>.

- The programming mode is selected according to the code applied on Port 0 (see Table 36). It has to be applied until the completion of this programming operation.

- The programming address is applied on Ports 1 and 3 which are respectively the Most Significant Byte (MSB) and the Least Significant Byte (LSB) of the address.

- The programming data are applied on Port 2.

- The EPROM Programming is done by raising the voltage on the EA# pin to V<sub>PP</sub>, then by generating a low level pulse on ALE/PROG# pin.

- The voltage on the EA# pin must be lowered to V<sub>DD</sub> before completing the programming operation.

- It is possible to alternate programming and verifying operation (See Paragraph Verify Algorithm). Please make sure the voltage on the EA# pin has actually been lowered to V<sub>DD</sub> before performing the verifying operation.

|                                  |                                               | 12  | MHz | 16  | MHz | 24 1 | MHz | Unit                |

|----------------------------------|-----------------------------------------------|-----|-----|-----|-----|------|-----|---------------------|

| Symbol                           | Parameter                                     | Min | Max | Min | Max | Min  | Max |                     |

| T <sub>OSC</sub>                 | 1/F <sub>osc</sub>                            | 83  |     | 62  |     | 41   |     | ns                  |

| T <sub>LHLL</sub>                | ALE Pulse Width                               | 78  |     | 58  |     | 38   |     | ns <sup>(2)</sup>   |

| T <sub>AVLL</sub>                | Address Valid to ALE Low                      | 78  |     | 58  |     | 37   |     | ns <sup>(2)</sup>   |

| $T_{LLAX}$                       | Address hold after ALE Low                    | 19  |     | 11  |     | 3    |     | ns                  |

| T <sub>RLRH</sub> <sup>(1)</sup> | RD#/PSEN# Pulse Width                         | 162 |     | 121 |     | 78   |     | ns <sup>(3)</sup>   |

| T <sub>WLWH</sub>                | WR# Pulse Width                               | 165 |     | 124 |     | 81   |     | ns <sup>(3)</sup>   |

| $T_{LLRL}^{(1)}$                 | ALE Low to RD#/PSEN# Low                      | 22  |     | 14  |     | 6    |     | ns                  |

| T <sub>LHAX</sub>                | ALE High to Address Hold                      | 99  |     | 70  |     | 40   |     | ns <sup>(2)</sup>   |

| T <sub>RLDV</sub> <sup>(1)</sup> | RD#/PSEN# Low to Valid Data                   |     | 146 |     | 104 |      | 61  | ns <sup>(3)</sup>   |

| $T_{RHDX}^{(1)}$                 | Data Hold After RD#/PSEN# High                | 0   |     | 0   |     | 0    |     | ns                  |

| T <sub>RHAX</sub> <sup>(1)</sup> | Address Hold After RD#/PSEN#<br>High          | 0   |     | 0   |     | 0    |     | ns                  |

| T <sub>RLAZ</sub> <sup>(1)</sup> | RD#/PSEN# Low to Address Float                |     | 0   |     | 0   |      | 0   | ns                  |

| T <sub>RHDZ1</sub>               | Instruction Float After RD#/PSEN#<br>High     |     | 45  |     | 40  |      | 30  | ns                  |

| T <sub>RHDZ2</sub>               | Data Float After RD#/PSEN# High               |     | 215 |     | 165 |      | 115 | ns                  |

| T <sub>RHLH1</sub>               | RD#/PSEN# high to ALE High<br>(Instruction)   | 49  |     | 43  |     | 31   |     | ns                  |

| T <sub>RHLH2</sub>               | RD#/PSEN# high to ALE High<br>(Data)          | 215 |     | 169 |     | 115  |     | ns                  |

| T <sub>WHLH</sub>                | WR# High to ALE High                          | 215 |     | 169 |     | 115  |     | ns                  |

| T <sub>AVDV1</sub>               | Address (P0) Valid to Valid Data In           |     | 250 |     | 175 |      | 105 | ns <sup>(2)(3</sup> |

| T <sub>AVDV2</sub>               | Address (P2) Valid to Valid Data In           |     | 306 |     | 223 |      | 140 | ns <sup>(2)(3</sup> |

| T <sub>AVDV3</sub>               | Address (P0) Valid to Valid<br>Instruction In |     | 150 |     | 109 |      | 68  | ns <sup>(3)</sup>   |

| T <sub>AXDX</sub>                | Data Hold after Address Hold                  | 0   |     | 0   |     | 0    |     | ns                  |

| T <sub>AVRL</sub> <sup>(1)</sup> | Address Valid to RD# Low                      | 100 |     | 70  |     | 40   |     | ns <sup>(2</sup>    |

| T <sub>AVWL1</sub>               | Address (P0) Valid to WR# Low                 | 100 |     | 70  |     | 40   |     | ns <sup>(2</sup>    |

| T <sub>AVWL2</sub>               | Address (P2) Valid to WR# Low                 | 158 |     | 115 |     | 74   |     | ns <sup>(2</sup>    |

| T <sub>WHQX</sub>                | Data Hold after WR# High                      | 90  |     | 69  |     | 32   |     | ns                  |

| T <sub>QVWH</sub>                | Data Valid to WR# High                        | 133 |     | 102 |     | 72   |     | ns <sup>(3</sup>    |

| T <sub>WHAX</sub>                | WR# High to Address Hold                      | 167 |     | 125 |     | 84   |     | ns                  |

| Table 39. Bus Cycles AC Timings; | $V_{DD}$ = 4.5 to 5.5 V, $T_A$ = -40 to 85°C |

|----------------------------------|----------------------------------------------|

|----------------------------------|----------------------------------------------|

Notes: 1. Specification for PSEN# are identical to those for RD#.

2. If a wait state is added by extending ALE, add  $2 \cdot T_{OSC}$ . 3. If wait states are added by extending RD#/PSEN#/WR#, add  $2N \cdot T_{OSC}$  (N = 1..3).

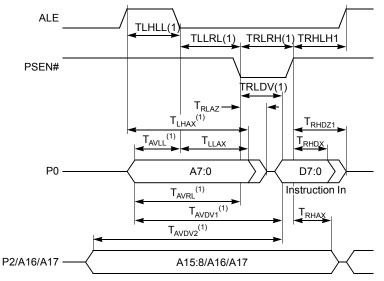

Waveforms in Non-Page Mode Figure 8. External Bus Cycle: Code Fetch (Non-Page Mode)

Note: 1. The value of this parameter depends on wait states. See Table 39 and Table 40.

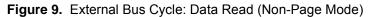

Note: 1. The value of this parameter depends on wait states. See Table 39 and Table 40.

## Timings

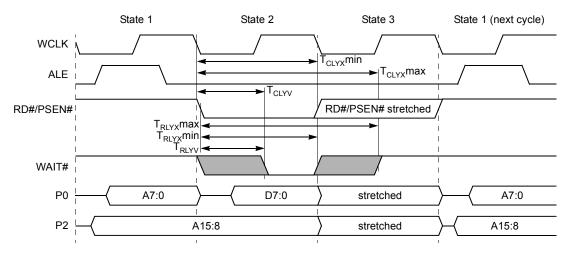

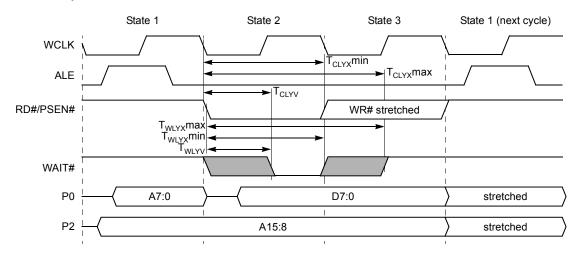

**Table 42.** Real-Time Synchronous Wait AC Timings;  $V_{DD}$  = 2.7 to 5.5 V,  $T_A$  = -40 to 85°C

| Symbol            | Parameter                      | Min                     | Мах                          | Unit |

|-------------------|--------------------------------|-------------------------|------------------------------|------|

| T <sub>CLYV</sub> | Wait Clock Low to Wait Set-up  | 0                       | T <sub>OSC</sub> - 20        | ns   |

| T <sub>CLYX</sub> | Wait Hold after Wait Clock Low | 2W·T <sub>OSC</sub> + 5 | (1+2W)·T <sub>OSC</sub> - 20 | ns   |

| T <sub>RLYV</sub> | PSEN#/RD# Low to Wait Set-up   | 0                       | T <sub>OSC</sub> - 20        | ns   |

| T <sub>RLYX</sub> | Wait Hold after PSEN#/RD# Low  | 2W·T <sub>OSC</sub> + 5 | (1+2W)·T <sub>OSC</sub> - 20 | ns   |

| T <sub>WLYV</sub> | WR# Low to Wait Set-up         | 0                       | T <sub>OSC</sub> - 20        | ns   |

| T <sub>WLYX</sub> | Wait Hold after WR# Low        | 2W·T <sub>OSC</sub> + 5 | (1+2W)·T <sub>OSC</sub> - 20 | ns   |

## Waveforms

### Figure 14. Real-time Synchronous Wait State: Code Fetch/Data Read

## Figure 15. Real-time Synchronous Wait State: Data Write

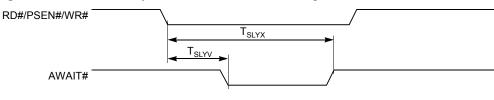

## AC Characteristics - Real-Time Asynchronous Wait State

### **Definition of Symbols**

**Table 43.** Real-Time Asynchronous Wait Timing Symbol Definitions

| Signals  |               |  |  |

|----------|---------------|--|--|

| S        | PSEN#/RD#/WR# |  |  |

| Y AWAIT# |               |  |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| L          | Low             |  |  |  |

| V          | Valid           |  |  |  |

| х          | No Longer Valid |  |  |  |

#### Timings

**Table 44.** Real-Time Asynchronous Wait AC Timings;  $V_{DD}$  = 2.7 to 5.5 V,  $T_A$  = -40 to 85°C

| Symbol            | Parameter                         | Min                          | Мах                   | Unit              |

|-------------------|-----------------------------------|------------------------------|-----------------------|-------------------|

| T <sub>SLYV</sub> | PSEN#/RD#/WR# Low to Wait Set-up  |                              | T <sub>OSC</sub> - 10 | ns                |

| T <sub>SLYX</sub> | Wait Hold after PSEN#/RD#/WR# Low | (2N-1)·T <sub>OSC</sub> + 10 |                       | ns <sup>(1)</sup> |

Note: 1. N is the number of wait states added (N $\geq$  1).

Waveforms

## Figure 16. Real-time Asynchronous Wait State Timings

## AC Characteristics - Serial Port in Shift Register Mode

**Definition of Symbols**

## Table 45. Serial Port Timing Symbol Definitions

| Signals |          |  |  |  |  |

|---------|----------|--|--|--|--|

| D       | Data In  |  |  |  |  |

| Q       | Data Out |  |  |  |  |

| Х       | Clock    |  |  |  |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| Н          | High            |  |  |  |

| L          | Low             |  |  |  |

| V          | Valid           |  |  |  |

| Х          | No Longer Valid |  |  |  |

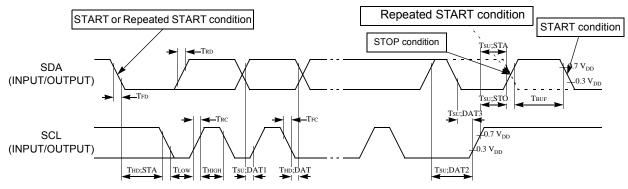

## AC Characteristics - SSLC: TWI Interface

## Timings

Table 47. TWI Interface AC Timing;  $V_{\text{DD}}$  = 2.7 to 5.5 V,  $T_{\text{A}}$  = -40 to 85°C

|           |                                                   | INPUT                   | OUTPUT                        |  |

|-----------|---------------------------------------------------|-------------------------|-------------------------------|--|

| Symbol    | Parameter                                         | Min Max                 | Min Max                       |  |

| THD; STA  | Start condition hold time                         | 14·Tclcl <sup>(4)</sup> | 4.0 μs <sup>(1)</sup>         |  |

| TLOW      | SCL low time                                      | 16·Tclcl <sup>(4)</sup> | 4.7 μs <sup>(1)</sup>         |  |

| Тнідн     | SCL high time                                     | 14·Tclcl <sup>(4)</sup> | 4.0 μs <sup>(1)</sup>         |  |

| Trc       | SCL rise time                                     | 1 μs                    | _(2)                          |  |

| TFC       | SCL fall time                                     | 0.3 μs                  | 0.3 μs <sup>(3)</sup>         |  |

| Tsu; DAT1 | Data set-up time                                  | 250 ns                  | 20.TCLCL <sup>(4)</sup> - TRD |  |

| Tsu; DAT2 | SDA set-up time (before repeated START condition) | 250 ns                  | 1 μs <sup>(1)</sup>           |  |

| Ts∪; DAT3 | SDA set-up time (before STOP condition)           | 250 ns                  | 8.TCLCL <sup>(4)</sup>        |  |

| THD; DAT  | Data hold time                                    | 0 ns                    | 8.TCLCL <sup>(4)</sup> - TFC  |  |

| Ts∪; STA  | Repeated START set-up time                        | 14·Tclcl <sup>(4)</sup> | 4.7 μs <sup>(1)</sup>         |  |

| Tsu; STO  | STOP condition set-up time                        | 14·Tclcl <sup>(4)</sup> | 4.0 μs <sup>(1)</sup>         |  |

| Твиғ      | Bus free time                                     | 14·Tclcl <sup>(4)</sup> | 4.7 μs <sup>(1)</sup>         |  |

| Trd       | SDA rise time                                     | 1 μs                    | _(2)                          |  |

| Tfd       | SDA fall time                                     | 0.3 μs                  | 0.3 μs <sup>(3)</sup>         |  |

Notes: 1. At 100 kbit/s. At other bit-rates this value is inversely proportional to the bit-rate of 100 kbit/s.

- 2. Determined by the external bus-line capacitance and the external bus-line pull-up resistor, this must be < 1  $\mu s.$

- Spikes on the SDA and SCL lines with a duration of less than 3. TCLCL will be filtered out. Maximum capacitance on bus-lines SDA and SCL = 400 pF.

- 4. TCLCL =  $T_{OSC}$  = one oscillator clock period.

## Waveforms

#### Figure 18. TWI Waveforms

# 54 AT/TSC8x251G2D

## Timings

## **Table 49.** SPI Interface AC Timing; $V_{DD}$ = 2.7 to 5.5 V, $T_A$ = -40 to 85°C

| Symbol                                | Parameter                              | Min | Max | Unit             |

|---------------------------------------|----------------------------------------|-----|-----|------------------|

|                                       | Slave Mode <sup>(1</sup>               | )   |     | 1                |

| Т <sub>снсн</sub>                     | Clock Period                           | 8   |     | T <sub>OSC</sub> |

| T <sub>CHCX</sub>                     | Clock High Time                        | 3.2 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 3.2 |     | T <sub>osc</sub> |

| T <sub>SLCH</sub> , T <sub>SLCL</sub> | SS# Low to Clock edge                  | 200 |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 100 | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>CLSH</sub> , T <sub>CHSH</sub> | SS# High after Clock Edge              | 0   |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>SLOV</sub>                     | SS# Low to Output Data Valid           |     | 130 | ns               |

| Т <sub>знох</sub>                     | Output Data Hold after SS# High        |     | 130 | ns               |

| T <sub>SHSL</sub>                     | SS# High to SS# Low                    | (2) |     |                  |

| T <sub>ILIH</sub>                     | Input Rise Time                        |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Fall Time                        |     | 2   | μs               |

| Т <sub>огон</sub>                     | Output Rise time                       |     | 100 | ns               |

| Т <sub>оног</sub>                     | Output Fall Time                       |     | 100 | ns               |

|                                       | Master Mode                            | (3) |     |                  |

| Тснсн                                 | Clock Period                           | 4   |     | T <sub>osc</sub> |

| Т <sub>снсх</sub>                     | Clock High Time                        | 1.6 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 1.6 |     | T <sub>osc</sub> |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 50  |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 50  |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 65  | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>ILIH</sub>                     | Input Data Rise Time                   |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Data Fall Time                   |     | 2   | μs               |

| Т <sub>оloн</sub>                     | Output Data Rise time                  |     | 50  | ns               |

| Т <sub>оноь</sub>                     | Output Data Fall Time                  |     | 50  | ns               |

Notes: 1. Capacitive load on all pins = 200 pF in slave mode.

2. The value of this parameter depends on software.

3. Capacitive load on all pins = 100 pF in master mode.

## Timings

| Symbol            | Parameter                          | Min Max  |     | Unit             |

|-------------------|------------------------------------|----------|-----|------------------|

| T <sub>osc</sub>  | XTAL1 Period                       | 83.5 250 |     | ns               |

| T <sub>AVGL</sub> | Address Setup to PROG# low         | 48       |     | T <sub>OSC</sub> |

| T <sub>GHAX</sub> | Address Hold after PROG# low       | 48       |     | T <sub>OSC</sub> |

| T <sub>DVGL</sub> | Data Setup to PROG# low            | 48       |     | T <sub>OSC</sub> |

| T <sub>GHDX</sub> | Data Hold after PROG#              | 48       |     | T <sub>OSC</sub> |

| T <sub>ELSH</sub> | ENABLE High to V <sub>PP</sub>     | 48       |     | T <sub>OSC</sub> |

| T <sub>SHGL</sub> | V <sub>PP</sub> Setup to PROG# low | 10       |     | μs               |

| T <sub>GHSL</sub> | V <sub>PP</sub> Hold after PROG#   | 10       |     | μs               |

| T <sub>SLEH</sub> | ENABLE Hold after V <sub>PP</sub>  | 0        |     | ns               |

| T <sub>GLGH</sub> | PROG# Width                        | 90       | 110 | μs               |

## Table 51. EPROM Programming AC timings; $V_{DD}$ = 4.5 to 5.5 V, $T_A$ = 0 to 40°C

**Table 52.** EPROM Verifying AC timings;  $V_{DD}$  = 4.5 to 5.5 V,  $V_{DD}$  = 2.7 to 5.5 V,  $T_A$  = 0 to 40°C

| Symbol            | Parameter                | Min  | Мах              | Unit             |

|-------------------|--------------------------|------|------------------|------------------|

| T <sub>osc</sub>  | XTAL1 Period 83.5        |      | 250              | ns               |

| T <sub>AVQV</sub> | Address to Data Valid 48 |      | T <sub>osc</sub> |                  |

| T <sub>AXQX</sub> | Address to Data Invalid  | 0    |                  | ns               |

| T <sub>ELQV</sub> | ENABLE low to Data Valid | 0 48 |                  | T <sub>osc</sub> |

| T <sub>EHQZ</sub> | Data Float after ENABLE  | 0 48 |                  | T <sub>osc</sub> |

## Waveforms

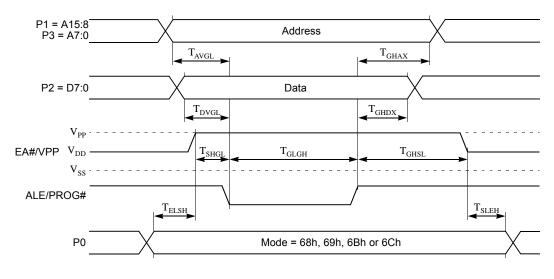

## Packages

List of Packages

- PDIL 40

- CDIL 40 with window

- PLCC 44

- CQPJ 44 with window

- VQFP 44 (10x10)

## PDIL 40 - Mechanical Outline

Figure 33. Plastic Dual In Line

## Table 57. PDIL Package Size

|    | MM           |       | Inch        |       |  |

|----|--------------|-------|-------------|-------|--|

|    | Min          | Мах   | Min         | Мах   |  |

| А  | -            | 5.08  | -           | .200  |  |

| A1 | 0.38         | -     | .015        | -     |  |

| A2 | 3.18         | 4.95  | .125        | .195  |  |

| В  | 0.36         | 0.56  | .014        | .022  |  |

| B1 | 0.76         | 1.78  | .030        | .070  |  |

| С  | 0.20         | 0.38  | .008        | .015  |  |

| D  | 50.29        | 53.21 | 1.980       | 2.095 |  |

| E  | 15.24        | 15.87 | .600        | .625  |  |

| E1 | 12.32        | 14.73 | .485        | .580  |  |

| е  | 2.54 B.S.C.  |       | .100 B.S.C. |       |  |

| eA | 15.24 B.S.C. |       | .600 B.S.C. |       |  |

| eB | -            | 17.78 | -           | .700  |  |

| L  | 2.93         | 3.81  | .115        | .150  |  |

| D1 | 0.13         | -     | .005        | -     |  |

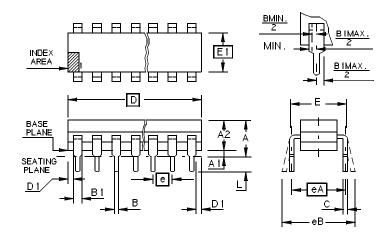

# AT/TSC8x251G2D

CDIL 40 with Window -Mechanical Outline

Figure 34. Ceramic Dual In Line

Table 58. CDIL Package Size

|    | ММ            |       | Inch        |       |

|----|---------------|-------|-------------|-------|

|    | Min           | Max   | Min         | Мах   |

| A  | -             | 5.71  | -           | .225  |

| b  | 0.36          | 0.58  | .014        | .023  |

| b2 | 1.14          | 1.65  | .045        | .065  |

| с  | 0.20          | 0.38  | .008        | .015  |

| D  | -             | 53.47 | -           | 2.105 |

| E  | 13.06         | 15.37 | .514        | .605  |

| e  | 2.54 B.S.C.   |       | .100 B.S.C. |       |

| eA | 15.24 B.S.C.  |       | .600 B.S.C. |       |

| L  | 3.18          | 5.08  | .125        | .200  |

| Q  | 0.38          | 1.40  | .015        | .055  |

| S1 | 0.13          | -     | .005        | -     |

| а  | 0 - 15 0 - 15 |       | 15          |       |

| Ν  | 40            |       |             |       |