Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | C251                                                                        |

| Core Size                  | 8/16-Bit                                                                    |

| Speed                      | 24MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, Microwire, SPI, UART/USART                       |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 32                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-LCC (J-Lead)                                                             |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/tsc87251g2d-24ibr |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Pin Description**

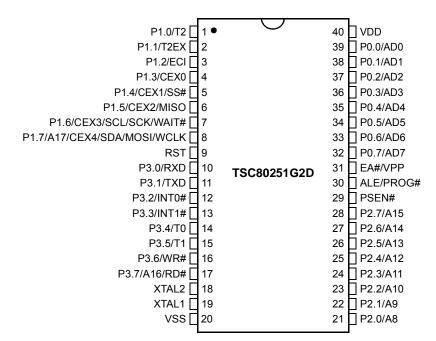

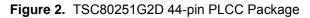

Pinout

Figure 1. TSC80251G2D 40-pin DIP package

## **Address Spaces**

The TSC80251G2D derivatives implement four different address spaces:

- On-chip ROM program/code memory (not present in ROMless devices)

- On-chip RAM data memory

- Special Function Registers (SFRs)

- Configuration array

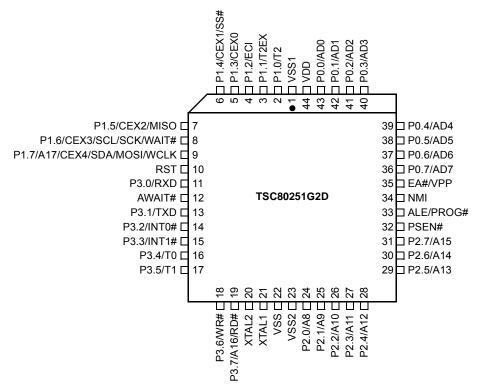

#### **Program/Code Memory** The TSC83251G2D and TSC87251G2D implement 32 KB of on-chip program/code memory. Figure 4 shows the split of the internal and external program/code memory spaces. If EA# is tied to a high level, the 32-Kbyte on-chip program memory is mapped in the lower part of segment FF: where the C251 core jumps after reset. The rest of the program/code memory space is mapped to the external memory. If EA# is tied to a low level, the internal program/code memory is not used and all the accesses are directed to the external memory.

The TSC83251G2D products provide the internal program/code memory in a masked ROM memory while the TSC87251G2D products provide it in an EPROM memory. For the TSC80251G2D products, there is no internal program/code memory and EA# must be tied to a low level.

Note:

Special care should be taken when the Program Counter (PC) increments:

If the program executes exclusively from on-chip code memory (not from external memory), beware of executing code from the upper eight bytes of the on-chip ROM (FF:7FF8h-FF:7FFh). Because of its pipeline capability, the TSC80251G2D derivative may attempt to prefetch code from external memory (at an address above FF:7FFFh) and thereby disrupt I/O Ports 0 and 2. Fetching code constants from these 8 bytes does not affect Ports 0 and 2.

When PC reaches the end of segment FF:, it loops to the reset address FF:0000h (for

compatibility with the C51 Architecture). When PC increments beyond the end of seqment FE:, it continues at the reset address FF:0000h (linearity). When PC increments beyond the end of segment 01:, it loops to the beginning of segment 00: (this prevents from its going into the reserved area).

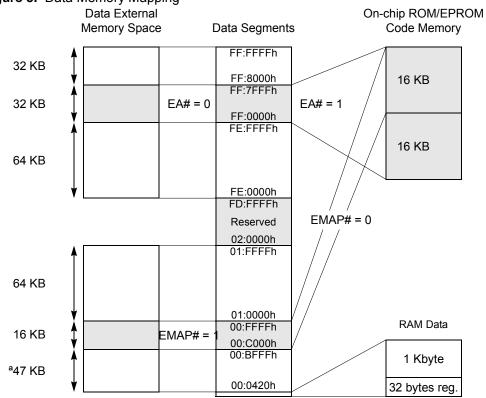

Data Memory The TSC80251G2D derivatives implement 1 Kbyte of on-chip data RAM. Figure 5 shows the split of the internal and external data memory spaces. This memory is mapped in the data space just over the 32 bytes of registers area (see TSC80251 Programmers' Guide). Hence, the part of the on-chip RAM located from 20h to FFh is bit addressable. This on-chip RAM is not accessible through the program/code memory space.

> For faster computation with the on-chip ROM/EPROM code of the TSC83251G2D/TSC87251G2D, its upper 16 KB are also mapped in the upper part of the region 00: if the On-Chip Code Memory Map configuration bit is cleared (EMAP# bit in UCONFIG1 byte, see Figure ). However, if EA# is tied to a low level, the TSC80251G2D derivative is running as a ROMless product and the code is actually fetched in the corresponding external memory (i.e. the upper 16 KB of the lower 32 KB of the segment FF:). If EMAP# bit is set, the on-chip ROM is not accessible through the region 00:.

> All the accesses to the portion of the data space with no on-chip memory mapped onto are redirected to the external memory.

Figure 5. Data Memory Mapping

# Special Function Registers

The Special Function Registers (SFRs) of the TSC80251G2D derivatives fall into the categories detailed in Table 1 to Table 9.

SFRs are placed in a reserved on-chip memory region S: which is not represented in the data memory mapping (Figure 5). The relative addresses within S: of these SFRs are provided together with their reset values in Table . They are upward compatible with the SFRs of the standard 80C51 and the Intel's 80C251Sx family. In this table, the C251 core registers are identified by Note 1 and are described in the TSC80251 Programmer's Guide. The other SFRs are described in the TSC80251G1D Design Guide. All the SFRs are bit-addressable using the C251 instruction set.

#### Table 1. C251 Core SFRs

| Mnemonic           | Name                       |  |  |  |

|--------------------|----------------------------|--|--|--|

| ACC <sup>(1)</sup> | Accumulator                |  |  |  |

| B <sup>(1)</sup>   | B Register                 |  |  |  |

| PSW                | Program Status Word        |  |  |  |

| PSW1               | Program Status Word 1      |  |  |  |

| SP <sup>(1)</sup>  | Stack Pointer - LSB of SPX |  |  |  |

| Mnemonic            | Name                                                     |

|---------------------|----------------------------------------------------------|

| SPH <sup>(1)</sup>  | Stack Pointer High - MSB of<br>SPX                       |

| DPL <sup>(1)</sup>  | Data Pointer Low byte - LSB of DPTR                      |

| DPH <sup>(1)</sup>  | Data Pointer High byte - MSB of DPTR                     |

| DPXL <sup>(1)</sup> | Data Pointer Extended Low<br>byte of DPX - Region number |

Note: 1. These SFRs can also be accessed by their corresponding registers in the register file.

#### Table 2. I/O Port SFRs

| Mnemonic | Name   |

|----------|--------|

| P0       | Port 0 |

| P1       | Port 1 |

# MnemonicNameP2Port 2P3Port 3

## Table 3. Timers SFRs

| Mnemonic | Name                             |  |  |

|----------|----------------------------------|--|--|

| TL0      | Timer/Counter 0 Low<br>Byte      |  |  |

| TH0      | Timer/Counter 0 High<br>Byte     |  |  |

| TL1      | Timer/Counter 1 Low<br>Byte      |  |  |

| TH1      | Timer/Counter 1 High<br>Byte     |  |  |

| TL2      | Timer/Counter 2 Low<br>Byte      |  |  |

| TH2      | Timer/Counter 2 High<br>Byte     |  |  |

| TCON     | Timer/Counter 0 and 1<br>Control |  |  |

| Mnemonic | Name                                           |

|----------|------------------------------------------------|

| TMOD     | Timer/Counter 0 and 1<br>Modes                 |

| T2CON    | Timer/Counter 2<br>Control                     |

| T2MOD    | Timer/Counter 2 Mode                           |

| RCAP2L   | Timer/Counter 2<br>Reload/Capture Low<br>Byte  |

| RCAP2H   | Timer/Counter 2<br>Reload/Capture High<br>Byte |

| WDTRST   | WatchDog Timer Reset                           |

#### Table 10. SFR Descriptions

|     | 0/8                             | 1/9                              | 2/A                             | 3/B                             | 4/C                              | 5/D                 | 6/E                             | 7/F               |     |

|-----|---------------------------------|----------------------------------|---------------------------------|---------------------------------|----------------------------------|---------------------|---------------------------------|-------------------|-----|

| F8h |                                 | CH<br>0000 0000                  | CCAP0H<br>0000 0000             | CCAP1H<br>0000 0000             | CCAP2H<br>0000 0000              | CCAP3H<br>0000 0000 | CCAP4H<br>0000 0000             |                   | FFh |

| F0h | B <sup>(1)</sup><br>0000 0000   |                                  |                                 |                                 |                                  |                     |                                 |                   | F7h |

| E8h |                                 | CL<br>0000 0000                  | CCAP0L<br>0000 0000             | CCAP1L<br>0000 0000             | CCAP2L<br>0000 0000              | CCAP3L<br>0000 0000 | CCAP4L<br>0000 0000             |                   | EFh |

| E0h | ACC <sup>(1)</sup><br>0000 0000 |                                  |                                 |                                 |                                  |                     |                                 |                   | E7h |

| D8h | CCON<br>00X0 0000               | CMOD<br>00XX X000                | CCAPM0<br>X000 0000             | CCAPM1<br>X000 0000             | CCAPM2<br>X000 0000              | CCAPM3<br>X000 0000 | CCAPM4<br>X000 0000             |                   | DFh |

| D0h | PSW <sup>(1)</sup><br>0000 0000 | PSW1 <sup>(1)</sup><br>0000 0000 |                                 |                                 |                                  |                     |                                 |                   | D7h |

| C8h | T2CON<br>0000 0000              | T2MOD<br>XXXX XX00               | RCAP2L<br>0000 0000             | RCAP2H<br>0000 0000             | TL2<br>0000 0000                 | TH2<br>0000 0000    |                                 |                   | CFh |

| C0h |                                 |                                  |                                 |                                 |                                  |                     |                                 |                   | C7h |

| B8h | IPL0<br>X000 0000               | SADEN<br>0000 0000               |                                 |                                 |                                  |                     | SPH <sup>(1)</sup><br>0000 0000 |                   | BFh |

| B0h | P3<br>1111 1111                 | IE1<br>XX0X XXX0                 | IPL1<br>XX0X XXX0               | IPH1<br>XX0X XXX0               |                                  |                     |                                 | IPH0<br>X000 0000 | B7h |

| A8h | IE0<br>0000 0000                | SADDR<br>0000 0000               |                                 |                                 |                                  |                     |                                 |                   | AFh |

| A0h | P2<br>1111 1111                 |                                  |                                 |                                 |                                  |                     | WDTRST<br>1111 1111             | WCON<br>XXXX XX00 | A7h |

| 98h | SCON<br>0000 0000               | SBUF<br>XXXX XXXX                | BRL<br>0000 0000                | BDRCON<br>XXX0 0000             | P1LS<br>0000 0000                | P1IE<br>0000 0000   | P1F<br>0000 0000                |                   | 9Fh |

| 90h | P1<br>1111 1111                 |                                  | SSBR<br>0000 0000               | SSCON <sup>(2)</sup>            | SSCS <sup>(3)</sup>              | SSDAT<br>0000 0000  | SSADR<br>0000 0000              |                   | 97h |

| 88h | TCON<br>0000 0000               | TMOD<br>0000 0000                | TL0<br>0000 0000                | TL1<br>0000 0000                | TH0<br>0000 0000                 | TH1<br>0000 0000    | CKRL<br>0000 1000               | POWM<br>0XXX XXXX | 8Fh |

| 80h | P0<br>1111 1111                 | SP <sup>(1)</sup><br>0000 0111   | DPL <sup>(1)</sup><br>0000 0000 | DPH <sup>(1)</sup><br>0000 0000 | DPXL <sup>(1)</sup><br>0000 0001 |                     |                                 | PCON<br>0000 0000 | 87h |

|     | 0/8                             | 1/9                              | 2/A                             | 3/B                             | 4/C                              | 5/D                 | 6/E                             | 7/F               |     |

#### Reserved

Notes: 1. These registers are described in the TSC80251 Programmer's Guide (C251 core registers).

- 2. In TWI and SPI modes, SSCON is splitted in two separate registers. SSCON reset value is 0000 0000 in TWI mode and 0000 0100 in SPI mode.

- 3. In read and write modes, SSCS is splitted in two separate registers. SSCS reset value is 1111 1000 in read mode and 0000 0000 in write mode.

# **Configuration Bytes**

The TSC80251G2D derivatives provide user design flexibility by configuring certain operating features at device reset. These features fall into the following categories:

- external memory interface (Page mode, address bits, programmed wait states and the address range for RD#, WR#, and PSEN#)

- source mode/binary mode opcodes

- selection of bytes stored on the stack by an interrupt

- mapping of the upper portion of on-chip code memory to region 00:

Two user configuration bytes UCONFIG0 (see Table 11) and UCONFIG1 (see Table 12) provide the information.

When EA# is tied to a low level, the configuration bytes are fetched from the external address space. The TSC80251G2D derivatives reserve the top eight bytes of the memory address space (FF:FFF8h-FF:FFFh) for an external 8-byte configuration array. Only two bytes are actually used: UCONFIG0 at FF:FFF8h and UCONFIG1 at FF:FFF9h.

For the mask ROM devices, configuration information is stored in on-chip memory (see ROM Verifying). When EA# is tied to a high level, the configuration information is retrieved from the on-chip memory instead of the external address space and there is no restriction in the usage of the external memory.

|          | <dest>,</dest>            |                                                         | Binary | Mode             | Source Mode |                  |

|----------|---------------------------|---------------------------------------------------------|--------|------------------|-------------|------------------|

| Mnemonic | <src><sup>(2)</sup></src> | Comments                                                | Bytes  | States           | Bytes       | States           |

|          | Rmd, Rms                  | Register with register                                  | 3      | 2                | 2           | 1                |

|          | WRjd,<br>WRjs             | Word register with word register                        | 3      | 3                | 2           | 2                |

|          | DRkd,<br>DRks             | Dword register with dword register                      | 3      | 5                | 2           | 4                |

|          | Rm, #data                 | Register with immediate data                            | 4      | 3                | 3           | 2                |

|          | WRj,<br>#data16           | Word register with immediate 16-bit data                | 5      | 4                | 4           | 3                |

|          | DRk,<br>#0data16          | Dword register with zero-extended 16-bit immediate data | 5      | 6                | 4           | 5                |

| CMP      | DRk,<br>#1data16          | Dword register with one-extended 16-bit immediate data  | 5      | 6                | 4           | 5                |

|          | Rm, dir8                  | Direct address (on-chip RAM or SFR) with byte register  | 4      | 3 <sup>(1)</sup> | 3           | 2 <sup>(1)</sup> |

|          | WRj, dir8                 | Direct address (on-chip RAM or SFR) with word register  | 4      | 4                | 3           | 3                |

|          | Rm, dir16                 | Direct address (64K) with byte register                 | 5      | 3 <sup>(2)</sup> | 4           | 2 <sup>(2)</sup> |

|          | WRj, dir16                | Direct address (64K) with word register                 | 5      | 4 <sup>(3)</sup> | 4           | 3 <sup>(3)</sup> |

|          | Rm, at WRj                | Indirect address (64K) with byte register               | 4      | 3 <sup>(2)</sup> | 3           | 2 <sup>(2)</sup> |

|          | Rm, at DRk                | Indirect address (16M) with byte register               | 4      | 4 <sup>(2)</sup> | 3           | 3(2)             |

## Table 22. Summary of Compare Instructions

Notes: 1. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 2. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

- 3. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

- Notes: 1. Logical instructions that affect a bit are in Table 27.

- 2. A shaded cell denotes an instruction in the C51 Architecture.

- 3. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 4. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

- 5. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

- 6. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

| Table 23. | Summar | of Logical | Instructions | (2/2) |

|-----------|--------|------------|--------------|-------|

|           |        |            |              |       |

| $      Shift Left LogicalSLL _{0} \leftarrow 0  _{n+1} \leftarrow _{n}, n = 0msb-1  (CY) \leftarrow _{msb} \\       Shift Right ArithmeticSRA _{msb} \leftarrow _{msb} \\ _{n-1} \leftarrow _{n}, n = msb1  (CY) \leftarrow _{0} \\       Shift Right LogicalSRL _{msb} \leftarrow 0 \\ _{n-1} \leftarrow _{n}, n = msb1 \\ (CY) \leftarrow _{0} \\       SwapSWAP AA_{3:0} A_{7:4} \\                                   $ |                                              |                                          |       |        |       |        |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------|-------|--------|-------|--------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                            | Binary Mode Source Mode                      |                                          |       |        |       |        |  |  |

| Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                   | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                 | Bytes | States | Bytes | States |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                            | Rm                                           | Shift byte register left through the MSB | 3     | 2      | 2     | 1      |  |  |

| SLL                                                                                                                                                                                                                                                                                                                                                                                                                        | WRj                                          | Shift word register left through the MSB | 3     | 2      | 2     | 1      |  |  |

| SRA                                                                                                                                                                                                                                                                                                                                                                                                                        | Rm                                           | Shift byte register right                | 3     | 2      | 2     | 1      |  |  |

| SKA                                                                                                                                                                                                                                                                                                                                                                                                                        | WRj                                          | Shift word register right                | 3     | 2      | 2     | 1      |  |  |

| SRL                                                                                                                                                                                                                                                                                                                                                                                                                        | Rm                                           | Shift byte register left                 | 3     | 2      | 2     | 1      |  |  |

| JRL                                                                                                                                                                                                                                                                                                                                                                                                                        | WRj                                          | Shift word register left                 | 3     | 2      | 2     | 1      |  |  |

| SWAP                                                                                                                                                                                                                                                                                                                                                                                                                       | А                                            | Swap nibbles within ACC                  | 1     | 2      | 1     | 2      |  |  |

Note: 1. A shaded cell denotes an instruction in the C51 Architecture.

| Binary Mode Source Mode |                                              |                                                    |       |                  |       |                  |  |  |  |

|-------------------------|----------------------------------------------|----------------------------------------------------|-------|------------------|-------|------------------|--|--|--|

| Mnemonic                | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                           | Bytes | States           | Bytes | State            |  |  |  |

|                         | A, Rn                                        | ACC and register                                   | 1     | 3                | 2     | 4                |  |  |  |

| ХСН                     | A, dir8                                      | ACC and direct address (on-chip RAM or SFR)        | 2     | 3 <sup>(3)</sup> | 2     | 3 <sup>(3)</sup> |  |  |  |

|                         | A, at Ri                                     | ACC and indirect address                           | 1     | 4                | 2     | 5                |  |  |  |

| XCHD                    | A, at Ri                                     | ACC low nibble and indirect address (256 bytes)    | 1     | 4                | 2     | 5                |  |  |  |

|                         | dir8                                         | Push direct address onto stack                     | 2     | 2 <sup>(2)</sup> | 2     | 2(2              |  |  |  |

|                         | #data                                        | Push immediate data onto stack                     | 4     | 4                | 3     | 3                |  |  |  |

| PUSH                    | #data16                                      | Push 16-bit immediate data onto stack              | 5     | 5                | 4     | 5                |  |  |  |

| F 0311                  | Rm                                           | Push byte register onto stack                      | 3     | 4                | 2     | 3                |  |  |  |

|                         | WRj                                          | Push word register onto stack                      | 3     | 5                | 2     | 4                |  |  |  |

|                         | DRk                                          | Push double word register onto stack               | 3     | 9                | 2     | 8                |  |  |  |

|                         | dir8                                         | Pop direct address (on-chip RAM or SFR) from stack | 2     | 3 <sup>(2)</sup> | 2     | 3(2              |  |  |  |

| POP                     | Rm                                           | Pop byte register from stack                       | 3     | 3                | 2     | 2                |  |  |  |

|                         | WRj                                          | Pop word register from stack                       | 3     | 5                | 2     | 4                |  |  |  |

|                         | DRk                                          | Pop double word register from stack                | 3     | 9                | 2     | 8                |  |  |  |

## Table 28. Summary of Exchange, Push and Pop Instructions

Exchange bytesXCH A, <src>(A)  $\leftrightarrow$  src opnd

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

3. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

#### Lock Bit System

The TSC87251G2D products implement 3 levels of security for User's program as described in Table 33. The TSC83251G2D products implement only the first level of security.

Level 0 is the level of an erased part and does not enable any security features.

Level 1 locks the programming of the User's internal Code Memory, the Configuration Bytes and the Encryption Array.

Level 2 locks the verifying of the User's internal Code Memory. It is always possible to verify the Configuration Bytes and the Lock Bits. It is not possible to verify the Encryption Array.

Level 3 locks the external execution.

| Level | Lock bits<br>LB[2:0] | Internal<br>Execution | External<br>Execution | Verification          | Programming | External<br>PROM read<br>(MOVC) |

|-------|----------------------|-----------------------|-----------------------|-----------------------|-------------|---------------------------------|

| 0     | 000                  | Enable                | Enable                | Enable <sup>(1)</sup> | Enable      | Enable <sup>(2)</sup>           |

| 1     | 001                  | Enable                | Enable                | Enable <sup>(1)</sup> | Disable     | Disable                         |

| 2     | 01x <sup>(3)</sup>   | Enable                | Enable                | Disable               | Disable     | Disable                         |

| 3     | 1xx <sup>(3)</sup>   | Enable                | Disable               | Disable               | Disable     | Disable                         |

Table 33. Lock Bits Programming

Notes: 1. Returns encrypted data if Encryption Array is programmed.

2. Returns non encrypted data.

3. x means don't care. Level 2 always enables level 1, and level 3 always enables levels 1 and 2.

The security level may be verified according to Table 34.

#### Table 34. Lock Bits Verifying

| Level | Lock bits Data <sup>(1)</sup> |  |  |

|-------|-------------------------------|--|--|

| 0     | xxxxx000                      |  |  |

| 1     | xxxxx001                      |  |  |

| 2     | xxxxx01x                      |  |  |

| 3     | xxxxx1xx                      |  |  |

Note: 1. x means don't care.

#### **Encryption Array**

The TSC83251G2D and TSC87251G2D products include a 128-byte Encryption Array located in non-volatile memory outside the memory address space. During verification of the on-chip code memory, the seven low-order address bits also address the Encryption Array. As the byte of the code memory is read, it is exclusive-NOR'ed (XNOR) with the key byte from the Encryption Array. If the Encryption Array is not programmed (still all 1s), the user program code is placed on the data bus in its original, unencrypted form. If the Encryption Array is programmed with key bytes, the user program code is encrypted and cannot be used without knowledge of the key byte sequence.

# **AC Characteristics - SSLC: SPI Interface**

## Definition of Symbols

#### Table 48. SPI Interface Timing Symbol Definitions

| Signals |          |  |  |  |

|---------|----------|--|--|--|

| С       | Clock    |  |  |  |

| I       | Data In  |  |  |  |

| 0       | Data Out |  |  |  |

| S       | SS#      |  |  |  |

|       | Conditions      |  |  |  |  |

|-------|-----------------|--|--|--|--|

| Н     | High            |  |  |  |  |

| L Low |                 |  |  |  |  |

| V     | Valid           |  |  |  |  |

| Х     | No Longer Valid |  |  |  |  |

| Z     | Floating        |  |  |  |  |

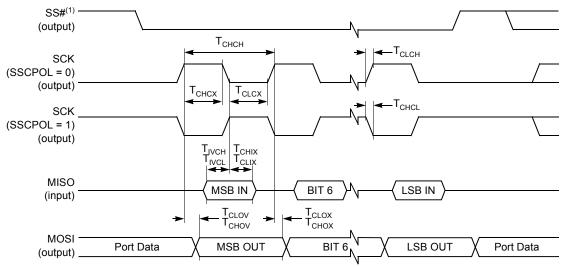

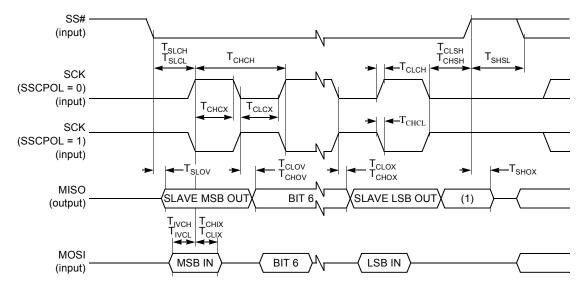

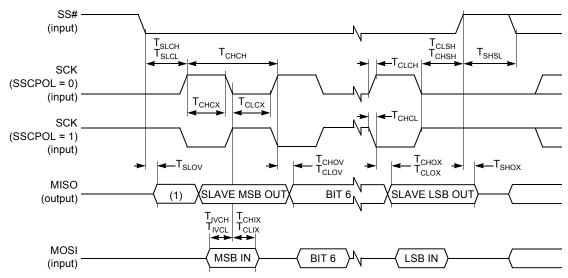

### Timings

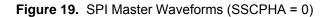

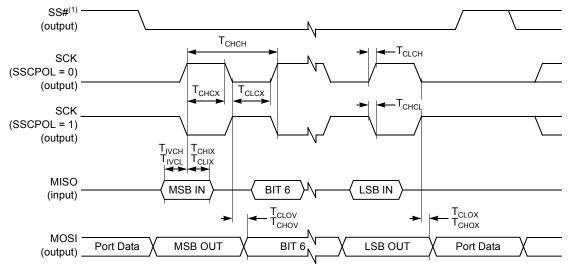

# **Table 49.** SPI Interface AC Timing; $V_{DD}$ = 2.7 to 5.5 V, $T_A$ = -40 to 85°C

| Symbol                                | Parameter                              | Min | Max | Unit             |

|---------------------------------------|----------------------------------------|-----|-----|------------------|

|                                       | Slave Mode <sup>(1</sup>               | )   |     | 1                |

| Тснсн                                 | Clock Period                           | 8   |     | T <sub>OSC</sub> |

| T <sub>CHCX</sub>                     | Clock High Time                        | 3.2 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 3.2 |     | T <sub>osc</sub> |

| T <sub>SLCH</sub> , T <sub>SLCL</sub> | SS# Low to Clock edge                  | 200 |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 100 | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>CLSH</sub> , T <sub>CHSH</sub> | SS# High after Clock Edge              | 0   |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>SLOV</sub>                     | SS# Low to Output Data Valid           |     | 130 | ns               |

| Т <sub>знох</sub>                     | Output Data Hold after SS# High        |     | 130 | ns               |

| T <sub>SHSL</sub>                     | SS# High to SS# Low                    | (2) |     |                  |

| T <sub>ILIH</sub>                     | Input Rise Time                        |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Fall Time                        |     | 2   | μs               |

| Т <sub>огон</sub>                     | Output Rise time                       |     | 100 | ns               |

| Т <sub>ОНОL</sub>                     | Output Fall Time                       |     | 100 | ns               |

|                                       | Master Mode                            | (3) |     |                  |

| Тснсн                                 | Clock Period                           | 4   |     | T <sub>osc</sub> |

| Т <sub>снсх</sub>                     | Clock High Time                        | 1.6 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 1.6 |     | T <sub>osc</sub> |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 50  |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 50  |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 65  | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>ILIH</sub>                     | Input Data Rise Time                   |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Data Fall Time                   |     | 2   | μs               |

| Т <sub>оloн</sub>                     | Output Data Rise time                  |     | 50  | ns               |

| Т <sub>оноь</sub>                     | Output Data Fall Time                  |     | 50  | ns               |

Notes: 1. Capacitive load on all pins = 200 pF in slave mode.

2. The value of this parameter depends on software.

3. Capacitive load on all pins = 100 pF in master mode.

Note: 1. SS# handled by software.

Note: 1. Not Defined but normally MSB of character just received.

## Figure 21. SPI Slave Waveforms (SSCPHA = 0)

Note: 1. Not Defined but generally the LSB of the character which has just been received.

#### Figure 22. SPI Slave Waveforms (SSCPHA = 1)

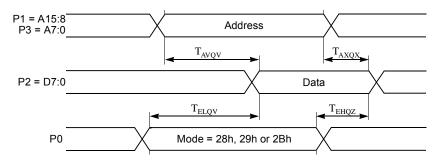

# **AC Characteristics - EPROM Programming and Verifying**

## **Definition of Symbols**

Table 50. EPROM Programming and Verifying Timing Symbol Definitions

| Signals   |                            |  |  |  |

|-----------|----------------------------|--|--|--|

| A Address |                            |  |  |  |

| E         | Enable: mode set on Port 0 |  |  |  |

| G         | G Program                  |  |  |  |

| Q         | Data Out                   |  |  |  |

| S         | Supply (V <sub>PP</sub> )  |  |  |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| н          | High            |  |  |  |

| L          | Low             |  |  |  |

| V          | Valid           |  |  |  |

| Х          | No Longer Valid |  |  |  |

| Z          | Floating        |  |  |  |

# 58 AT/TSC8x251G2D

4135F-8051-11/06

### Figure 24. EPROM Verifying Waveforms

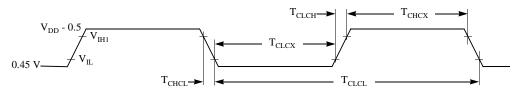

# AC Characteristics - External Clock Drive and Logic Level References

**Definition of Symbols**

Table 53. External Clock Timing Symbol Definitions

| Signals |       |  |

|---------|-------|--|

| С       | Clock |  |

|         |       |  |

|         |       |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| H High     |                 |  |  |  |

| L Low      |                 |  |  |  |

| Х          | No Longer Valid |  |  |  |

#### Timings

# **Table 54.** External Clock AC Timings; $V_{DD}$ = 4.5 to 5.5 V, $T_A$ = -40 to +85°C

| Symbol            | Parameter            | Min | Max | Unit |

|-------------------|----------------------|-----|-----|------|

| F <sub>osc</sub>  | Oscillator Frequency |     | 24  | MHz  |

| T <sub>CHCX</sub> | High Time            | 10  |     | ns   |

| T <sub>CLCX</sub> | Low Time             | 10  |     | ns   |

| T <sub>CLCH</sub> | Rise Time            | 3   |     | ns   |

| T <sub>CHCL</sub> | Fall Time            | 3   |     | ns   |

## Waveforms

Figure 25. External Clock Waveform

- Notes: 1. During AC testing, all inputs are driven at  $V_{DD}$  -0.5 V for a logic 1 and 0.45 V for a logic 0.

- 2. Timing measurements are made on all outputs at  $V_{\rm IH}$  min for a logic 1 and  $V_{\rm IL}$  max for a logic 0.

# **DC Characteristics**

# High Speed Versions - Commercial, Industrial, and Automotive

| Symbol           | Parameter                                                                                   | Min                                                                     | Typical <sup>(4)</sup> | Max                       | Units | Test Conditions                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------|---------------------------|-------|--------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage<br>(except EA#, SCL, SDA)                                                 | -0.5                                                                    |                        | 0.2·V <sub>DD</sub> - 0.1 | V     |                                                                                                                          |

| $V_{IL1}^{(5)}$  | Input Low Voltage<br>(SCL, SDA)                                                             | -0.5                                                                    |                        | 0.3·V <sub>DD</sub>       | V     |                                                                                                                          |

| $V_{\text{IL2}}$ | Input Low Voltage<br>(EA#)                                                                  | 0                                                                       |                        | 0.2·V <sub>DD</sub> - 0.3 | V     |                                                                                                                          |

| V <sub>IH</sub>  | Input high Voltage<br>(except XTAL1, RST, SCL, SDA)                                         | 0.2·V <sub>DD</sub> + 0.9                                               |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                          |

| $V_{IH1}^{(5)}$  | Input high Voltage<br>(XTAL1, RST, SCL, SDA)                                                | 0.7·V <sub>DD</sub>                                                     |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                          |

| V <sub>OL</sub>  | Output Low Voltage<br>(Ports 1, 2, 3)                                                       |                                                                         |                        | 0.3<br>0.45<br>1.0        | V     | $I_{OL} = 100 \ \mu A^{(1)(2)}$ $I_{OL} = 1.6 \ m A^{(1)(2)}$ $I_{OL} = 3.5 \ m A^{(1)(2)}$                              |

| V <sub>OL1</sub> | Output Low Voltage<br>(Ports 0, ALE, PSEN#, Port 2 in Page Mode during<br>External Address) |                                                                         |                        | 0.3<br>0.45<br>1.0        | V     | $I_{OL} = 200 \ \mu A^{(1)(2)}$ $I_{OL} = 3.2 \ m A^{(1)(2)}$ $I_{OL} = 7.0 \ m A^{(1)(2)}$                              |

| V <sub>OH</sub>  | Output high Voltage<br>(Ports 1, 2, 3, ALE, PSEN#)                                          | V <sub>DD</sub> - 0.3<br>V <sub>DD</sub> - 0.7<br>V <sub>DD</sub> - 1.5 |                        |                           | V     | $\begin{split} I_{OH} &= -10 \; \mu A^{(3)} \\ I_{OH} &= -30 \; \mu A^{(3)} \\ I_{OH} &= -60 \; \mu A^{(3)} \end{split}$ |

| V <sub>OH1</sub> | Output high Voltage<br>(Port 0, Port 2 in Page Mode during External Address)                | V <sub>DD</sub> - 0.3<br>V <sub>DD</sub> - 0.7<br>V <sub>DD</sub> - 1.5 |                        |                           | V     | I <sub>OH</sub> = -200 μA<br>I <sub>OH</sub> = -3.2 mA<br>I <sub>OH</sub> = -7.0 mA                                      |

| $V_{RET}$        | V <sub>DD</sub> data retention limit                                                        |                                                                         |                        | 1.8                       | V     |                                                                                                                          |

| I <sub>IL0</sub> | Logical 0 Input Current<br>(Ports 1, 2, 3)                                                  |                                                                         |                        | - 50                      | μA    | V <sub>IN</sub> = 0.45 V                                                                                                 |

| I <sub>IL1</sub> | Logical 1 Input Current<br>(NMI)                                                            |                                                                         |                        | + 50                      | μA    | V <sub>IN</sub> = V <sub>DD</sub>                                                                                        |

| I <sub>LI</sub>  | Input Leakage Current<br>(Port 0)                                                           |                                                                         |                        | ± 10                      | μA    | 0.45 V < V <sub>IN</sub> < V <sub>DD</sub>                                                                               |

| I <sub>TL</sub>  | Logical 1-to-0 Transition Current<br>(Ports 1, 2, 3 - AWAIT#)                               |                                                                         |                        | - 650                     | μA    | V <sub>IN</sub> = 2.0 V                                                                                                  |

| R <sub>RST</sub> | RST Pull-Down Resistor                                                                      | 40                                                                      | 110                    | 225                       | kΩ    |                                                                                                                          |

| CIO              | Pin Capacitance                                                                             |                                                                         | 10                     |                           | pF    | T <sub>A</sub> = 25°C                                                                                                    |

| I <sub>DD</sub>  | Operating Current                                                                           |                                                                         | 20<br>25<br>35         | 25<br>30<br>40            | mA    | $F_{OSC}$ = 12 MHz<br>$F_{OSC}$ = 16 MHz<br>$F_{OSC}$ = 24 MHz                                                           |

| I <sub>DL</sub>  | Idle Mode Current                                                                           |                                                                         | 5<br>6.5<br>9.5        | 8<br>10<br>14             | mA    | $F_{OSC}$ = 12 MHz<br>$F_{OSC}$ = 16 MHz<br>$F_{OSC}$ = 24 MHz                                                           |

| I <sub>PD</sub>  | Power-Down Current                                                                          |                                                                         | 2                      | 20                        | μA    | $V_{RET} < V_{DD} < 5.5 V$                                                                                               |

| $V_{PP}$         | Programming supply voltage                                                                  | 12.5                                                                    |                        | 13                        | V     | $T_A = 0$ to +40°C                                                                                                       |

| I <sub>PP</sub>  | Programming supply current                                                                  | 1                                                                       |                        | 75                        | mA    | T <sub>A</sub> = 0 to +40°C                                                                                              |

# Low Voltage Versions - Commercial & Industrial

| Table 56. | DC Characteristics; | V <sub>DD</sub> = 2.7 to | 5.5 V, T <sub>A</sub> | = -40 to +85°C |

|-----------|---------------------|--------------------------|-----------------------|----------------|

|-----------|---------------------|--------------------------|-----------------------|----------------|

| Symbol              | Parameter                                                                                   | Min                       | Typical <sup>(4)</sup> | Max                       | Units | Test Conditions                                                                                                                                                                                                                                                |

|---------------------|---------------------------------------------------------------------------------------------|---------------------------|------------------------|---------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>     | Input Low Voltage<br>(except EA#, SCL, SDA)                                                 | -0.5                      |                        | 0.2·V <sub>DD</sub> - 0.1 | V     |                                                                                                                                                                                                                                                                |

| $V_{IL1}^{(5)}$     | Input Low Voltage<br>(SCL, SDA)                                                             | -0.5                      |                        | 0.3·V <sub>DD</sub>       | v     |                                                                                                                                                                                                                                                                |

| V <sub>IL2</sub>    | Input Low Voltage<br>(EA#)                                                                  | 0                         |                        | 0.2·V <sub>DD</sub> - 0.3 | V     |                                                                                                                                                                                                                                                                |

| V <sub>IH</sub>     | Input high Voltage<br>(except XTAL1, RST, SCL, SDA)                                         | 0.2·V <sub>DD</sub> + 0.9 |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                                                                                                                                                                |

| $V_{\rm IH1}^{(5)}$ | Input high Voltage<br>(XTAL1, RST, SCL, SDA)                                                | 0.7·V <sub>DD</sub>       |                        | V <sub>DD</sub> + 0.5     | v     |                                                                                                                                                                                                                                                                |

| V <sub>OL</sub>     | Output Low Voltage<br>(Ports 1, 2, 3)                                                       |                           |                        | 0.45                      | v     | $I_{OL} = 0.8 \text{ mA}^{(1)(2)}$                                                                                                                                                                                                                             |

| V <sub>OL1</sub>    | Output Low Voltage<br>(Ports 0, ALE, PSEN#, Port 2 in Page<br>Mode during External Address) |                           |                        | 0.45                      | v     | $I_{OL} = 1.6 \text{ mA}^{(1)(2)}$                                                                                                                                                                                                                             |

| V <sub>OH</sub>     | Output high Voltage<br>(Ports 1, 2, 3, ALE, PSEN#)                                          | 0.9·V <sub>DD</sub>       |                        |                           | v     | I <sub>OH</sub> = -10 μA <sup>(3)</sup>                                                                                                                                                                                                                        |

| V <sub>OH1</sub>    | Output high Voltage<br>(Port 0, Port 2 in Page Mode during<br>External Address)             | 0.9·V <sub>DD</sub>       |                        |                           | v     | I <sub>OH</sub> = -40 μA                                                                                                                                                                                                                                       |

| V <sub>RET</sub>    | V <sub>DD</sub> data retention limit                                                        |                           |                        | 1.8                       | V     |                                                                                                                                                                                                                                                                |

| I <sub>ILO</sub>    | Logical 0 Input Current<br>(Ports 1, 2, 3 - AWAIT#)                                         |                           |                        | - 50                      | μΑ    | V <sub>IN</sub> = 0.45 V                                                                                                                                                                                                                                       |

| I <sub>IL1</sub>    | Logical 1 Input Current<br>(NMI)                                                            |                           |                        | + 50                      | μA    | V <sub>IN</sub> = V <sub>DD</sub>                                                                                                                                                                                                                              |

| I <sub>LI</sub>     | Input Leakage Current<br>(Port 0)                                                           |                           |                        | ± 10                      | μA    | 0.45 V < V <sub>IN</sub> < V <sub>DD</sub>                                                                                                                                                                                                                     |

| I <sub>TL</sub>     | Logical 1-to-0 Transition Current<br>(Ports 1, 2, 3)                                        |                           |                        | - 650                     | μA    | V <sub>IN</sub> = 2.0 V                                                                                                                                                                                                                                        |

| R <sub>RST</sub>    | RST Pull-Down Resistor                                                                      | 40                        | 110                    | 225                       | kΩ    |                                                                                                                                                                                                                                                                |

| C <sub>IO</sub>     | Pin Capacitance                                                                             |                           | 10                     |                           | pF    | T <sub>A</sub> = 25°C                                                                                                                                                                                                                                          |

| I <sub>DD</sub>     | Operating Current                                                                           |                           | 4<br>8<br>9<br>11      | 8<br>11<br>12<br>14       | mA    | $\begin{array}{c} 5 \text{ MHz, } \text{V}_{\text{DD}} < 3.6 \text{ V} \\ 10 \text{ MHz, } \text{V}_{\text{DD}} < 3.6 \text{ V} \\ 12 \text{ MHz, } \text{V}_{\text{DD}} < 3.6 \text{ V} \\ 16 \text{ MHz, } \text{V}_{\text{DD}} < 3.6 \text{ V} \end{array}$ |

| I <sub>DL</sub>     | Idle Mode Current                                                                           |                           | 0.5<br>1.5<br>2<br>3   | 1<br>4<br>5<br>7          | mA    | $\begin{array}{c} 5 \mbox{ MHz, } V_{\rm DD} < 3.6 \mbox{ V} \\ 10 \mbox{ MHz, } V_{\rm DD} < 3.6 \mbox{ V} \\ 12 \mbox{ MHz, } V_{\rm DD} < 3.6 \mbox{ V} \\ 16 \mbox{ MHz, } V_{\rm DD} < 3.6 \mbox{ V} \end{array}$                                         |

| I <sub>PD</sub>     | Power-Down Current                                                                          |                           | 1                      | 10                        | μA    | V <sub>RET</sub> < V <sub>DD</sub> < 3.6 V                                                                                                                                                                                                                     |

Notes: 1. Under steady-state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum IOL per port pin: 10 mA

Maximum IOL per 8-bit port: Port 0 26 mA

Ports 1-315 mA

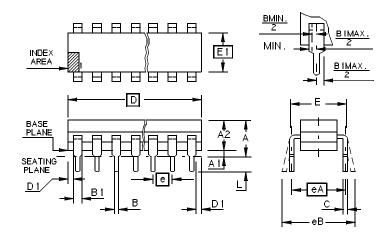

# Packages

List of Packages

- PDIL 40

- CDIL 40 with window

- PLCC 44

- CQPJ 44 with window

- VQFP 44 (10x10)

# PDIL 40 - Mechanical Outline

Figure 33. Plastic Dual In Line

## Table 57. PDIL Package Size

| MM Inch |              |       |             |       |  |

|---------|--------------|-------|-------------|-------|--|

|         | M            | м     | Inch        |       |  |

|         | Min          | Мах   | Min         | Мах   |  |

| А       | -            | 5.08  | -           | .200  |  |

| A1      | 0.38         | -     | .015        | -     |  |

| A2      | 3.18         | 4.95  | .125        | .195  |  |

| В       | 0.36         | 0.56  | .014        | .022  |  |

| B1      | 0.76         | 1.78  | .030        | .070  |  |

| С       | 0.20         | 0.38  | .008        | .015  |  |

| D       | 50.29        | 53.21 | 1.980       | 2.095 |  |

| E       | 15.24        | 15.87 | .600        | .625  |  |

| E1      | 12.32        | 14.73 | .485        | .580  |  |

| е       | 2.54 B.S.C.  |       | .100 B.S.C. |       |  |

| eA      | 15.24 B.S.C. |       | .600 B.S.C. |       |  |

| eB      | -            | 17.78 | -           | .700  |  |

| L       | 2.93         | 3.81  | .115        | .150  |  |

| D1      | 0.13         | -     | .005        | -     |  |

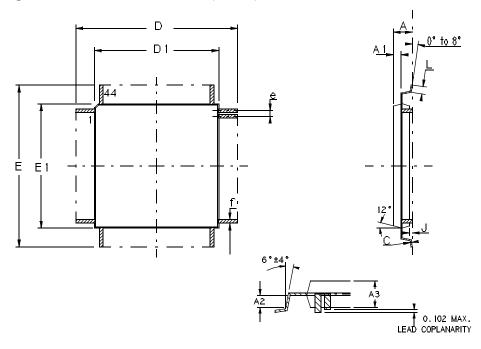

# VQFP 44 (10x10) -Mechanical Outline

Figure 37. Shrink Quad Flat Pack (Plastic)

| Table 61. | VQFP | Package Size |

|-----------|------|--------------|

|-----------|------|--------------|

|    | М        | М     | Inch      |      |  |

|----|----------|-------|-----------|------|--|

|    | Min      | Мах   | Min       | Max  |  |

| A  | -        | 1.60  | -         | .063 |  |

| A1 | 0.64 REF |       | .025 REF  |      |  |

| A2 | 0.64 REF |       | .025REF   |      |  |

| A3 | 1.35     | 1.45  | .053      | .057 |  |

| D  | 11.90    | 12.10 | .468      | .476 |  |

| D1 | 9.90     | 10.10 | .390      | .398 |  |

| E  | 11.90    | 12.10 | .468      | .476 |  |

| E1 | 9.90     | 10.10 | .390      | .398 |  |

| J  | 0.05     | -     | .002      | 6    |  |

| L  | 0.45     | 0.75  | .018      | .030 |  |

| е  | 0.80 BSC |       | .0315 BSC |      |  |

| f  | 0.35 BSC |       | .014 BSC  |      |  |

# **Ordering Information**

# AT/TSC80251G2D ROMIess

| Part Number                                                 | ROM     | Description                                      |  |  |  |

|-------------------------------------------------------------|---------|--------------------------------------------------|--|--|--|

| High Speed Versions 4.5 to 5.5 V, Commercial and Industrial |         |                                                  |  |  |  |

| TSC80251G2D-16CB                                            | ROMless | 16 MHz, Commercial 0° to 70°C, PLCC 44           |  |  |  |

| TSC80251G2D-24CB                                            | ROMless | 24 MHz, Commercial 0° to 70°C, PLCC 44           |  |  |  |

| TSC80251G2D-24CE                                            | ROMless | 24 MHz, Commercial 0° to 70°C, VQFP 44           |  |  |  |

| TSC80251G2D-24IA                                            | ROMless | 24 MHz, Industrial -40° to 85°C, PDIL 40         |  |  |  |

| TSC80251G2D-24IB                                            | ROMless | 24 MHz, Industrial -40° to 85°C, PLCC 44         |  |  |  |

| AT80251G2D-SLSUM                                            | ROMless | 24 MHz, Industrial & Green -40° to 85°C, PLCC 44 |  |  |  |

| AT80251G2D-3CSUM                                            | ROMless | 24 MHz, Industrial & Green -40° to 85°C, PDIL 40 |  |  |  |

| AT80251G2D-RLTUM                                            | ROMless | 24 MHz, Industrial & Green -40° to 85°C, VQFP 44 |  |  |  |

| Low Voltage Versions 2.7 to 5.5 V                           |         |                                                  |  |  |  |

| TSC80251G2D-L16CB                                           | ROMless | 16 MHz, Commercial, PLCC 44                      |  |  |  |

| TSC80251G2D-L16CE                                           | ROMless | 16 MHz, Commercial, VQFP 44                      |  |  |  |

| AT80251G2D-SLSUL                                            | ROMless | 16 MHz, Industrial & Green, PLCC 44              |  |  |  |

| AT80251G2D-RLTUL                                            | ROMless | 16 MHz, Industrial & Green, VQFP 44              |  |  |  |

# AT/TSC83251G2D 32 kilobytes MaskROM

| Part Number <sup>(1)</sup>                                  | ROM         | Description                                      |  |  |

|-------------------------------------------------------------|-------------|--------------------------------------------------|--|--|

| High Speed Versions 4.5 to 5.5 V, Commercial and Industrial |             |                                                  |  |  |

| TSC251G2Dxxx-16CB                                           | 32K MaskROM | 16 MHz, Commercial 0° to 70°C, PLCC 44           |  |  |

| TSC251G2Dxxx-24CB                                           | 32K MaskROM | 24 MHz, Commercial 0° to 70°C, PLCC 44           |  |  |

| TSC251G2Dxxx-24CE                                           | 32K MaskROM | 24 MHz, Commercial 0° to 70°C, VQFP 44           |  |  |

| TSC251G2Dxxx-24IA                                           | 32K MaskROM | 24 MHz, Industrial -40° to 85°C, PDIL 40         |  |  |

| TSC251G2Dxxx-24IB                                           | 32K MaskROM | 24 MHz, Industrial -40° to 85°C, PLCC 44         |  |  |

| AT251G2Dxxx-SLSUM                                           | 32K MaskROM | 24 MHz, Industrial & Green -40° to 85°C, PLCC 44 |  |  |

| AT251G2Dxxx-3CSUM                                           | 32K MaskROM | 24 MHz, Industrial & Green -40° to 85°C, PDIL 40 |  |  |

| AT251G2Dxxx-RLTUM                                           | 32K MaskROM | 24 MHz, Industrial & Green -40° to 85°C, VQFP 44 |  |  |

| AT251G2Dxxx-SLSTM                                           | 32K MaskROM | 24 MHz, Automotive & Green -40° to 85°C, PLCC 44 |  |  |