#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | C251                                                                       |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 24MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, Microwire, SPI, UART/USART                      |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | -                                                                          |

| Supplier Device Package    | 44-CQPJ                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/tsc87251g2d-24ic |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Signals

#### Table 2. Product Name Signal Description

| Table 2.             | 2. Product Name Signal Description |                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |

|----------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Signal<br>Name       | Туре                               | Description                                                                                                                                                                                                                                                                                                                                                                                                          | Alternate<br>Function |

| A17                  | 0                                  | <b>18<sup>th</sup> Address Bit</b><br>Output to memory as 18th external address bit (A17) in extended bus<br>applications, depending on the values of bits RD0 and RD1 in UCONFIG0<br>byte (see Table 13, Page 20).                                                                                                                                                                                                  | P1.7                  |

| A16                  | 0                                  | <b>17<sup>th</sup> Address Bit</b><br>Output to memory as 17th external address bit (A16) in extended bus<br>applications, depending on the values of bits RD0 and RD1 in UCONFIG0<br>byte (see Table 13, Page 20).                                                                                                                                                                                                  | P3.7                  |

| A15:8 <sup>(1)</sup> | 0                                  | Address Lines<br>Upper address lines for the external bus.                                                                                                                                                                                                                                                                                                                                                           | P2.7:0                |

| AD7:0 <sup>(1)</sup> | I/O                                | Address/Data Lines<br>Multiplexed lower address lines and data for the external memory.                                                                                                                                                                                                                                                                                                                              | P0.7:0                |

| ALE                  | 0                                  | Address Latch Enable<br>ALE signals the start of an external bus cycle and indicates that valid<br>address information are available on lines A16/A17 and A7:0. An external<br>latch can use ALE to demultiplex the address from address/data bus.                                                                                                                                                                   | -                     |

| AWAIT#               | I                                  | <b>Real-time Asynchronous Wait States Input</b><br>When this pin is active (low level), the memory cycle is stretched until it<br>becomes high. When using the Product Name as a pin-for-pin replacement<br>for a 8xC51 product, AWAIT# can be unconnected without loss of<br>compatibility or power consumption increase (on-chip pull-up).<br>Not available on DIP package.                                        | _                     |

| CEX4:0               | I/O                                | <b>PCA Input/Output pins</b><br>CEXx are input signals for the PCA capture mode and output signals for<br>the PCA compare and PWM modes.                                                                                                                                                                                                                                                                             | P1.7:3                |

| EA#                  | I                                  | <b>External Access Enable</b><br>EA# directs program memory accesses to on-chip or off-chip code memory.<br>For EA# = 0, all program memory accesses are off-chip.<br>For EA# = 1, an access is on-chip ROM if the address is within the range of<br>the on-chip ROM; otherwise the access is off-chip. The value of EA# is<br>latched at reset.<br>For devices without ROM on-chip, EA# must be strapped to ground. | _                     |

| ECI                  | 0                                  | PCA External Clock input<br>ECI is the external clock input to the 16-bit PCA timer.                                                                                                                                                                                                                                                                                                                                 | P1.2                  |

| MISO                 | I/O                                | SPI Master Input Slave Output line<br>When SPI is in master mode, MISO receives data from the slave<br>peripheral. When SPI is in slave mode, MISO outputs data to the master<br>controller.                                                                                                                                                                                                                         | P1.5                  |

| MOSI                 | I/O                                | SPI Master Output Slave Input line<br>When SPI is in master mode, MOSI outputs data to the slave peripheral.<br>When SPI is in slave mode, MOSI receives data from the master controller.                                                                                                                                                                                                                            | P1.7                  |

| INT1:0#              | I                                  | <b>External Interrupts 0 and 1</b><br>INT1#/INT0# inputs set IE1:0 in the TCON register. If bits IT1:0 in the<br>TCON register are set, bits IE1:0 are set by a falling edge on INT1#/INT0#.<br>If bits IT1:0 are cleared, bits IE1:0 are set by a low level on INT1#/INT0#.                                                                                                                                         | P3.3:2                |

| Table 2.         Product Name Signal Description (Continued) |      |                                                                                                                                                                                                                                                                                                                                                          |                       |

|--------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Signal<br>Name                                               | Туре | Description                                                                                                                                                                                                                                                                                                                                              | Alternate<br>Function |

| T1:0                                                         | I/O  | <b>Timer 1:0 External Clock Inputs</b><br>When timer 1:0 operates as a counter, a falling edge on the T1:0 pin increments the count.                                                                                                                                                                                                                     | -                     |

| T2                                                           | I/O  | <b>Timer 2 Clock Input/Output</b><br>For the timer 2 capture mode, T2 is the external clock input. For the Timer 2 clock-out mode, T2 is the clock output.                                                                                                                                                                                               | P1.0                  |

| T2EX                                                         | I    | <b>Timer 2 External Input</b><br>In timer 2 capture mode, a falling edge initiates a capture of the timer 2<br>registers. In auto-reload mode, a falling edge causes the timer 2 register to<br>be reloaded. In the up-down counter mode, this signal determines the<br>count direction: 1 = up, 0 = down.                                               | P1.1                  |

| тхр                                                          | 0    | <b>Transmit Serial Data</b><br>TXD outputs the shift clock in serial I/O mode 0 and transmits data in serial<br>I/O modes 1, 2 and 3.                                                                                                                                                                                                                    | P3.1                  |

| VDD                                                          | PWR  | <b>Digital Supply Voltage</b><br>Connect this pin to +5V or +3V supply voltage.                                                                                                                                                                                                                                                                          | -                     |

| VPP                                                          | I    | <b>Programming Supply Voltage</b><br>The programming supply voltage is applied to this input for programming<br>the on-chip EPROM/OTPROM.                                                                                                                                                                                                                | -                     |

| VSS                                                          | GND  | Circuit Ground<br>Connect this pin to ground.                                                                                                                                                                                                                                                                                                            | -                     |

| VSS1                                                         | GND  | Secondary Ground 1<br>This ground is provided to reduce ground bounce and improve power<br>supply bypassing. Connection of this pin to ground is recommended.<br>However, when using the TSC80251G2D as a pin-for-pin replacement for a<br>8xC51 product, VSS1 can be unconnected without loss of compatibility.<br>Not available on DIP package.        | Ι                     |

| VSS2                                                         | GND  | <b>Secondary Ground 2</b><br>This ground is provided to reduce ground bounce and improve power<br>supply bypassing. Connection of this pin to ground is recommended.<br>However, when using the TSC80251G2D as a pin-for-pin replacement for a<br>8xC51 product, VSS2 can be unconnected without loss of compatibility.<br>Not available on DIP package. | _                     |

| WAIT#                                                        | I    | <b>Real-time Synchronous Wait States Input</b><br>The real-time WAIT# input is enabled by setting RTWE bit in WCON<br>(S:A7h). During bus cycles, the external memory system can signal<br>'system ready' to the microcontroller in real time by controlling the WAIT#<br>input signal.                                                                  | P1.6                  |

| WCLK                                                         | 0    | Wait Clock Output<br>The real-time WCLK output is enabled by setting RTWCE bit in WCON<br>(S:A7h). When enabled, the WCLK output produces a square wave signal<br>with a period of one half the oscillator frequency.                                                                                                                                    | P1.7                  |

| WR#                                                          | 0    | <b>Write</b><br>Write signal output to external memory.                                                                                                                                                                                                                                                                                                  | P3.6                  |

| XTAL1                                                        | I    | Input to the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected to this<br>pin. If an external oscillator is used, its output is connected to this pin.<br>XTAL1 is the clock source for internal timing.                                                                                | -                     |

Table 2.

Product Name Signal Description (Continued)

#### Table 4. Serial I/O Port SFRs

| Mnemonic | Name                  |

|----------|-----------------------|

| SCON     | Serial Control        |

| SBUF     | Serial Data Buffer    |

| SADEN    | Slave Address<br>Mask |

### Table 5. SSLC SFRs

| Mnemonic | Name                                     |

|----------|------------------------------------------|

| SSCON    | Synchronous Serial control               |

| SSDAT    | Synchronous Serial<br>Data               |

| SSCS     | Synchronous Serial<br>Control and Status |

| Mnemonic | Name              |

|----------|-------------------|

| SADDR    | Slave Address     |

| BRL      | Baud Rate Reload  |

| BDRCON   | Baud Rate Control |

| Mnemonic | Name                           |

|----------|--------------------------------|

| SSADR    | Synchronous Serial<br>Address  |

| SSBR     | Synchronous Serial<br>Bit Rate |

#### Table 6. Event Waveform Control SFRs

| Mnemonic | Name                                  |

|----------|---------------------------------------|

| CCON     | EWC-PCA Timer/Counter Control         |

| CMOD     | EWC-PCA Timer/Counter Mode            |

| CL       | EWC-PCA Timer/Counter Low<br>Register |

| СН       | EWC-PCA Timer/Counter High Register   |

| CCAPM0   | EWC-PCA Timer/Counter Mode 0          |

| CCAPM1   | EWC-PCA Timer/Counter Mode 1          |

| CCAPM2   | EWC-PCA Timer/Counter Mode 2          |

| CCAPM3   | EWC-PCA Timer/Counter Mode 3          |

| CCAPM4   | EWC-PCA Timer/Counter Mode 4          |

| Mnemonic | Name                                              |

|----------|---------------------------------------------------|

| CCAP0L   | EWC-PCA Compare Capture<br>Module 0 Low Register  |

| CCAP1L   | EWC-PCA Compare Capture<br>Module 1 Low Register  |

| CCAP2L   | EWC-PCA Compare Capture<br>Module 2 Low Register  |

| CCAP3L   | EWC-PCA Compare Capture<br>Module 3 Low Register  |

| CCAP4L   | EWC-PCA Compare Capture<br>Module 4 Low Register  |

| CCAP0H   | EWC-PCA Compare Capture<br>Module 0 High Register |

| CCAP1H   | EWC-PCA Compare Capture<br>Module 1 High Register |

| CCAP2H   | EWC-PCA Compare Capture<br>Module 2 High Register |

| ССАРЗН   | EWC-PCA Compare Capture<br>Module 3 High Register |

| CCAP4H   | EWC-PCA Compare Capture<br>Module 4 High Register |

#### Table 16. Notation for Immediate Addressing

| Immediate<br>Address | Description                                                                                                                           | C251 | C51 |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| #data                | An 8-bit constant that is immediately addressed in an instruction                                                                     | 3    | 3   |

| #data16              | A 16-bit constant that is immediately addressed in an instruction                                                                     | 3    | -   |

| #0data16<br>#1data16 | A 32-bit constant that is immediately addressed in an instruction. The upper word is filled with zeros (#0data16) or ones (#1data16). | 3    | _   |

| #short               | A constant, equal to 1, 2, or 4, that is immediately addressed in an instruction.                                                     | 3    | _   |

#### Table 17. Notation for Bit Addressing

| Direct<br>Address | Description                                                                                                                                                                                                                                                            | C251 | C51 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| bit51             | A directly addressed bit (bit number = 00h-FFh) in memory or an SFR. Bits 00h-7Fh are the 128 bits in byte locations 20h-2Fh in the on-chip RAM. Bits 80h-FFh are the 128 bits in the 16 SFRs with addresses that end in 0h or 8h, S:80h, S:88h, S:90h,, S:F0h, S:F8h. | _    | 3   |

| bit               | A directly addressed bit in memory locations 00:0020h-00:007Fh or in any defined SFR.                                                                                                                                                                                  | 3    |     |

#### Table 18. Notation for Destination in Control Instructions

| Direct<br>Address | Description                                                                                                                              | C251 | C51 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| rel               | A signed (two's complement) 8-bit relative address. The destination is -128 to +127 bytes relative to the next instruction's first byte. | 3    | 3   |

| addr11            | An 11-bit target address. The target is in the same 2-Kbyte block of memory as the next instruction's first byte.                        | _    | 3   |

| addr16            | A 16-bit target address. The target can be anywhere within the same 64-Kbyte region as the next instruction's first byte.                | _    | 3   |

| addr24            | A 24-bit target address. The target can be anywhere within the 16-<br>Mbyte address space.                                               | 3    | -   |

# Size and Execution Time for Instruction Families

#### Table 20. Summary of Add and Subtract Instructions

| AddADD <dest>, <src>dest opnd <math>\leftarrow</math> dest opnd + src opnd</src></dest>                       |

|---------------------------------------------------------------------------------------------------------------|

| SubtractSUB <dest>, <src>dest opnd <math display="inline">\leftarrow</math> dest opnd - src opnd</src></dest> |

| Add with CarryADDC <dest>, <src>(A) <math>\leftarrow</math> (A) + src opnd + (CY)</src></dest>                |

| Subtract with BorrowSUBB <dest>, <src>(A) <math>\leftarrow</math> (A) - src opnd - (CY)</src></dest>          |

|               | -dost>                                       |                                                               | Binary | Mode             | Source | e Mode           |

|---------------|----------------------------------------------|---------------------------------------------------------------|--------|------------------|--------|------------------|

| Mnemonic      | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                                      | Bytes  | States           | Bytes  | States           |

|               | A, Rn                                        | Register to ACC                                               | 1      | 1                | 2      | 2                |

|               | A, dir8                                      | Direct address to ACC                                         | 2      | 1 <sup>(2)</sup> | 2      | 1 <sup>(2)</sup> |

| ADD           | A, at Ri                                     | Indirect address to ACC                                       | 1      | 2                | 2      | 3                |

|               | A, #data                                     | Immediate data to ACC                                         | 2      | 1                | 2      | 1                |

|               | Rmd, Rms                                     | Byte register to/from byte register                           | 3      | 2                | 2      | 1                |

|               | WRjd, WRjs                                   | Word register to/from word register                           | 3      | 3                | 2      | 2                |

|               | DRkd, DRks                                   | Dword register to/from dword register                         | 3      | 5                | 2      | 4                |

|               | Rm, #data                                    | Immediate 8-bit data to/from byte register                    | 4      | 3                | 3      | 3                |

|               | WRj, #data16                                 | Immediate 16-bit data to/from word register                   | 5      | 4                | 4      |                  |

|               | DRk,<br>#0data16                             | 16-bit unsigned immediate data to/from dword register         | 5      | 6                | 4      |                  |

| ADD/SUB       | Rm, dir8                                     | Direct address (on-chip RAM or SFR)<br>to/from byte register  | 4      | 3 <sup>(2)</sup> | 3      | 2 <sup>(2)</sup> |

|               | WRj, dir8                                    | Direct address (on-chip RAM or SFR) to/from word register     | 4      | 4                | 3      | 3                |

|               | Rm, dir16                                    | Direct address (64K) to/from byte<br>register                 | 5      | 3 <sup>(3)</sup> | 4      | 2 <sup>(3)</sup> |

|               | WRj, dir16                                   | Direct address (64K) to/from word register                    | 5      | 4 <sup>(4)</sup> | 4      | 3 <sup>(4)</sup> |

|               | Rm, at WRj                                   | Indirect address (64K) to/from byte register                  | 4      | 3 <sup>(3)</sup> | 3      | 2 <sup>(3)</sup> |

|               | Rm, at DRk                                   | Indirect address (16M) to/from byte register                  | 4      | 4 <sup>(3)</sup> | 3      | 3 <sup>(3)</sup> |

|               | A, Rn                                        | Register to/from ACC with carry                               | 1      | 1                | 2      | 2                |

|               | A, dir8                                      | Direct address (on-chip RAM or SFR)<br>to/from ACC with carry | 2      | 1 <sup>(2)</sup> | 2      | 1 <sup>(2)</sup> |

| ADDC/SU<br>BB | A, at Ri                                     | Indirect address to/from ACC with carry                       | 1      | 2                | 2      | 3                |

|               | A, #data                                     | Immediate data to/from ACC with carry                         | 2      | 1                | 2      | 1                |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

3. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

4. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

$IncrementINC < dest>dest opnd \leftarrow dest opnd + 1$

IncrementINC <dest>, <src>dest opnd  $\leftarrow$  dest opnd + src opnd

$DecrementDEC < dest>dest opnd \leftarrow dest opnd - 1$

$\texttt{DecrementDEC <dest>, <src>dest opnd \leftarrow dest opnd - src opnd}$

|          |                                              |                                          | Binary | Mode             | Source | e Mode           |

|----------|----------------------------------------------|------------------------------------------|--------|------------------|--------|------------------|

| Mnemonic | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                 | Bytes  | States           | Bytes  | States           |

|          | A                                            | ACC by 1                                 | 1      | 1                | 1      | 1                |

| INC      | Rn                                           | Register by 1                            | 1      | 1                | 2      | 2                |

| DEC      | dir8                                         | Direct address (on-chip RAM or SFR) by 1 | 2      | 2 <sup>(2)</sup> | 2      | 2 <sup>(2)</sup> |

|          | at Ri                                        | Indirect address by 1                    | 1      | 3                | 2      | 4                |

| INC      | Rm, #short                                   | Byte register by 1, 2, or 4              | 3      | 2                | 2      | 1                |

| DEC      | WRj, #short                                  | Word register by 1, 2, or 4              | 3      | 2                | 2      | 1                |

| INC      | DRk, #short                                  | Double word register by 1, 2, or 4       | 3      | 4                | 2      | 3                |

| DEC      | DRk, #short                                  | Double word register by 1, 2, or 4       | 3      | 5                | 2      | 4                |

| INC      | DPTR                                         | Data pointer by 1                        | 1      | 1                | 1      | 1                |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

- Notes: 1. Logical instructions that affect a bit are in Table 27.

- 2. A shaded cell denotes an instruction in the C51 Architecture.

- 3. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

- 4. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

- 5. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

- 6. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

| Table 23. | Summar | of Logical | Instructions | (2/2) |

|-----------|--------|------------|--------------|-------|

|           |        |            |              |       |

| (CY) ← <des<br>Shift Right Arithme<br/><dest><sub>n-1</sub> ←<br/>(CY) ← <des<br>Shift Right Logical</des<br></dest></des<br> | <dest><sub>n</sub>, n =<br/>tt&gt;<sub>msb</sub><br/>eticSRA <des<br><dest><sub>n</sub>, n = n<br/>tt&gt;<sub>0</sub><br/>SRL <dest>&lt;<br/><dest><sub>n</sub>, n = n<br/>tt&gt;<sub>0</sub></dest></dest></dest></des<br></dest> | 0msb-1<br>t> <dest><sub>msb</sub> ← <dest><sub>msb</sub><br/>msb1<br/>:dest&gt;<sub>msb</sub> ← 0</dest></dest> |        |        |        |        |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|

|                                                                                                                               | <dest>,</dest>                                                                                                                                                                                                                     |                                                                                                                 | Binary | Mode   | Source | e Mode |

| Mnemonic                                                                                                                      | <src><sup>(1)</sup></src>                                                                                                                                                                                                          | Comments                                                                                                        | Bytes  | States | Bytes  | States |

|                                                                                                                               | Rm                                                                                                                                                                                                                                 | Shift byte register left through the MSB                                                                        | 3      | 2      | 2      | 1      |

| SLL                                                                                                                           | WRj                                                                                                                                                                                                                                | Shift word register left through the MSB                                                                        | 3      | 2      | 2      | 1      |

| SRA                                                                                                                           | Rm                                                                                                                                                                                                                                 | Shift byte register right                                                                                       | 3      | 2      | 2      | 1      |

| SKA                                                                                                                           | WRj                                                                                                                                                                                                                                | Shift word register right                                                                                       | 3      | 2      | 2      | 1      |

| SRL                                                                                                                           | Rm                                                                                                                                                                                                                                 | Shift byte register left                                                                                        | 3      | 2      | 2      | 1      |

| JRL                                                                                                                           | WRj                                                                                                                                                                                                                                | Shift word register left                                                                                        | 3      | 2      | 2      | 1      |

| SWAP                                                                                                                          | А                                                                                                                                                                                                                                  | Swap nibbles within ACC                                                                                         | 1      | 2      | 1      | 2      |

Note: 1. A shaded cell denotes an instruction in the C51 Architecture.

#### Lock Bit System

The TSC87251G2D products implement 3 levels of security for User's program as described in Table 33. The TSC83251G2D products implement only the first level of security.

Level 0 is the level of an erased part and does not enable any security features.

Level 1 locks the programming of the User's internal Code Memory, the Configuration Bytes and the Encryption Array.

Level 2 locks the verifying of the User's internal Code Memory. It is always possible to verify the Configuration Bytes and the Lock Bits. It is not possible to verify the Encryption Array.

Level 3 locks the external execution.

| Level | Lock bits<br>LB[2:0] | Internal<br>Execution | External<br>Execution | Verification          | Programming | External<br>PROM read<br>(MOVC) |

|-------|----------------------|-----------------------|-----------------------|-----------------------|-------------|---------------------------------|

| 0     | 000                  | Enable                | Enable                | Enable <sup>(1)</sup> | Enable      | Enable <sup>(2)</sup>           |

| 1     | 001                  | Enable                | Enable                | Enable <sup>(1)</sup> | Disable     | Disable                         |

| 2     | 01x <sup>(3)</sup>   | Enable                | Enable                | Disable               | Disable     | Disable                         |

| 3     | 1xx <sup>(3)</sup>   | Enable                | Disable               | Disable               | Disable     | Disable                         |

Table 33. Lock Bits Programming

Notes: 1. Returns encrypted data if Encryption Array is programmed.

2. Returns non encrypted data.

3. x means don't care. Level 2 always enables level 1, and level 3 always enables levels 1 and 2.

The security level may be verified according to Table 34.

#### Table 34. Lock Bits Verifying

| Level | Lock bits Data <sup>(1)</sup> |

|-------|-------------------------------|

| 0     | xxxxx000                      |

| 1     | xxxxx001                      |

| 2     | xxxxx01x                      |

| 3     | xxxxx1xx                      |

Note: 1. x means don't care.

#### **Encryption Array**

The TSC83251G2D and TSC87251G2D products include a 128-byte Encryption Array located in non-volatile memory outside the memory address space. During verification of the on-chip code memory, the seven low-order address bits also address the Encryption Array. As the byte of the code memory is read, it is exclusive-NOR'ed (XNOR) with the key byte from the Encryption Array. If the Encryption Array is not programmed (still all 1s), the user program code is placed on the data bus in its original, unencrypted form. If the Encryption Array is programmed with key bytes, the user program code is encrypted and cannot be used without knowledge of the key byte sequence.

• PSEN# and the other control signals have to be released to complete a sequence of programming operations or a sequence of programming and verifying operations.

Table 36.

Programming Modes

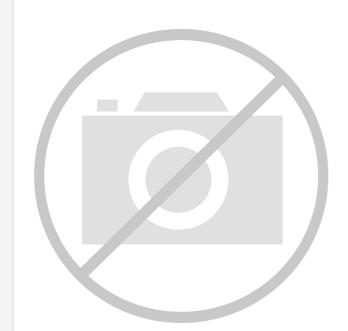

| ROM Area <sup>(1)</sup> | RST | EA#/VPP         | PSEN<br># | ALE/PROG# <sup>(2)</sup> | P0  | P2   | P1(MSB) P3(LSB)                                 |

|-------------------------|-----|-----------------|-----------|--------------------------|-----|------|-------------------------------------------------|

| On-chip Code<br>Memory  | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 68h | Data | 16-bit Address<br>0000h-7FFFh (32<br>kilobytes) |

| Configuration<br>Bytes  | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 69h | Data | CONFIG0: FFF8h<br>CONFIG1: FFF9h                |

| Lock Bits               | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 6Bh | х    | LB0: 0001h<br>LB1: 0002h<br>LB2: 0003h          |

| Encryption Array        | 1   | V <sub>PP</sub> | 0         | 1 Pulse                  | 6Ch | Data | 0000h-007Fh                                     |

Notes: 1. Signature Bytes are not user-programmable.

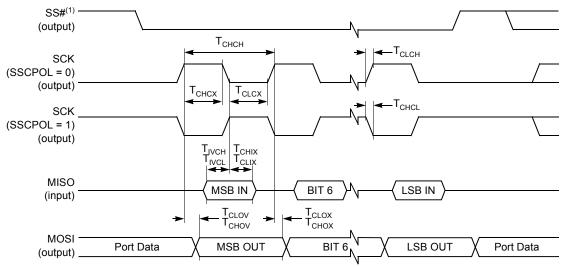

2. The ALE/PROG# pulse waveform is shown in Figure 23 page 59.

### **Verify Algorithm**

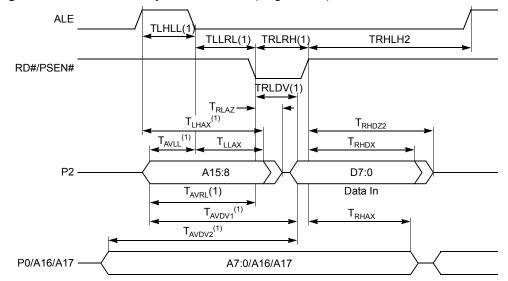

Figure 7 shows the hardware setup needed to verify the TSC87251G2D EPROM/OTPROM or TSC83251G2D ROM areas:

- The chip has to be put under reset and maintained in this state until the completion of the verifying sequence.

- PSEN# and the other control signals (ALE and Port 0) have to be set to a high level.

- Then PSEN# has to be to forced to a low level after two clock cycles or more and it

has to be maintained in this state until the completion of the verifying sequence (see

below).

- The voltage on the EA# pin must be set to V<sub>DD</sub> and ALE must be set to a high level.

- The Verifying Mode is selected according to the code applied on Port 0. It has to be applied until the completion of this verifying operation.

- The verifying address is applied on Ports 1 and 3 which are respectively the MSB and the LSB of the address.

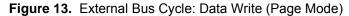

Figure 12. External Bus Cycle: Data Read (Page Mode)

#### AC Characteristics - Real-Time Synchronous Wait State

#### **Definition of Symbols**

**Table 41.** Real-Time Synchronous Wait Timing Symbol Definitions

|   | Signals   |

|---|-----------|

| С | WCLK      |

| R | RD#/PSEN# |

| W | WR#       |

| Y | WAIT#     |

| Conditions |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| L          | Low             |  |  |  |  |

| V          | Valid           |  |  |  |  |

| Х          | No Longer Valid |  |  |  |  |

## 50 AT/TSC8x251G2D

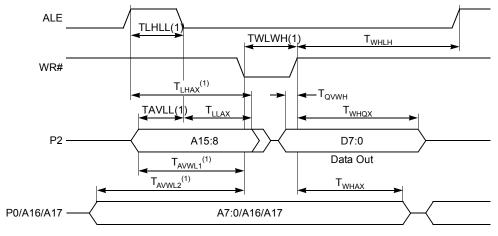

### AC Characteristics - Real-Time Asynchronous Wait State

#### **Definition of Symbols**

**Table 43.** Real-Time Asynchronous Wait Timing Symbol Definitions

| Signals |               |  |  |  |  |

|---------|---------------|--|--|--|--|

| S       | PSEN#/RD#/WR# |  |  |  |  |

| Y       | AWAIT#        |  |  |  |  |

| Conditions        |  |  |  |

|-------------------|--|--|--|

| L Low             |  |  |  |

| V Valid           |  |  |  |

| X No Longer Valid |  |  |  |

#### Timings

**Table 44.** Real-Time Asynchronous Wait AC Timings;  $V_{DD}$  = 2.7 to 5.5 V,  $T_A$  = -40 to 85°C

| Symbol            | Parameter                         | Min                          | Мах                   | Unit              |

|-------------------|-----------------------------------|------------------------------|-----------------------|-------------------|

| T <sub>SLYV</sub> | PSEN#/RD#/WR# Low to Wait Set-up  |                              | T <sub>OSC</sub> - 10 | ns                |

| T <sub>SLYX</sub> | Wait Hold after PSEN#/RD#/WR# Low | (2N-1)·T <sub>OSC</sub> + 10 |                       | ns <sup>(1)</sup> |

Note: 1. N is the number of wait states added (N $\geq$  1).

Waveforms

#### Figure 16. Real-time Asynchronous Wait State Timings

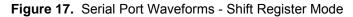

### AC Characteristics - Serial Port in Shift Register Mode

**Definition of Symbols**

#### Table 45. Serial Port Timing Symbol Definitions

| Signals |          |  |  |

|---------|----------|--|--|

| D       | Data In  |  |  |

| Q       | Data Out |  |  |

| Х       | Clock    |  |  |

| Conditions |                 |  |  |

|------------|-----------------|--|--|

| Н          | High            |  |  |

| L          | Low             |  |  |

| V          | Valid           |  |  |

| Х          | No Longer Valid |  |  |

#### Timings

**Table 46.** Serial Port AC Timing -Shift Register Mode;  $V_{DD}$  = 2.7 to 5.5 V,  $T_A$  = -40 to 85°C

|                   |                                             | 12  | MHz | 16  | ИНz | 24 M | Hz <sup>(1)</sup> |      |

|-------------------|---------------------------------------------|-----|-----|-----|-----|------|-------------------|------|

| Symbol            | Parameter                                   | Min | Max | Min | Max | Min  | Max               | Unit |

| T <sub>XLXL</sub> | Serial Port Clock Cycle Time                | 998 |     | 749 |     | 500  |                   | ns   |

| T <sub>QVXH</sub> | Output Data Setup to Clock Rising<br>Edge   | 833 |     | 625 |     | 417  |                   | ns   |

| T <sub>XHQX</sub> | Output Data hold after Clock Rising<br>Edge | 165 |     | 124 |     | 82   |                   | ns   |

| T <sub>XHDX</sub> | Input Data Hold after Clock Rising<br>Edge  | 0   |     | 0   |     | 0    |                   | ns   |

| T <sub>XHDV</sub> | Clock Rising Edge to Input Data<br>Valid    |     | 974 |     | 732 |      | 482               | ns   |

Note: 1. For high speed versions only.

#### Waveforms

Note: 1. TI and RI are set during S1P1 of the peripheral cycle following the shift of the eight bit.

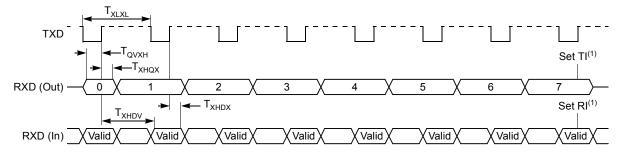

#### Timings

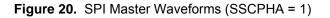

### **Table 49.** SPI Interface AC Timing; $V_{DD}$ = 2.7 to 5.5 V, $T_A$ = -40 to 85°C

| Symbol                                | Parameter                              | Min | Max | Unit             |

|---------------------------------------|----------------------------------------|-----|-----|------------------|

|                                       | Slave Mode <sup>(1</sup>               | )   |     | 1                |

| Тснсн                                 | Clock Period                           | 8   |     | T <sub>OSC</sub> |

| T <sub>CHCX</sub>                     | Clock High Time                        | 3.2 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 3.2 |     | T <sub>osc</sub> |

| T <sub>SLCH</sub> , T <sub>SLCL</sub> | SS# Low to Clock edge                  | 200 |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 100 | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>CLSH</sub> , T <sub>CHSH</sub> | SS# High after Clock Edge              | 0   |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>SLOV</sub>                     | SS# Low to Output Data Valid           |     | 130 | ns               |

| Т <sub>знох</sub>                     | Output Data Hold after SS# High        |     | 130 | ns               |

| T <sub>SHSL</sub>                     | SS# High to SS# Low                    | (2) |     |                  |

| T <sub>ILIH</sub>                     | Input Rise Time                        |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Fall Time                        |     | 2   | μs               |

| Т <sub>огон</sub>                     | Output Rise time                       |     | 100 | ns               |

| Т <sub>ОНОL</sub>                     | Output Fall Time                       |     | 100 | ns               |

|                                       | Master Mode                            | (3) |     |                  |

| Тснсн                                 | Clock Period                           | 4   |     | T <sub>osc</sub> |

| Т <sub>снсх</sub>                     | Clock High Time                        | 1.6 |     | T <sub>osc</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 1.6 |     | T <sub>osc</sub> |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 50  |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 50  |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 65  | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>ILIH</sub>                     | Input Data Rise Time                   |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Data Fall Time                   |     | 2   | μs               |

| Т <sub>оloн</sub>                     | Output Data Rise time                  |     | 50  | ns               |

| Т <sub>оноь</sub>                     | Output Data Fall Time                  |     | 50  | ns               |

Notes: 1. Capacitive load on all pins = 200 pF in slave mode.

2. The value of this parameter depends on software.

3. Capacitive load on all pins = 100 pF in master mode.

Note: 1. SS# handled by software.

Note: 1. Not Defined but normally MSB of character just received.

#### Timings

| Symbol            | Parameter                          | Min  | Мах | Unit             |

|-------------------|------------------------------------|------|-----|------------------|

| T <sub>osc</sub>  | XTAL1 Period                       | 83.5 | 250 | ns               |

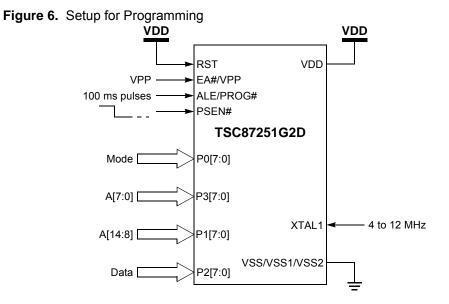

| T <sub>AVGL</sub> | Address Setup to PROG# low         | 48   |     | T <sub>OSC</sub> |

| T <sub>GHAX</sub> | Address Hold after PROG# low       | 48   |     | T <sub>OSC</sub> |

| T <sub>DVGL</sub> | Data Setup to PROG# low            | 48   |     | T <sub>OSC</sub> |

| T <sub>GHDX</sub> | Data Hold after PROG#              | 48   |     | T <sub>OSC</sub> |

| T <sub>ELSH</sub> | ENABLE High to V <sub>PP</sub>     | 48   |     | T <sub>OSC</sub> |

| T <sub>SHGL</sub> | V <sub>PP</sub> Setup to PROG# low | 10   |     | μs               |

| T <sub>GHSL</sub> | V <sub>PP</sub> Hold after PROG#   | 10   |     | μs               |

| T <sub>SLEH</sub> | ENABLE Hold after V <sub>PP</sub>  | 0    |     | ns               |

| T <sub>GLGH</sub> | PROG# Width                        | 90   | 110 | μs               |

### Table 51. EPROM Programming AC timings; $V_{DD}$ = 4.5 to 5.5 V, $T_A$ = 0 to 40°C

**Table 52.** EPROM Verifying AC timings;  $V_{DD}$  = 4.5 to 5.5 V,  $V_{DD}$  = 2.7 to 5.5 V,  $T_A$  = 0 to 40°C

| Symbol            | Parameter                | Min  | Мах | Unit             |

|-------------------|--------------------------|------|-----|------------------|

| T <sub>osc</sub>  | XTAL1 Period             | 83.5 | 250 | ns               |

| T <sub>AVQV</sub> | Address to Data Valid    |      | 48  | T <sub>osc</sub> |

| T <sub>AXQX</sub> | Address to Data Invalid  | 0    |     | ns               |

| T <sub>ELQV</sub> | ENABLE low to Data Valid | 0    | 48  | T <sub>osc</sub> |

| T <sub>EHQZ</sub> | Data Float after ENABLE  | 0    | 48  | T <sub>osc</sub> |

#### Waveforms

## Absolute Maximum Rating and Operating Conditions

## Absolute Maximum Ratings

| Storage Temperature65 to +150°C              | *NOTICE: Stressing the device beyond the "Absolute Maxi-<br>mum Ratings" may cause permanent damage. |

|----------------------------------------------|------------------------------------------------------------------------------------------------------|

| Voltage on any other Pin to VSS0.5 to +6.5 V | These are stress ratings only. Operation beyond                                                      |

| I <sub>OL</sub> per I/O Pin 15 mA            | the "operating conditions" is not recommended<br>and extended exposure beyond the "Operating         |

| Power Dissipation 1.5 W                      | Conditions" may affect device reliability.                                                           |

| Ambient Temperature Under Bias               |                                                                                                      |

| Commercial0 to +70°C                         |                                                                                                      |

| Industrial40 to +85°C                        |                                                                                                      |

| Automotive40 to +85°C                        |                                                                                                      |

| V <sub>DD</sub>                              |                                                                                                      |

| High Speed versions                          |                                                                                                      |

| Low Voltage versions 2.7 to 5.5 V            |                                                                                                      |

## Low Voltage Versions - Commercial & Industrial

| Table 56. | DC Characteristics; | V <sub>DD</sub> = 2.7 to | 5.5 V, T <sub>A</sub> : | = -40 to +85°C |

|-----------|---------------------|--------------------------|-------------------------|----------------|

|-----------|---------------------|--------------------------|-------------------------|----------------|

| Symbol              | Parameter                                                                                   | Min                       | Typical <sup>(4)</sup> | Max                       | Units | Test Conditions                                                                                                                                                                                                                    |

|---------------------|---------------------------------------------------------------------------------------------|---------------------------|------------------------|---------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>     | Input Low Voltage<br>(except EA#, SCL, SDA)                                                 | -0.5                      |                        | 0.2·V <sub>DD</sub> - 0.1 | V     |                                                                                                                                                                                                                                    |

| $V_{IL1}^{(5)}$     | Input Low Voltage<br>(SCL, SDA)                                                             | -0.5                      |                        | 0.3·V <sub>DD</sub>       | v     |                                                                                                                                                                                                                                    |

| V <sub>IL2</sub>    | Input Low Voltage<br>(EA#)                                                                  | 0                         |                        | 0.2·V <sub>DD</sub> - 0.3 | V     |                                                                                                                                                                                                                                    |

| V <sub>IH</sub>     | Input high Voltage<br>(except XTAL1, RST, SCL, SDA)                                         | 0.2·V <sub>DD</sub> + 0.9 |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                                                                                                                                    |

| $V_{\rm IH1}^{(5)}$ | Input high Voltage<br>(XTAL1, RST, SCL, SDA)                                                | 0.7·V <sub>DD</sub>       |                        | V <sub>DD</sub> + 0.5     | v     |                                                                                                                                                                                                                                    |

| V <sub>OL</sub>     | Output Low Voltage<br>(Ports 1, 2, 3)                                                       |                           |                        | 0.45                      | v     | $I_{OL} = 0.8 \text{ mA}^{(1)(2)}$                                                                                                                                                                                                 |

| V <sub>OL1</sub>    | Output Low Voltage<br>(Ports 0, ALE, PSEN#, Port 2 in Page<br>Mode during External Address) |                           |                        | 0.45                      | v     | I <sub>OL</sub> = 1.6 mA <sup>(1)(2)</sup>                                                                                                                                                                                         |

| V <sub>OH</sub>     | Output high Voltage<br>(Ports 1, 2, 3, ALE, PSEN#)                                          | 0.9·V <sub>DD</sub>       |                        |                           | V     | I <sub>OH</sub> = -10 μA <sup>(3)</sup>                                                                                                                                                                                            |

| V <sub>OH1</sub>    | Output high Voltage<br>(Port 0, Port 2 in Page Mode during<br>External Address)             | 0.9·V <sub>DD</sub>       |                        |                           | v     | Ι <sub>ΟΗ</sub> = -40 μΑ                                                                                                                                                                                                           |

| $V_{RET}$           | V <sub>DD</sub> data retention limit                                                        |                           |                        | 1.8                       | V     |                                                                                                                                                                                                                                    |

| I <sub>ILO</sub>    | Logical 0 Input Current<br>(Ports 1, 2, 3 - AWAIT#)                                         |                           |                        | - 50                      | μA    | V <sub>IN</sub> = 0.45 V                                                                                                                                                                                                           |

| I <sub>IL1</sub>    | Logical 1 Input Current<br>(NMI)                                                            |                           |                        | + 50                      | μA    | V <sub>IN</sub> = V <sub>DD</sub>                                                                                                                                                                                                  |

| I <sub>LI</sub>     | Input Leakage Current<br>(Port 0)                                                           |                           |                        | ± 10                      | μΑ    | 0.45 V < V <sub>IN</sub> < V <sub>DD</sub>                                                                                                                                                                                         |

| I <sub>TL</sub>     | Logical 1-to-0 Transition Current<br>(Ports 1, 2, 3)                                        |                           |                        | - 650                     | μΑ    | V <sub>IN</sub> = 2.0 V                                                                                                                                                                                                            |

| R <sub>RST</sub>    | RST Pull-Down Resistor                                                                      | 40                        | 110                    | 225                       | kΩ    |                                                                                                                                                                                                                                    |

| C <sub>IO</sub>     | Pin Capacitance                                                                             |                           | 10                     |                           | pF    | T <sub>A</sub> = 25°C                                                                                                                                                                                                              |

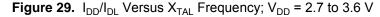

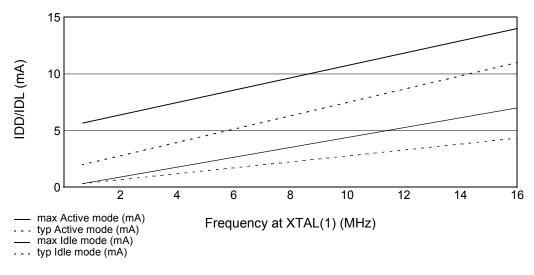

| I <sub>DD</sub>     | Operating Current                                                                           |                           | 4<br>8<br>9<br>11      | 8<br>11<br>12<br>14       | mA    | $\begin{array}{l} 5 \mbox{ MHz, } V_{\rm DD} < 3.6 \mbox{ V} \\ 10 \mbox{ MHz, } V_{\rm DD} < 3.6 \mbox{ V} \\ 12 \mbox{ MHz, } V_{\rm DD} < 3.6 \mbox{ V} \\ 16 \mbox{ MHz, } V_{\rm DD} < 3.6 \mbox{ V} \end{array}$             |

| I <sub>DL</sub>     | Idle Mode Current                                                                           |                           | 0.5<br>1.5<br>2<br>3   | 1<br>4<br>5<br>7          | mA    | $\begin{array}{c} 5 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 10 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 12 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \\ 16 \text{ MHz, } V_{\text{DD}} < 3.6 \text{ V} \end{array}$ |

| I <sub>PD</sub>     | Power-Down Current                                                                          |                           | 1                      | 10                        | μA    | V <sub>RET</sub> < V <sub>DD</sub> < 3.6 V                                                                                                                                                                                         |

Notes: 1. Under steady-state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum IOL per port pin: 10 mA

Maximum IOL per 8-bit port: Port 0 26 mA

Ports 1-315 mA

Maximum Total IOL for all:Output Pins71 mA

If IOL exceeds the test conditions, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 2. Capacitive loading on Ports 0 and 2 may cause spurious noise pulses above 0.4 V on the low-level outputs of ALE and Ports 1, 2, and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins change from high to low. In applications where capacitive loading exceeds 100 pF, the noise pulses on these signals may exceed 0.8 V. It may be desirable to qualify ALE or other signals with a Schmitt Trigger or CMOS-level input logic.

- Capacitive loading on Ports 0 and 2 causes the V<sub>OH</sub> on ALE and PSEN# to drop below the specification when the address lines are stabilizing.

- 4. Typical values are obtained using  $V_{DD}$  = 3 V and  $T_A$  = 25°C. They are not tested and there is not guarantee on these values.

- The input threshold voltage of SCL and SDA meets the TWI specification, so an input voltage below 0.3 V<sub>DD</sub> will be recognized as a logic 0 while an input voltage above 0.7 V<sub>DD</sub> will be recognized as a logic 1.

Note: 1.The clock prescaler is not used:  $F_{OSC} = F_{XTAL}$ .

## $I_{DD}$ , $I_{DL}$ and $I_{PD}$ Test Conditions

| Part Number <sup>(1)</sup>        | ROM         | Description                            |  |  |

|-----------------------------------|-------------|----------------------------------------|--|--|

| Low Voltage Versions 2.7 to 5.5 V |             |                                        |  |  |

| TSC251G2Dxxx-L16CB                | 32K MaskROM | 16 MHz, Commercial 0° to 70°C, PLCC 44 |  |  |

| TSC251G2Dxxx-L16CE                | 32K MaskROM | 16 MHz, Commercial 0° to 70°C, VQFP 44 |  |  |

| AT251G2Dxxx-SLSUL                 | 32K MaskROM | 16 MHz, Industrial & Green, PLCC 44    |  |  |

| AT251G2Dxxx-RLTUL                 | 32K MaskROM | 16 MHz, Industrial & Green, VQFP 44    |  |  |

Note: 1. xxx: means ROM code, is Cxxx in case of encrypted code.

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

Memory 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

*Microcontrollers* 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

ASIC/ASSP/Smart Cards Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743 **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNTIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically providedotnerts in applications intended to support or sustain life.

© Atmel Corporation 2006. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and Everywhere You Are<sup>®</sup> are the trademarks or registered trademarks, of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.