Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | C251                                                                        |

| Core Size                  | 8/16-Bit                                                                    |

| Speed                      | 16MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, Microwire, SPI, UART/USART                       |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 32                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-LCC (J-Lead)                                                             |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/tsc87251g2d-l16cb |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Typical Operating Current:11 mA at 3V

- Typical Power-down Current: 1 μA

- Temperature Ranges: Commercial (0°C to +70°C), Industrial (-40°C to +85°C), Automotive ((-40°C to +85°C) ROM only)

- Option: Extended Range (-55°C to +125°C)

- Packages: PDIL 40, PLCC 44 and VQFP 44

- Options: Known Good Dice and Ceramic Packages

## Description

The TSC80251G2D products are derivatives of the Atmel Microcontroller family based on the 8/16-bit C251 Architecture. This family of products is tailored to 8/16-bit microcontroller applications requiring an increased instruction throughput, a reduced operating frequency or a larger addressable memory space. The architecture can provide a significant code size reduction when compiling C programs while fully preserving the legacy of C51 assembly routines.

The TSC80251G2D derivatives are pin and software compatible with standard 80C51/Fx/Rx/Rx+ with extended on-chip data memory (1 Kbyte RAM) and up to 256 kilobytes of external code and data. Additionally, the TSC83251G2D and TSC87251G2D provide on-chip code memory: 32 kilobytes ROM and 32 kilobytes EPROM/OTPROM respectively.

They provide transparent enhancements to Intel's xC251Sx family with an additional Synchronous Serial Link Controller (SSLC supporting TWI,  $\mu$ Wire and SPI protocols), a Keyboard interrupt interface, a dedicated Baud Rate Generator for UART, and Power Management features.

TSC80251G2D derivatives are optimized for speed and for low power consumption on a wide voltage range.

Note: 1. This Datasheet provides the technical description of the TSC80251G2D derivatives. For further information on the device usage, please request the TSC80251 Programmer's Guide and the TSC80251G1D Design Guide and errata sheet.

## Typical Applications • ISDN Terminals

- High-Speed Modems

- PABX (SOHO)

- Line Cards

- DVD ROM and Players

- Printers

- Plotters

- Scanners

- Banking Machines

- Barcode Readers

- Smart Cards Readers

- High-End Digital Monitors

- High-End Joysticks

- High-end TV's

| Table 2.       | Produ | ct Name Signal Description (Continued)                                                                                                                                                                                                                                                                                                                   |                       |

|----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Signal<br>Name | Туре  | Description                                                                                                                                                                                                                                                                                                                                              | Alternate<br>Function |

| T1:0           | I/O   | <b>Timer 1:0 External Clock Inputs</b><br>When timer 1:0 operates as a counter, a falling edge on the T1:0 pin increments the count.                                                                                                                                                                                                                     | -                     |

| T2             | I/O   | <b>Timer 2 Clock Input/Output</b><br>For the timer 2 capture mode, T2 is the external clock input. For the Timer 2 clock-out mode, T2 is the clock output.                                                                                                                                                                                               | P1.0                  |

| T2EX           | I     | <b>Timer 2 External Input</b><br>In timer 2 capture mode, a falling edge initiates a capture of the timer 2<br>registers. In auto-reload mode, a falling edge causes the timer 2 register to<br>be reloaded. In the up-down counter mode, this signal determines the<br>count direction: 1 = up, 0 = down.                                               | P1.1                  |

| тхр            | 0     | <b>Transmit Serial Data</b><br>TXD outputs the shift clock in serial I/O mode 0 and transmits data in serial<br>I/O modes 1, 2 and 3.                                                                                                                                                                                                                    | P3.1                  |

| VDD            | PWR   | <b>Digital Supply Voltage</b><br>Connect this pin to +5V or +3V supply voltage.                                                                                                                                                                                                                                                                          | -                     |

| VPP            | I     | <b>Programming Supply Voltage</b><br>The programming supply voltage is applied to this input for programming<br>the on-chip EPROM/OTPROM.                                                                                                                                                                                                                | -                     |

| VSS            | GND   | Circuit Ground<br>Connect this pin to ground.                                                                                                                                                                                                                                                                                                            | -                     |

| VSS1           | GND   | Secondary Ground 1<br>This ground is provided to reduce ground bounce and improve power<br>supply bypassing. Connection of this pin to ground is recommended.<br>However, when using the TSC80251G2D as a pin-for-pin replacement for a<br>8xC51 product, VSS1 can be unconnected without loss of compatibility.<br>Not available on DIP package.        | Ι                     |

| VSS2           | GND   | <b>Secondary Ground 2</b><br>This ground is provided to reduce ground bounce and improve power<br>supply bypassing. Connection of this pin to ground is recommended.<br>However, when using the TSC80251G2D as a pin-for-pin replacement for a<br>8xC51 product, VSS2 can be unconnected without loss of compatibility.<br>Not available on DIP package. | _                     |

| WAIT#          | I     | <b>Real-time Synchronous Wait States Input</b><br>The real-time WAIT# input is enabled by setting RTWE bit in WCON<br>(S:A7h). During bus cycles, the external memory system can signal<br>'system ready' to the microcontroller in real time by controlling the WAIT#<br>input signal.                                                                  | P1.6                  |

| WCLK           | 0     | Wait Clock Output<br>The real-time WCLK output is enabled by setting RTWCE bit in WCON<br>(S:A7h). When enabled, the WCLK output produces a square wave signal<br>with a period of one half the oscillator frequency.                                                                                                                                    | P1.7                  |

| WR#            | 0     | <b>Write</b><br>Write signal output to external memory.                                                                                                                                                                                                                                                                                                  | P3.6                  |

| XTAL1          | I     | Input to the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected to this<br>pin. If an external oscillator is used, its output is connected to this pin.<br>XTAL1 is the clock source for internal timing.                                                                                | -                     |

Table 2.

Product Name Signal Description (Continued)

| Table 2. | Product Name Signal Description | (Continued) |

|----------|---------------------------------|-------------|

|----------|---------------------------------|-------------|

| Signal<br>Name | Туре | Description                                                                                                                                                                                                  | Alternate<br>Function |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| XTAL2          | ο    | Output of the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected to this<br>pin. If an external oscillator is used, leave XTAL2 unconnected. | _                     |

Note: The description of A15:8/P2.7:0 and AD7:0/P0.7:0 are for the Non-Page mode chip configuration. If the chip is configured in Page mode operation, port 0 carries the lower address bits (A7:0) while port 2 carries the upper address bits (A15:8) and the data (D7:0).

### **Configuration Byte 1**

### Table 13. Address Ranges and Usage of RD#, WR# and PSEN# Signals

| RD1 | RD0 | P1.7    | P3.7/RD#                                     | PSEN#                                               | WR#                                                  | External<br>Memory       |

|-----|-----|---------|----------------------------------------------|-----------------------------------------------------|------------------------------------------------------|--------------------------|

| 0   | 0   | A17     | A16                                          | Read signal for all<br>external memory<br>locations | Write signal for all<br>external memory<br>locations | 256 KB                   |

| 0   | 1   | I/O pin | A16                                          | Read signal for all external memory locations       | Write signal for all<br>external memory<br>locations | 128 KB                   |

| 1   | 0   | I/O pin | I/O pin                                      | Read signal for all external memory locations       | Write signal for all external memory locations       | 64 KB                    |

| 1   | 1   | I/O pin | Read<br>signal for<br>regions 00:<br>and 01: | Read signal for<br>regions FE: and FF:              | Write signal for all<br>external memory<br>locations | 2 × 64 KB <sup>(1)</sup> |

Notes: 1. This selection provides compatibility with the standard 80C51 hardware which has separate external memory spaces for data and code.

## Instruction Set Summary

This section contains tables that summarize the instruction set. For each instruction there is a short description, its length in bytes, and its execution time in states (one state time is equal to two system clock cycles). There are two concurrent processes limiting the effective instruction throughput:

- Instruction Fetch

- Instruction Execution

Table 20 to Table 32 assume code executing from on-chip memory, then the CPU is fetching 16-bit at a time and this is never limiting the execution speed.

If the code is fetched from external memory, a pre-fetch queue will store instructions ahead of execution to optimize the memory bandwidth usage when slower instructions are executed. However, the effective speed may be limited depending on the average size of instructions (for the considered section of the program flow). The maximum average instruction throughput is provided by Table 14 depending on the external memory configuration (from Page Mode to Non-Page Mode and the maximum number of wait states). If the average size of instructions is not an integer, the maximum effective throughput is found by pondering the number of states for the neighbor integer values.

| Average size               |                       | Non-page Mode (states) |                 |               |               |               |  |

|----------------------------|-----------------------|------------------------|-----------------|---------------|---------------|---------------|--|

| of Instructions<br>(bytes) | Page Mode<br>(states) | 0 Wait<br>State        | 1 Wait<br>State | 2 Wait States | 3 Wait States | 4 Wait States |  |

| 1                          | 1                     | 2                      | 3               | 4             | 5             | 6             |  |

| 2                          | 2                     | 4                      | 6               | 8             | 10            | 12            |  |

| 3                          | 3                     | 6                      | 9               | 12            | 15            | 18            |  |

| 4                          | 4                     | 8                      | 12              | 16            | 20            | 24            |  |

| 5                          | 5                     | 10                     | 15              | 20            | 25            | 30            |  |

Table 14.

Minimum Number of States per Instruction for given Average Sizes

If the average execution time of the considered instructions is larger than the number of states given by Table 14, this larger value will prevail as the limiting factor. Otherwise, the value from Table 14 must be taken. This is providing a fair estimation of the execution speed but only the actual code execution can provide the final value.

### Table 15 to Table 19 provide notation for Instruction Operands.

#### Notation for Instruction Operands

.

#### Table 15. Notation for Direct Addressing

| Direct<br>Address | Description                                                                                                                                                            | C251 | C51 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| dir8              | A direct 8-bit address. This can be a memory address (00h-7Fh) or a SFR address (80h-FFh). It is a byte (default), word or double word depending on the other operand. | 3    | з   |

| dir16             | A 16-bit memory address (00:0000h-00:FFFFh) used in direct addressing.                                                                                                 | 3    | _   |

| Register                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C251 | C51 |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| at Ri                                                       | A memory location (00h-FFh) addressed indirectly via byte registers<br>R0 or R1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _    | 3   |

| Rn<br>n                                                     | Byte register R0-R7 of the currently selected register bank<br>Byte register index: n = 0-7                                                                                                                                                                                                                                                                                                                                                                                                                                      | _    | 3   |

| Rm<br>Rmd<br>Rms<br>m, md, ms                               | Byte register R0-R15 of the currently selected register file<br>Destination register<br>Source register<br>Byte register index: m, md, ms = 0-15                                                                                                                                                                                                                                                                                                                                                                                 | 3    | -   |

| WRj<br>WRjd<br>WRjs<br>at WRj<br>at WRj +dis16<br>j, jd, js | Word register WR0, WR2,, WR30 of the currently selected register<br>file<br>Destination register<br>Source register<br>A memory location (00:0000h-00:FFFFh) addressed indirectly<br>through word register WR0-WR30, is the target address for jump<br>instructions.<br>A memory location (00:0000h-00:FFFFh) addressed indirectly<br>through word register (WR0-WR30) + 16-bit signed (two's<br>complement) displacement value<br>Word register index: j, jd, js = 0-30                                                         | 3    | _   |

| DRk<br>DRkd<br>DRks<br>at DRk<br>at DRk +dis16<br>k, kd, ks | Dword register DR0, DR4,, DR28, DR56, DR60 of the currently<br>selected register file<br>Destination register<br>Source register<br>A memory location (00:0000h-FF:FFFFh) addressed indirectly<br>through dword register DR0-DR28, DR56 and DR60, is the target<br>address for jump instruction<br>A memory location (00:0000h-FF:FFFFh) addressed indirectly<br>through dword register (DR0-DR28, DR56, DR60) + 16-bit (two's<br>complement) signed displacement value<br>Dword register index: k, kd, ks = 0, 4, 8, 28, 56, 60 | 3    | _   |

#### Table 19. Notation for Register Operands

4. If this instruction addresses external memory location, add 2(N+2) to the number of states (N: number of wait states).

$IncrementINC < dest>dest opnd \leftarrow dest opnd + 1$

IncrementINC <dest>, <src>dest opnd  $\leftarrow$  dest opnd + src opnd

$DecrementDEC < dest>dest opnd \leftarrow dest opnd - 1$

$\texttt{DecrementDEC <dest>, <src>dest opnd \leftarrow dest opnd - src opnd}$

|            |                                              |                                          | Binary | Mode             | Source Mode |                  |

|------------|----------------------------------------------|------------------------------------------|--------|------------------|-------------|------------------|

| Mnemonic   | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                 | Bytes  | States           | Bytes       | States           |

|            | A                                            | ACC by 1                                 | 1      | 1                | 1           | 1                |

| INC<br>DEC | Rn                                           | Register by 1                            | 1      | 1                | 2           | 2                |

|            | dir8                                         | Direct address (on-chip RAM or SFR) by 1 | 2      | 2 <sup>(2)</sup> | 2           | 2 <sup>(2)</sup> |

|            | at Ri                                        | Indirect address by 1                    | 1      | 3                | 2           | 4                |

| INC        | Rm, #short                                   | Byte register by 1, 2, or 4              | 3      | 2                | 2           | 1                |

| DEC        | WRj, #short                                  | Word register by 1, 2, or 4              | 3      | 2                | 2           | 1                |

| INC        | DRk, #short                                  | Double word register by 1, 2, or 4       | 3      | 4                | 2           | 3                |

| DEC        | DRk, #short                                  | Double word register by 1, 2, or 4       | 3      | 5                | 2           | 4                |

| INC        | DPTR                                         | Data pointer by 1                        | 1      | 1                | 1           | 1                |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

| MOV | WRj, at WRj<br>+dis24 | Indirect with 16-bit displacement (16M) to word register | 5 | 8 <sup>(5)</sup> | 4 | 7 <sup>(5)</sup> |

|-----|-----------------------|----------------------------------------------------------|---|------------------|---|------------------|

| MOV | at WRj +dis16,<br>Rm  | Byte register to indirect with 16-bit displacement (64K) | 5 | 6 <sup>(4)</sup> | 4 | 5 <sup>(4)</sup> |

| MOV | at WRj +dis16,<br>WRj | Word register to indirect with 16-bit displacement (64K) | 5 | 7 <sup>(5)</sup> | 4 | 6 <sup>(5)</sup> |

| MOV | at DRk +dis24,<br>Rm  | Byte register to indirect with 16-bit displacement (16M) | 5 | 7 <sup>(4)</sup> | 4 | 6 <sup>(4)</sup> |

| MOV | at DRk +dis24,<br>WRj | Word register to indirect with 16-bit displacement (16M) | 5 | 8(5)             | 4 | 7 <sup>(5)</sup> |

Notes: 1. Instructions that move bits are in Table 27.

2. Move instructions unique to the C251 Architecture.

3. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

4. If this instruction addresses external memory location, add N+2 to the number of states (N: number of wait states).

5. If this instruction addresses external memory location, add 2(N+1) to the number of states (N: number of wait states).

6. If this instruction addresses external memory location, add 4(N+2) to the number of states (N: number of wait states).

|          |                                              |                                                    | Binary | Mode             | Source | e Mode           |

|----------|----------------------------------------------|----------------------------------------------------|--------|------------------|--------|------------------|

| Mnemonic | <dest>,<br/><src><sup>(1)</sup></src></dest> | Comments                                           | Bytes  | States           | Bytes  | State            |

|          | A, Rn                                        | ACC and register                                   | 1      | 3                | 2      | 4                |

| ХСН      | A, dir8                                      | ACC and direct address (on-chip RAM or SFR)        | 2      | 3 <sup>(3)</sup> | 2      | 3 <sup>(3)</sup> |

|          | A, at Ri                                     | ACC and indirect address                           | 1      | 4                | 2      | 5                |

| XCHD     | A, at Ri                                     | ACC low nibble and indirect address (256 bytes)    | 1      | 4                | 2      | 5                |

|          | dir8                                         | Push direct address onto stack                     | 2      | 2 <sup>(2)</sup> | 2      | 2(2              |

|          | #data                                        | Push immediate data onto stack                     | 4      | 4                | 3      | 3                |

| PUSH     | #data16                                      | Push 16-bit immediate data onto stack              | 5      | 5                | 4      | 5                |

| F 0311   | Rm                                           | Push byte register onto stack                      | 3      | 4                | 2      | 3                |

|          | WRj                                          | Push word register onto stack                      | 3      | 5                | 2      | 4                |

|          | DRk                                          | Push double word register onto stack               | 3      | 9                | 2      | 8                |

|          | dir8                                         | Pop direct address (on-chip RAM or SFR) from stack | 2      | 3 <sup>(2)</sup> | 2      | 3(2              |

| POP      | Rm                                           | Pop byte register from stack                       | 3      | 3                | 2      | 2                |

|          | WRj                                          | Pop word register from stack                       | 3      | 5                | 2      | 4                |

|          | DRk                                          | Pop double word register from stack                | 3      | 9                | 2      | 8                |

#### Table 28. Summary of Exchange, Push and Pop Instructions

Exchange bytesXCH A, <src>(A)  $\leftrightarrow$  src opnd

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. If this instruction addresses an I/O Port (Px, x = 0-3), add 1 to the number of states. Add 2 if it addresses a Peripheral SFR.

3. If this instruction addresses an I/O Port (Px, x = 0-3), add 2 to the number of states. Add 3 if it addresses a Peripheral SFR.

| Table 29. | Summar | of Conditional Jump Instructions ( | (1/2) |

|-----------|--------|------------------------------------|-------|

|-----------|--------|------------------------------------|-------|

| Jump conditional on statusJcc rel(PC) $\leftarrow$ (PC) + size (instr);<br>IF [cc] THEN (PC) $\leftarrow$ (PC) + rel |                           |                                        |        |                    |       |                    |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------|--------|--------------------|-------|--------------------|--|

|                                                                                                                      | <dest>,</dest>            |                                        | Binary | Binary Mode        |       | Source Mode        |  |

| Mnemonic                                                                                                             | <src><sup>(1)</sup></src> | Comments                               | Bytes  | States             | Bytes | States             |  |

| JC                                                                                                                   | rel                       | Jump if carry                          | 2      | 1/4 <sup>(3)</sup> | 2     | 1/4 <sup>(3)</sup> |  |

| JNC                                                                                                                  | rel                       | Jump if not carry                      | 2      | 1/4 <sup>(3)</sup> | 2     | 1/4 <sup>(3)</sup> |  |

| JE                                                                                                                   | rel                       | Jump if equal                          | 3      | 2/5 <sup>(3)</sup> | 2     | 1/4 <sup>(3)</sup> |  |

| JNE                                                                                                                  | rel                       | Jump if not equal                      | 3      | 2/5 <sup>(3)</sup> | 2     | 1/4 <sup>(3)</sup> |  |

| JG                                                                                                                   | rel                       | Jump if greater than                   | 3      | 2/5 <sup>(3)</sup> | 2     | 1/4 <sup>(3)</sup> |  |

| JLE                                                                                                                  | rel                       | Jump if less than, or equal            | 3      | 2/5 <sup>(3)</sup> | 2     | 1/4 <sup>(3)</sup> |  |

| JSL                                                                                                                  | rel                       | Jump if less than (signed)             | 3      | 2/5 <sup>(3)</sup> | 2     | 1/4 <sup>(3)</sup> |  |

| JSLE                                                                                                                 | rel                       | Jump if less than, or equal (signed)   | 3      | 2/5 <sup>(3)</sup> | 2     | 1/4 <sup>(3)</sup> |  |

| JSG                                                                                                                  | rel                       | Jump if greater than (signed)          | 3      | 2/5 <sup>(3)</sup> | 2     | 1/4 <sup>(3)</sup> |  |

| JSGE                                                                                                                 | rel                       | Jump if greater than or equal (signed) | 3      | 2/5 <sup>(3)</sup> | 2     | 1/4 <sup>(3)</sup> |  |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

2. States are given as jump not-taken/taken.

3. In internal execution only, add 1 to the number of states of the 'jump taken' if the destination address is internal and odd.

Add 3 if it addresses a Peripheral SFR.

- 5. If this instruction addresses an I/O Port (Px, x = 0-3), add 3 to the number of states. Add 5 if it addresses a Peripheral SFR.

- 6. In internal execution only, add 1 to the number of states of the 'jump taken' if the destination address is internal and odd.

#### Table 31. Summary of Unconditional Jump Instructions

Absolute jumpAJMP <src>(PC)  $\leftarrow$  (PC) +2; (PC)<sub>10:0</sub>  $\leftarrow$  src opnd Extended jumpEJMP <src>(PC)  $\leftarrow$  (PC) + size (instr); (PC)<sub>23:0</sub>  $\leftarrow$  src opnd Long jumpLJMP <src>(PC)  $\leftarrow$  (PC) + size (instr); (PC)<sub>15:0</sub>  $\leftarrow$  src opnd Short jumpSJMP rel(PC)  $\leftarrow$  (PC) +2; (PC)  $\leftarrow$  (PC) +rel Jump indirectJMP at A +DPTR(PC)<sub>23:16</sub>  $\leftarrow$  FFh; (PC)<sub>15:0</sub>  $\leftarrow$  (A) + (DPTR) No operationNOP(PC)  $\leftarrow$  (PC) +1

|          | -dott                     |                                    | <dest>,</dest> |                     | Binary Mode |                     | Source Mode |  |

|----------|---------------------------|------------------------------------|----------------|---------------------|-------------|---------------------|-------------|--|

| Mnemonic | <src><sup>(1)</sup></src> | Comments                           | Bytes          | States              | Bytes       | States              |             |  |

| AJMP     | addr11                    | Absolute jump                      | 2              | 3 <sup>(2)(3)</sup> | 2           | 3 <sup>(2)(3)</sup> |             |  |

| EJMP     | addr24                    | Extended jump                      | 5              | 6 <sup>(2)(4)</sup> | 4           | 5 <sup>(2)(4)</sup> |             |  |

| EJIVIP   | at DRk                    | Extended jump (indirect)           | 3              | 7 <sup>(2)(4)</sup> | 2           | 6 <sup>(2)(4)</sup> |             |  |

| LJMP     | at WRj                    | Long jump (indirect)               | 3              | 6 <sup>(2)(4)</sup> | 2           | 5 <sup>(2)(4)</sup> |             |  |

| LJIMP    | addr16                    | Long jump (direct address)         | 3              | 5 <sup>(2)(4)</sup> | 3           | 5 <sup>(2)(4)</sup> |             |  |

| SJMP     | rel                       | Short jump (relative address)      | 2              | 4 <sup>(2)(4)</sup> | 2           | 4 <sup>(2)(4)</sup> |             |  |

| JMP      | at A +DPTR                | Jump indirect relative to the DPTR | 1              | 5 <sup>(2)(4)</sup> | 1           | 5 <sup>(2)(4)</sup> |             |  |

| NOP      |                           | No operation (Jump never)          | 1              | 1                   | 1           | 1                   |             |  |

Notes: 1. A shaded cell denotes an instruction in the C51 Architecture.

- 2. In internal execution only, add 1 to the number of states if the destination address is internal and odd.

- 3. Add 2 to the number of states if the destination address is external.

- 4. Add 3 to the number of states if the destination address is external.

To preserve the secrecy of the encryption key byte sequence, the Encryption Array can not be verified.

- Notes: 1. When a MOVC instruction is executed, the content of the ROM is not encrypted. In order to fully protect the user program code, the lock bit level 1 (see Table 33) must always be set when encryption is used.

- 2. If the encryption feature is implemented, the portion of the on-chip code memory that does not contain program code should be filled with "random" byte values to prevent the encryption key sequence from being revealed.

**Signature Bytes** The TSC80251G2D derivatives contain factory-programmed Signature Bytes. These bytes are located in non-volatile memory outside the memory address space at 30h, 31h, 60h and 61h. To read the Signature Bytes, perform the procedure described in section Verify Algorithm, using the verify signature mode (see Table 37). Signature byte values are listed in Table 35.

|              |                                    | Signature Address | Signature Data |

|--------------|------------------------------------|-------------------|----------------|

| Vendor       | Atmel                              | 30h               | 58h            |

| Architecture | C251                               | 31h               | 40h            |

| Memory       | 32 kilobytes EPROM or<br>OTPROM    | 60h               | F7h            |

| Niemory      | 32 kilobytes MaskROM<br>or ROMless |                   | 77h            |

| Revision     | TSC80251G2D<br>derivative          | 61h               | FDh            |

Table 35. Signature Bytes (Electronic ID)

# **Programming Algorithm** Figure 6 shows the hardware setup needed to program the TSC87251G2D EPROM/OTPROM areas:

- The chip has to be put under reset and maintained in this state until completion of the programming sequence.

- PSEN# and the other control signals (ALE and Port 0) have to be set to a high level.

- Then PSEN# has to be to forced to a low level after two clock cycles or more and it

has to be maintained in this state until the completion of the programming sequence

(see below).

- The voltage on the EA# pin must be set to V<sub>DD</sub>.

- The programming mode is selected according to the code applied on Port 0 (see Table 36). It has to be applied until the completion of this programming operation.

- The programming address is applied on Ports 1 and 3 which are respectively the Most Significant Byte (MSB) and the Least Significant Byte (LSB) of the address.

- The programming data are applied on Port 2.

- The EPROM Programming is done by raising the voltage on the EA# pin to V<sub>PP</sub>, then by generating a low level pulse on ALE/PROG# pin.

- The voltage on the EA# pin must be lowered to V<sub>DD</sub> before completing the programming operation.

- It is possible to alternate programming and verifying operation (See Paragraph Verify Algorithm). Please make sure the voltage on the EA# pin has actually been lowered to V<sub>DD</sub> before performing the verifying operation.

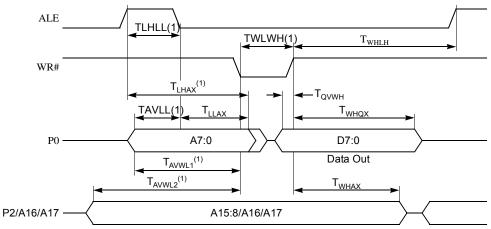

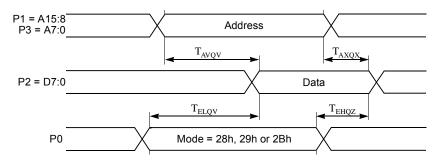

Figure 10. External Bus Cycle: Data Write (Non-Page Mode)

Waveforms in Page Mode

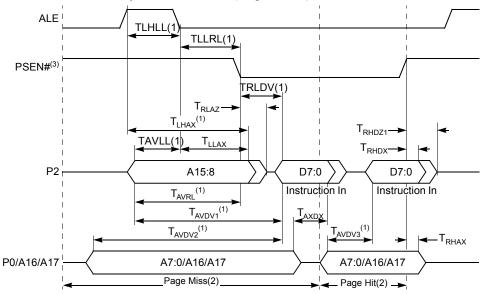

Figure 11. External Bus Cycle: Code Fetch (Page Mode)

- Note: 1. The value of this parameter depends on wait states. See Table 39 and Table 40.

- A page hit (i.e., a code fetch to the same 256-byte "page" as the previous code fetch) requires one state (2·T<sub>OSC</sub>);

a page miss requires two states ( $4 \cdot T_{OSC}$ ).

During a sequence of page hits, PSEN# remains low until the end of the last page-hit cycle.

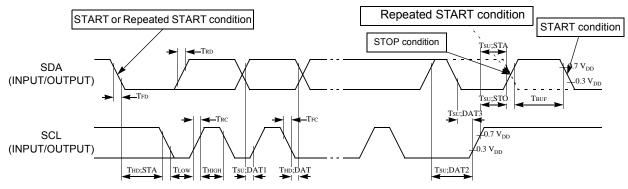

### AC Characteristics - SSLC: TWI Interface

#### Timings

Table 47. TWI Interface AC Timing;  $V_{\text{DD}}$  = 2.7 to 5.5 V,  $T_{\text{A}}$  = -40 to 85°C

|           |                                                   | INPUT                   | OUTPUT                        |

|-----------|---------------------------------------------------|-------------------------|-------------------------------|

| Symbol    | Parameter                                         | Min Max                 | Min Max                       |

| THD; STA  | Start condition hold time                         | 14·Tclcl <sup>(4)</sup> | 4.0 μs <sup>(1)</sup>         |

| TLOW      | SCL low time                                      | 16·Tclcl <sup>(4)</sup> | 4.7 μs <sup>(1)</sup>         |

| Тнідн     | SCL high time                                     | 14·Tclcl <sup>(4)</sup> | 4.0 μs <sup>(1)</sup>         |

| Trc       | SCL rise time                                     | 1 μs                    | _(2)                          |

| TFC       | SCL fall time                                     | 0.3 μs                  | 0.3 μs <sup>(3)</sup>         |

| Tsu; DAT1 | Data set-up time                                  | 250 ns                  | 20.TCLCL <sup>(4)</sup> - TRD |

| Tsu; DAT2 | SDA set-up time (before repeated START condition) | 250 ns                  | 1 μs <sup>(1)</sup>           |

| Ts∪; DAT3 | SDA set-up time (before STOP condition)           | 250 ns                  | 8.TCLCL <sup>(4)</sup>        |

| THD; DAT  | Data hold time                                    | 0 ns                    | 8.TCLCL <sup>(4)</sup> - TFC  |

| Ts∪; STA  | Repeated START set-up time                        | 14·Tclcl <sup>(4)</sup> | 4.7 μs <sup>(1)</sup>         |

| Tsu; STO  | STOP condition set-up time                        | 14·Tclcl <sup>(4)</sup> | 4.0 μs <sup>(1)</sup>         |

| Твиғ      | Bus free time                                     | 14·Tclcl <sup>(4)</sup> | 4.7 μs <sup>(1)</sup>         |

| Trd       | SDA rise time                                     | 1 μs                    | _(2)                          |

| Tfd       | SDA fall time                                     | 0.3 μs                  | 0.3 μs <sup>(3)</sup>         |

Notes: 1. At 100 kbit/s. At other bit-rates this value is inversely proportional to the bit-rate of 100 kbit/s.

- 2. Determined by the external bus-line capacitance and the external bus-line pull-up resistor, this must be < 1  $\mu s.$

- Spikes on the SDA and SCL lines with a duration of less than 3. TCLCL will be filtered out. Maximum capacitance on bus-lines SDA and SCL = 400 pF.

- 4. TCLCL =  $T_{OSC}$  = one oscillator clock period.

#### Waveforms

#### Figure 18. TWI Waveforms

# 54 AT/TSC8x251G2D

#### Figure 24. EPROM Verifying Waveforms

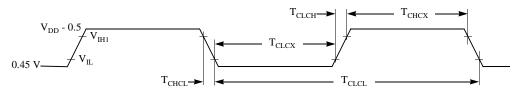

### AC Characteristics - External Clock Drive and Logic Level References

**Definition of Symbols**

Table 53. External Clock Timing Symbol Definitions

| Signals |         |  |  |  |  |

|---------|---------|--|--|--|--|

| С       | C Clock |  |  |  |  |

|         |         |  |  |  |  |

|         |         |  |  |  |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| Н          | High            |  |  |  |

| L          | Low             |  |  |  |

| Х          | No Longer Valid |  |  |  |

#### Timings

### **Table 54.** External Clock AC Timings; $V_{DD}$ = 4.5 to 5.5 V, $T_A$ = -40 to +85°C

| Symbol            | Parameter            | Min | Max | Unit |

|-------------------|----------------------|-----|-----|------|

| F <sub>osc</sub>  | Oscillator Frequency |     | 24  | MHz  |

| T <sub>CHCX</sub> | High Time            | 10  |     | ns   |

| T <sub>CLCX</sub> | Low Time             | 10  |     | ns   |

| T <sub>CLCH</sub> | Rise Time            | 3   |     | ns   |

| T <sub>CHCL</sub> | Fall Time            | 3   |     | ns   |

#### Waveforms

Figure 25. External Clock Waveform

- Notes: 1. During AC testing, all inputs are driven at  $V_{DD}$  -0.5 V for a logic 1 and 0.45 V for a logic 0.

- 2. Timing measurements are made on all outputs at  $V_{\rm IH}$  min for a logic 1 and  $V_{\rm IL}$  max for a logic 0.

## **DC Characteristics**

## High Speed Versions - Commercial, Industrial, and Automotive

| Symbol           | Parameter                                                                                   | Min                                                                     | Typical <sup>(4)</sup> | Max                       | Units | Test Conditions                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------|---------------------------|-------|-----------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage<br>(except EA#, SCL, SDA)                                                 | -0.5                                                                    |                        | 0.2·V <sub>DD</sub> - 0.1 | V     |                                                                                                                       |

| $V_{IL1}^{(5)}$  | Input Low Voltage<br>(SCL, SDA)                                                             | -0.5                                                                    |                        | 0.3·V <sub>DD</sub>       | V     |                                                                                                                       |

| $V_{\text{IL2}}$ | Input Low Voltage<br>(EA#)                                                                  | 0                                                                       |                        | 0.2·V <sub>DD</sub> - 0.3 | V     |                                                                                                                       |

| V <sub>IH</sub>  | Input high Voltage<br>(except XTAL1, RST, SCL, SDA)                                         | 0.2·V <sub>DD</sub> + 0.9                                               |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                       |

| $V_{IH1}^{(5)}$  | Input high Voltage<br>(XTAL1, RST, SCL, SDA)                                                | 0.7·V <sub>DD</sub>                                                     |                        | V <sub>DD</sub> + 0.5     | V     |                                                                                                                       |

| V <sub>OL</sub>  | Output Low Voltage<br>(Ports 1, 2, 3)                                                       |                                                                         |                        | 0.3<br>0.45<br>1.0        | V     | $I_{OL} = 100 \ \mu A^{(1)(2)}$ $I_{OL} = 1.6 \ m A^{(1)(2)}$ $I_{OL} = 3.5 \ m A^{(1)(2)}$                           |

| V <sub>OL1</sub> | Output Low Voltage<br>(Ports 0, ALE, PSEN#, Port 2 in Page Mode during<br>External Address) |                                                                         |                        | 0.3<br>0.45<br>1.0        | V     | $I_{OL} = 200 \ \mu A^{(1)(2)}$ $I_{OL} = 3.2 \ m A^{(1)(2)}$ $I_{OL} = 7.0 \ m A^{(1)(2)}$                           |

| V <sub>OH</sub>  | Output high Voltage<br>(Ports 1, 2, 3, ALE, PSEN#)                                          | V <sub>DD</sub> - 0.3<br>V <sub>DD</sub> - 0.7<br>V <sub>DD</sub> - 1.5 |                        |                           | V     | $\begin{split} I_{OH} &= -10 \ \mu A^{(3)} \\ I_{OH} &= -30 \ \mu A^{(3)} \\ I_{OH} &= -60 \ \mu A^{(3)} \end{split}$ |

| V <sub>OH1</sub> | Output high Voltage<br>(Port 0, Port 2 in Page Mode during External Address)                | V <sub>DD</sub> - 0.3<br>V <sub>DD</sub> - 0.7<br>V <sub>DD</sub> - 1.5 |                        |                           | V     | I <sub>OH</sub> = -200 μA<br>I <sub>OH</sub> = -3.2 mA<br>I <sub>OH</sub> = -7.0 mA                                   |

| $V_{RET}$        | V <sub>DD</sub> data retention limit                                                        |                                                                         |                        | 1.8                       | V     |                                                                                                                       |

| I <sub>IL0</sub> | Logical 0 Input Current<br>(Ports 1, 2, 3)                                                  |                                                                         |                        | - 50                      | μA    | V <sub>IN</sub> = 0.45 V                                                                                              |

| I <sub>IL1</sub> | Logical 1 Input Current<br>(NMI)                                                            |                                                                         |                        | + 50                      | μA    | V <sub>IN</sub> = V <sub>DD</sub>                                                                                     |

| I <sub>LI</sub>  | Input Leakage Current<br>(Port 0)                                                           |                                                                         |                        | ± 10                      | μA    | 0.45 V < V <sub>IN</sub> < V <sub>DD</sub>                                                                            |

| I <sub>TL</sub>  | Logical 1-to-0 Transition Current<br>(Ports 1, 2, 3 - AWAIT#)                               |                                                                         |                        | - 650                     | μA    | V <sub>IN</sub> = 2.0 V                                                                                               |

| R <sub>RST</sub> | RST Pull-Down Resistor                                                                      | 40                                                                      | 110                    | 225                       | kΩ    |                                                                                                                       |

| CIO              | Pin Capacitance                                                                             |                                                                         | 10                     |                           | pF    | T <sub>A</sub> = 25°C                                                                                                 |

| I <sub>DD</sub>  | Operating Current                                                                           |                                                                         | 20<br>25<br>35         | 25<br>30<br>40            | mA    | $F_{OSC}$ = 12 MHz<br>$F_{OSC}$ = 16 MHz<br>$F_{OSC}$ = 24 MHz                                                        |

| I <sub>DL</sub>  | Idle Mode Current                                                                           |                                                                         | 5<br>6.5<br>9.5        | 8<br>10<br>14             | mA    | $F_{OSC}$ = 12 MHz<br>$F_{OSC}$ = 16 MHz<br>$F_{OSC}$ = 24 MHz                                                        |

| I <sub>PD</sub>  | Power-Down Current                                                                          |                                                                         | 2                      | 20                        | μA    | $V_{RET} < V_{DD} < 5.5 V$                                                                                            |

| $V_{PP}$         | Programming supply voltage                                                                  | 12.5                                                                    |                        | 13                        | V     | $T_A = 0$ to +40°C                                                                                                    |

| I <sub>PP</sub>  | Programming supply current                                                                  | 1                                                                       |                        | 75                        | mA    | T <sub>A</sub> = 0 to +40°C                                                                                           |

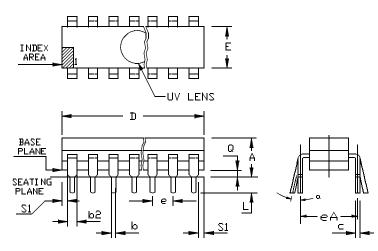

CDIL 40 with Window -Mechanical Outline

Figure 34. Ceramic Dual In Line

Table 58. CDIL Package Size

|    | ММ            |        | In          | ch    |

|----|---------------|--------|-------------|-------|

|    | Min           | Мах    | Min         | Мах   |

| A  | -             | 5.71   | -           | .225  |

| b  | 0.36          | 0.58   | .014        | .023  |

| b2 | 1.14          | 1.65   | .045        | .065  |

| с  | 0.20          | 0.38   | .008        | .015  |

| D  | -             | 53.47  | -           | 2.105 |

| E  | 13.06         | 15.37  | .514        | .605  |

| e  | 2.54 B.S.C.   |        | .100 B.S.C. |       |

| eA | 15.24         | B.S.C. | .600 B.S.C. |       |

| L  | 3.18          | 5.08   | .125        | .200  |

| Q  | 0.38          | 1.40   | .015        | .055  |

| S1 | 0.13          | -      | .005        | -     |

| а  | 0 - 15 0 - 15 |        |             | 15    |

| N  | 40            |        |             |       |

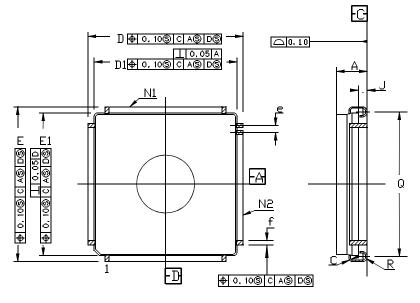

Figure 36. Ceramic Quad Pack J

### CQPJ 44 with Window -Mechanical Outline

| Table 60. | CQPJ Package Size |

|-----------|-------------------|

|-----------|-------------------|

|         | ММ       |       | Inch     |      |

|---------|----------|-------|----------|------|

|         | Min      | Max   | Min      | Max  |

| A       | -        | 4.90  | -        | .193 |

| С       | 0.15     | 0.25  | .006     | .010 |

| D - E   | 17.40    | 17.55 | .685     | .691 |

| D1 - E1 | 16.36    | 16.66 | .644     | .656 |

| e       | 1.27 TYP |       | .050 TYP |      |

| f       | 0.43     | 0.53  | .017     | .021 |

| J       | 0.86     | 1.12  | .034     | .044 |

| Q       | 15.49    | 16.00 | .610     | .630 |

| R       | 0.86 TYP |       | .034 TYP |      |

| N1      | 11       |       | 11       |      |

| N2      | 11       |       | 11       |      |

| Part Number <sup>(1)</sup>        | ROM         | Description                            |  |  |  |

|-----------------------------------|-------------|----------------------------------------|--|--|--|

| Low Voltage Versions 2.7 to 5.5 V |             |                                        |  |  |  |

| TSC251G2Dxxx-L16CB                | 32K MaskROM | 16 MHz, Commercial 0° to 70°C, PLCC 44 |  |  |  |

| TSC251G2Dxxx-L16CE                | 32K MaskROM | 16 MHz, Commercial 0° to 70°C, VQFP 44 |  |  |  |

| AT251G2Dxxx-SLSUL                 | 32K MaskROM | 16 MHz, Industrial & Green, PLCC 44    |  |  |  |

| AT251G2Dxxx-RLTUL                 | 32K MaskROM | 16 MHz, Industrial & Green, VQFP 44    |  |  |  |

Note: 1. xxx: means ROM code, is Cxxx in case of encrypted code.

### AT/TSC87251G2D OTPROM

| Part Number                                                 | ROM        | Description                                      |  |  |  |

|-------------------------------------------------------------|------------|--------------------------------------------------|--|--|--|

| High Speed Versions 4.5 to 5.5 V, Commercial and Industrial |            |                                                  |  |  |  |

| TSC87251G2D-16CB                                            | 32K OTPROM | 16 MHz, Commercial 0° to 70°C, PLCC 44           |  |  |  |

| TSC87251G2D-24CB                                            | 32K OTPROM | 24 MHz, Commercial 0° to 70°C, PLCC 44           |  |  |  |

| TSC87251G2D-24CED                                           | 32K OTPROM | 24 MHz, Commercial 0° to 70°C, VQFP 44           |  |  |  |

| TSC87251G2D-24IA                                            | 32K OTPROM | 24 MHz, Industrial -40° to 85°C, PDIL 40         |  |  |  |

| TSC87251G2D-24IB                                            | 32K OTPROM | 24 MHz, Industrial -40° to 85°C, PLCC 44         |  |  |  |

| AT87251G2D-SLSUM                                            | 32K OTPROM | 24 MHz, Industrial & Green -40° to 85°C, PLCC 44 |  |  |  |

| AT87251G2D-3CSUM                                            | 32K OTPROM | 24 MHz, Industrial & Green -40° to 85°C, PDIL 40 |  |  |  |

| AT87251G2D-RLTUM                                            | 32K OTPROM | 24 MHz, Industrial & Green -40° to 85°C, VQFP 44 |  |  |  |

| Low Voltage Versions 2.7 to 5.5 V                           |            |                                                  |  |  |  |

| TSC87251G2D-L16CB                                           | 32K OTPROM | 16 MHz, Commercial 0° to 70°C, PLCC 44           |  |  |  |

| TSC87251G2D-L16CED                                          | 32K OTPROM | 16 MHz, Commercial 0° to 70°C, VQFP 44           |  |  |  |

| AT87251G2D-SLSUL                                            | 32K OTPROM | 16 MHz, Industrial & Green, 0° to 70°C, PLCC 44  |  |  |  |

| AT87251G2D-RLTUL                                            | 32K OTPROM | 16 MHz, Industrial & Green, 0° to 70°C, VQFP 44  |  |  |  |

## **Document Revision History**

**Changes from** 1. Added automotive qualification, and ordering information for ROM product version.

- 4135D to 4135E

- 1. Absolute Maximum Ratings added for automotive product version.

Changes from 4135E to 4135F

AIMEL