#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 4MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 13                                                                      |

| Program Memory Size        | 896B (512 x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64 x 8                                                                  |

| RAM Size                   | 36 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                            |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 18-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f83-04-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

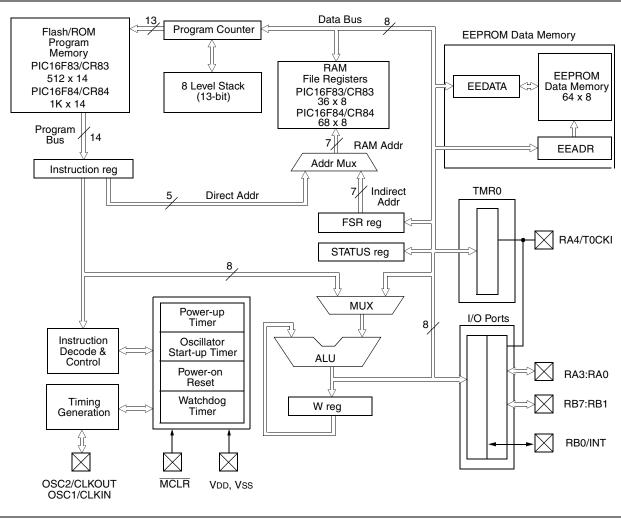

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register), and the other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram for the PIC16F8X is shown in Figure 3-1, its corresponding pin description is shown in Table 3-1.

#### 3.1 <u>Clocking Scheme/Instruction Cycle</u>

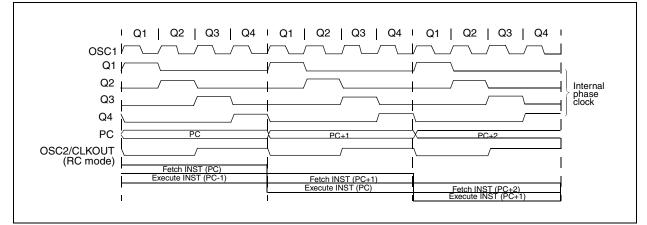

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

#### 3.2 Instruction Flow/Pipelining

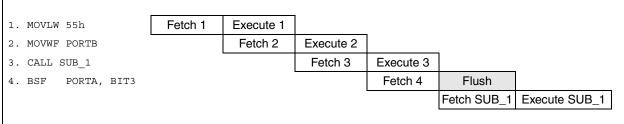

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### 4.3 Program Counter: PCL and PCLATH

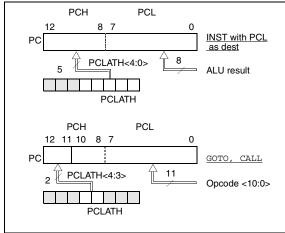

The Program Counter (PC) is 13-bits wide. The low byte is the PCL register, which is a readable and writable register. The high byte of the PC (PC<12:8>) is not directly readable nor writable and comes from the PCLATH register. The PCLATH (PC latch high) register is a holding register for PC<12:8>. The contents of PCLATH are transferred to the upper byte of the program counter when the PC is loaded with a new value. This occurs during a CALL, GOTO or a write to PCL. The high bits of PC are loaded from PCLATH as shown in Figure 4-1.

#### FIGURE 4-1: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 word block). Refer to the application note *"Implementing a Table Read"* (AN556).

#### 4.3.2 PROGRAM MEMORY PAGING

The PIC16F83 and PIC16CR83 have 512 words of program memory. The PIC16F84 and PIC16CR84 have 1K of program memory. The CALL and GOTO instructions have an 11-bit address range. This 11-bit address range allows a branch within a 2K program memory page size. For future PIC16F8X program memory expansion, there must be another two bits to specify the program memory page. These paging bits come from the PCLATH<4:3> bits (Figure 4-1). When doing a CALL or a GOTO instruction, the user must ensure that these page bits (PCLATH<4:3>) are programmed to the desired program memory page. If a CALL instruction (or interrupt) is executed, the entire 13-bit PC is "pushed" onto the stack (see next section). Therefore, manipulation of the PCLATH<4:3> is not required for the return instructions (which "pops" the PC from the stack).

| Note: | The PIC16F8X ignores the PCLATH<4:3>    |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|--|

|       | bits, which are used for program memory |  |  |  |  |  |  |  |  |

|       | pages 1, 2 and 3 (0800h - 1FFFh). The   |  |  |  |  |  |  |  |  |

|       | use of PCLATH<4:3> as general purpose   |  |  |  |  |  |  |  |  |

|       | R/W bits is not recommended since this  |  |  |  |  |  |  |  |  |

|       | may affect upward compatibility with    |  |  |  |  |  |  |  |  |

|       | future products.                        |  |  |  |  |  |  |  |  |

#### 4.4 Stack

The PIC16FXX has an 8 deep x 13-bit wide hardware stack (Figure 4-1). The stack space is not part of either program or data space and the stack pointer is not readable or writable.

The entire 13-bit PC is "pushed" onto the stack when a CALL instruction is executed or an interrupt is acknowledged. The stack is "popped" in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a push or a pop operation.

| Note: | There are no instruction mnemonics         |

|-------|--------------------------------------------|

|       | called push or pop. These are actions that |

|       | occur from the execution of the CALL,      |

|       | RETURN, RETLW, and RETFIE instruc-         |

|       | tions, or the vectoring to an interrupt    |

|       | address.                                   |

The stack operates as a circular buffer. That is, after the stack has been pushed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

If the stack is effectively popped nine times, the PC value is the same as the value from the first pop.

**Note:** There are no status bits to indicate stack overflow or stack underflow conditions.

#### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch is unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output current may damage the chip.

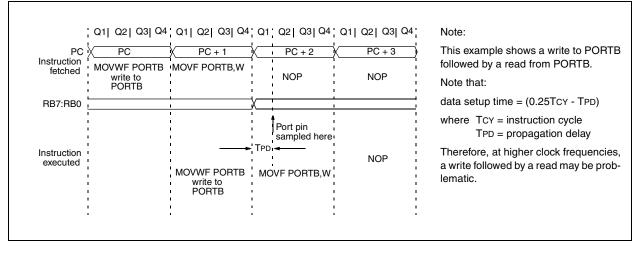

## 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-5). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such that the pin voltage stabilizes (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}\,,\,\,{\tt BSF},\, etc.)$  on an I/O port.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ;PORTB<7:6> have external pull-ups and are ;not connected to other circuitry

| ' |     |        |       |   |      |       |      |      |

|---|-----|--------|-------|---|------|-------|------|------|

| ; |     |        |       |   | PORT | latch | PORT | pins |

| ; |     |        |       |   |      |       |      |      |

|   | BCF | PORTB, | 7     | ; | 01pp | ppp   | 11pp | ppp  |

|   | BCF | PORTB, | 6     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BSF | STATUS | , RPO | ; |      |       |      |      |

|   | BCF | TRISB, | 7     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BCF | TRISB, | 6     | ; | 10pp | ppp   | 10pp | ppp  |

| : |     |        |       |   |      |       |      |      |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

#### FIGURE 5-5: SUCCESSIVE I/O OPERATION

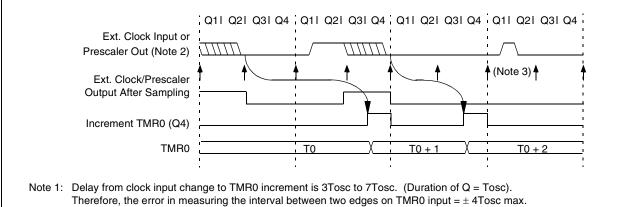

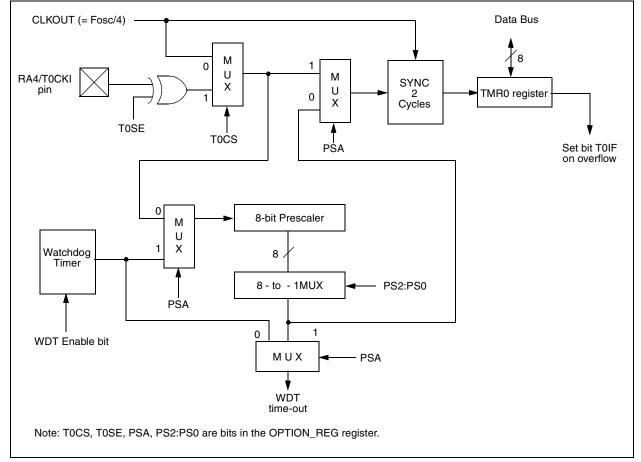

2: External clock if no prescaler selected, Prescaler output otherwise.

3: The arrows ↑ indicate where sampling occurs. A small clock pulse may be missed by sampling.

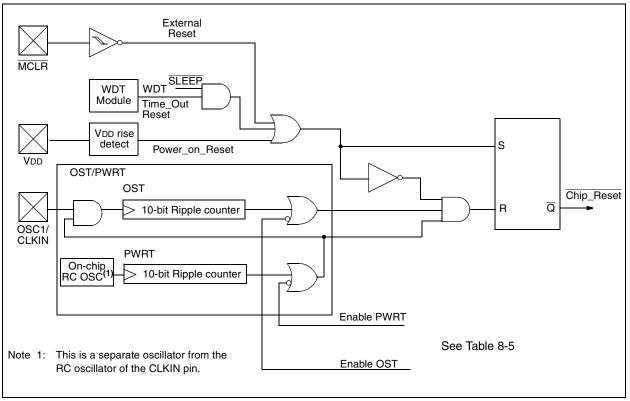

#### FIGURE 8-8: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### TABLE 8-3 RESET CONDITION FOR PROGRAM COUNTER AND THE STATUS REGISTER

| Condition                           | Program Counter       | STATUS Register |

|-------------------------------------|-----------------------|-----------------|

| Power-on Reset                      | 000h                  | 0001 1xxx       |

| MCLR Reset during normal operation  | 000h                  | 000u uuuu       |

| MCLR Reset during SLEEP             | 000h                  | 0001 0uuu       |

| WDT Reset (during normal operation) | 000h                  | 0000 luuu       |

| WDT Wake-up                         | PC + 1                | uuu0 0uuu       |

| Interrupt wake-up from SLEEP        | PC + 1 <sup>(1)</sup> | uuul 0uuu       |

Legend: u = unchanged, x = unknown.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| Register   | Address | Power-on Reset | MCLR Reset during:<br>– normal operation<br>– SLEEP<br>WDT Reset during nor-<br>mal operation | Wake-up from SLEEP:<br>– through interrupt<br>– through WDT Time-out |

|------------|---------|----------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| W          | _       | XXXX XXXX      | սսսս սսսս                                                                                     | սսսս սսսս                                                            |

| INDF       | 00h     |                |                                                                                               |                                                                      |

| TMR0       | 01h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| PCL        | 02h     | 0000h          | 0000h                                                                                         | PC + 1 <sup>(2)</sup>                                                |

| STATUS     | 03h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                                      | uuuq quuu <sup>(3)</sup>                                             |

| FSR        | 04h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| PORTA      | 05h     | x xxxx         | u uuuu                                                                                        | u uuuu                                                               |

| PORTB      | 06h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| EEDATA     | 08h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| EEADR      | 09h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| PCLATH     | 0Ah     | 0 0000         | 0 0000                                                                                        | u uuuu                                                               |

| INTCON     | 0Bh     | 0000 000x      | 0000 000u                                                                                     | uuuu uuuu <sup>(1)</sup>                                             |

| INDF       | 80h     |                |                                                                                               |                                                                      |

| OPTION_REG | 81h     | 1111 1111      | 1111 1111                                                                                     | uuuu uuuu                                                            |

| PCL        | 82h     | 0000h          | 0000h                                                                                         | PC + 1                                                               |

| STATUS     | 83h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                                      | uuuq quuu <sup>(3)</sup>                                             |

| FSR        | 84h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| TRISA      | 85h     | 1 1111         | 1 1111                                                                                        | u uuuu                                                               |

| TRISB      | 86h     | 1111 1111      | 1111 1111                                                                                     | սսսս սսսս                                                            |

| EECON1     | 88h     | 0 x000         | 0 q000                                                                                        | 0 uuuu                                                               |

| EECON2     | 89h     |                |                                                                                               |                                                                      |

| PCLATH     | 8Ah     | 0 0000         | 0 0000                                                                                        | u uuuu                                                               |

| INTCON     | 8Bh     | 0000 000x      | 0000 000u                                                                                     | uuuu uuuu <sup>(1)</sup>                                             |

#### TABLE 8-4 RESET CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0',

q = value depends on condition.

Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: Table 8-3 lists the reset value for each specific condition.

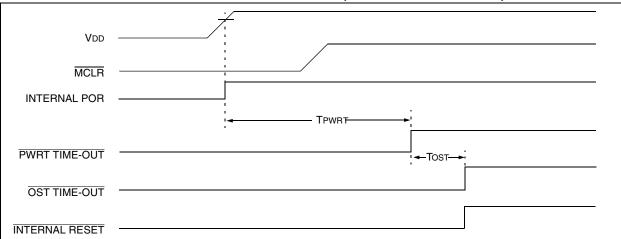

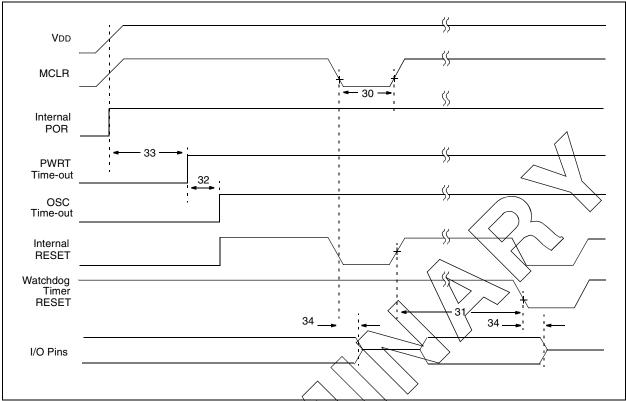

FIGURE 8-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

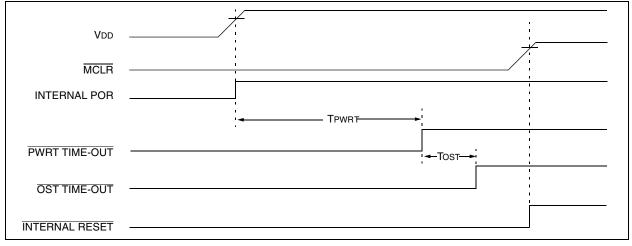

#### FIGURE 8-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

#### 8.7 <u>Time-out Sequence and Power-down</u> Status Bits (TO/PD)

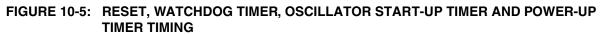

On power-up (Figure 8-10, Figure 8-11, Figure 8-12 and Figure 8-13) the time-out sequence is as follows: First PWRT time-out is invoked after a POR has expired. Then the OST is activated. The total time-out will vary based on oscillator configuration and PWRTE configuration bit status. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

## TABLE 8-5TIME-OUT IN VARIOUSSITUATIONS

| Oscillator    | Powe                | Wake-up          |               |  |

|---------------|---------------------|------------------|---------------|--|

| Configuration | PWRT<br>Enabled     | PWRT<br>Disabled | from<br>SLEEP |  |

| XT, HS, LP    | 72 ms +<br>1024Tosc | 1024Tosc         | 1024Tosc      |  |

| RC            | 72 ms               | _                | _             |  |

Since the time-outs occur from the POR reset pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high, execution will begin immediately (Figure 8-10). This is useful for testing purposes or to synchronize more than one PIC16F8X device when operating in parallel.

Table 8-6 shows the significance of the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits. Table 8-3 lists the reset conditions for some special registers, while Table 8-4 lists the reset conditions for all the registers.

# TABLE 8-6STATUS BITS AND THEIRSIGNIFICANCE

| то | PD | Condition                                                         |

|----|----|-------------------------------------------------------------------|

| 1  | 1  | Power-on Reset                                                    |

| 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| x  | 0  | Illegal, PD is set on POR                                         |

| 0  | 1  | WDT Reset (during normal operation)                               |

| 0  | 0  | WDT Wake-up                                                       |

| 1  | 1  | MCLR Reset during normal operation                                |

| 1  | 0  | MCLR Reset during SLEEP or interrupt                              |

|    |    | wake-up from SLEEP                                                |

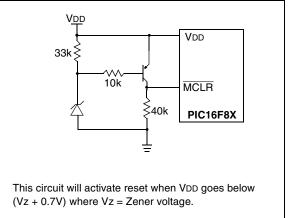

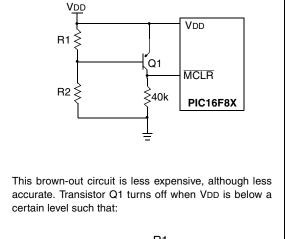

### 8.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset a PIC16F8X device when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 8-14 and Figure 8-15.

#### FIGURE 8-14: BROWN-OUT PROTECTION CIRCUIT 1

#### FIGURE 8-15: BROWN-OUT PROTECTION CIRCUIT 2

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

# PIC16F8X

| NOP               | No Operation |                  |                  |                  |  |  |  |

|-------------------|--------------|------------------|------------------|------------------|--|--|--|

| Syntax:           | [ label ]    | NOP              |                  |                  |  |  |  |

| Operands:         | None         |                  |                  |                  |  |  |  |

| Operation:        | No opera     | ition            |                  |                  |  |  |  |

| Status Affected:  | None         |                  |                  |                  |  |  |  |

| Encoding:         | 00           | 0000             | 0xx0             | 0000             |  |  |  |

| Description:      | No operati   | ion.             |                  |                  |  |  |  |

| Words:            | 1            |                  |                  |                  |  |  |  |

| Cycles:           | 1            |                  |                  |                  |  |  |  |

| Q Cycle Activity: | Q1           | Q2               | Q3               | Q4               |  |  |  |

|                   | Decode       | No-Opera<br>tion | No-Opera<br>tion | No-Operat<br>ion |  |  |  |

| Example           | NOP          |                  |                  |                  |  |  |  |

| RETFIE            | Return fi                                                                                                                                                                                                         | rom Inter        | rupt               |                    |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|--------------------|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                         | RETFIE           |                    |                    |  |  |

| Operands:         | None                                                                                                                                                                                                              |                  |                    |                    |  |  |

| Operation:        | $\begin{array}{l} TOS \to F \\ 1 \to GIE \end{array}$                                                                                                                                                             | PC,              |                    |                    |  |  |

| Status Affected:  | None                                                                                                                                                                                                              |                  |                    |                    |  |  |

| Encoding:         | 0 0                                                                                                                                                                                                               | 0000             | 0000               | 1001               |  |  |

| Description:      | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in the<br>PC. Interrupts are enabled by setting<br>Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |                  |                    |                    |  |  |

| Words:            | 1                                                                                                                                                                                                                 |                  |                    |                    |  |  |

| Cycles:           | 2                                                                                                                                                                                                                 |                  |                    |                    |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                | Q2               | Q3                 | Q4                 |  |  |

| 1st Cycle         | Decode                                                                                                                                                                                                            | No-Opera<br>tion | Set the<br>GIE bit | Pop from the Stack |  |  |

| 2nd Cycle         | No-Operat<br>ion                                                                                                                                                                                                  | No-Opera<br>tion | No-Opera<br>tion   | No-Operat<br>ion   |  |  |

| Example           | RETFIE                                                                                                                                                                                                            |                  |                    |                    |  |  |

After Interrupt PC = TOS GIE = 1

| OPTION           | Load Option Register                                                                                                                                                                                                                               |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] OPTION                                                                                                                                                                                                                                     |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                               |  |  |  |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                           |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                               |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0010                                                                                                                                                                                                                                  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code com-<br>patibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly address<br>it. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Example          |                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products,<br>do not use this instruction.                                                                                                                                                 |  |  |  |  |  |

# PIC16F8X

| RETLW             | Return v                                                         | vith Liter          | al in W                          |                                         | RETURN            | Return f                                                                                                  | rom Sub          | routine          |                  |

|-------------------|------------------------------------------------------------------|---------------------|----------------------------------|-----------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|

| Syntax:           | [ <i>label</i> ] RETLW k                                         |                     |                                  | Syntax:                                 | [ label ]         | RETUR                                                                                                     | N                |                  |                  |

| Operands:         | $0 \le k \le 2$                                                  | 55                  |                                  |                                         | Operands:         | None                                                                                                      |                  |                  |                  |

| Operation:        | $k \rightarrow (W);$                                             |                     |                                  |                                         | Operation:        | $TOS \rightarrow F$                                                                                       | ъС               |                  |                  |

|                   | $TOS \rightarrow F$                                              | ъС                  |                                  |                                         | Status Affected:  | None                                                                                                      |                  |                  |                  |

| Status Affected:  | None                                                             |                     |                                  |                                         | Encoding:         | 00                                                                                                        | 0000             | 0000             | 1000             |

| Encoding:         | 11                                                               | 01xx                | kkkk                             | kkkk                                    | Description:      | Return fro                                                                                                | m subrout        | ine. The st      | ack is           |

| Description:      | The W reg<br>bit literal 'k<br>loaded fro                        | <. The pro          | gram coun                        | iter is                                 |                   | POPed and the top of the stack (TOS) is loaded into the program counter. This is a two cycle instruction. |                  |                  |                  |

|                   | return add                                                       | Iress). This        |                                  |                                         | Words:            | 1                                                                                                         |                  |                  |                  |

| Manda.            | instructior                                                      | 1.                  |                                  |                                         | Cycles:           | 2                                                                                                         |                  |                  |                  |

| Words:            | 1                                                                |                     |                                  |                                         | Q Cycle Activity: | Q1                                                                                                        | Q2               | Q3               | Q4               |

| Cycles:           | 2                                                                | 00                  | 00                               | 04                                      | 1st Cycle         | Decode                                                                                                    | No-Opera         |                  | Pop from         |

| Q Cycle Activity: | Q1                                                               | Q2                  | Q3                               | Q4                                      |                   |                                                                                                           | tion             | tion             | the Stack        |

| 1st Cycle         | Decode                                                           | Read<br>literal 'k' | No-Opera<br>tion                 | Write to<br>W, Pop<br>from the<br>Stack | 2nd Cycle         | No-Operat<br>ion                                                                                          | No-Opera<br>tion | No-Opera<br>tion | No-Opera<br>tion |

| 2nd Cycle         |                                                                  | No-Opera            |                                  | No-Operat                               | Example           | RETURN                                                                                                    |                  |                  |                  |

|                   | No-Operat<br>ion                                                 | tion                | tion                             | ion                                     |                   | After Inte                                                                                                | errupt           |                  |                  |

|                   |                                                                  |                     | •                                |                                         |                   |                                                                                                           |                  | TOS              |                  |

| Example           | CALL TABL                                                        | ;offset             | tains tabl<br>value<br>has table |                                         |                   |                                                                                                           |                  |                  |                  |

| TABLE             | •<br>ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ; |                     |                                  |                                         |                   |                                                                                                           |                  |                  |                  |

|                   | •                                                                |                     |                                  |                                         |                   |                                                                                                           |                  |                  |                  |

|                   | •<br>RETLW kn ; End of table                                     |                     |                                  |                                         |                   |                                                                                                           |                  |                  |                  |

|                   | Before Instruction                                               |                     |                                  |                                         |                   |                                                                                                           |                  |                  |                  |

|                   |                                                                  |                     | 0x07                             |                                         |                   |                                                                                                           |                  |                  |                  |

|                   | After Inst                                                       |                     | value of k                       | 3                                       |                   |                                                                                                           |                  |                  |                  |

|                   |                                                                  |                     |                                  | -                                       |                   |                                                                                                           |                  |                  |                  |

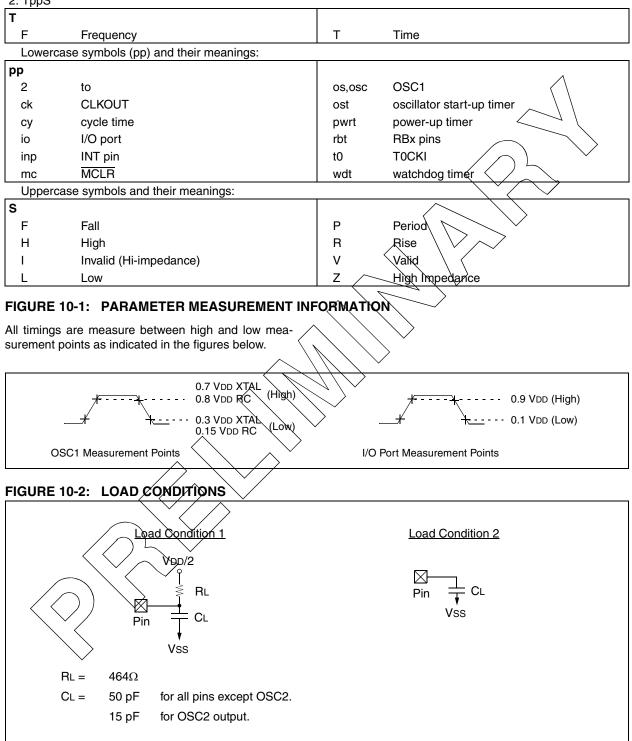

#### **TABLE 10-2** TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

- 1. TppS2ppS

- 2. TppS

####

| Parameter |       |                                                  | $\langle \ \rangle$ | $\searrow$ |       |       |                                  |

|-----------|-------|--------------------------------------------------|---------------------|------------|-------|-------|----------------------------------|

| No.       | Sym   | Characteristic                                   | Min                 | Тур†       | Max   | Units | Conditions                       |

| 30        | TmcL  | MCLR Pulse Width (low)                           | 1000*               | _          |       | ns    | $2.0V \leq V\text{DD} \leq 6.0V$ |

| 31        | Twdt  | Watchdog Timer Time-out Period<br>(No Prescater) | 7*                  | 18         | 33 *  | ms    | VDD = 5.0V                       |

| 32        | Tost  | Oscillation Start-up Timer Period                |                     | 1024Tosc   |       | ms    | Tosc = OSC1 period               |

| 33        | Tpwrt | Power-up Timer Period                            | 28 *                | 72         | 132 * | ms    | VDD = 5.0V                       |

| 34        | Tioz  | I/O Hi-impedance from MCLR Low                   | _                   | _          | 100 * | ns    |                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 50, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested

#### 11.1 DC CHARACTERISTICS:

#### PIC16CR84, PIC16CR83 (Commercial, Industrial)

| DC Characteristics<br>Power Supply Pins |      |                                                                  |            | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial) |                |                |                                                                                                                                                                              |  |  |

|-----------------------------------------|------|------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter<br>No.                        | Sym  | Characteristic                                                   | Min        | Тур†                                                                                                                                                                                   | Max            | Units          | Conditions                                                                                                                                                                   |  |  |

| D001<br>D001A                           | Vdd  | Supply Voltage                                                   | 4.0<br>4.5 | _                                                                                                                                                                                      | 6.0<br>5.5     | V<br>V         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                      |  |  |

| D002                                    | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5*       | —                                                                                                                                                                                      | —              | V              | Device in SLEEP mode                                                                                                                                                         |  |  |

| D003                                    | VPOR | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | —          | Vss                                                                                                                                                                                    | —              | V              | See section on Power-on Reset for details                                                                                                                                    |  |  |

| D004                                    | Svdd | VDD rise rate to ensure<br>internal Power-on<br>Reset signal     | 0.05*      | —                                                                                                                                                                                      | —              | V/ms           | See section on Power-on Reset for details                                                                                                                                    |  |  |

| D010<br>D010A                           | IDD  | Supply Current <sup>(2)</sup>                                    |            | 1.8<br>7.3                                                                                                                                                                             | 4.5<br>10      | mA<br>mA       | RC and XT ose configuration <sup>(4)</sup><br>Fosc = 4.0 MHz, VDD = 5.5V<br>Fosc = 4.0 MHz, VDD = 5.5V<br>(During EERROM programming)<br>HS ose configuration (PIC16CR84-10) |  |  |

| D013                                    |      | (0)                                                              |            | 5                                                                                                                                                                                      | 10             | mA<            | Fosc = $10$ MHz, VDD = 5.5V                                                                                                                                                  |  |  |

| D020<br>D021<br>D021A                   | IPD  | Power-down Current <sup>(3)</sup>                                |            | 7.0<br>1.0<br>1.0                                                                                                                                                                      | 28<br>14<br>16 | μΑ<br>μΑ<br>μΑ | $V_{DD} = 4.0V$ , WDT enabled, industrial<br>$V_{DD} = 4.0V$ , WDT disabled, commercial<br>$V_{DD} = 4.0V$ , WDT disabled, industrial                                        |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

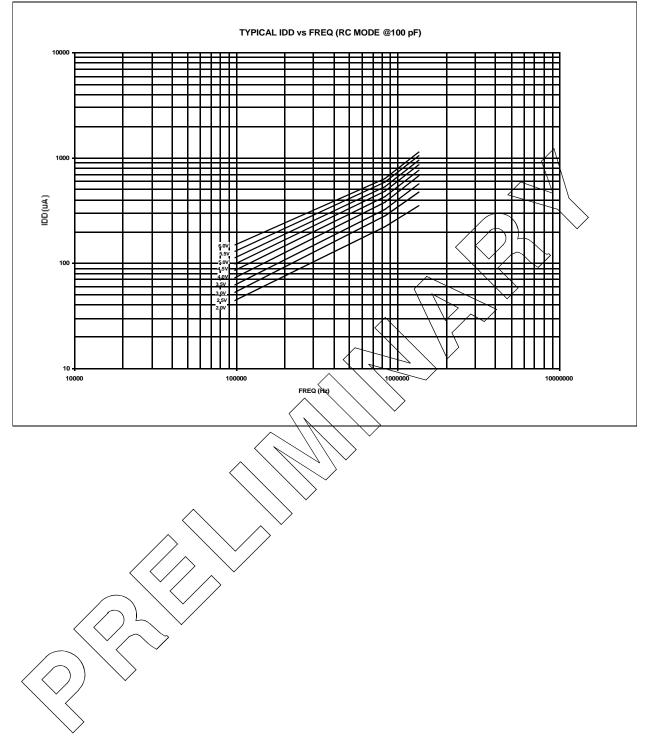

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1=external square wave, from rail to rail, all I/O pins tristated, pulled to VDD, T0CKI = VDD,  $\overline{MCLR} = VDD$ ; WDT applied displayed as approximate

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula IB = VpD/2Rext (mA) with Rext in kOhm.

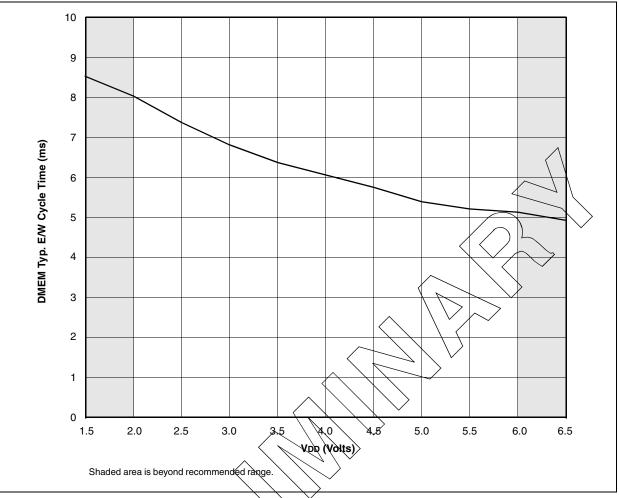

#### FIGURE 12-21: TYPICAL DATA MEMORY ERASE/WRITE CYCLE TIME VS. VDD

#### TABLE 12-2 INPUT CAPACITANCE\*

| Pin Name    | Typical Capa | acitance (pF) |

|-------------|--------------|---------------|

|             | 18L PDIP     | 18L SOIC      |

| PORTA       | 5.0          | 4.3           |

| POBTB       | 5.0          | 4.3           |

|             | 17.0         | 17.0          |

| OSCIŲCĽKĮM  | 4.0          | 3.5           |

| OSCZYCLKOUT | 4.3          | 3.5           |

| СС тоскі    | 3.2          | 2.8           |

All capacitance values are typical at 25°C. A part to part variation of  $\pm 25\%$  (three standard deviations) should be taken into account.

## **13.0 PACKAGING INFORMATION**

### 13.1 Package Marking Information

##

#### Example

#### 18L SOIC

#### Example

| L | .egend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                        | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |  |  |  |

|---|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| N | I       | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

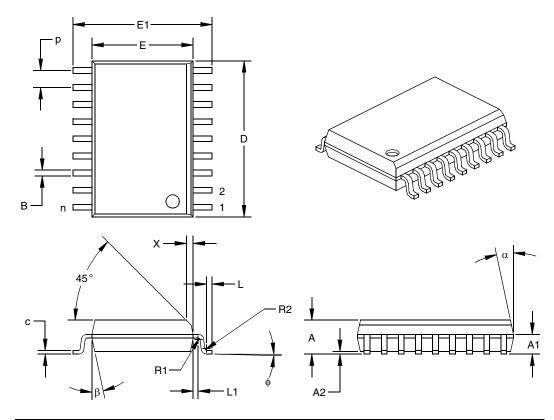

| Units                   |                | INCHES* |       |       | MILLIMETERS |       |       |

|-------------------------|----------------|---------|-------|-------|-------------|-------|-------|

| Dimension Limits        |                | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |

| Pitch                   | р              |         | 0.050 |       |             | 1.27  |       |

| Number of Pins          | n              |         | 18    |       |             | 18    |       |

| Overall Pack. Height    | А              | 0.093   | 0.099 | 0.104 | 2.36        | 2.50  | 2.64  |

| Shoulder Height         | A1             | 0.048   | 0.058 | 0.068 | 1.22        | 1.47  | 1.73  |

| Standoff                | A2             | 0.004   | 0.008 | 0.011 | 0.10        | 0.19  | 0.28  |

| Molded Package Length   | D‡             | 0.450   | 0.456 | 0.462 | 11.43       | 11.58 | 11.73 |

| Molded Package Width    | E‡             | 0.292   | 0.296 | 0.299 | 7.42        | 7.51  | 7.59  |

| Outside Dimension       | E1             | 0.394   | 0.407 | 0.419 | 10.01       | 10.33 | 10.64 |

| Chamfer Distance        | Х              | 0.010   | 0.020 | 0.029 | 0.25        | 0.50  | 0.74  |

| Shoulder Radius         | R1             | 0.005   | 0.005 | 0.010 | 0.13        | 0.13  | 0.25  |

| Gull Wing Radius        | R2             | 0.005   | 0.005 | 0.010 | 0.13        | 0.13  | 0.25  |

| Foot Length             | L              | 0.011   | 0.016 | 0.021 | 0.28        | 0.41  | 0.53  |

| Foot Angle              | φ              | 0       | 4     | 8     | 0           | 4     | 8     |

| Radius Centerline       | L1             | 0.010   | 0.015 | 0.020 | 0.25        | 0.38  | 0.51  |

| Lead Thickness          | С              | 0.009   | 0.011 | 0.012 | 0.23        | 0.27  | 0.30  |

| Lower Lead Width        | B <sup>†</sup> | 0.014   | 0.017 | 0.019 | 0.36        | 0.42  | 0.48  |

| Mold Draft Angle Top    | α              | 0       | 12    | 15    | 0           | 12    | 15    |

| Mold Draft Angle Bottom | β              | 0       | 12    | 15    | 0           | 12    | 15    |

Controlling Parameter.

<sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

### **PIC16F8X PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br> <br>Device | -XX     X     /XX     XXX                                 Frequency Temperature     Package     Pattern       Range     Range                                                                                                                                                                                                                  | Examples:<br>a) PIC16F84 -04/P 301 = Commercial<br>temp., PDIP package, 4 MHz, normal                                                                                                                                                                                          |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                  | PIC16F8X <sup>(2)</sup> , PIC16F8XT <sup>(3)</sup><br>PIC16LF8X <sup>(2)</sup> , PIC16LF8XT <sup>(3)</sup><br>PIC16F8XA <sup>(2)</sup> , PIC16F8XAT <sup>(3)</sup><br>PIC16LF8XA <sup>(2)</sup> , PIC16LF8XAT <sup>(3)</sup><br>PIC16CR8X <sup>(2)</sup> , PIC16CR8XT <sup>(3)</sup><br>PIC16LCR8X <sup>(2)</sup> , PIC16LCR8XT <sup>(3)</sup> | <ul> <li>VDD limits, QTP pattern #301.</li> <li>b) PIC16LF84 - 04I/SO = Industrial temp.,<br/>SOIC package, 200 kHz, Extended VDD<br/>limits.</li> <li>c) PIC16CR84 - 10I/P = ROM program<br/>memory, Industrial temp., PDIP package,<br/>10MHz, normal VDD limits.</li> </ul> |

| Frequency<br>Range      | 04 = 4 MHz<br>10 = 10 MHz<br>20 = 20 MHz                                                                                                                                                                                                                                                                                                       | Note 1: b = blank                                                                                                                                                                                                                                                              |

| Temperature<br>Range    | $b^{(1)} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ (Commercial)}$<br>I = -40°C to +85°C (Industrial)                                                                                                                                                                                                                                        | 2: F = Standard VDD range<br>LF = Extended VDD range<br>CR = ROM Version, Standard VDD                                                                                                                                                                                         |

| Package<br>Pattern      | P = PDIP<br>SO = SOIC (Gull Wing, 300 mil body)<br>SS = SSOP<br>3-digit Pattern Code for QTP, ROM (blank otherwise)                                                                                                                                                                                                                            | range<br>LCR = ROM Version, Extended VDD<br>range<br>3: T = in tape and reel - SOIC, SSOP                                                                                                                                                                                      |

|                         |                                                                                                                                                                                                                                                                                                                                                | packages only.                                                                                                                                                                                                                                                                 |

## SALES AND SUPPORT

Products supported by a preliminary Data Sheet may possibly have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office.

- 2. The Microchip's Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).

## Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820