Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               |                                                                          |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 896B (512 x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 36 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 18-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f83-04-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16F8X is a group in the PIC16CXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers. This group contains the following devices:

- PIC16F83

- PIC16F84

- PIC16CR83

- PIC16CR84

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. PIC16F8X devices have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with a separate 8-bit wide data bus. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set is used to achieve a very high performance level.

PIC16F8X microcontrollers typically achieve a 2:1 code compression and up to a 4:1 speed improvement (at 20 MHz) over other 8-bit microcontrollers in their class.

The PIC16F8X has up to 68 bytes of RAM, 64 bytes of Data EEPROM memory, and 13 I/O pins. A timer/counter is also available.

The PIC16CXX family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers power saving. The user can wake the chip from sleep through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

The devices with Flash program memory allow the same device package to be used for prototyping and production. In-circuit reprogrammability allows the code to be updated without the device being removed from the end application. This is useful in the development of many applications where the device may not be easily accessible, but the prototypes may require code updates. This is also useful for remote applications where the code may need to be updated (such as rate information). Table 1-1 lists the features of the PIC16F8X. A simplified block diagram of the PIC16F8X is shown in Figure 3-1.

The PIC16F8X fits perfectly in applications ranging from high speed automotive and appliance motor control to low-power remote sensors, electronic locks, security devices and smart cards. The Flash/EEPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, security codes, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high performance, ease-of-use and I/O flexibility make the PIC16F8X very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions; serial communication; capture, compare and PWM functions; and co-processor applications).

The serial in-system programming feature (via two pins) offers flexibility of customizing the product after complete assembly and testing. This feature can be used to serialize a product, store calibration data, or program the device with the current firmware before shipping.

## 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for PIC16C5X devices can be easily ported to PIC16F8X devices (Appendix B).

# 1.2 <u>Development Support</u>

The PIC16CXX family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler and fuzzy logic support tools are also available.

# TABLE 4-1 REGISTER FILE SUMMARY

| Address | Name                  | Bit 7     | Bit 6        | Bit 5        | Bit 4             | Bit 3          | Bit 2         | Bit 1 | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note3) |

|---------|-----------------------|-----------|--------------|--------------|-------------------|----------------|---------------|-------|---------|-------------------------------|-----------------------------------------|

| Bank 0  |                       |           |              |              | •                 |                |               |       |         |                               | •                                       |

| 00h     | INDF                  | Uses co   | ntents of F  | SR to addre  | ess data memor    | y (not a phys  | sical registe | r)    |         |                               |                                         |

| 01h     | TMR0                  | 8-bit rea | I-time clock | /counter     |                   |                |               |       |         | xxxx xxxx                     | uuuu uuuu                               |

| 02h     | PCL                   | Low ord   | er 8 bits of | the Program  | m Counter (PC)    |                |               |       |         | 0000 0000                     | 0000 0000                               |

| 03h     | STATUS <sup>(2)</sup> | IRP       | RP1          | RP0          | TO                | PD             | Z             | DC    | С       | 0001 1xxx                     | 000q quuu                               |

| 04h     | FSR                   | Indirect  | data memo    | ry address   | pointer 0         |                |               |       |         | xxxx xxxx                     | uuuu uuuu                               |

| 05h     | PORTA                 | —         | —            | _            | RA4/T0CKI         | RA3            | RA2           | RA1   | RA0     | x xxxx                        | u uuuu                                  |

| 06h     | PORTB                 | RB7       | RB6          | RB5          | RB4               | RB3            | RB2           | RB1   | RB0/INT | XXXX XXXX                     | uuuu uuuu                               |

| 07h     |                       | Unimple   | mented loc   | ation, read  | as '0'            |                |               | •     | •       |                               |                                         |

| 08h     | EEDATA                | EEPRO     | V data regi  | ster         |                   |                |               |       |         | XXXX XXXX                     | uuuu uuuu                               |

| 09h     | EEADR                 | EEPROI    | M address    | register     |                   |                |               |       |         | XXXX XXXX                     | uuuu uuuu                               |

| 0Ah     | PCLATH                | _         |              | _            | Write buffer for  | r upper 5 bit  | s of the PC   | (1)   |         | 0 0000                        | 0 0000                                  |

| 0Bh     | INTCON                | GIE       | EEIE         | TOIE         | INTE              | RBIE           | TOIF          | INTF  | RBIF    | 0000 000x                     | 0000 000u                               |

| Bank 1  |                       |           |              |              |                   |                |               |       |         |                               |                                         |

| 80h     | INDF                  | Uses co   | ntents of F  | SR to addre  | ess data memor    | y (not a phys  | sical registe | r)    |         |                               |                                         |

| 81h     | OPTION_<br>REG        | RBPU      | INTEDG       | TOCS         | TOSE              | PSA            | PS2           | PS1   | PS0     | 1111 1111                     | 1111 1111                               |

| 82h     | PCL                   | Low ord   | er 8 bits of | Program C    | ounter (PC)       |                |               | •     | •       | 0000 0000                     | 0000 0000                               |

| 83h     | STATUS (2)            | IRP       | RP1          | RP0          | TO                | PD             | Z             | DC    | С       | 0001 1xxx                     | 000q quuu                               |

| 84h     | FSR                   | Indirect  | data memo    | ry address   | pointer 0         |                |               |       |         | xxxx xxxx                     | uuuu uuuu                               |

| 85h     | TRISA                 | —         | —            | —            | PORTA data d      | irection regis | ster          |       |         | 1 1111                        | 1 1111                                  |

| 86h     | TRISB                 | PORTB     | data directi | on register  | •                 |                |               |       |         | 1111 1111                     | 1111 1111                               |

| 87h     |                       | Unimple   | mented loc   | ation, read  | as '0'            |                |               |       |         |                               |                                         |

| 88h     | EECON1                | —         | _            | _            | EEIF              | WRERR          | WREN          | WR    | RD      | 0 x000                        | 0 q000                                  |

| 89h     | EECON2                | EEPRO     | V control re | gister 2 (no | ot a physical reg | ister)         | -             |       |         |                               |                                         |

| 0Ah     | PCLATH                | _         | _            | _            | Write buffer for  | r upper 5 bit  | s of the PC   | (1)   |         | 0 0000                        | 0 0000                                  |

| 0Bh     | INTCON                | GIE       | EEIE         | TOIE         | INTE              | RBIE           | TOIF          | INTF  | RBIF    | 0000 000x                     | 0000 000u                               |

Legend: x = unknown, u = unchanged. - = unimplemented read as '0', q = value depends on condition.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a slave register for PC<12:8>. The contents of PCLATH can be transferred to the upper byte of the program counter, but the contents of PC<12:8> is never transferred to PCLATH.

2: The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  status bits in the STATUS register are not affected by a  $\overline{\text{MCLR}}$  reset.

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

### 4.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external INT interrupt, TMR0, and the weak pull-ups on PORTB.

## FIGURE 4-1: OPTION\_REG REGISTER (ADDRESS 81h)

**Note:** When the prescaler is assigned to the WDT (PSA = '1'), TMR0 has a 1:1 prescaler assignment.

| R/W-1            | R/W-1       | R/W-1            | R/W-1    | R/W-1      | R/W-1        | R/W-1        | R/W-1 |                                       |

|------------------|-------------|------------------|----------|------------|--------------|--------------|-------|---------------------------------------|

| RBPU             | INTEDG      | TOCS             | T0SE     | PSA        | PS2          | PS1          | PS0   | R = Readable bit                      |

| bit7             |             |                  |          |            |              |              | bit0  | W = Writable bit                      |

|                  |             |                  |          |            |              |              |       | U = Unimplemented bit,<br>read as '0' |

|                  |             |                  |          |            |              |              |       | - n = Value at POR reset              |

| bit 7:           | RBPU: PC    |                  | ın Enabl | a hit      |              |              |       |                                       |

| Dit 7.           | 1 = PORTI   |                  |          |            |              |              |       |                                       |

|                  |             |                  |          |            | dividual por | t latch valı | ues)  |                                       |

| bit 6:           | INTEDG:     |                  |          |            | ·            |              | ,     |                                       |

| bit 0.           | 1 = Interru | •                | •        |            | nin          |              |       |                                       |

|                  | 0 = Interru |                  |          |            |              |              |       |                                       |

| bit 5:           | TOCS: TM    |                  |          |            | F.           |              |       |                                       |

| Dit J.           | 1 = Transit |                  |          |            |              |              |       |                                       |

|                  | 0 = Interna |                  |          | •          | OUT)         |              |       |                                       |

| bit 4:           | TOSE: TM    |                  | •        |            |              |              |       |                                       |

| DIL 4.           |             |                  |          |            | on RA4/T00   |              |       |                                       |

|                  |             |                  |          |            | on RA4/T00   |              |       |                                       |

| bit 3:           | PSA: Pres   |                  | •        |            |              | p            |       |                                       |

| DIL 3.           | 1 = Presca  |                  |          |            |              |              |       |                                       |

|                  | 0 = Presca  |                  |          |            |              |              |       |                                       |

| hit 2 0.         | PS2:PS0:    | •                |          |            |              |              |       |                                       |

| bit <u>∠</u> -0. |             |                  |          |            |              |              |       |                                       |

|                  | Bit Value   | TMR0 Ra          | te WD    | Γ Rate     |              |              |       |                                       |

|                  | 000         | 1:2              | 1 :      |            |              |              |       |                                       |

|                  | 001         | 1:4              | 1:       |            |              |              |       |                                       |

|                  | 010<br>011  | 1:8              |          | : 4<br>: 8 |              |              |       |                                       |

|                  | 100         | 1 : 16<br>1 : 32 |          | 16         |              |              |       |                                       |

|                  | 101         | 1:64             |          | 32         |              |              |       |                                       |

|                  | 110         | 1 : 128          |          | 64         |              |              |       |                                       |

|                  | 111         | 1 : 256          | 1:       | 128        |              |              |       |                                       |

|                  |             |                  |          |            |              |              |       |                                       |

|                  |             |                  |          |            |              |              |       |                                       |

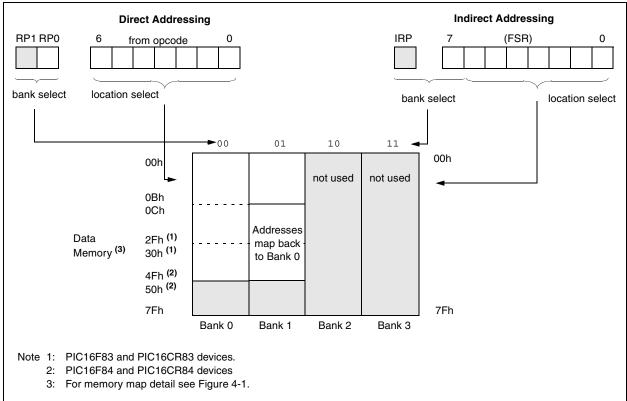

### 4.5 Indirect Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

### EXAMPLE 4-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

FIGURE 4-1: DIRECT/INDIRECT ADDRESSING

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-2.

### EXAMPLE 4-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | movwf | FSR   | ; to RAM             |

| NEXT     | clrf  | INDF  | ;clear INDF register |

|          | incf  | FSR   | ;inc pointer         |

|          | btfss | FSR,4 | ;all done?           |

|          | goto  | NEXT  | ;NO, clear next      |

| CONTINUE |       |       |                      |

|          | :     |       | ;YES, continue       |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-1. However, IRP is not used in the PIC16F8X.

# TABLE 5-1 PORTA FUNCTIONS

| Name      | Bit0 | Buffer Type | Function                                                                     |

|-----------|------|-------------|------------------------------------------------------------------------------|

| RA0       | bit0 | TTL         | Input/output                                                                 |

| RA1       | bit1 | TTL         | Input/output                                                                 |

| RA2       | bit2 | TTL         | Input/output                                                                 |

| RA3       | bit3 | TTL         | Input/output                                                                 |

| RA4/T0CKI | bit4 | ST          | Input/output or external clock input for TMR0.<br>Output is open drain type. |

Legend: TTL = TTL input, ST = Schmitt Trigger input

### TABLE 5-2 SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|-------|-------|-------|-------|-----------|--------|--------|--------|--------|-------------------------------|---------------------------|

| 05h     | PORTA | —     | —     | —     | RA4/T0CKI | RA3    | RA2    | RA1    | RA0    | x xxxx                        | u uuuu                    |

| 85h     | TRISA | -     | —     | _     | TRISA4    | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111                        | 1 1111                    |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are unimplemented, read as '0'

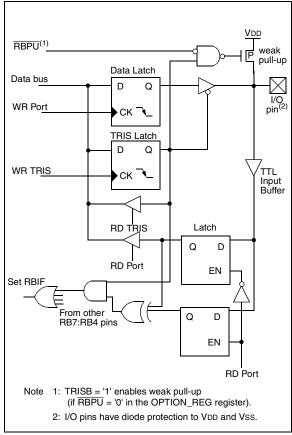

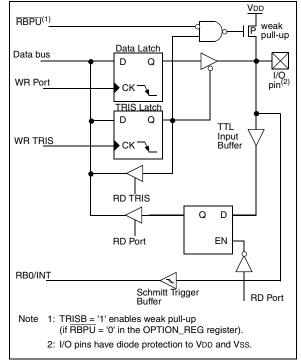

### 5.2 **PORTB and TRISB Registers**

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' on any bit in the TRISB register puts the corresponding output driver in a hi-impedance mode. A '0' on any bit in the TRISB register puts the contents of the output latch on the selected pin(s).

Each of the PORTB pins have a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION\_REG<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The pins value in input mode are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of the pins are OR'ed together to generate the RB port change interrupt.

### FIGURE 5-3: BLOCK DIAGRAM OF PINS RB7:RB4

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Read (or write) PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set the RBIF bit. Reading PORTB will end the mismatch condition, and allow the RBIF bit to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression (see AN552 in the Embedded Control Handbook).

Note 1: For a change on the I/O pin to be recognized, the pulse width must be at least TcY (4/fosc) wide.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

### FIGURE 5-4: BLOCK DIAGRAM OF PINS RB3:RB0

## 8.1 <u>Configuration Bits</u>

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

Address 2007h is beyond the user program memory space and it belongs to the special test/configuration memory space (2000h - 3FFFh). This space can only be accessed during programming.

To find out how to program the PIC16C84, refer to *PIC16C84 EEPROM Memory Programming Specifica-tion* (DS30189).

# FIGURE 8-1: CONFIGURATION WORD - PIC16CR83 AND PIC16CR84

| <b>D</b>  | <b>D</b>             | Π                                                | <b>D</b>                     | <b>D</b>  | <b>D</b>  | D/D         | <b>D</b>  | D         | <b>D</b>  | <b>D</b>     | <b>D</b>    | D                                 | D                                                      |   |

|-----------|----------------------|--------------------------------------------------|------------------------------|-----------|-----------|-------------|-----------|-----------|-----------|--------------|-------------|-----------------------------------|--------------------------------------------------------|---|

| R-u<br>CP | R-u<br>CP            | R-u<br>CP                                        | R-u<br>CP                    | R-u<br>CP | R-u<br>CP | R/P-u<br>DP | R-u<br>CP | R-u<br>CP | R-u<br>CP | R-u<br>PWRTE | R-u<br>WDTE | R-u<br>FOSC1                      | R-u<br>FOSC0                                           |   |

| bit13     |                      | 01                                               | 01                           |           |           |             | 01        |           | 01        |              |             | R = Rea<br>P = Prog<br>- n = Valu | bit0<br>adable bit<br>grammable bit<br>ie at POR reset | t |

| bit 13:8  | 1 = 0                | Program<br>Code pro<br>Program                   | tection                      | off       |           |             | it        |           |           |              |             | u = unch                          | langeu                                                 |   |

| bit 7     | 1 = 0                | Data Me<br>Code pro<br>Data mer                  | tection                      | off       |           |             |           |           |           |              |             |                                   |                                                        |   |

| bit 6:4   | 1 = 0                | Program<br>Code pro<br>Program                   | tection                      | off       |           |             | it        |           |           |              |             |                                   |                                                        |   |

| bit 3     | 1 = F                | RTE: Pov<br>Power-up<br>Power-up                 | timer                        | is disal  | oled      | bit         |           |           |           |              |             |                                   |                                                        |   |

| bit 2     | 1 = V                | E: Wato<br>VDT ena<br>VDT disa                   | abled                        | imer E    | nable I   | oit         |           |           |           |              |             |                                   |                                                        |   |

| bit 1:0   | 11 =<br>10 =<br>01 = | C1:FOS<br>RC osc<br>HS osc<br>XT osci<br>LP osci | illator<br>illator<br>llator | cillator  | Selec     | tion bits   |           |           |           |              |             |                                   |                                                        |   |

### 8.7 <u>Time-out Sequence and Power-down</u> Status Bits (TO/PD)

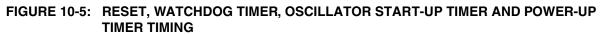

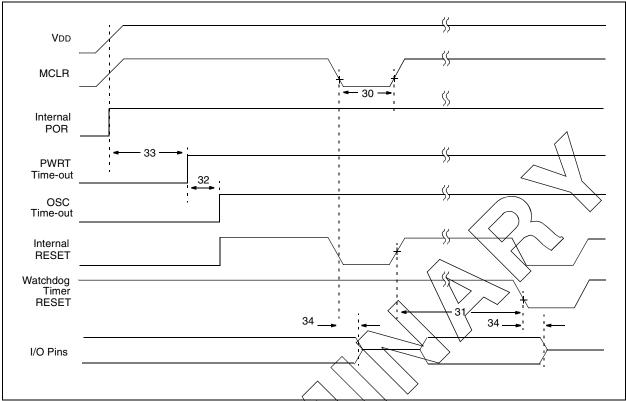

On power-up (Figure 8-10, Figure 8-11, Figure 8-12 and Figure 8-13) the time-out sequence is as follows: First PWRT time-out is invoked after a POR has expired. Then the OST is activated. The total time-out will vary based on oscillator configuration and PWRTE configuration bit status. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

# TABLE 8-5TIME-OUT IN VARIOUSSITUATIONS

| Oscillator    | Powe                | er-up            | Wake-up       |

|---------------|---------------------|------------------|---------------|

| Configuration | PWRT<br>Enabled     | PWRT<br>Disabled | from<br>SLEEP |

| XT, HS, LP    | 72 ms +<br>1024Tosc | 1024Tosc         | 1024Tosc      |

| RC            | 72 ms               | _                | _             |

Since the time-outs occur from the POR reset pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high, execution will begin immediately (Figure 8-10). This is useful for testing purposes or to synchronize more than one PIC16F8X device when operating in parallel.

Table 8-6 shows the significance of the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits. Table 8-3 lists the reset conditions for some special registers, while Table 8-4 lists the reset conditions for all the registers.

# TABLE 8-6STATUS BITS AND THEIR<br/>SIGNIFICANCE

| то | PD | Condition                                                         |

|----|----|-------------------------------------------------------------------|

| 1  | 1  | Power-on Reset                                                    |

| 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| x  | 0  | Illegal, PD is set on POR                                         |

| 0  | 1  | WDT Reset (during normal operation)                               |

| 0  | 0  | WDT Wake-up                                                       |

| 1  | 1  | MCLR Reset during normal operation                                |

| 1  | 0  | MCLR Reset during SLEEP or interrupt                              |

|    |    | wake-up from SLEEP                                                |

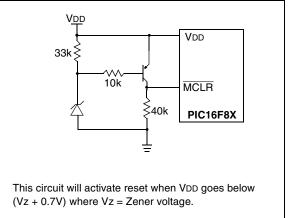

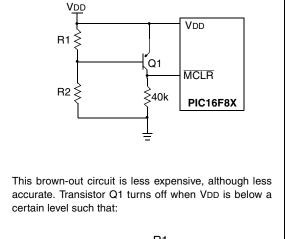

# 8.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset a PIC16F8X device when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 8-14 and Figure 8-15.

## FIGURE 8-14: BROWN-OUT PROTECTION CIRCUIT 1

### FIGURE 8-15: BROWN-OUT PROTECTION CIRCUIT 2

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

### 8.12 Power-down Mode (SLEEP)

A device may be powered down (SLEEP) and later powered up (Wake-up from SLEEP).

#### 8.12.1 SLEEP

The Power-down mode is entered by executing the SLEEP instruction.

If enabled, the Watchdog Timer is cleared (but keeps running), the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  bit (STATUS<4>) is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For the lowest current consumption in SLEEP mode, place all I/O pins at either at VDD or VSS, with no external circuitry drawing current from the I/O pins, and disable external clocks. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

It should be noted that a RESET generated by a WDT time-out does not drive the MCLR pin low.

#### 8.12.2 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. WDT Wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, RB port change, or data EEPROM write complete.

Peripherals cannot generate interrupts during SLEEP, since no on-chip Q clocks are present.

The first event ( $\overline{\text{MCLR}}$  reset) will cause a device reset. The two latter events are considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits can be used to determine the cause of a device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

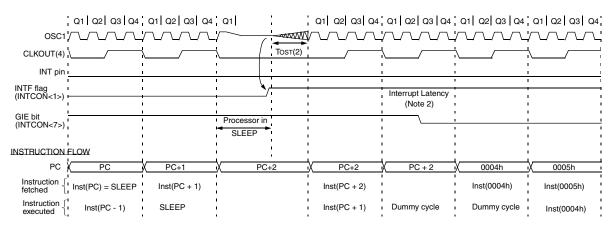

While the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the state of the substant of the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

# FIGURE 8-19: WAKE-UP FROM SLEEP THROUGH INTERRUPT

Note 1: XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

# 9.1 Instruction Descriptions

| ADDLW             | Add Lite                                     | ral and V           | W               |               |

|-------------------|----------------------------------------------|---------------------|-----------------|---------------|

| Syntax:           | [ <i>label</i> ] Al                          | DDLW                | k               |               |

| Operands:         | $0 \le k \le 2\xi$                           | 55                  |                 |               |

| Operation:        | (W) + k –                                    | → (W)               |                 |               |

| Status Affected:  | C, DC, Z                                     |                     |                 |               |

| Encoding:         | 11                                           | 111x                | kkkk            | kkkk          |

| Description:      | The conter<br>added to the<br>result is play | ne eight b          | it literal 'k'  | and the       |

| Words:            | 1                                            |                     |                 |               |

| Cycles:           | 1                                            |                     |                 |               |

| Q Cycle Activity: | Q1                                           | Q2                  | Q3              | Q4            |

|                   | Decode                                       | Read<br>literal 'k' | Process<br>data | Write to<br>W |

| Example:          | ADDLW                                        | 0x15                |                 |               |

|                   | Before In                                    | struction<br>W =    | 0x10            |               |

|                   | After Inst                                   | ruction<br>W =      | 0x25            |               |

| ADDWF             | Add W a                                                        | nd f                       |                             |                      |

|-------------------|----------------------------------------------------------------|----------------------------|-----------------------------|----------------------|

| Syntax:           | [ <i>label</i> ] A                                             | DDWF                       | f,d                         |                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$ | 7                          |                             |                      |

| Operation:        | (W) + (f)                                                      | ightarrow (desti           | nation)                     |                      |

| Status Affected:  | C, DC, Z                                                       |                            |                             |                      |

| Encoding:         | 00                                                             | 0111                       | dfff                        | ffff                 |

| Description:      | Add the co<br>register 'f'.<br>in the W re<br>stored bac       | If 'd' is 0<br>egister. If | the result i<br>d' is 1 the | is stored            |

| Words:            | 1                                                              |                            |                             |                      |

| Cycles:           | 1                                                              |                            |                             |                      |

| Q Cycle Activity: | Q1                                                             | Q2                         | Q3                          | Q4                   |

|                   | Decode                                                         | Read<br>register<br>'f'    | Process<br>data             | Write to destination |

| Example           | ADDWF                                                          | FSR,                       | 0                           |                      |

|                   | Before In                                                      | struction                  | I                           |                      |

|                   |                                                                | W =<br>FSR =               | 0x17<br>0xC2                |                      |

|                   | After Inst                                                     |                            | UNOL                        |                      |

|                   |                                                                | W =<br>FSR =               | 0xD9<br>0xC2                |                      |

| ANDLW                                                                                                              | AND Lite                                                                                                                                                                           |                                                                                                                                            | W                                                                                                        |                                                                          |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Syntax:                                                                                                            | [ <i>label</i> ] A                                                                                                                                                                 | NDLW                                                                                                                                       | k                                                                                                        |                                                                          |

| Operands:                                                                                                          | $0 \le k \le 28$                                                                                                                                                                   | 55                                                                                                                                         |                                                                                                          |                                                                          |

| Operation:                                                                                                         | (W) .ANE                                                                                                                                                                           | D. (k) $\rightarrow$ (                                                                                                                     | (W)                                                                                                      |                                                                          |

| Status Affected:                                                                                                   | Z                                                                                                                                                                                  |                                                                                                                                            |                                                                                                          |                                                                          |

| Encoding:                                                                                                          | 11                                                                                                                                                                                 | 1001                                                                                                                                       | kkkk                                                                                                     | kkkk                                                                     |

| Description:                                                                                                       | The conte<br>AND'ed wi<br>result is pl                                                                                                                                             | ith the eig                                                                                                                                |                                                                                                          | l 'k'. The                                                               |

| Words:                                                                                                             | 1                                                                                                                                                                                  |                                                                                                                                            |                                                                                                          |                                                                          |

| Cycles:                                                                                                            | 1                                                                                                                                                                                  |                                                                                                                                            |                                                                                                          |                                                                          |

| Q Cycle Activity:                                                                                                  | Q1                                                                                                                                                                                 | Q2                                                                                                                                         | Q3                                                                                                       | Q4                                                                       |

|                                                                                                                    | Decode                                                                                                                                                                             | Read<br>literal "k"                                                                                                                        | Process<br>data                                                                                          | Write to<br>W                                                            |

| Example                                                                                                            | ANDLW                                                                                                                                                                              | 0x5F                                                                                                                                       |                                                                                                          |                                                                          |

|                                                                                                                    | Before In                                                                                                                                                                          | struction                                                                                                                                  | l                                                                                                        |                                                                          |

|                                                                                                                    |                                                                                                                                                                                    | W =                                                                                                                                        | 0xA3                                                                                                     |                                                                          |

|                                                                                                                    | After Inst                                                                                                                                                                         | W =                                                                                                                                        | 0x03                                                                                                     |                                                                          |

| ANDWF                                                                                                              | AND W v                                                                                                                                                                            | vith f                                                                                                                                     |                                                                                                          |                                                                          |

| -                                                                                                                  |                                                                                                                                                                                    |                                                                                                                                            |                                                                                                          |                                                                          |

| Syntax:                                                                                                            | [ <i>label</i> ] A                                                                                                                                                                 |                                                                                                                                            | f,d                                                                                                      |                                                                          |

| Syntax:<br>Operands:                                                                                               | [ <i>label</i> ] A<br>0 ≤ f ≤ 12<br>d ∈ [0,1]                                                                                                                                      |                                                                                                                                            | f,d                                                                                                      |                                                                          |

| -                                                                                                                  | 0 ≤ f ≤ 12                                                                                                                                                                         | 27                                                                                                                                         |                                                                                                          | n)                                                                       |

| Operands:                                                                                                          | 0 ≤ f ≤ 12<br>d ∈ [0,1]                                                                                                                                                            | 27                                                                                                                                         |                                                                                                          | n)                                                                       |

| Operands:<br>Operation:                                                                                            | 0 ≤ f ≤ 12<br>d ∈ [0,1]<br>(W) .ANE                                                                                                                                                | 27                                                                                                                                         |                                                                                                          | n)<br>ffff                                                               |

| Operands:<br>Operation:<br>Status Affected:                                                                        | 0 ≤ f ≤ 12<br>d ∈ [0,1]<br>(W) .ANE<br>Z                                                                                                                                           | 27<br>D. (f) $\rightarrow$ (f)<br>0101<br>V register<br>sult is stor<br>1 the res                                                          | destinatio<br>dfff<br>with regist<br>red in the V                                                        | ffff<br>er 'f'. If 'd'<br><i>N</i> regis-                                |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                           | $0 \le f \le 12$<br>$d \in [0,1]$<br>(W) .ANE<br>Z<br>00<br>AND the V<br>is 0 the rester. If 'd' is                                                                                | 27<br>D. (f) $\rightarrow$ (f)<br>0101<br>V register<br>sult is stor<br>1 the res                                                          | destinatio<br>dfff<br>with regist<br>red in the V                                                        | ffff<br>er 'f'. If 'd'<br><i>N</i> regis-                                |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:                                 | $0 \le f \le 12$<br>$d \in [0,1]$<br>(W) .ANE<br>Z<br>00<br>AND the V<br>is 0 the reater. If 'd' is<br>register 'f'.                                                               | 27<br>D. (f) $\rightarrow$ (f)<br>0101<br>V register<br>sult is stor<br>1 the res                                                          | destinatio<br>dfff<br>with regist<br>red in the V                                                        | ffff<br>er 'f'. If 'd'<br><i>N</i> regis-                                |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                                           | $0 \le f \le 12$<br>$d \in [0,1]$<br>(W) .ANE<br>Z<br>00<br>AND the V<br>is 0 the reater. If 'd' is<br>register 'f'.<br>1                                                          | 27<br>D. (f) $\rightarrow$ (f)<br>0101<br>V register<br>sult is stor<br>1 the res                                                          | destinatio<br>dfff<br>with regist<br>red in the V                                                        | ffff<br>er 'f'. If 'd'<br><i>N</i> regis-                                |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                      | $0 \le f \le 12$<br>$d \in [0,1]$<br>(W) .ANE<br>Z<br>00<br>AND the V<br>is 0 the reater. If 'd' is<br>register 'f'.<br>1<br>1                                                     | 2.7<br>D. (f) $\rightarrow$ (f)<br>0101<br>V register<br>sult is stored<br>1 the res                                                       | destination<br>dfff<br>with regist<br>red in the V<br>ult is store                                       | ffff<br>er 'f'. If 'd'<br><i>N</i> regis-<br>d back in                   |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                      | $0 \le f \le 12$<br>$d \in [0,1]$<br>(W) .ANE<br>Z<br>00<br>AND the V<br>is 0 the re-<br>ter. If 'd' is<br>register 'f'.<br>1<br>1<br>Q1                                           | 27<br>D. (f) → (f)<br>0101<br>V register<br>sult is stored<br>1 the res<br>Q2<br>Read<br>register                                          | destination<br>dfff<br>with regist<br>red in the V<br>ult is store<br>Q3<br>Process                      | ffff<br>er 'f'. If 'd'<br><i>N</i> regis-<br>d back in<br>Q4<br>Write to |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $0 \le f \le 12$<br>$d \in [0,1]$<br>(W) .ANE<br>Z<br>00<br>AND the V<br>is 0 the re-<br>ter. If 'd' is<br>register 'f'.<br>1<br>1<br>Q1<br>Decode                                 | 27<br>D. (f) $\rightarrow$ (f)<br>0101<br>V register<br>sult is stou<br>1 the res<br>Q2<br>Read<br>register<br>ff<br>FSR,                  | destination<br>dfff<br>with regist<br>red in the V<br>ult is store<br>Q3<br>Process<br>data<br>1         | ffff<br>er 'f'. If 'd'<br><i>N</i> regis-<br>d back in<br>Q4<br>Write to |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $0 \le f \le 12$<br>$d \in [0,1]$<br>(W) .ANE<br>Z<br>00<br>AND the V<br>is 0 the rester. If 'd' is<br>register 'f'.<br>1<br>1<br>Q1<br>Decode<br>ANDWF<br>Before In               | 27<br>D. (f) → (f)<br>0101<br>V register<br>sult is stou<br>1 the res<br>Q2<br>Read<br>register<br>f'<br>FSR,<br>struction<br>W =          | destination<br>dfff<br>with regist<br>red in the V<br>ult is store<br>Q3<br>Process<br>data<br>1<br>0x17 | ffff<br>er 'f'. If 'd'<br><i>N</i> regis-<br>d back in<br>Q4<br>Write to |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $0 \le f \le 12$<br>$d \in [0,1]$<br>(W) .ANE<br>Z<br>00<br>AND the V<br>is 0 the rester. If 'd' is<br>register 'f'.<br>1<br>1<br>Q1<br>Decode<br>ANDWF<br>Before In               | 27<br>D. (f) → (f)<br>0101<br>V register<br>sult is stol<br>1 the res<br>Q2<br>Read<br>register<br>f'<br>FSR,<br>struction<br>W =<br>FSR = | destination<br>dfff<br>with regist<br>red in the V<br>ult is store<br>Q3<br>Process<br>data<br>1         | ffff<br>er 'f'. If 'd'<br><i>N</i> regis-<br>d back in<br>Q4<br>Write to |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $0 \le f \le 12$<br>$d \in [0,1]$<br>(W) .ANE<br>Z<br>00<br>AND the V<br>is 0 the rester. If 'd' is<br>register 'f'.<br>1<br>1<br>Q1<br>Decode<br>ANDWF<br>Before In<br>After Inst | 27<br>D. (f) → (f)<br>0101<br>V register<br>sult is stol<br>1 the res<br>Q2<br>Read<br>register<br>f'<br>FSR,<br>struction<br>W =<br>FSR = | destination<br>dfff<br>with regist<br>red in the V<br>ult is store<br>Q3<br>Process<br>data<br>1<br>0x17 | ffff<br>er 'f'. If 'd'<br><i>N</i> regis-<br>d back in<br>Q4<br>Write to |

| BTFSS             | Bit Test f, S                         | Skip if S                                                                                                                                                  | Set                |                  | CALL                 | Call Sub                                                                                                                                                                                                  | proutine             |                  |                  |  |

|-------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--|

| Syntax:           | [ <i>label</i> ] BTFS                 | SS f,b                                                                                                                                                     |                    |                  | Syntax:              | [ <i>label</i> ] CALL k                                                                                                                                                                                   |                      |                  |                  |  |

| Operands:         | $0 \le f \le 127$                     |                                                                                                                                                            |                    | Operands:        | $0 \le k \le 2$      | $0 \le k \le 2047$                                                                                                                                                                                        |                      |                  |                  |  |

|                   | 0 ≤ b < 7                             |                                                                                                                                                            |                    |                  | Operation:           | (PC)+ 1-                                                                                                                                                                                                  | → TOS,               |                  |                  |  |

| Operation:        | skip if (f <b>) = 1</b>               |                                                                                                                                                            |                    |                  | $k \rightarrow PC <$ | ,                                                                                                                                                                                                         | 50 /0                |                  |                  |  |

| Status Affected:  | None                                  |                                                                                                                                                            |                    |                  | <b>.</b>             | ,                                                                                                                                                                                                         | 1<4:3>) -            | → PC<12          | :11>             |  |

| Encoding:         | 01 13                                 | L1bb                                                                                                                                                       | bfff               | ffff             | Status Affected:     | None                                                                                                                                                                                                      |                      |                  | 1 1              |  |

| Description:      | If bit 'b' in regi                    |                                                                                                                                                            |                    | ne next          | Encoding:            | 10                                                                                                                                                                                                        | 0kkk                 | kkkk             | kkkk             |  |

| Words:            | If bit 'b' is '1', t<br>discarded and | instruction is executed.<br>If bit 'b' is '1', then the next instruction is<br>discarded and a NOP is executed<br>instead, making this a 2TCY instruction. |                    |                  | Description:         | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is loaded<br>into PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH. CALL |                      |                  |                  |  |

| Cycles:           | 1(2)                                  |                                                                                                                                                            |                    |                  |                      |                                                                                                                                                                                                           | ycle instru          | ction.           |                  |  |

| Q Cycle Activity: | Q1                                    | Q2                                                                                                                                                         | Q3                 | Q4               | Words:               | 1                                                                                                                                                                                                         |                      |                  |                  |  |

|                   |                                       | Read                                                                                                                                                       | Process            | No-Operat        | Cycles:              | 2                                                                                                                                                                                                         | 0.0                  |                  | <u>.</u>         |  |

|                   | reș                                   | egister 'f'                                                                                                                                                | data               | ion              | Q Cycle Activity:    | Q1                                                                                                                                                                                                        | Q2                   | Q3               | Q4               |  |

| If Skip:          | (2nd Cycle)                           | )                                                                                                                                                          |                    |                  | 1st Cycle            | Decode                                                                                                                                                                                                    | Read<br>literal 'k', | Process<br>data  | Write to<br>PC   |  |

|                   | Q1                                    | Q2                                                                                                                                                         | Q3                 | Q4               |                      |                                                                                                                                                                                                           | Push PC<br>to Stack  |                  |                  |  |

|                   | No-Operat<br>ion                      | o-Operati<br>on                                                                                                                                            | No-Opera<br>tion   | No-Operat<br>ion | 2nd Cycle            | No-Opera<br>tion                                                                                                                                                                                          | No-Opera<br>tion     | No-Opera<br>tion | No-Operat<br>ion |  |

| Example           |                                       |                                                                                                                                                            | FLAG,1<br>PROCESS  | CODE             | Example              | HERE                                                                                                                                                                                                      | CALL                 | THERE            |                  |  |

|                   | TRUE •                                | •                                                                                                                                                          | -                  | _                |                      | Before Ir                                                                                                                                                                                                 | nstruction           |                  |                  |  |

|                   | •                                     | •                                                                                                                                                          |                    |                  |                      | After Ins                                                                                                                                                                                                 | -                    | ddress HE        | RE               |  |

|                   | Before Instru                         | ruction                                                                                                                                                    |                    |                  |                      |                                                                                                                                                                                                           | PC = A               | ddress TH        |                  |  |

|                   |                                       |                                                                                                                                                            | ddress H           | IERE             |                      |                                                                                                                                                                                                           | TOS = A              | ddress HE        | RE+1             |  |

|                   | After Instruc                         |                                                                                                                                                            | 0                  |                  |                      |                                                                                                                                                                                                           |                      |                  |                  |  |

|                   | PC                                    | FLAG<1><br>C = a                                                                                                                                           | = 0,<br>address F7 | ALSE             |                      |                                                                                                                                                                                                           |                      |                  |                  |  |

|                   | if Fl                                 | LAG<1>                                                                                                                                                     | = 1,               |                  |                      |                                                                                                                                                                                                           |                      |                  |                  |  |

|                   | PC                                    | C = 6                                                                                                                                                      | address TH         | RUE              |                      |                                                                                                                                                                                                           |                      |                  |                  |  |

# PIC16F8X

| INCFSZ            | Increment f, Skip if 0                                                                                                                                           | IORLW             | Inclusive OR Literal with W                                                   |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------|

| Syntax:           | [label] INCFSZ f,d                                                                                                                                               | Syntax:           | [ <i>label</i> ] IORLW k                                                      |

| Operands:         | $0 \le f \le 127$                                                                                                                                                | Operands:         | $0 \le k \le 255$                                                             |

|                   | d ∈ [0,1]                                                                                                                                                        | Operation:        | (W) .OR. $k \rightarrow$ (W)                                                  |

| Operation:        | (f) + 1 $\rightarrow$ (destination),                                                                                                                             | Status Affected:  | Z                                                                             |

|                   | skip if result = 0                                                                                                                                               | Encoding:         | 11 1000 kkkk kkkk                                                             |

| Status Affected:  | None                                                                                                                                                             | Description:      | The contents of the W register is                                             |

| Encoding:         | 00 1111 dfff ffff                                                                                                                                                |                   | OR'ed with the eight bit literal 'k'. The result is placed in the W register. |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in                                                                           | Words:            | 1                                                                             |

|                   | the W register. If 'd' is 1 the result is<br>placed back in register 'f'.                                                                                        | Cycles:           | 1                                                                             |

|                   | If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is exe-<br>cuted instead making it a 2TCY instruc-                            | -                 |                                                                               |

|                   | cuted instead making it a 2Tcy instruc-<br>tion.                                                                                                                 | Q Cycle Activity: | Q1 Q2 Q3 Q4 Decode Read Process Write to                                      |