Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | 36 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f83-04i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16F8X is a group in the PIC16CXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers. This group contains the following devices:

- PIC16F83

- PIC16F84

- PIC16CR83

- PIC16CR84

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. PIC16F8X devices have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with a separate 8-bit wide data bus. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set is used to achieve a very high performance level.

PIC16F8X microcontrollers typically achieve a 2:1 code compression and up to a 4:1 speed improvement (at 20 MHz) over other 8-bit microcontrollers in their class.

The PIC16F8X has up to 68 bytes of RAM, 64 bytes of Data EEPROM memory, and 13 I/O pins. A timer/counter is also available.

The PIC16CXX family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers power saving. The user can wake the chip from sleep through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

The devices with Flash program memory allow the same device package to be used for prototyping and production. In-circuit reprogrammability allows the code to be updated without the device being removed from the end application. This is useful in the development of many applications where the device may not be easily accessible, but the prototypes may require code updates. This is also useful for remote applications where the code may need to be updated (such as rate information). Table 1-1 lists the features of the PIC16F8X. A simplified block diagram of the PIC16F8X is shown in Figure 3-1.

The PIC16F8X fits perfectly in applications ranging from high speed automotive and appliance motor control to low-power remote sensors, electronic locks, security devices and smart cards. The Flash/EEPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, security codes, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high performance, ease-of-use and I/O flexibility make the PIC16F8X very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions; serial communication; capture, compare and PWM functions; and co-processor applications).

The serial in-system programming feature (via two pins) offers flexibility of customizing the product after complete assembly and testing. This feature can be used to serialize a product, store calibration data, or program the device with the current firmware before shipping.

# 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for PIC16C5X devices can be easily ported to PIC16F8X devices (Appendix B).

# 1.2 <u>Development Support</u>

The PIC16CXX family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler and fuzzy logic support tools are also available.

# TABLE 1-1 PIC16F8X FAMILY OF DEVICES

|             |                                         | PIC16F83            | PIC16CR83           | PIC16F84            | PIC16CR84           |

|-------------|-----------------------------------------|---------------------|---------------------|---------------------|---------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz) | 10                  | 10                  | 10                  | 10                  |

|             | Flash Program Memory                    | 512                 | —                   | 1K                  | —                   |

|             | EEPROM Program Memory                   | —                   | —                   | —                   | —                   |

| Memory      | ROM Program Memory                      | —                   | 512                 | —                   | 1K                  |

|             | Data Memory (bytes)                     | 36                  | 36                  | 68                  | 68                  |

|             | Data EEPROM (bytes)                     | 64                  | 64                  | 64                  | 64                  |

| Peripherals | Timer Module(s)                         | TMR0                | TMR0                | TMR0                | TMR0                |

|             | Interrupt Sources                       | 4                   | 4                   | 4                   | 4                   |

|             | I/O Pins                                | 13                  | 13                  | 13                  | 13                  |

| Features    | Voltage Range (Volts)                   | 2.0-6.0             | 2.0-6.0             | 2.0-6.0             | 2.0-6.0             |

|             | Packages                                | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC |

All PIC<sup>®</sup> Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16F8X Family devices use serial programming with clock pin RB6 and data pin RB7.

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture. This architecture has the program and data accessed from separate memories. So the device has a program memory bus and a data memory bus. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory (accesses over the same bus). Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. PIC16CXX opcodes are 14-bits wide, enabling single word instructions. The full 14-bit wide program memory bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions execute in a single cycle except for program branches.

The PIC16F83 and PIC16CR83 address 512 x 14 of program memory, and the PIC16F84 and PIC16CR84 address 1K x 14 program memory. All program memory is internal.

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. An orthogonal (symmetrical) instruction set makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

# TABLE 4-1 REGISTER FILE SUMMARY

| Address | Name                  | Bit 7     | Bit 6                                  | Bit 5        | Bit 4             | Bit 3          | Bit 2         | Bit 1 | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note3) |

|---------|-----------------------|-----------|----------------------------------------|--------------|-------------------|----------------|---------------|-------|---------|-------------------------------|-----------------------------------------|

| Bank 0  |                       |           |                                        |              | •                 |                |               |       |         |                               | •                                       |

| 00h     | INDF                  | Uses co   | ntents of F                            | SR to addre  | ess data memor    | y (not a phys  | sical registe | r)    |         |                               |                                         |

| 01h     | TMR0                  | 8-bit rea | I-time clock                           | /counter     |                   |                |               |       |         | xxxx xxxx                     | uuuu uuuu                               |

| 02h     | PCL                   | Low ord   | er 8 bits of                           | the Program  | m Counter (PC)    |                |               |       |         | 0000 0000                     | 0000 0000                               |

| 03h     | STATUS <sup>(2)</sup> | IRP       | RP1                                    | RP0          | TO                | PD             | Z             | DC    | С       | 0001 1xxx                     | 000q quuu                               |

| 04h     | FSR                   | Indirect  | Indirect data memory address pointer 0 |              |                   |                |               |       |         |                               | uuuu uuuu                               |

| 05h     | PORTA                 | —         | —                                      | _            | RA4/T0CKI         | RA3            | RA2           | RA1   | RA0     | x xxxx                        | u uuuu                                  |

| 06h     | PORTB                 | RB7       | RB6                                    | RB5          | RB4               | RB3            | RB2           | RB1   | RB0/INT | XXXX XXXX                     | uuuu uuuu                               |

| 07h     |                       | Unimple   | Unimplemented location, read as '0'    |              |                   |                |               |       |         |                               |                                         |

| 08h     | EEDATA                | EEPRO     | EEPROM data register                   |              |                   |                |               |       |         | XXXX XXXX                     | uuuu uuuu                               |

| 09h     | EEADR                 | EEPROI    | EEPROM address register                |              |                   |                |               |       |         | XXXX XXXX                     | uuuu uuuu                               |

| 0Ah     | PCLATH                | _         |                                        | _            | Write buffer for  | r upper 5 bit  | s of the PC   | (1)   |         | 0 0000                        | 0 0000                                  |

| 0Bh     | INTCON                | GIE       | EEIE                                   | TOIE         | INTE              | RBIE           | TOIF          | INTF  | RBIF    | 0000 000x                     | 0000 000u                               |

| Bank 1  |                       |           |                                        |              |                   |                |               |       |         |                               |                                         |

| 80h     | INDF                  | Uses co   | ntents of F                            | SR to addre  | ess data memor    | y (not a phys  | sical registe | r)    |         |                               |                                         |

| 81h     | OPTION_<br>REG        | RBPU      | INTEDG                                 | TOCS         | TOSE              | PSA            | PS2           | PS1   | PS0     | 1111 1111                     | 1111 1111                               |

| 82h     | PCL                   | Low ord   | er 8 bits of                           | Program C    | ounter (PC)       |                |               | •     | •       | 0000 0000                     | 0000 0000                               |

| 83h     | STATUS (2)            | IRP       | RP1                                    | RP0          | TO                | PD             | Z             | DC    | С       | 0001 1xxx                     | 000q quuu                               |

| 84h     | FSR                   | Indirect  | data memo                              | ry address   | pointer 0         |                |               |       |         | xxxx xxxx                     | uuuu uuuu                               |

| 85h     | TRISA                 | —         | —                                      | —            | PORTA data d      | irection regis | ster          |       |         | 1 1111                        | 1 1111                                  |

| 86h     | TRISB                 | PORTB     | data directi                           | on register  | •                 |                |               |       |         | 1111 1111                     | 1111 1111                               |

| 87h     |                       | Unimple   | mented loc                             | ation, read  | as '0'            |                |               |       |         |                               |                                         |

| 88h     | EECON1                | —         | _                                      | _            | EEIF              | WRERR          | WREN          | WR    | RD      | 0 x000                        | 0 q000                                  |

| 89h     | EECON2                | EEPRO     | V control re                           | gister 2 (no | ot a physical reg | ister)         | -             |       |         |                               |                                         |

| 0Ah     | PCLATH                | _         | _                                      | _            | Write buffer for  | r upper 5 bit  | s of the PC   | (1)   |         | 0 0000                        | 0 0000                                  |

| 0Bh     | INTCON                | GIE       | EEIE                                   | TOIE         | INTE              | RBIE           | TOIF          | INTF  | RBIF    | 0000 000x                     | 0000 000u                               |

Legend: x = unknown, u = unchanged. - = unimplemented read as '0', q = value depends on condition.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a slave register for PC<12:8>. The contents of PCLATH can be transferred to the upper byte of the program counter, but the contents of PC<12:8> is never transferred to PCLATH.

2: The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  status bits in the STATUS register are not affected by a  $\overline{\text{MCLR}}$  reset.

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

#### 4.2.2.1 STATUS REGISTER

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bit for data memory.

As with any register, the STATUS register can be the destination for any instruction. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

Only the BCF, BSF, SWAPF and MOVWF instructions should be used to alter the STATUS register (Table 9-2) because these instructions do not affect any status bit.

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16F8X and should be programmed as cleared. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

- Note 3: When the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. The specified bit(s) will be updated according to device logic

| <u>R/W-0</u><br>IRP                                                                                                                                                                                                                                                                               | <u>R/W-0</u><br>RP1                       | R/W-0<br>RP0                              | <u>R-1</u><br>TO                                 | <u>R-1</u><br>PD                                         | R/W-x<br>Z                                    | R/W-x<br>DC                                 | R/W-x                 | R = Readable bit                                                                      |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------------------------|----------------------------------------------------------|-----------------------------------------------|---------------------------------------------|-----------------------|---------------------------------------------------------------------------------------|--|

| bit7                                                                                                                                                                                                                                                                                              |                                           | nru                                       |                                                  | FU                                                       | 2                                             |                                             | bit0                  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |

| bit 7:                                                                                                                                                                                                                                                                                            | 0 = Bank<br>1 = Bank                      | 0, 1 (00h -<br>2, 3 (100h                 | FFh)<br>- 1FFh)                                  |                                                          | indirect add<br>X. IRP shor                   | -                                           | ntained clea          | ar.                                                                                   |  |

| bit 6-5: <b>RP1:RP0</b> : Register Bank Select bits (used for direct addressing)<br>00 = Bank 0 (00h - 7Fh)<br>01 = Bank 1 (80h - FFh)<br>10 = Bank 2 (100h - 17Fh)<br>11 = Bank 3 (180h - 1FFh)<br>Each bank is 128 bytes. Only bit RP0 is used by the PIC16F8X. RP1 should be maintained clear. |                                           |                                           |                                                  |                                                          |                                               |                                             |                       |                                                                                       |  |

| bit 4:                                                                                                                                                                                                                                                                                            |                                           |                                           |                                                  |                                                          |                                               |                                             |                       |                                                                                       |  |

| bit 3:                                                                                                                                                                                                                                                                                            | 1 = After                                 | er-down bit<br>power-up o<br>ecution of   | or by the                                        |                                                          |                                               |                                             |                       |                                                                                       |  |

| bit 2:                                                                                                                                                                                                                                                                                            |                                           | esult of an                               |                                                  |                                                          | operation is                                  |                                             |                       |                                                                                       |  |

| bit 1:                                                                                                                                                                                                                                                                                            | 1 = A car                                 | ry-out from                               | the 4th lo                                       | ow order b                                               | nd ADDLW in<br>it of the res<br>bit of the re | ult occurre                                 |                       | $\overline{w}$ the polarity is reversed)                                              |  |

| bit 0:                                                                                                                                                                                                                                                                                            | 1 = A can<br>0 = No ca<br>Note:For<br>the | ry-out from<br>arry-out fro<br>borrow the | the most<br>m the mo<br>e polarity<br>perand. Fo | significan<br>st significa<br>is reverse<br>or rotate (F |                                               | result occu<br>e result occ<br>ction is exe | curred<br>ecuted by a | adding the two's complement of<br>baded with either the high or low                   |  |

# FIGURE 4-1: STATUS REGISTER (ADDRESS 03h, 83h)

#### 4.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external INT interrupt, TMR0, and the weak pull-ups on PORTB.

# FIGURE 4-1: OPTION\_REG REGISTER (ADDRESS 81h)

**Note:** When the prescaler is assigned to the WDT (PSA = '1'), TMR0 has a 1:1 prescaler assignment.

| R/W-1            | R/W-1                                                                                       | R/W-1                                                                            | R/W-1 | R/W-1      | R/W-1      | R/W-1    | R/W-1 |                                       |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------|------------|------------|----------|-------|---------------------------------------|--|--|--|--|

| RBPU             | INTEDG                                                                                      | TOCS                                                                             | T0SE  | PSA        | PS2        | PS1      | PS0   | R = Readable bit                      |  |  |  |  |

| bit7             |                                                                                             |                                                                                  |       |            |            |          | bit0  | W = Writable bit                      |  |  |  |  |

|                  |                                                                                             |                                                                                  |       |            |            |          |       | U = Unimplemented bit,<br>read as '0' |  |  |  |  |

|                  |                                                                                             |                                                                                  |       |            |            |          |       | - n = Value at POR reset              |  |  |  |  |

| bit 7:           |                                                                                             |                                                                                  |       |            |            |          |       |                                       |  |  |  |  |

| Dit 7.           | 1 = PORTB pull-ups are disabled                                                             |                                                                                  |       |            |            |          |       |                                       |  |  |  |  |

|                  | 0 = PORTB pull-ups are enabled (by individual port latch values)                            |                                                                                  |       |            |            |          |       |                                       |  |  |  |  |

| bit 6:           |                                                                                             |                                                                                  |       |            |            |          |       |                                       |  |  |  |  |

| bit 0.           |                                                                                             | •                                                                                | •     |            | nin        |          |       |                                       |  |  |  |  |

|                  | 1 = Interrupt on rising edge of RB0/INT pin<br>0 = Interrupt on falling edge of RB0/INT pin |                                                                                  |       |            |            |          |       |                                       |  |  |  |  |

| bit 5:           |                                                                                             |                                                                                  |       |            | r          |          |       |                                       |  |  |  |  |

| Dit J.           |                                                                                             | <b>TOCS</b> : TMR0 Clock Source Select bit                                       |       |            |            |          |       |                                       |  |  |  |  |

|                  |                                                                                             | 1 = Transition on RA4/T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT) |       |            |            |          |       |                                       |  |  |  |  |

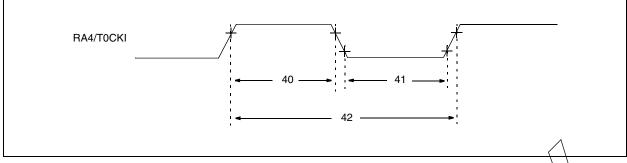

| bit 4:           | TOSE: TM                                                                                    |                                                                                  | •     |            |            |          |       |                                       |  |  |  |  |

| DIL 4.           |                                                                                             |                                                                                  |       |            | on RA4/T00 |          |       |                                       |  |  |  |  |

|                  |                                                                                             |                                                                                  |       |            | on RA4/T00 |          |       |                                       |  |  |  |  |

| bit 3:           | PSA: Pres                                                                                   |                                                                                  | •     |            |            | <b>P</b> |       |                                       |  |  |  |  |

| DIL 3.           | 1 = Presca                                                                                  |                                                                                  |       |            |            |          |       |                                       |  |  |  |  |

|                  | 0 = Presca                                                                                  |                                                                                  |       |            |            |          |       |                                       |  |  |  |  |

| hit 2 0.         | PS2:PS0:                                                                                    | •                                                                                |       |            |            |          |       |                                       |  |  |  |  |

| bit <u>∠</u> -0. |                                                                                             |                                                                                  |       |            |            |          |       |                                       |  |  |  |  |

|                  | Bit Value                                                                                   | TMR0 Ra                                                                          | te WD | Γ Rate     |            |          |       |                                       |  |  |  |  |

|                  | 000                                                                                         | 1:2                                                                              | 1 :   |            |            |          |       |                                       |  |  |  |  |

|                  | 001                                                                                         | 1:4                                                                              | 1:    |            |            |          |       |                                       |  |  |  |  |

|                  | 010<br>011                                                                                  | 1:8                                                                              |       | : 4<br>: 8 |            |          |       |                                       |  |  |  |  |

|                  | 100                                                                                         | 1 : 16<br>1 : 32                                                                 |       | 16         |            |          |       |                                       |  |  |  |  |

|                  | 101                                                                                         | 1:64                                                                             |       | 32         |            |          |       |                                       |  |  |  |  |

|                  | 110                                                                                         | 1 : 128                                                                          |       | 64         |            |          |       |                                       |  |  |  |  |

|                  | 111                                                                                         | 1 : 256                                                                          | 1:    | 128        |            |          |       |                                       |  |  |  |  |

|                  |                                                                                             |                                                                                  |       |            |            |          |       |                                       |  |  |  |  |

|                  |                                                                                             |                                                                                  |       |            |            |          |       |                                       |  |  |  |  |

### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch is unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output current may damage the chip.

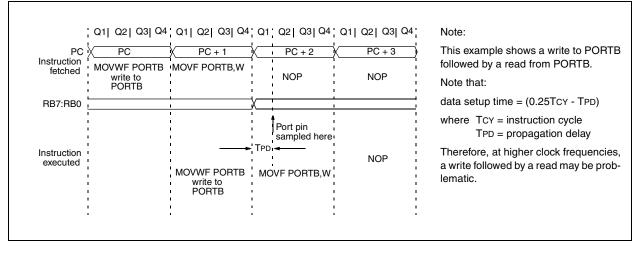

# 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-5). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such that the pin voltage stabilizes (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}\,,\,\,{\tt BSF},\, etc.)$  on an I/O port.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ;PORTB<7:6> have external pull-ups and are ;not connected to other circuitry

| ' |     |        |       |   |      |       |      |      |

|---|-----|--------|-------|---|------|-------|------|------|

| ; |     |        |       |   | PORT | latch | PORT | pins |

| ; |     |        |       |   |      |       |      |      |

|   | BCF | PORTB, | 7     | ; | 01pp | ppp   | 11pp | ppp  |

|   | BCF | PORTB, | 6     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BSF | STATUS | , RPO | ; |      |       |      |      |

|   | BCF | TRISB, | 7     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BCF | TRISB, | 6     | ; | 10pp | ppp   | 10pp | ppp  |

| : |     |        |       |   |      |       |      |      |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

# FIGURE 5-5: SUCCESSIVE I/O OPERATION

# 7.5 <u>Write Verify</u>

Depending on the application, good programming practice may dictate that the value written to the Data EEPROM should be verified (Example 7-1) to the desired value to be written. This should be used in applications where an EEPROM bit will be stressed near the specification limit. The Total Endurance disk will help determine your comfort level.

Generally the EEPROM write failure will be a bit which was written as a '1', but reads back as a '0' (due to leakage off the bit).

# EXAMPLE 7-1: WRITE VERIFY

|    | BCF    | STATUS,   | RP0   | ; | Bank 0               |

|----|--------|-----------|-------|---|----------------------|

|    | :      |           |       | ; | Any code can go here |

|    | :      |           |       | ; |                      |

|    | MOVF   | EEDATA,   | W     | ; | Must be in Bank 0    |

|    | BSF    | STATUS,   | RP0   | ; | Bank 1               |

| RE | EAD    |           |       |   |                      |

|    | BSF    | EECON1,   | RD    | ; | YES, Read the        |

|    |        |           |       | ; | value written        |

|    | BCF    | STATUS,   | RP0   | ; | Bank 0               |

| ;  |        |           |       |   |                      |

| ;  | Is the | value wr: | itter | ı | (in W reg) and       |

| ;  | read   | (in EEDA  | ΓA) t | h | e same?              |

|    |        |           |       |   |                      |

| SUBWF | EEDATA, W | ;               |     |

|-------|-----------|-----------------|-----|

| BTFSS | STATUS, Z | ; Is difference | 0?  |

| GOTO  | WRITE_ERR | ; NO, Write err | or  |

| :     |           | ; YES, Good wri | te  |

| :     |           | ; Continue prog | ram |

### 7.6 Protection Against Spurious Writes

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built in. On power-up, WREN is cleared. Also, the Power-up Timer (72 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch, or software malfunction.

#### 7.7 Data EEPROM Operation during Code Protect

When the device is code protected, the CPU is able to read and write unscrambled data to the Data EEPROM.

For ROM devices, there are two code protection bits (Section 8.1). One for the ROM program memory and one for the Data EEPROM memory.

# TABLE 7-1 REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name   | Bit 7    | Bit 6                       | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|--------|----------|-----------------------------|---------|-------|-------|-------|-------|-------|-------------------------------|---------------------------|

| 08h     | EEDATA | EEPROM   | EPROM data register         |         |       |       |       |       |       |                               | uuuu uuuu                 |

| 09h     | EEADR  | EEPROM a | address re                  | egister |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                 |

| 88h     | EECON1 | —        | — — — EEIF WRERR WREN WR RD |         |       |       |       |       | RD    | 0 x000                        | 0 q000                    |

| 89h     | EECON2 | EEPROM   | PROM control register 2     |         |       |       |       |       |       |                               |                           |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by Data EEPROM.

# FIGURE 8-6: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

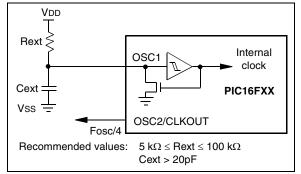

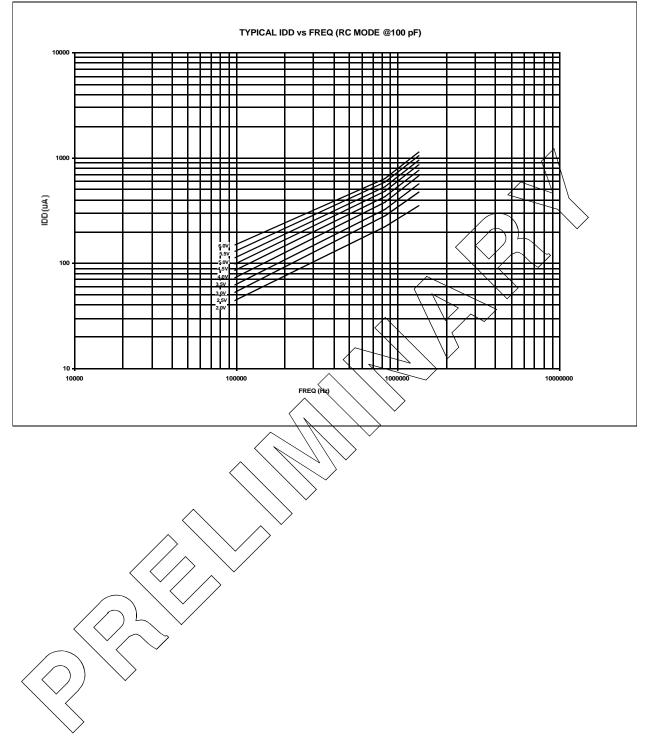

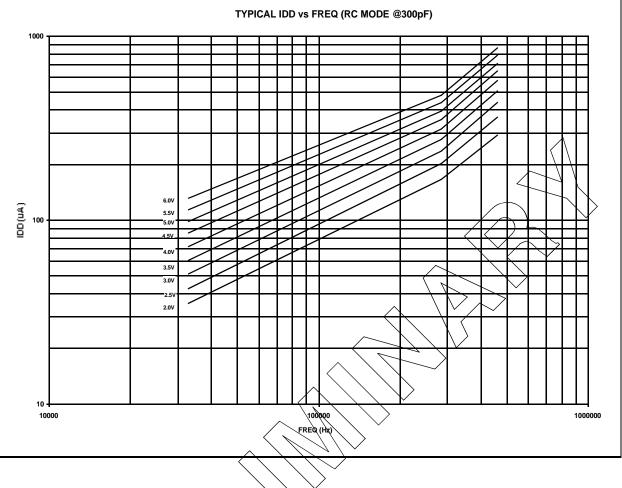

#### 8.2.4 RC OSCILLATOR

For timing insensitive applications the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) values, capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types also affects the oscillation frequency, especially for low Cext values. The user needs to take into account variation due to tolerance of the external R and C components. Figure 8-7 shows how an R/C combination is connected to the PIC16F8X. For Rext values below  $4 k\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g.,  $1 \text{ M}\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping Rext between 5 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With little or no external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See the electrical specification section for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance has a greater affect on RC frequency).

See the electrical specification section for variation of oscillator frequency due to VDD for given Rext/Cext values as well as frequency variation due to operating temperature.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-2 for waveform).

#### FIGURE 8-7: RC OSCILLATOR MODE

# 8.3 <u>Reset</u>

The PIC16F8X differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

Figure 8-8 shows a simplified block diagram of the on-chip reset circuit. The  $\overline{\text{MCLR}}$  reset path has a noise filter to ignore small pulses. The electrical specifications state the pulse width requirements for the  $\overline{\text{MCLR}}$  pin.

Some registers are not affected in any reset condition; their status is unknown on a POR reset and unchanged in any other reset. Most other registers are reset to a "reset state" on POR, MCLR or WDT reset during normal operation and on MCLR reset during SLEEP. They are not affected by a WDT reset during SLEEP, since this reset is viewed as the resumption of normal operation.

Table 8-3 gives a description of reset conditions for the program counter (PC) and the STATUS register. Table 8-4 gives a full description of reset states for all registers.

The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations (Section 8.7). These bits are used in software to determine the nature of the reset.

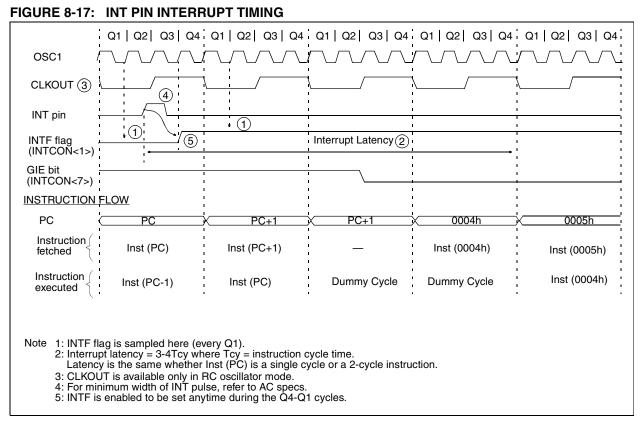

#### 8.9.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if INTEDG bit (OPTION\_REG<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing control bit INTE (INTCON<4>). Flag bit INTF must be cleared in software via the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake the processor from SLEEP (Section 8.12) only if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether the processor branches to the interrupt vector following wake-up.

#### 8.9.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in TMR0 will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 6.0).

#### 8.9.3 PORT RB INTERRUPT

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<3>) (Section 5.2).

**Note 1:** For a change on the I/O pin to be recognized, the pulse width must be at least TCY wide.

| CLRF              | Clear f                                                               |                         |                 |                       |  |  |  |  |

|-------------------|-----------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|--|

| Syntax:           | [label] C                                                             | [ <i>label</i> ] CLRF f |                 |                       |  |  |  |  |

| Operands:         | $0 \le f \le 12$                                                      | $0 \leq f \leq 127$     |                 |                       |  |  |  |  |

| Operation:        | $\begin{array}{c} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ | )                       |                 |                       |  |  |  |  |

| Status Affected:  | Z                                                                     |                         |                 |                       |  |  |  |  |

| Encoding:         | 00                                                                    | 0001                    | lfff            | ffff                  |  |  |  |  |

| Description:      | The contents of register 'f' are cleared and the Z bit is set.        |                         |                 |                       |  |  |  |  |

| Words:            | 1                                                                     |                         |                 |                       |  |  |  |  |

| Cycles:           | 1                                                                     |                         |                 |                       |  |  |  |  |

| Q Cycle Activity: | Q1                                                                    | Q2                      | Q3              | Q4                    |  |  |  |  |

|                   | Decode                                                                | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |

| Example           | CLRF                                                                  | FLAG                    | _REG            |                       |  |  |  |  |

|                   | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction            |                         |                 |                       |  |  |  |  |

|                   |                                                                       | FLAG_RE<br>Z            | EG =<br>=       | 0x00<br>1             |  |  |  |  |

| CLRW                                                                                    | Clear W                                                                                                                                                                                                                                                                                     |                                                                                             |                                                              |                                                                                |  |  |  |  |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                                                 | [ label ]                                                                                                                                                                                                                                                                                   | CLRW                                                                                        |                                                              |                                                                                |  |  |  |  |

| Operands:                                                                               | None                                                                                                                                                                                                                                                                                        |                                                                                             |                                                              |                                                                                |  |  |  |  |

| Operation:                                                                              | $00h \rightarrow (V 1 \rightarrow Z$                                                                                                                                                                                                                                                        | V)                                                                                          |                                                              |                                                                                |  |  |  |  |

| Status Affected:                                                                        | Z                                                                                                                                                                                                                                                                                           |                                                                                             |                                                              |                                                                                |  |  |  |  |

| Encoding:                                                                               | 00                                                                                                                                                                                                                                                                                          | 0001                                                                                        | 0xxx                                                         | xxxx                                                                           |  |  |  |  |

| Description:                                                                            | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                 |                                                                                             |                                                              |                                                                                |  |  |  |  |

| Words:                                                                                  | 1                                                                                                                                                                                                                                                                                           |                                                                                             |                                                              |                                                                                |  |  |  |  |

| Cycles:                                                                                 | 1                                                                                                                                                                                                                                                                                           |                                                                                             |                                                              |                                                                                |  |  |  |  |

| Q Cycle Activity:                                                                       | Q1                                                                                                                                                                                                                                                                                          | Q2                                                                                          | Q3                                                           | Q4                                                                             |  |  |  |  |

|                                                                                         | Decode                                                                                                                                                                                                                                                                                      | No-Opera<br>tion                                                                            | Process<br>data                                              | Write to<br>W                                                                  |  |  |  |  |

| Example                                                                                 | CLRW                                                                                                                                                                                                                                                                                        |                                                                                             |                                                              |                                                                                |  |  |  |  |

|                                                                                         | Before In                                                                                                                                                                                                                                                                                   |                                                                                             |                                                              |                                                                                |  |  |  |  |

|                                                                                         |                                                                                                                                                                                                                                                                                             | W = 0x5A<br>After Instruction                                                               |                                                              |                                                                                |  |  |  |  |

|                                                                                         |                                                                                                                                                                                                                                                                                             | W = 0x00                                                                                    |                                                              |                                                                                |  |  |  |  |

|                                                                                         |                                                                                                                                                                                                                                                                                             | Z =                                                                                         | 1                                                            |                                                                                |  |  |  |  |

|                                                                                         |                                                                                                                                                                                                                                                                                             |                                                                                             |                                                              |                                                                                |  |  |  |  |

| CLRWDT                                                                                  | Clear Wa                                                                                                                                                                                                                                                                                    | atchdog <sup>-</sup>                                                                        | Timer                                                        |                                                                                |  |  |  |  |

| Syntax:                                                                                 | [ label ]                                                                                                                                                                                                                                                                                   | CLRWD                                                                                       | Г                                                            |                                                                                |  |  |  |  |

| Operands:                                                                               | None                                                                                                                                                                                                                                                                                        |                                                                                             |                                                              |                                                                                |  |  |  |  |

| Operation:                                                                              | $00h \rightarrow WDT$                                                                                                                                                                                                                                                                       |                                                                                             |                                                              |                                                                                |  |  |  |  |

| oporation.                                                                              |                                                                                                                                                                                                                                                                                             |                                                                                             |                                                              |                                                                                |  |  |  |  |

|                                                                                         | $0 \rightarrow WD^{-1}$                                                                                                                                                                                                                                                                     | T prescale                                                                                  | er,                                                          |                                                                                |  |  |  |  |

|                                                                                         |                                                                                                                                                                                                                                                                                             |                                                                                             | er,                                                          |                                                                                |  |  |  |  |

| Status Affected:                                                                        | $\begin{array}{c} 0 \rightarrow WD^{-} \\ 1 \rightarrow \overline{TO} \end{array}$                                                                                                                                                                                                          |                                                                                             | er,                                                          |                                                                                |  |  |  |  |

|                                                                                         | $\begin{array}{c} 0 \rightarrow WD^{-} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$                                                                                                                                                                           |                                                                                             | er,                                                          | 0100                                                                           |  |  |  |  |

| Status Affected:                                                                        | $\begin{array}{c} 0 \rightarrow WD^{\circ} \\ 1 \rightarrow TO \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 \\ \hline \\ CLRWDT ir \\ dog Timer \end{array}$                                                                                                                           | T prescale                                                                                  | 0110<br>resets the pr                                        | Watch-<br>e <u>sc</u> aler                                                     |  |  |  |  |

| Status Affected:<br>Encoding:                                                           | $\begin{array}{c} 0 \rightarrow WD^{*} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \hline \overline{TO}, \overline{PD} \\ \hline \end{array} \\ \hline \begin{array}{c} 00 \\ \hline \end{array} \\ \hline \\ CLRWDT \ ir \\ dog \ Timer \\ of \ the \ WD \end{array}$ | 0000<br>01 talso res                                                                        | 0110<br>resets the pr                                        | Watch-<br>e <u>sc</u> aler                                                     |  |  |  |  |

| Status Affected:<br>Encoding:<br>Description:                                           | $\begin{array}{c} 0 \rightarrow WD^{\circ} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \hline \overline{TO}, \overline{PD} \\ \hline \end{array}$                                                                                                                      | 0000<br>01 talso res                                                                        | 0110<br>resets the pr                                        | Watch-<br>e <u>sc</u> aler                                                     |  |  |  |  |

| Status Affected:<br>Encoding:<br>Description:<br>Words:                                 | $\begin{array}{c} 0 \rightarrow WD^{\circ} \\ 1 \rightarrow TO \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline \end{array} \\ \hline \begin{array}{c} 00 \\ \\ CLRWDT \text{ irr} \\ dog Timer \\ of the WD \\ set. \\ \end{array} \\ \end{array}$                                           | 0000<br>01 talso res                                                                        | 0110<br>resets the pr                                        | Watch-<br>e <u>sc</u> aler                                                     |  |  |  |  |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                      | $\begin{array}{c} 0 \rightarrow WD^{\circ} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \hline \overline{TO}, \overline{PD} \\ \hline 00 \\ \hline \\ CLRWDT \ irr \\ dog \ Timer \\ of \ the \ WD \\ set. \\ 1 \\ 1 \end{array}$                                       | 0000<br>otruction r<br>. It also ree<br>T. Status b                                         | 0110<br>esets the pr<br>set <u>s th</u> e pr<br>its TO and   | Watch-<br>e <u>sc</u> aler<br>PD are                                           |  |  |  |  |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $\begin{array}{c} 0 \rightarrow WD^{\circ} \\ 1 \rightarrow TO \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 \\ \hline CLRWDT \text{ irr} \\ dog Timer \\ of the WD \\ set. \\ 1 \\ 1 \\ \hline Q1 \\ \end{array}$                                                                      | C prescale<br>0000<br>Instruction r<br>. It also ree<br>T. Status b<br>Q2<br>No-Opera       | 0110<br>esets the pr<br>its TO and<br>Q3<br>Process          | Watch-<br>escaler<br>PD are<br>Q4<br>Clear<br>WDT                              |  |  |  |  |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                      | $\begin{array}{c} 0 \rightarrow WD^{*}\\ 1 \rightarrow TO \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 \\ \hline CLRWDT irr \\ dog Timer \\ of the WD \\ set. \\ 1 \\ 1 \\ \hline Q1 \\ \hline Decode \\ \hline \\ CLRWDT \\ \end{array}$                                              | 0000<br>nstruction r<br>It also res<br>T. Status b<br>Q2<br>No-Opera<br>tion                | 0110<br>esets the pr<br>its TO and<br>Q3<br>Process          | Watch-<br>escaler<br>PD are<br>Q4<br>Clear<br>WDT                              |  |  |  |  |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $\begin{array}{c} 0 \rightarrow WD^{*}\\ 1 \rightarrow TO \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 \\ \hline CLRWDT inr \\ dog Timer \\ dog Timer \\ of the WD \\ set. \\ 1 \\ 1 \\ \hline Q1 \\ \hline CLRWDT \\ Before In \\ \end{array}$                                        | C prescale<br>0000<br>Instruction r<br>It also res<br>T. Status b<br>Q2<br>No-Opera<br>tion | 0110<br>sets the pr<br>its TO and<br>Q3<br>Process<br>data   | Watch-<br>escaler<br>PD are<br>Q4<br>Clear<br>WDT<br>Counter                   |  |  |  |  |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $\begin{array}{c} 0 \rightarrow WD^{*}\\ 1 \rightarrow TO \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 \\ \hline CLRWDT irr \\ dog Timer \\ of the WD \\ set. \\ 1 \\ 1 \\ \hline Q1 \\ \hline Decode \\ \hline \\ CLRWDT \\ \hline Before In \end{array}$                             | Q2<br>No-Opera<br>tion<br>WDT cour                                                          | 0110<br>sets the pr<br>its TO and<br>Q3<br>Process<br>data   | Watch-<br>escaler<br>PD are<br>Q4<br>Clear<br>WDT                              |  |  |  |  |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $\begin{array}{c} 0 \rightarrow WD^{*}\\ 1 \rightarrow TO \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 \\ \hline CLRWDT ir \\ dog Timer \\ of the WD \\ set. \\ 1 \\ 1 \\ Q1 \\ \hline Q1 \\ \hline CLRWDT \\ Before In \\ After Instein \\ \end{array}$                               | Q2<br>No-Opera<br>tion<br>WDT cour<br>WDT cour<br>WDT cour                                  | 0110<br>resets the pr<br>its TO and<br>Q3<br>Process<br>data | Watch-<br>escaler<br>PD are<br>Q4<br>Clear<br>WDT<br>Counter<br>?              |  |  |  |  |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $\begin{array}{c} 0 \rightarrow WD^{*}\\ 1 \rightarrow TO \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 \\ \hline CLRWDT ir \\ dog Timer \\ of the WD \\ set. \\ 1 \\ 1 \\ Q1 \\ \hline Q1 \\ \hline CLRWDT \\ Before In \\ After Instein \\ \end{array}$                               | Q2<br>No-Opera<br>tion<br>WDT cour<br>ruction                                               | 0110<br>resets the pr<br>its TO and<br>Q3<br>Process<br>data | Watch-<br>escaler<br>PD are<br>Q4<br>Clear<br>WDT<br>Counter                   |  |  |  |  |

| Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | $\begin{array}{c} 0 \rightarrow WD^{*}\\ 1 \rightarrow TO \\ 1 \rightarrow PD \\ \hline TO, PD \\ \hline 00 \\ \hline CLRWDT ir \\ dog Timer \\ of the WD \\ set. \\ 1 \\ 1 \\ Q1 \\ \hline Q1 \\ \hline CLRWDT \\ Before In \\ After Instein \\ \end{array}$                               | Q2<br>No-Opera<br>tion<br>WDT cour<br>WDT pres                                              | 0110<br>esets the pr<br>its TO and<br>Q3<br>Process<br>data  | Watch-<br>escaler<br>PD are<br>Q4<br>Clear<br>WDT<br>Counter<br>?<br>0x00<br>0 |  |  |  |  |

#### SLEEP

| Syntax:           | [ label ] SLEEP                                                                                                                                                                                                                                  |                  |                  |                |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------------|--|--|--|--|

| Operands:         | None                                                                                                                                                                                                                                             |                  |                  |                |  |  |  |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                             |                  |                  |                |  |  |  |  |

| Status Affected:  | TO, PD                                                                                                                                                                                                                                           |                  |                  |                |  |  |  |  |

| Encoding:         | 0 0                                                                                                                                                                                                                                              | 0000             | 0110             | 0011           |  |  |  |  |