#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 10MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 13                                                                      |

| Program Memory Size        | 896B (512 x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64 x 8                                                                  |

| RAM Size                   | 36 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

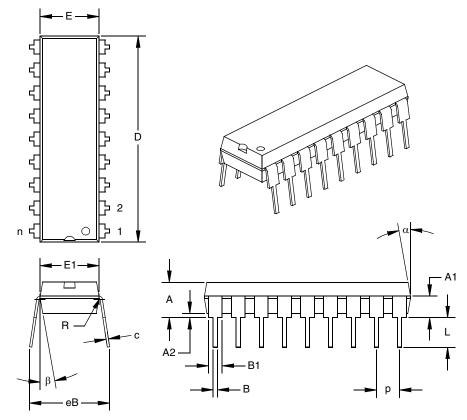

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 18-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f83-10-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | .0 General Description                                                              |     |

|-------|-------------------------------------------------------------------------------------|-----|

| 2.0   | 2.0 PIC16F8X Device Varieties                                                       | 5   |

| 3.0   | 3.0 Architectural Overview                                                          | 7   |

| 4.0   | I.0 Memory Organization                                                             |     |

| 5.0   | 5.0 I/O Ports                                                                       |     |

| 6.0   |                                                                                     |     |

| 7.0   |                                                                                     |     |

| 8.0   |                                                                                     |     |

| 9.0   | · · · · · · · · · · · · · · · · · · ·                                               |     |

| 10.0  |                                                                                     |     |

| 11.0  |                                                                                     | -   |

|       |                                                                                     |     |

| 13.0  |                                                                                     |     |

|       | 4.0 Packaging Information                                                           |     |

| Appe  | Appendix A: Feature Improvements - From PIC16C5X To PIC16F8X                        |     |

| Appe  | Appendix B: Code Compatibility - from PIC16C5X to PIC16F8X                          |     |

| Appe  | Appendix C: What's New In This Data Sheet                                           |     |

| Appe  | Appendix D: What's Changed In This Data Sheet                                       |     |

| Appe  | Appendix E: Conversion Considerations - PIC16C84 to PIC16F83/F84 And PIC16CR83/CR84 | 115 |

| Index | ndex                                                                                |     |

| On-L  | Dn-Line Support                                                                     | 119 |

| Read  | Reader Response                                                                     | 120 |

|       | PIC16F8X Product Identification System                                              |     |

| Sales | Sales and Support                                                                   |     |

# To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register), and the other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

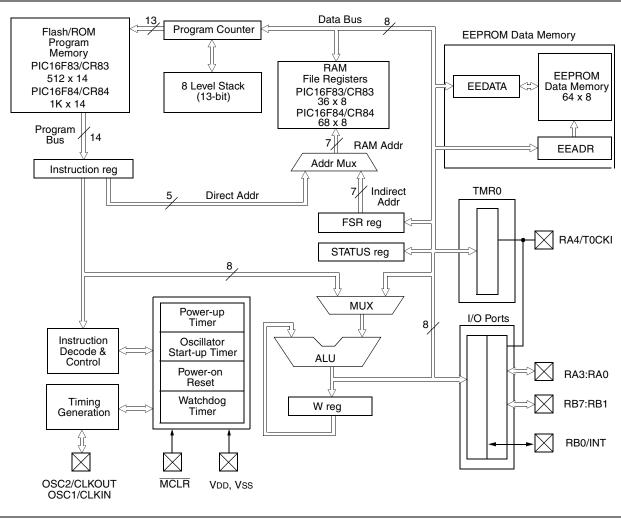

A simplified block diagram for the PIC16F8X is shown in Figure 3-1, its corresponding pin description is shown in Table 3-1.

### 4.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external INT interrupt, TMR0, and the weak pull-ups on PORTB.

# FIGURE 4-1: OPTION\_REG REGISTER (ADDRESS 81h)

**Note:** When the prescaler is assigned to the WDT (PSA = '1'), TMR0 has a 1:1 prescaler assignment.

| R/W-1            | R/W-1       | R/W-1            | R/W-1    | R/W-1      | R/W-1        | R/W-1        | R/W-1 |                                       |

|------------------|-------------|------------------|----------|------------|--------------|--------------|-------|---------------------------------------|

| RBPU             | INTEDG      | TOCS             | T0SE     | PSA        | PS2          | PS1          | PS0   | R = Readable bit                      |

| bit7             |             |                  |          |            |              |              | bit0  | W = Writable bit                      |

|                  |             |                  |          |            |              |              |       | U = Unimplemented bit,<br>read as '0' |

|                  |             |                  |          |            |              |              |       | - n = Value at POR reset              |

| bit 7:           | RBPU: PC    |                  | ın Enabl | a hit      |              |              |       |                                       |

| Dit 7.           | 1 = PORTI   |                  |          |            |              |              |       |                                       |

|                  |             |                  |          |            | dividual por | t latch valı | ues)  |                                       |

| bit 6:           | INTEDG:     |                  |          |            |              |              | ,     |                                       |

| bit 0.           | 1 = Interru | •                | •        |            | nin          |              |       |                                       |

|                  | 0 = Interru |                  |          |            |              |              |       |                                       |

| bit 5:           | TOCS: TM    |                  |          |            | F.           |              |       |                                       |

| Dit J.           | 1 = Transit |                  |          |            |              |              |       |                                       |

|                  | 0 = Interna |                  |          | •          | OUT)         |              |       |                                       |

| bit 4:           | TOSE: TM    |                  | •        |            |              |              |       |                                       |

| DIL 4.           |             |                  |          |            | on RA4/T00   |              |       |                                       |

|                  |             |                  |          |            | on RA4/T00   |              |       |                                       |

| bit 3:           | PSA: Pres   |                  | •        |            |              | <b>P</b>     |       |                                       |

| DIL 3.           | 1 = Presca  |                  |          |            |              |              |       |                                       |

|                  | 0 = Presca  |                  |          |            |              |              |       |                                       |

| hit 2 0.         | PS2:PS0:    | •                |          |            |              |              |       |                                       |

| bit <u>∠</u> -0. |             |                  |          |            |              |              |       |                                       |

|                  | Bit Value   | TMR0 Ra          | te WD    | Γ Rate     |              |              |       |                                       |

|                  | 000         | 1:2              | 1 :      |            |              |              |       |                                       |

|                  | 001         | 1:4              | 1:       |            |              |              |       |                                       |

|                  | 010<br>011  | 1:8              |          | : 4<br>: 8 |              |              |       |                                       |

|                  | 100         | 1 : 16<br>1 : 32 |          | 16         |              |              |       |                                       |

|                  | 101         | 1:64             |          | 32         |              |              |       |                                       |

|                  | 110         | 1 : 128          |          | 64         |              |              |       |                                       |

|                  | 111         | 1 : 256          | 1:       | 128        |              |              |       |                                       |

|                  |             |                  |          |            |              |              |       |                                       |

|                  |             |                  |          |            |              |              |       |                                       |

# 5.0 I/O PORTS

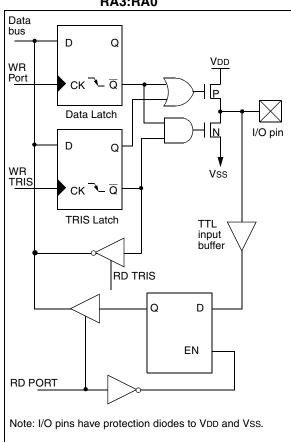

The PIC16F8X has two ports, PORTA and PORTB. Some port pins are multiplexed with an alternate function for other features on the device.

## 5.1 PORTA and TRISA Registers

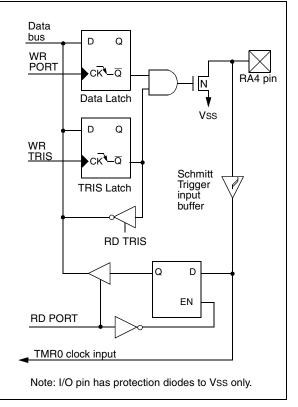

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, i.e., put the contents of the output latch on the selected pin.

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

The RA4 pin is multiplexed with the TMR0 clock input.

# FIGURE 5-1: BLOCK DIAGRAM OF PINS RA3:RA0

### EXAMPLE 5-1: INITIALIZING PORTA

| CLRF  | PORTA       | ; Initialize PORTA by   |

|-------|-------------|-------------------------|

|       |             | ; setting output        |

|       |             | ; data latches          |

| BSF   | STATUS, RPO | ; Select Bank 1         |

| MOVLW | 0x0F        | ; Value used to         |

|       |             | ; initialize data       |

|       |             | ; direction             |

| MOVWF | TRISA       | ; Set RA<3:0> as inputs |

|       |             | ; RA4 as outputs        |

|       |             | ; TRISA<7:5> are always |

|       |             | ; read as '0'.          |

### FIGURE 5-2: BLOCK DIAGRAM OF PIN RA4

# EXAMPLE 5-1: INITIALIZING PORTB

|       | -           |   |                       |

|-------|-------------|---|-----------------------|

| CLRF  | PORTB       | ; | Initialize PORTB by   |

|       |             | ; | setting output        |

|       |             | ; | data latches          |

| BSF   | STATUS, RPO | ; | Select Bank 1         |

| MOVLW | 0xCF        | ; | Value used to         |

|       |             | ; | initialize data       |

|       |             | ; | direction             |

| MOVWF | TRISB       | ; | Set RB<3:0> as inputs |

|       |             | ; | RB<5:4> as outputs    |

|       |             | ; | RB<7:6> as inputs     |

# TABLE 5-3 PORTB FUNCTIONS

| Name    | Bit  | Buffer Type           | I/O Consistency Function                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger.

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

# TABLE 5-4 SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name           | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|----------------|--------|--------|--------|--------|--------|--------|--------|---------|-------------------------------|---------------------------|

| 06h     | PORTB          | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0/INT | XXXX XXXX                     | uuuu uuuu                 |

| 86h     | TRISB          | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0  | 1111 1111                     | 1111 1111                 |

| 81h     | OPTION_<br>REG | RBPU   | INTEDG | TOCS   | TOSE   | PSA    | PS2    | PS1    | PS0     | 1111 1111                     | 1111 1111                 |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

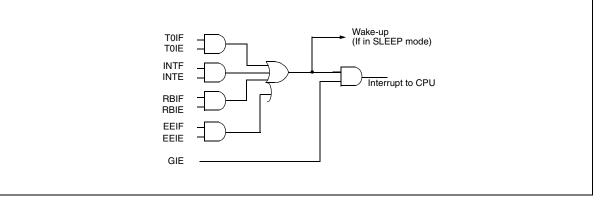

## 8.9 <u>Interrupts</u>

The PIC16F8X has 4 sources of interrupt:

- External interrupt RB0/INT pin

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB7:RB4)

- Data EEPROM write complete interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also contains the individual and global interrupt enable bits.

The global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. Bit GIE is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits interrupt routine as well as sets the GIE bit, which re-enable interrupts.

## FIGURE 8-16: INTERRUPT LOGIC

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

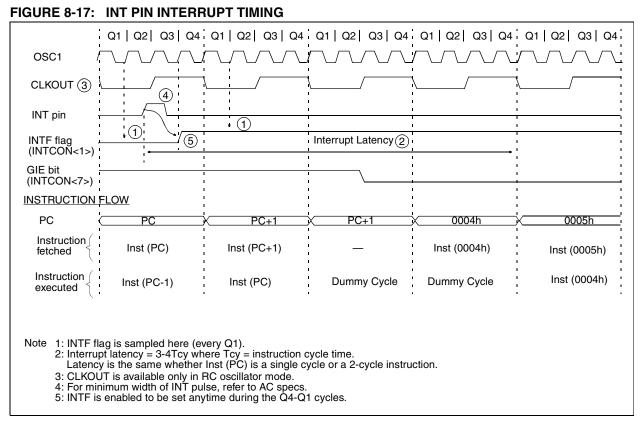

When an interrupt is responded to; the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. For external interrupt events, such as the RB0/INT pin or PORTB change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 8-17). The latency is the same for both one and two cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests.

Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

### 8.9.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if INTEDG bit (OPTION\_REG<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing control bit INTE (INTCON<4>). Flag bit INTF must be cleared in software via the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake the processor from SLEEP (Section 8.12) only if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether the processor branches to the interrupt vector following wake-up.

### 8.9.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in TMR0 will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 6.0).

### 8.9.3 PORT RB INTERRUPT

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<3>) (Section 5.2).

Note 1: For a change on the I/O pin to be recognized, the pulse width must be at least TCY wide.

#### 8.12.3 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

# 8.13 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting widowed devices.               |

### 8.14 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations to store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable only during program/verify. Only the 4 least significant bits of ID location are usable.

For ROM devices, these values are submitted along with the ROM code.

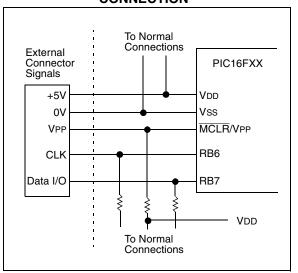

# 8.15 In-Circuit Serial Programming

PIC16F8X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. Customers can manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product, allowing the most recent firmware or custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low, while raising the MCLR pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) points to location 00h. A 6-bit command is then supplied to the device, 14-bits of program data is then supplied to or from the device, using load or read-type instructions. For complete details of serial programming, please refer to the PIC16CXX Programming Specifications (Literature #DS30189).

#### FIGURE 8-20: TYPICAL IN-SYSTEM SERIAL PROGRAMMING CONNECTION

For ROM devices, both the program memory and Data EEPROM memory may be read, but only the Data EEPROM memory may be programmed.

# PIC16F8X

| BCF               | Bit Clear                                                                     | f                       |                 |                       | BT         |

|-------------------|-------------------------------------------------------------------------------|-------------------------|-----------------|-----------------------|------------|

| Syntax:           | [ <i>label</i> ] BC                                                           | CF f,b                  |                 |                       | Syn        |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b \leq 7 \end{array}$            | 7                       |                 |                       | Ope        |

| Operation:        | $0 \rightarrow (f < b;$                                                       | >)                      |                 |                       | Ope        |

| Status Affected:  | None                                                                          |                         |                 |                       | Stat       |

| Encoding:         | 01                                                                            | 00bb                    | bfff            | ffff                  | Enc        |

| Description:      | Bit 'b' in re                                                                 | gister 'f' is           | s cleared.      | •                     | Des        |

| Words:            | 1                                                                             |                         |                 |                       |            |

| Cycles:           | 1                                                                             |                         |                 |                       |            |

| Q Cycle Activity: | Q1                                                                            | Q2                      | Q3              | Q4                    |            |

|                   | Decode                                                                        | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' | Woi<br>Cyc |

| Example           | BCF                                                                           | FLAG_                   | REG, 7          |                       | QC         |

|                   | Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction<br>FLAG_REG = 0x47 |                         |                 |                       |            |

| BTFSC             | Bit Test,                                                                                                                                                                                                                                                                               | Skip if Cl           | ear                |                  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|------------------|--|--|

| Syntax:           | [ <i>label</i> ] BT                                                                                                                                                                                                                                                                     | FSC f,b              |                    |                  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                                     |                      |                    |                  |  |  |

| Operation:        | skip if (f<                                                                                                                                                                                                                                                                             | b>) = 0              |                    |                  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                    |                      |                    |                  |  |  |

| Encoding:         | 01                                                                                                                                                                                                                                                                                      | 10bb                 | bfff               | ffff             |  |  |

| Description:      | If bit 'b' in register 'f' is '1' then the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a 2Tcy<br>instruction.                                                      |                      |                    |                  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                       |                      |                    |                  |  |  |

| Cycles:           | 1(2)                                                                                                                                                                                                                                                                                    |                      |                    |                  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                                                      | Q4                   |                    |                  |  |  |

|                   | Decode                                                                                                                                                                                                                                                                                  | Read<br>register 'f' | Process<br>data    | No-Operat<br>ion |  |  |

| If Skip:          | (2nd Cyc                                                                                                                                                                                                                                                                                | le)                  |                    |                  |  |  |

|                   | Q1                                                                                                                                                                                                                                                                                      | Q2                   | Q3                 | Q4               |  |  |

|                   | No-Operat<br>ion                                                                                                                                                                                                                                                                        | No-Operati<br>on     | No-Opera<br>tion   | No-Operat<br>ion |  |  |

| Example           | HERE<br>FALSE<br>TRUE                                                                                                                                                                                                                                                                   |                      | FLAG,1<br>PROCESS_ | _CODE            |  |  |

|                   | $\begin{array}{rcl} \text{Before Instruction} & \text{PC} &= & \text{address} & \text{HERE} \\ \text{After Instruction} & & \text{if FLAG<1>=0,} & \\ & \text{PC} &= & \text{address} & \text{TRUE} \\ & & \text{if FLAG<1>=1,} & \\ & \text{PC} &= & \text{address FALSE} \end{array}$ |                      |                    |                  |  |  |

| BSF               | Bit Set f                                                                     |                         |                 |                       |  |  |

|-------------------|-------------------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|

| Syntax:           | [ <i>label</i> ] BS                                                           | SF f,b                  |                 |                       |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$           |                         |                 |                       |  |  |

| Operation:        | $1 \rightarrow (f < b >$                                                      | >)                      |                 |                       |  |  |

| Status Affected:  | None                                                                          |                         |                 |                       |  |  |

| Encoding:         | 01                                                                            | 01bb                    | bfff            | ffff                  |  |  |

| Description:      | Bit 'b' in re                                                                 | gister 'f' is           | s set.          |                       |  |  |

| Words:            | 1                                                                             |                         |                 |                       |  |  |

| Cycles:           | 1                                                                             |                         |                 |                       |  |  |

| Q Cycle Activity: | Q1                                                                            | Q2                      | Q3              | Q4                    |  |  |

|                   | Decode                                                                        | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |

| Example           | BSF                                                                           | FLAG_F                  | REG, 7          |                       |  |  |

|                   | Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |                         |                 |                       |  |  |

# PIC16F8X

| NOP               | No Operation |                  |                  |                  |  |  |

|-------------------|--------------|------------------|------------------|------------------|--|--|

| Syntax:           | [ label ]    | NOP              |                  |                  |  |  |

| Operands:         | None         |                  |                  |                  |  |  |

| Operation:        | No opera     | ition            |                  |                  |  |  |

| Status Affected:  | None         |                  |                  |                  |  |  |

| Encoding:         | 00           | 0000             | 0xx0             | 0000             |  |  |

| Description:      | No operati   | ion.             |                  |                  |  |  |

| Words:            | 1            |                  |                  |                  |  |  |

| Cycles:           | 1            |                  |                  |                  |  |  |

| Q Cycle Activity: | Q1           | Q2               | Q3               | Q4               |  |  |

|                   | Decode       | No-Opera<br>tion | No-Opera<br>tion | No-Operat<br>ion |  |  |

| Example           | NOP          |                  |                  |                  |  |  |

| RETFIE            | Return fi                                                                         | rom Inter                                           | rupt                                       |                           |  |  |  |

|-------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------|---------------------------|--|--|--|

| Syntax:           | [ label ]                                                                         | RETFIE                                              |                                            |                           |  |  |  |

| Operands:         | None                                                                              |                                                     |                                            |                           |  |  |  |

| Operation:        | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                           |                                                     |                                            |                           |  |  |  |

| Status Affected:  | None                                                                              |                                                     |                                            |                           |  |  |  |

| Encoding:         | 0 0                                                                               | 0000                                                | 0000                                       | 1001                      |  |  |  |

| Description:      | Return fro<br>and Top of<br>PC. Interru<br>Global Inte<br>(INTCON<<br>instruction | Stack (TC<br>upts are er<br>errupt Ena<br>7>). This | DS) is load<br>habled by s<br>ble bit, GIE | ed in the<br>setting<br>E |  |  |  |

| Words:            | 1                                                                                 |                                                     |                                            |                           |  |  |  |

| Cycles:           | 2                                                                                 |                                                     |                                            |                           |  |  |  |

| Q Cycle Activity: | Q1                                                                                | Q2                                                  | Q3                                         | Q4                        |  |  |  |

| 1st Cycle         | Decode                                                                            | No-Opera<br>tion                                    | Set the<br>GIE bit                         | Pop from the Stack        |  |  |  |

| 2nd Cycle         | No-Operat<br>ion                                                                  | No-Opera<br>tion                                    | No-Opera<br>tion                           | No-Operat<br>ion          |  |  |  |

| Example           | RETFIE                                                                            |                                                     |                                            |                           |  |  |  |

After Interrupt PC = TOS GIE = 1

| OPTION           | Load Option Register                                                                                                                                                                                                                               |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] OPTION                                                                                                                                                                                                                                     |

| Operands:        | None                                                                                                                                                                                                                                               |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                               |

| Encoding:        | 00 0000 0110 0010                                                                                                                                                                                                                                  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code com-<br>patibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly address<br>it. |

| Words:           | 1                                                                                                                                                                                                                                                  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |

| Example          |                                                                                                                                                                                                                                                    |

|                  | To maintain upward compatibility<br>with future PIC16CXX products,<br>do not use this instruction.                                                                                                                                                 |

# PIC16F8X

| XORLW                                                       | Exclusive OR Literal with W                                                                   | XORWF                                       | Exclusive OR W with f                                                                                                                                                              |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                     | [ <i>label</i> ] XORLW k                                                                      | Syntax:                                     | [ <i>label</i> ] XORWF f,d                                                                                                                                                         |

| Operands:                                                   | $0 \le k \le 255$                                                                             | Operands:                                   | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                           |

| Operation:<br>Status Affected:<br>Encoding:<br>Description: | (W) .XOR. $k \rightarrow$ (W)<br>Z<br>11 1010 kkkk kkkk<br>The contents of the W register are | Operation:<br>Status Affected:<br>Encoding: | (W) .XOR. (f) $\rightarrow$ (destination)<br>Z                                                                                                                                     |

|                                                             | XOR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter.        | Description:                                | Exclusive OR the contents of the W<br>register with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'. |

| Words:                                                      | 1                                                                                             | Words:                                      | 1                                                                                                                                                                                  |

| Cycles:<br>Q Cycle Activity:                                | 1<br>Q1 Q2 Q3 Q4                                                                              | Cycles:<br>Q Cycle Activity:                | 1<br>Q1 Q2 Q3 Q4                                                                                                                                                                   |

|                                                             | Decode Read Process Write to<br>literal 'k' data W                                            |                                             | Decode Read Process Write to destination                                                                                                                                           |

| Example:                                                    | XORLW 0xAF                                                                                    |                                             |                                                                                                                                                                                    |

|                                                             | Before Instruction                                                                            | Example                                     | XORWF REG 1                                                                                                                                                                        |

|                                                             | W = 0xB5                                                                                      |                                             | Before Instruction                                                                                                                                                                 |

|                                                             | After Instruction<br>W = 0x1A                                                                 |                                             | $\begin{array}{rcl} REG &=& 0xAF \\ W &=& 0xB5 \end{array}$                                                                                                                        |

|                                                             |                                                                                               |                                             | After Instruction                                                                                                                                                                  |

|                                                             |                                                                                               |                                             | REG = 0x1A<br>W = 0xB5                                                                                                                                                             |

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC MCU. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

# 10.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC MCU series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

# 10.12 <u>C Compiler (MPLAB-C17)</u>

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC17CXXX family of microcontrollers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display.

## 10.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, Edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

# 10.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

# 10.15 <u>SEEVAL<sup>®</sup> Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in trade-off analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

# 10.16 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

# 10.3 DC CHARACTERISTICS:

#### PIC16F84, PIC16F83 (Commercial, Industrial) PIC16I F84 PIC16I F83 (Commercial Industrial)

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PIC16LF84, PIC16LF83 (Commercial, Industrial)                                                                                                      |        |                                           |                       |                                                       |           |                              |                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------|-----------------------|-------------------------------------------------------|-----------|------------------------------|--------------------------------------------------------------|

| -40°C $\leq$ TA $\leq$ +85°C (industrial)Porential operating voltage VDD range as described in DC spec<br>Section 10.1 and Section 10.2.Parameter<br>ter<br>No.SymCharacteristicMinTyptMaxUnitsConditionsD030Input Low Voltage<br>I/O portsInput Low Voltage<br>I/O portsVil.Input Low Voltage<br>I/O portsVil.Vil.ConditionsD030with TTL buffer<br>With CLR, RA4/T0CKIVss-0.8V4.5 V $\leq$ Vpb $\leq$ 5.5 V(4)D031<br>D033with Schmitt Trigger buffer<br>VII.Vss-0.2 VbpVentire Tange(4)D033<br>D034OSC1 (XT, HS and LP modes)(1)Vss-0.3 VbpVentire Tange(4)D040<br>D040AVIHInput High Voltage<br>I/O portsVbpVD041<br>D042With TTL buffer<br>(RC mode)2.4-VppVD043<br>D050OSC1 (XT, HS and LP modes)(1)<br>(RC mode)0.4 SVbp<br>VppVppVentire range(4)D044<br>D044with Schmitt Trigger buffer<br>(RC mode)0.4 SVbp<br>VppVppVentire range(4)D043<br>D050VHYS<br>Hysteresis of<br>Schmitt Trigger inputs-VppVVbpsD060<br>D061IIL<br>I/O portsInput Leakage Current(2/3)<br>OSC1±1µA<br>VSs $\leq$ VPIN $\leq$ VDD<br>VSs $\leq$ VPIN $\leq$ VDD<br>VSS $-±1µAVSS \leq VPIN \leq VDDVSS VppVppD060IILI/O ports±1$                 | <b>Standard Operating Conditions (unless otherwise stated</b><br><b>DC Characteristics</b> $0^{\circ}C_{1} < T_{2} < 10^{\circ}C_{1}$ (commercial) |        |                                           |                       |                                                       |           |                              |                                                              |

| Operating voltage VDD range as described in DC spec<br>Section 10.1 and Section 10.2.Parameter<br>No.SymCharacteristicMinTyptMaxUnitsConditionsD030Input Low Voltage<br>I/O portsInput Low Voltage<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                    |        |                                           |                       |                                                       |           |                              |                                                              |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                    |        |                                           |                       |                                                       |           |                              |                                                              |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                    |        |                                           | Section               | 0.1 and                                               | d Section | 10.2.                        |                                                              |

| No.SymCharacteristicMinTyp†MaxUnitsConditionsD030Input Low VoltageI/O portsInput Low VoltageInput Low VoltageInput Low VoltageInput Low VoltageD030With TTL bufferVss-0.8V4.5 V $\leq$ VBB $\leq$ 5.5 V <sup>(4)</sup> D031with Schmitt Trigger bufferVss-0.16VDDVD032MCLR, RA4/T0CKIVss-0.2VDDVD033OSC1 (XT, HS and LP modes) <sup>(1)</sup> Vss-0.3VDDVD034OSC1 (RC mode)Vss-0.1VDDVD040with Schmitt Trigger buffer0.48VDD-VDDVD041with Schmitt Trigger buffer0.48VDD-VbDVentre range <sup>(4)</sup> D042MCLR, RA4/T0CKI, OSC10.85Ventre rangeVentre rangeVentre rangeD043OSC1 (XT, HS and LP modes) <sup>(1)</sup> 0.7VDDVVentire rangeD044With Schmitt Trigger buffer0.45VDDVbDVentire rangeD043OSC1 (XT, HS and LP modes) <sup>(1)</sup> 0.7VDDVVDDSchmitt Trigger inputsD050VHYSHysteresis of<br>Schmitt Trigger inputsTBD-VD060IILI/O ports- $\pm$ 1 $\mu$ AVss $\leq$ VPIN $\leq$ VDD,<br>Pin at hi-impedanceD061MCLR, RA4/T0CRI $\pm$ 5 $\mu$ AVss $\leq$ VPIN $\leq$ VDD,<br>VIN $\leq$ VDDD063OSC1MCLR, RA4/T0CRI $\pm$ 1 $\mu$ A </th <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> |                                                                                                                                                    |        |                                           |                       |                                                       |           |                              |                                                              |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                    | Sym    | Characteristic                            | Min                   | Typt                                                  | Мах       | Units                        | Conditions                                                   |

| VILI/O ports<br>with TTL bufferVss-0.8V4.5 V $\leq$ VBb $\leq$ 5.5 V <sup>(4)</sup><br>entire range <sup>(4)</sup><br>entire range <sup>(4)</sup> D031with Schmitt Trigger bufferVss-0.16VDDVD032MCLR, RA4/T0CKIVss-0.2VDDVD033OSC1 (XT, HS and LP modes) <sup>(1)</sup> Vss-0.3VDDVD034OSC1 (RC mode)Vss-0.16VDDVD040OSC1 (RC mode)Vss-0.1VDDVD044With TTL buffer2.4-VDDVD040with Schmitt Trigger buffer0.48VDD-VDDVD041with Schmitt Trigger buffer0.45VDDVbDVentire range <sup>(4)</sup> D042MCLR, RA4/T0CKI, OSC10.85VDDVDDVD043OSC1 (XT, HS and LP modes) <sup>(1)</sup> 0.7VpDVpDVD050VHYSHysteresis of<br>Schmitt Trigger inputsTBD-VD070IPURBPORTB weak pull-up current50250*400*µAD060IILI/O ports-±1µAVss ≤ VPIN ≤ VDD,<br>Pin at hi-impedanceD061MCLR, RA4/T0CKI±5µAVss ≤ VPIN ≤ VDD,<br>Vin ≤ VDD,<br>Pin at hi-impedance                                                                                                                                                                                                                                                                                              |                                                                                                                                                    | -      |                                           |                       |                                                       |           |                              | 4                                                            |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                    | VIL    |                                           |                       |                                                       |           |                              |                                                              |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D030                                                                                                                                               |        | •                                         | Vss                   | _                                                     | 0.8       | v                            | $4.5 V \le VDD \le 5.5 V^{(4)}$                              |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D030A                                                                                                                                              |        |                                           | Vss                   | _                                                     | 0.16VDD   | V                            |                                                              |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D031                                                                                                                                               |        | with Schmitt Trigger buffer               | Vss                   | _                                                     | 0.2VDD    | V                            | entire range                                                 |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D032                                                                                                                                               |        | MCLR, RA4/T0CKI                           | Vss                   | —                                                     | 0.2VDD    | V                            |                                                              |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D033                                                                                                                                               |        | OSC1 (XT, HS and LP modes) <sup>(1)</sup> | Vss                   | —                                                     | 0.3VDD    | v <                          | $\langle \rangle \land \rangle$                              |

| VIHI/O ports-D040with TTL buffer2.4-D040Awith Schmitt Trigger buffer0.48VDD-D041with Schmitt Trigger buffer0.45VDDVbDD042MCLR, RA4/TOCKI, OSC10.85VbDD043OSC1 (XT, HS and LP modes) <sup>(1)</sup> 0.7VDDVpDD050VHYSHysteresis of<br>Schmitt Trigger inputsTBD-D070IPURBPORTB weak pull-up current50*250*D060IILI/O ports- $\pm 1$ D061MCLR, RA4/TOCKI $\pm 5$ D063OSC1 $\pm 5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D034                                                                                                                                               |        | OSC1 (RC mode)                            | Vss                   | —                                                     | 0.1VDD    | V                            | $\backslash$ $\langle$ $\checkmark$                          |