Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 68 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                             |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 18-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f84-04-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-1 PIC16F8X FAMILY OF DEVICES

|             |                                         | PIC16F83            | PIC16CR83           | PIC16F84            | PIC16CR84           |

|-------------|-----------------------------------------|---------------------|---------------------|---------------------|---------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz) | 10                  | 10                  | 10                  | 10                  |

|             | Flash Program Memory                    | 512                 | —                   | 1K                  | —                   |

|             | EEPROM Program Memory                   | —                   | —                   | —                   | —                   |

| Memory      | ROM Program Memory                      | —                   | 512                 | —                   | 1K                  |

|             | Data Memory (bytes)                     | 36                  | 36                  | 68                  | 68                  |

|             | Data EEPROM (bytes)                     | 64                  | 64                  | 64                  | 64                  |

| Peripherals | Timer Module(s)                         | TMR0                | TMR0                | TMR0                | TMR0                |

|             | Interrupt Sources                       | 4                   | 4                   | 4                   | 4                   |

|             | I/O Pins                                | 13                  | 13                  | 13                  | 13                  |

| Features    | Voltage Range (Volts)                   | 2.0-6.0             | 2.0-6.0             | 2.0-6.0             | 2.0-6.0             |

|             | Packages                                | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC |

All PIC<sup>®</sup> Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16F8X Family devices use serial programming with clock pin RB6 and data pin RB7.

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture. This architecture has the program and data accessed from separate memories. So the device has a program memory bus and a data memory bus. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory (accesses over the same bus). Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. PIC16CXX opcodes are 14-bits wide, enabling single word instructions. The full 14-bit wide program memory bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions execute in a single cycle except for program branches.

The PIC16F83 and PIC16CR83 address 512 x 14 of program memory, and the PIC16F84 and PIC16CR84 address 1K x 14 program memory. All program memory is internal.

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. An orthogonal (symmetrical) instruction set makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

| Pin Name         | DIP<br>No.     | SOIC<br>No.       | l/O/P<br>Type | Buffer<br>Type        | Description                                                                                                                                                                                              |

|------------------|----------------|-------------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN       | 16             | 16                | Ι             | ST/CMOS (3)           | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT      | 15             | 15                | 0             |                       | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR             | 4              | 4                 | I/P           | ST                    | Master clear (reset) input/programming voltage input. This pin is an active low reset to the device.                                                                                                     |

|                  |                |                   |               |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0              | 17             | 17                | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA1              | 18             | 18                | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA2              | 1              | 1                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA3              | 2              | 2                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA4/T0CKI        | 3              | 3                 | I/O           | ST                    | Can also be selected to be the clock input to the TMR0 timer/<br>counter. Output is open drain type.                                                                                                     |

|                  |                |                   |               |                       | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                       |

| RB0/INT          | 6              | 6                 | I/O           | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                               |

| RB1              | 7              | 7                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB2              | 8              | 8                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB3              | 9              | 9                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB4              | 10             | 10                | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB5              | 11             | 11                | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB6              | 12             | 12                | I/O           | TTL/ST <sup>(2)</sup> | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7              | 13             | 13                | I/O           | TTL/ST (2)            | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Vss              | 5              | 5                 | Р             | —                     | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| Vdd              | 14             | 14                | Р             | —                     | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Legend: I= input | 0 = 0<br>— = N | utput<br>lot used |               | /O = Input/Out        | •                                                                                                                                                                                                        |

# TABLE 3-1 PIC16F8X PINOUT DESCRIPTION

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

### 4.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external INT interrupt, TMR0, and the weak pull-ups on PORTB.

## FIGURE 4-1: OPTION\_REG REGISTER (ADDRESS 81h)

**Note:** When the prescaler is assigned to the WDT (PSA = '1'), TMR0 has a 1:1 prescaler assignment.

| R/W-1            | R/W-1                                                            | R/W-1            | R/W-1 | R/W-1      | R/W-1      | R/W-1 | R/W-1 |                                       |  |  |  |

|------------------|------------------------------------------------------------------|------------------|-------|------------|------------|-------|-------|---------------------------------------|--|--|--|

| RBPU             | INTEDG                                                           | TOCS             | T0SE  | PSA        | PS2        | PS1   | PS0   | R = Readable bit                      |  |  |  |

| bit7             |                                                                  |                  |       |            |            |       | bit0  | W = Writable bit                      |  |  |  |

|                  |                                                                  |                  |       |            |            |       |       | U = Unimplemented bit,<br>read as '0' |  |  |  |

|                  |                                                                  |                  |       |            |            |       |       | - n = Value at POR reset              |  |  |  |

| bit 7:           | <b>RBPU</b> : PORTB Pull-up Enable bit                           |                  |       |            |            |       |       |                                       |  |  |  |

| Dit 7.           | 1 = PORTB pull-ups are disabled                                  |                  |       |            |            |       |       |                                       |  |  |  |

|                  | 0 = PORTB pull-ups are enabled (by individual port latch values) |                  |       |            |            |       |       |                                       |  |  |  |

| bit 6:           | INTEDG:                                                          |                  |       |            | ·          |       | ,     |                                       |  |  |  |

| bit 0.           | 1 = Interru                                                      | •                | •     |            | nin        |       |       |                                       |  |  |  |

|                  | 0 = Interru                                                      |                  |       |            |            |       |       |                                       |  |  |  |

| bit 5:           | TOCS: TM                                                         |                  |       |            | F.         |       |       |                                       |  |  |  |

| Dit J.           | 1 = Transit                                                      |                  |       |            |            |       |       |                                       |  |  |  |

|                  | 0 = Interna                                                      |                  |       | •          | OUT)       |       |       |                                       |  |  |  |

| bit 4:           | TOSE: TM                                                         |                  | •     |            |            |       |       |                                       |  |  |  |

| DIL 4.           |                                                                  |                  |       |            | on RA4/T00 |       |       |                                       |  |  |  |

|                  |                                                                  |                  |       |            | on RA4/T00 |       |       |                                       |  |  |  |

| bit 3:           | PSA: Pres                                                        |                  | •     |            |            | p     |       |                                       |  |  |  |

| DIL 3.           | 1 = Presca                                                       |                  |       |            |            |       |       |                                       |  |  |  |

|                  | 0 = Presca                                                       |                  |       |            |            |       |       |                                       |  |  |  |

| hit 2 0.         | PS2:PS0:                                                         | •                |       |            |            |       |       |                                       |  |  |  |

| bit <u>∠</u> -0. |                                                                  |                  |       |            |            |       |       |                                       |  |  |  |

|                  | Bit Value                                                        | TMR0 Ra          | te WD | Γ Rate     |            |       |       |                                       |  |  |  |

|                  | 000                                                              | 1:2              | 1 :   |            |            |       |       |                                       |  |  |  |

|                  | 001                                                              | 1:4              | 1:    |            |            |       |       |                                       |  |  |  |

|                  | 010<br>011                                                       | 1:8              |       | : 4<br>: 8 |            |       |       |                                       |  |  |  |

|                  | 100                                                              | 1 : 16<br>1 : 32 |       | 16         |            |       |       |                                       |  |  |  |

|                  | 101                                                              | 1:64             |       | 32         |            |       |       |                                       |  |  |  |

|                  | 110                                                              | 1 : 128          |       | 64         |            |       |       |                                       |  |  |  |

|                  | 111                                                              | 1 : 256          | 1:    | 128        |            |       |       |                                       |  |  |  |

|                  |                                                                  |                  |       |            |            |       |       |                                       |  |  |  |

|                  |                                                                  |                  |       |            |            |       |       |                                       |  |  |  |

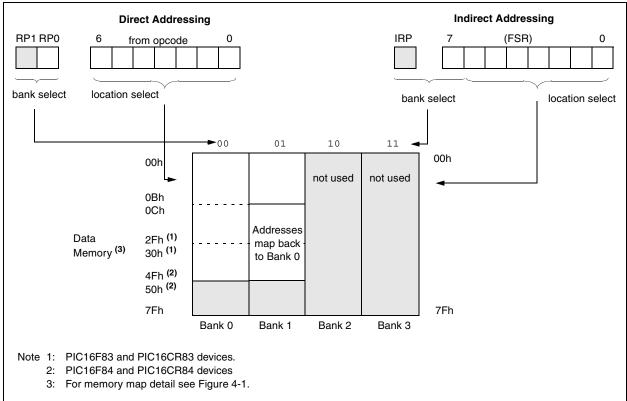

### 4.5 Indirect Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

### EXAMPLE 4-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

FIGURE 4-1: DIRECT/INDIRECT ADDRESSING

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-2.

### EXAMPLE 4-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | movwf | FSR   | ; to RAM             |

| NEXT     | clrf  | INDF  | ;clear INDF register |

|          | incf  | FSR   | ;inc pointer         |

|          | btfss | FSR,4 | ;all done?           |

|          | goto  | NEXT  | ;NO, clear next      |

| CONTINUE |       |       |                      |

|          | :     |       | ;YES, continue       |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-1. However, IRP is not used in the PIC16F8X.

### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch is unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output current may damage the chip.

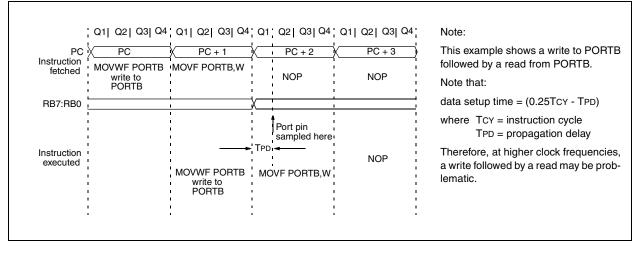

# 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-5). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such that the pin voltage stabilizes (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}\,,\,\,{\tt BSF},\, etc.)$  on an I/O port.

### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ;PORTB<7:6> have external pull-ups and are ;not connected to other circuitry

| ' |     |        |       |   |      |       |      |      |

|---|-----|--------|-------|---|------|-------|------|------|

| ; |     |        |       |   | PORT | latch | PORT | pins |

| ; |     |        |       |   |      |       |      |      |

|   | BCF | PORTB, | 7     | ; | 01pp | ppp   | 11pp | ppp  |

|   | BCF | PORTB, | 6     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BSF | STATUS | , RPO | ; |      |       |      |      |

|   | BCF | TRISB, | 7     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BCF | TRISB, | 6     | ; | 10pp | ppp   | 10pp | ppp  |

| : |     |        |       |   |      |       |      |      |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

# FIGURE 5-5: SUCCESSIVE I/O OPERATION

## 7.2 EECON1 and EECON2 Registers

EECON1 is the control register with five low order bits physically implemented. The upper-three bits are nonexistent and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$  reset or a WDT time-out reset during normal operation. In these situations, following reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit EEIF is set when write is complete. It must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the Data EEPROM write sequence.

### 7.3 Reading the EEPROM Data Memory

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD (EECON1<0>). The data is available, in the very next cycle, in the EEDATA register; therefore it can be read in the next instruction. EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

## EXAMPLE 7-1: DATA EEPROM READ

| BCF   | STATUS, RPO | ; Bank 0          |

|-------|-------------|-------------------|

| MOVLW | CONFIG_ADDR | ;                 |

| MOVWF | EEADR       | ; Address to read |

| BSF   | STATUS, RPO | ; Bank 1          |

| BSF   | EECON1, RD  | ; EE Read         |

| BCF   | STATUS, RPO | ; Bank 0          |

| MOVF  | EEDATA, W   | ; W = EEDATA      |

### 7.4 Writing to the EEPROM Data Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific sequence to initiate the write for each byte.

## EXAMPLE 7-1: DATA EEPROM WRITE

|                     | BSF<br>BCF | STATUS, RPO<br>INTCON, GIE | ' | Bank 1<br>Disable INTs. |

|---------------------|------------|----------------------------|---|-------------------------|

|                     | BSF        | EECON1, WREN               | ; | Enable Write            |

|                     | MOVLW      | 55h                        | ; |                         |

|                     | MOVWF      | EECON2                     | ; | Write 55h               |

| p e                 | MOVLW      | AAh                        | ; |                         |

| lequired<br>equence | MOVWF      | EECON2                     | ; | Write AAh               |

| ng ng               | BSF        | EECON1,WR                  | ; | Set WR bit              |

| Se                  |            |                            | ; | begin write             |

|                     | BSF        | INTCON, GIE                | ; | Enable INTs.            |

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

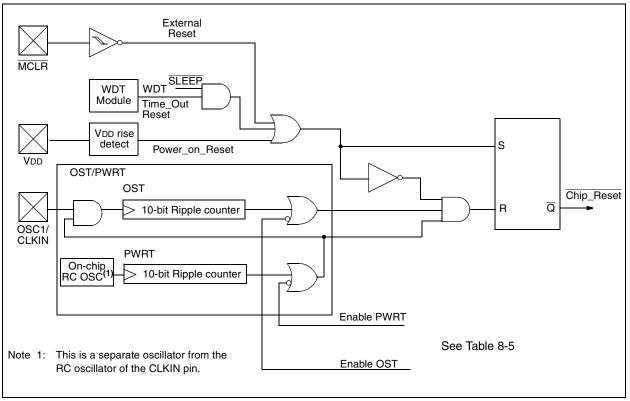

### FIGURE 8-8: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

### 8.4 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, just tie the  $\overline{MCLR}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A minimum rise time for VDD must be met for this to operate properly. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be meet to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting.*"

The POR circuit does not produce an internal reset when VDD declines.

### 8.5 Power-up Timer (PWRT)

The Power-up Timer (PWRT) provides a fixed 72 ms nominal time-out (TPWRT) from POR (Figure 8-10, Figure 8-11, Figure 8-12 and Figure 8-13). The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level (Possible exception shown in Figure 8-13).

A configuration bit, PWRTE, can enable/disable the PWRT. See either Figure 8-1 or Figure 8-2 for the operation of the PWRTE bit for a particular device.

The power-up time delay TPWRT will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

## 8.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle delay (from OSC1 input) after the PWRT delay ends (Figure 8-10, Figure 8-11, Figure 8-12 and Figure 8-13). This ensures the crystal oscillator or resonator has started and stabilized.

The OST time-out (TOST) is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

When VDD rises very slowly, it is possible that the TPWRT time-out and TOST time-out will expire before VDD has reached its final value. In this case (Figure 8-13), an external power-on reset circuit may be necessary (Figure 8-9).

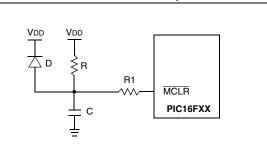

#### FIGURE 8-9: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up rate is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not exceed 0.2V (max leakage current spec on MCLR pin is 5 μA). A larger voltage drop will degrade VIH level on the MCLR pin.

- 3: R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of an MCLR pin breakdown due to ESD or EOS.

### 8.7 <u>Time-out Sequence and Power-down</u> Status Bits (TO/PD)

On power-up (Figure 8-10, Figure 8-11, Figure 8-12 and Figure 8-13) the time-out sequence is as follows: First PWRT time-out is invoked after a POR has expired. Then the OST is activated. The total time-out will vary based on oscillator configuration and PWRTE configuration bit status. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

# TABLE 8-5TIME-OUT IN VARIOUSSITUATIONS

| Oscillator    | Powe                | Wake-up          |               |

|---------------|---------------------|------------------|---------------|

| Configuration | PWRT<br>Enabled     | PWRT<br>Disabled | from<br>SLEEP |

| XT, HS, LP    | 72 ms +<br>1024Tosc | 1024Tosc         | 1024Tosc      |

| RC            | 72 ms               | _                | _             |

Since the time-outs occur from the POR reset pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high, execution will begin immediately (Figure 8-10). This is useful for testing purposes or to synchronize more than one PIC16F8X device when operating in parallel.

Table 8-6 shows the significance of the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits. Table 8-3 lists the reset conditions for some special registers, while Table 8-4 lists the reset conditions for all the registers.

# TABLE 8-6STATUS BITS AND THEIRSIGNIFICANCE

| то | PD | Condition                                                         |  |  |  |  |  |

|----|----|-------------------------------------------------------------------|--|--|--|--|--|

| 1  | 1  | Power-on Reset                                                    |  |  |  |  |  |

| 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |  |  |  |  |  |

| x  | 0  | Illegal, PD is set on POR                                         |  |  |  |  |  |

| 0  | 1  | WDT Reset (during normal operation)                               |  |  |  |  |  |

| 0  | 0  | WDT Wake-up                                                       |  |  |  |  |  |

| 1  | 1  | MCLR Reset during normal operation                                |  |  |  |  |  |

| 1  | 0  | MCLR Reset during SLEEP or interrupt                              |  |  |  |  |  |

|    |    | wake-up from SLEEP                                                |  |  |  |  |  |

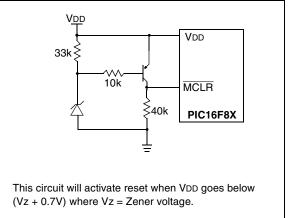

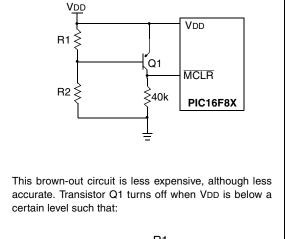

# 8.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset a PIC16F8X device when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 8-14 and Figure 8-15.

## FIGURE 8-14: BROWN-OUT PROTECTION CIRCUIT 1

## FIGURE 8-15: BROWN-OUT PROTECTION CIRCUIT 2

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

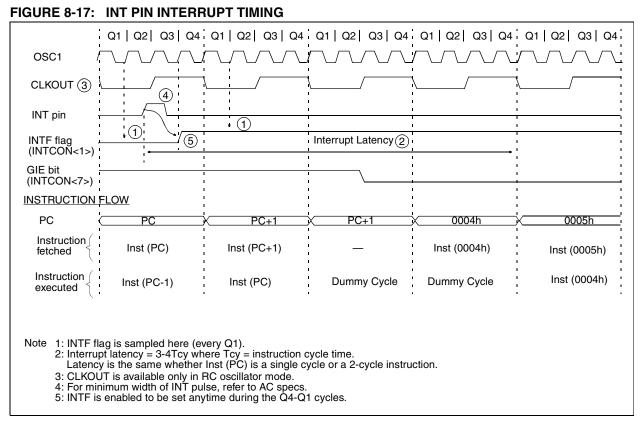

### 8.9.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if INTEDG bit (OPTION\_REG<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing control bit INTE (INTCON<4>). Flag bit INTF must be cleared in software via the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake the processor from SLEEP (Section 8.12) only if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether the processor branches to the interrupt vector following wake-up.

### 8.9.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in TMR0 will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 6.0).

### 8.9.3 PORT RB INTERRUPT

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<3>) (Section 5.2).

**Note 1:** For a change on the I/O pin to be recognized, the pulse width must be at least TCY wide.

| Mnemonic,                              |      | Description                  | Cycles   |       | 14-Bit | Opcode | Э    | Status   | Notes |

|----------------------------------------|------|------------------------------|----------|-------|--------|--------|------|----------|-------|

| Operan                                 | ds   |                              |          | MSb   |        |        | LSb  | Affected |       |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |      |                              |          |       |        |        |      |          |       |

| ADDWF                                  | f, d | Add W and f                  | 1        | 00    | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF                                  | f, d | AND W with f                 | 1        | 00    | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF                                   | f    | Clear f                      | 1        | 00    | 0001   | lfff   | ffff | Z        | 2     |

| CLRW                                   | -    | Clear W                      | 1        | 00    | 0001   | 0xxx   | xxxx | Z        |       |

| COMF                                   | f, d | Complement f                 | 1        | 00    | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF                                   | f, d | Decrement f                  | 1        | 00    | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ                                 | f, d | Decrement f, Skip if 0       | 1(2)     | 00    | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF                                   | f, d | Increment f                  | 1        | 00    | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ                                 | f, d | Increment f, Skip if 0       | 1(2)     | 00    | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF                                  | f, d | Inclusive OR W with f        | 1        | 00    | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF                                   | f, d | Move f                       | 1        | 00    | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF                                  | f    | Move W to f                  | 1        | 00    | 0000   | lfff   | ffff |          |       |

| NOP                                    | -    | No Operation                 | 1        | 00    | 0000   | 0xx0   | 0000 |          |       |

| RLF                                    | f, d | Rotate Left f through Carry  | 1        | 00    | 1101   | dfff   | ffff | С        | 1,2   |

| RRF                                    | f, d | Rotate Right f through Carry | 1        | 00    | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF                                  | f, d | Subtract W from f            | 1        | 00    | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF                                  | f, d | Swap nibbles in f            | 1        | 00    | 1110   | dfff   | ffff |          | 1,2   |

| XORWF                                  | f, d | Exclusive OR W with f        | 1        | 00    | 0110   | dfff   | ffff | Z        | 1,2   |

|                                        |      | BIT-ORIENTED FILE REGIS      | TER OPER | RATIO | NS     |        |      |          |       |

| BCF                                    | f, b | Bit Clear f                  | 1        | 01    | 00bb   | bfff   | ffff |          | 1,2   |

| BSF                                    | f, b | Bit Set f                    | 1        | 01    | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC                                  | f, b | Bit Test f, Skip if Clear    | 1 (2)    | 01    | 10bb   | bfff   | ffff |          | 3     |

| BTFSS                                  | f, b | Bit Test f, Skip if Set      | 1 (2)    | 01    | 11bb   | bfff   | ffff |          | 3     |

|                                        |      | LITERAL AND CONTRO           | L OPERAT | IONS  |        |        |      |          |       |

| ADDLW                                  | k    | Add literal and W            | 1        | 11    | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW                                  | k    | AND literal with W           | 1        | 11    | 1001   | kkkk   | kkkk | Z        |       |

| CALL                                   | k    | Call subroutine              | 2        | 10    | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT                                 | -    | Clear Watchdog Timer         | 1        | 00    | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO                                   | k    | Go to address                | 2        | 10    | 1kkk   | kkkk   | kkkk |          |       |

| IORLW                                  | k    | Inclusive OR literal with W  | 1        | 11    | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW                                  | k    | Move literal to W            | 1        | 11    | 00xx   | kkkk   | kkkk |          |       |

| RETFIE                                 | -    | Return from interrupt        | 2        | 00    | 0000   | 0000   | 1001 |          |       |

| RETLW                                  | k    | Return with literal in W     | 2        | 11    | 01xx   | kkkk   | kkkk |          |       |

| RETURN                                 | -    | Return from Subroutine       | 2        | 00    | 0000   | 0000   | 1000 |          |       |

| SLEEP                                  | -    | Go into standby mode         | 1        | 00    | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW                                  | k    | Subtract W from literal      | 1        | 11    | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW                                  | k    | Exclusive OR literal with W  | 1        | 11    | 1010   | レレレレ   | kkkk | Z        |       |

### TABLE 9-2 PIC16FXX INSTRUCTION SET

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| BTFSS             | Bit Test f, Skip if Set                                                                                                                                    |                  | CALL               | Call Sub         | proutine          |                                                    |                                                     |                                                                      |                                  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|------------------|-------------------|----------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------|----------------------------------|--|

| Syntax:           | [ <i>label</i> ] BTFSS f,b                                                                                                                                 |                  |                    |                  | Syntax:           | [ <i>label</i> ] CALL k                            |                                                     |                                                                      |                                  |  |

| Operands:         | $0 \le f \le 127$                                                                                                                                          |                  |                    | Operands:        | $0 \le k \le 2$   | $0 \le k \le 2047$                                 |                                                     |                                                                      |                                  |  |

|                   | 0 ≤ b < 7                                                                                                                                                  |                  |                    |                  | Operation:        | (PC)+ 1-                                           | → TOS,                                              |                                                                      |                                  |  |

| Operation:        | skip if (f <b>)</b>                                                                                                                                        | -) = 1           |                    |                  |                   | $k \rightarrow PC <$                               | ,                                                   | 50 /0                                                                |                                  |  |

| Status Affected:  | None                                                                                                                                                       |                  |                    |                  | <b>.</b>          | ,                                                  | 1<4:3>) -                                           | → PC<12                                                              | :11>                             |  |

| Encoding:         | 01 1                                                                                                                                                       | 11bb             | bfff               | ffff             | Status Affected:  | None                                               |                                                     |                                                                      | 1 1                              |  |

| Description:      | If bit 'b' in regi                                                                                                                                         |                  |                    | ne next          | Encoding:         | 10                                                 | 0kkk                                                | kkkk                                                                 | kkkk                             |  |

| Words:            | instruction is executed.<br>If bit 'b' is '1', then the next instruction is<br>discarded and a NOP is executed<br>instead, making this a 2TCY instruction. |                  |                    |                  | Description:      | (PC+1) is<br>eleven bit<br>into PC bi<br>the PC ar | pushed or<br>immediate<br>ts <10:0>.<br>e loaded fr | st, return a<br>nto the stace<br>address i<br>The upper<br>com PCLAT | ck. The<br>s loaded<br>r bits of |  |

| Cycles:           | 1(2)                                                                                                                                                       |                  |                    |                  |                   |                                                    | ycle instru                                         | ction.                                                               |                                  |  |

| Q Cycle Activity: | Q1                                                                                                                                                         | Q2               | Q3                 | Q4               | Words:            | 1                                                  |                                                     |                                                                      |                                  |  |

|                   |                                                                                                                                                            | Read             | Process            | No-Operat        | Cycles:           | 2                                                  | 0.0                                                 |                                                                      | <u>.</u>                         |  |

|                   | re                                                                                                                                                         | egister 'f'      | data               | ion              | Q Cycle Activity: | Q1                                                 | Q2                                                  | Q3                                                                   | Q4                               |  |

| If Skip:          | (2nd Cycle)                                                                                                                                                | )                |                    |                  | 1st Cycle         | Decode                                             | Read<br>literal 'k',                                | Process<br>data                                                      | Write to<br>PC                   |  |

|                   | Q1                                                                                                                                                         | Q2               | Q3                 | Q4               |                   |                                                    | Push PC<br>to Stack                                 |                                                                      |                                  |  |

|                   | No-Operat<br>ion                                                                                                                                           | o-Operati<br>on  | No-Opera<br>tion   | No-Operat<br>ion | 2nd Cycle         | No-Opera<br>tion                                   | No-Opera<br>tion                                    | No-Opera<br>tion                                                     | No-Operat<br>ion                 |  |

| Example           |                                                                                                                                                            |                  | FLAG,1<br>PROCESS  | CODE             | Example           | HERE                                               | CALL                                                | THERE                                                                |                                  |  |

|                   | TRUE •                                                                                                                                                     | •                | -                  | _                |                   | Before Ir                                          | nstruction                                          |                                                                      |                                  |  |

|                   | •                                                                                                                                                          | •                |                    |                  |                   | After Ins                                          | -                                                   | ddress HE                                                            | RE                               |  |

|                   | Before Instru                                                                                                                                              | ruction          |                    |                  |                   |                                                    |                                                     | ddress TH                                                            | IERE                             |  |

|                   | PC = address HERE<br>After Instruction                                                                                                                     |                  |                    |                  |                   | TOS = A                                            | ddress HE                                           | IRE+1                                                                |                                  |  |

|                   |                                                                                                                                                            |                  |                    |                  |                   |                                                    |                                                     |                                                                      |                                  |  |

|                   | if Fl<br>PC                                                                                                                                                | FLAG<1><br>C = a | = 0,<br>address F# | ALSE             |                   |                                                    |                                                     |                                                                      |                                  |  |

|                   | if Fl                                                                                                                                                      | -LAG<1>          |                    |                  |                   |                                                    |                                                     |                                                                      |                                  |  |

|                   | PC                                                                                                                                                         | C = 6            | address TI         | RUE              |                   |                                                    |                                                     |                                                                      |                                  |  |

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC MCU. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

## 10.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC MCU series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

## 10.12 <u>C Compiler (MPLAB-C17)</u>

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC17CXXX family of microcontrollers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display.

### 10.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, Edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

### 10.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

## 10.15 <u>SEEVAL<sup>®</sup> Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in trade-off analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

### 10.16 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

# TABLE 10-1CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS<br/>AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| OSC | PIC16F84-04<br>PIC16F83-04                                                                                  | PIC16F84-10<br>PIC16F83-10                                                                              | PIC16LF84-04<br>PIC16LF83-04                                                                                 |  |

|-----|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| RC  | VDD: 4.0V to 6.0V   IDD: 4.5 mA max. at 5.5V   IPD: 14 μA max. at 4V WDT dis   Freq: 4.0 MHz max.           | VDD: 4.5V to 5.5V   IDD: 1.8 mA typ. at 5.5V   IPD: 1.0 μA typ. at 5.5V WDT dis   Freq: 40 MHz max.     | VDD: 2.0V to 6.0V   IDD: 4.5 mA max. at 5.5V   IPD: 7.0 μA max. at 2V WDT dis   Freq: 2.0 MHz max.           |  |

| XT  | VDD: 4.0V to 6.0V<br>IDD: 4.5 mA max. at 5.5V<br>IPD: 14 μA max. at 4V WDT dis<br>Freq: 4.0 MHz max.        | VDD: 4.5V to 5.5V   IDD: 1.8 mA typ. at 5.5V   IPD: 1.0 μA typ. at 5.5V WDT dis   Freq: 4.0 MHz max.    | VDD: 2.0V to 6.0V<br>IDD: 4.5 mA max. at 555V<br>IPD: 7.0 μA max. at 2V WDT dis<br>Freq: 2.0 MHz max.        |  |

| HS  | VDD: 4.5V to 5.5V   IDD: 4.5 mA typ. at 5.5V   IPD: 1.0 μA typ. at 4.5V WDT dis   Freq: 4.0 MHz max.        | VDD: 4.5V to 5.5V   IDD: 10 mA max. at 5.5V typ.   IPD: 1.0 μA typ. at 4.5V WDT dis   Freq: 10 MHz max. | Do not use in HS mode                                                                                        |  |

| LP  | VDD: 4.0V to 6.0V   IDD: 48 μA typ. at 32 kHz, 2.0V   IPD: 0.6 μA typ. at 3.0V WDT dis   Freq: 200 kHz max. | Do not use in LP mode                                                                                   | VDD: 2.0V to 6.0V<br>IDD: 45 μA max. at 32 kHz, 2.0V<br>IRD: 7 μA max, at 2.0V WDT dis<br>Freq: 200 kHz max. |  |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

### 10.4 DC CHARACTERISTICS: PIC16F84, PIC16F83 (Commercial, Industrial) PIC16LF84, PIC16F83 (Commercial, Industrial)

| DC Characteristics<br>All Pins Except<br>Power Supply Pins |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$   |               |                     |             |       |                                                                         |

|------------------------------------------------------------|-------|--------------------------------------------------------|---------------|---------------------|-------------|-------|-------------------------------------------------------------------------|

| Parameter<br>No.                                           | Sym   | Characteristic                                         | Min           | Тур†                | Мах         | Units | Conditions                                                              |

| D100                                                       | Cosc2 | Capacitive Loading Specs<br>on Output Pins<br>OSC2 pin | _             | _                   | 15          | pF    | In XT, HS and LP modes<br>when external clock is used to<br>drive OSC1. |

| D101                                                       | Сю    | All I/O pins and OSC2<br>(RC mode)                     | —             | _                   | 50          | рF    |                                                                         |

|                                                            |       | Data EEPROM Memory                                     |               |                     |             |       | $\langle \vee \rangle \rangle$                                          |

| D120                                                       | ED    | Endurance                                              | 1M            | 10M                 | —           | EAV   | 25°C at 5V                                                              |

| D121                                                       | Vdrw  | VDD for read/write                                     | VMIN          | —                   | 6.0         | V     | VMIN = Minimum operating                                                |

| D122                                                       | TDEW  | Erase/Write cycle time                                 |               | 10                  | <b>2</b> 0* | miş∖  |                                                                         |

|                                                            |       | Program Flash Memory                                   |               | ~                   |             |       |                                                                         |

| D130                                                       | Eр    | Endurance                                              | 100           | 1000                |             | ÈXW   | /                                                                       |

| D131                                                       | Vpr   | VDD for read                                           | VMIN          | $\langle  \rangle$  | 6.0         | V     | VMIN = Minimum operating voltage                                        |

| D132                                                       | VPEW  | VDD for erase/write                                    | 4.5           | $\langle - \rangle$ | 5.5         | V     |                                                                         |

| D133                                                       | TPEW  | Erase/Write cycle time                                 | $  - \rangle$ | 10                  | $\searrow$  | ms    |                                                                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

DS30430D-page 11-80

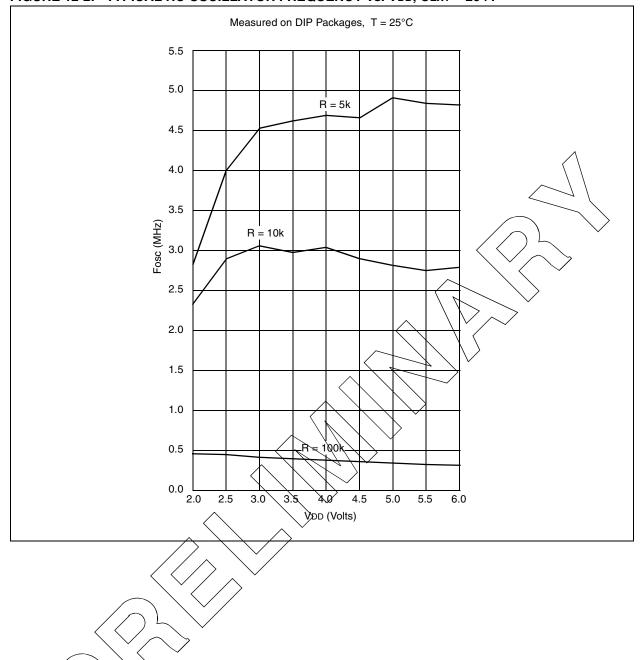

# FIGURE 12-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 20 PF

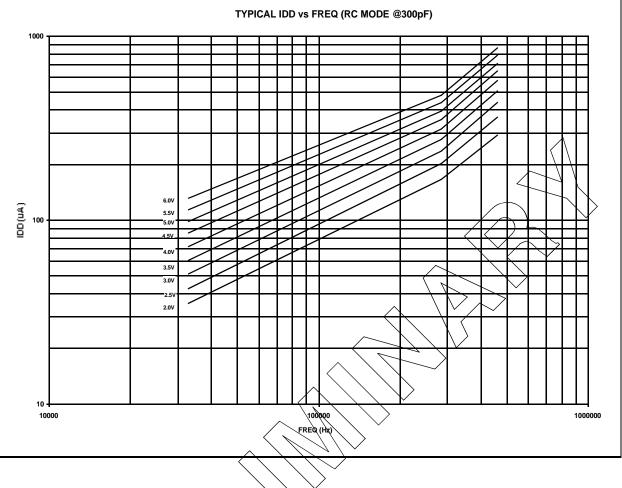

# FIGURE 12-12: TYPICAL IDD vs. FREQUENCY (RC MODE @300PF, 25°C)

# APPENDIX C: WHAT'S NEW IN THIS DATA SHEET

Here's what's new in this data sheet:

- 1. DC & AC Characteristics Graphs/Tables section for PIC16F8X devices has been added.

- 2. An appendix on conversion considerations has been added. This explains differences for customers wanting to go from PIC16C84 to PIC16F84 or similar device.

# APPENDIX D: WHAT'S CHANGED IN THIS DATA SHEET

Here's what's changed in this data sheet:

- 1. Errata information has been included.

- Option register name has been changed from OPTION to OPTION\_REG. This is consistant with other data sheets and header files, and resolves the conflict between the OPTION command and OPTION register.

- 3. Errors have been fixed.

- 4. The appendix containing PIC16/17 microcontrollers has been removed.

### **Revision D (January 2013)**

Added a note to each package drawing.

## Ρ

| Paging, Program Memory                           |

|--------------------------------------------------|

| PCL                                              |

| PCLATH                                           |

| PD                                               |

| PICDEM-1 Low-Cost PIC MCU Demo Board70           |

| PICDEM-2 Low-Cost PIC16CXX Demo Board70          |

| PICDEM-3 Low-Cost PIC16CXXX Demo Board70         |

| PICMASTER® In-Circuit Emulator69                 |

| PICSTART® Plus Entry Level Development System 69 |

| Pinout Descriptions9                             |

| POR                                              |

| Oscillator Start-up Timer (OST)                  |

| Power-on Reset (POR)                             |

| Power-up Timer (PWRT)                            |

| Time-out Sequence46                              |

| Time-out Sequence on Power-up44                  |

| TO                                               |

| Port RB Interrupt                                |

| PORTA                                            |

| PORTB                                            |

| Power-down Mode (SLEEP)51                        |

| Prescaler                                        |

| PRO MATE® II Universal Programmer                |

| Product Identification System                    |

|                                                  |

# R

| RBIF bit           |  |

|--------------------|--|

| RC Oscillator      |  |

| Read-Modify-Write  |  |

| Register File      |  |

| Reset              |  |

| Reset on Brown-Out |  |

# S

| Saving W Register and STATUS in RAM       |           |

|-------------------------------------------|-----------|

| SEEVAL® Evaluation and Programming System |           |

| SLEEP                                     |           |

| Software Simulator (MPLAB-SIM)            |           |

| Special Features of the CPU               |           |

| Special Function Registers                |           |

| Stack                                     | -         |

| Overflows                                 |           |

| Underflows                                |           |

| STATUS                                    | 7, 15, 42 |

| т                                         |           |

| time-out                                  | 42        |

| Timer0                                    |           |

| Switching Prescaler Assignment            | 31        |

| T0IF                                      |           |

| Timer0 Module                             | 27        |

| TMR0 Interrupt                            |           |

| TMR0 with External Clock                  | 29        |

| Timing Diagrams                           |           |

| Time-out Sequence                         |           |

| Timing Diagrams and Specifications        |           |

| TRISA                                     |           |

| TRISB                                     |           |

| W                                         |           |

| W                                         |           |

| Wake-up from SLEEP                        |           |

| Watchdog Timer (WDT)37                    |           |

| WDT                                       |           |

| Period                                    |           |

| Programming Considerations<br>Time-out |    |

|----------------------------------------|----|

| x                                      |    |

| ХТ                                     | 46 |

| Z                                      |    |

| Zero bit                               | 7  |