### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 10MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 13                                                                      |

| Program Memory Size        | 1.75KB (1K x 14)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64 x 8                                                                  |

| RAM Size                   | 68 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 18-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f84-10-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | .0 General Description                                                              |     |

|-------|-------------------------------------------------------------------------------------|-----|

| 2.0   | 2.0 PIC16F8X Device Varieties                                                       | 5   |

| 3.0   | 3.0 Architectural Overview                                                          | 7   |

| 4.0   | I.0 Memory Organization                                                             |     |

| 5.0   | 5.0 I/O Ports                                                                       |     |

| 6.0   |                                                                                     |     |

| 7.0   |                                                                                     |     |

| 8.0   |                                                                                     |     |

| 9.0   | · · · · · · · · · · · · · · · · · · ·                                               |     |

| 10.0  |                                                                                     |     |

| 11.0  |                                                                                     | -   |

|       |                                                                                     |     |

| 13.0  |                                                                                     |     |

|       | 4.0 Packaging Information                                                           |     |

| Appe  | Appendix A: Feature Improvements - From PIC16C5X To PIC16F8X                        |     |

| Appe  | Appendix B: Code Compatibility - from PIC16C5X to PIC16F8X                          |     |

| Appe  | Appendix C: What's New In This Data Sheet                                           |     |

| Appe  | Appendix D: What's Changed In This Data Sheet                                       |     |

| Appe  | Appendix E: Conversion Considerations - PIC16C84 to PIC16F83/F84 And PIC16CR83/CR84 | 115 |

| Index | ndex                                                                                | 117 |

| On-L  | Dn-Line Support                                                                     | 119 |

| Read  | Reader Response                                                                     | 120 |

|       | PIC16F8X Product Identification System                                              |     |

| Sales | Sales and Support                                                                   |     |

# To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

# 1.0 GENERAL DESCRIPTION

The PIC16F8X is a group in the PIC16CXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers. This group contains the following devices:

- PIC16F83

- PIC16F84

- PIC16CR83

- PIC16CR84

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. PIC16F8X devices have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with a separate 8-bit wide data bus. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set is used to achieve a very high performance level.

PIC16F8X microcontrollers typically achieve a 2:1 code compression and up to a 4:1 speed improvement (at 20 MHz) over other 8-bit microcontrollers in their class.

The PIC16F8X has up to 68 bytes of RAM, 64 bytes of Data EEPROM memory, and 13 I/O pins. A timer/counter is also available.

The PIC16CXX family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers power saving. The user can wake the chip from sleep through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

The devices with Flash program memory allow the same device package to be used for prototyping and production. In-circuit reprogrammability allows the code to be updated without the device being removed from the end application. This is useful in the development of many applications where the device may not be easily accessible, but the prototypes may require code updates. This is also useful for remote applications where the code may need to be updated (such as rate information). Table 1-1 lists the features of the PIC16F8X. A simplified block diagram of the PIC16F8X is shown in Figure 3-1.

The PIC16F8X fits perfectly in applications ranging from high speed automotive and appliance motor control to low-power remote sensors, electronic locks, security devices and smart cards. The Flash/EEPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, security codes, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high performance, ease-of-use and I/O flexibility make the PIC16F8X very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions; serial communication; capture, compare and PWM functions; and co-processor applications).

The serial in-system programming feature (via two pins) offers flexibility of customizing the product after complete assembly and testing. This feature can be used to serialize a product, store calibration data, or program the device with the current firmware before shipping.

# 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for PIC16C5X devices can be easily ported to PIC16F8X devices (Appendix B).

# 1.2 <u>Development Support</u>

The PIC16CXX family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler and fuzzy logic support tools are also available.

# 2.0 PIC16F8X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in this section. When placing orders, please use the "PIC16F8X Product Identification System" at the back of this data sheet to specify the correct part number.

There are four device "types" as indicated in the device number.

- 1. **F**, as in PIC16**F**84. These devices have Flash program memory and operate over the standard voltage range.

- LF, as in PIC16LF84. These devices have Flash program memory and operate over an extended voltage range.

- 3. **CR**, as in PIC16**CR**83. These devices have ROM program memory and operate over the standard voltage range.

- 4. **LCR**, as in PIC16**LCR**84. These devices have ROM program memory and operate over an extended voltage range.

When discussing memory maps and other architectural features, the use of **F** and **CR** also implies the **LF** and **LCR** versions.

## 2.1 Flash Devices

These devices are offered in the lower cost plastic package, even though the device can be erased and reprogrammed. This allows the same device to be used for prototype development and pilot programs as well as production.

A further advantage of the electrically-erasable Flash version is that it can be erased and reprogrammed incircuit, or by device programmers, such as Microchip's PICSTART<sup>®</sup> Plus or PRO MATE<sup>®</sup> II programmers.

### 2.2 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices have all Flash locations and configuration options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available.

For information on submitting a QTP code, please contact your Microchip Regional Sales Office.

# 2.3 <u>Serialized Quick-Turnaround-</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers the unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

For information on submitting a SQTP code, please contact your Microchip Regional Sales Office.

# 2.4 ROM Devices

Some of Microchip's devices have a corresponding device where the program memory is a ROM. These devices give a cost savings over Microchip's traditional user programmed devices (EPROM, EEPROM).

ROM devices (PIC16CR8X) do not allow serialization information in the program memory space. The user may program this information into the Data EEPROM.

For information on submitting a ROM code, please contact your Microchip Regional Sales Office.

### 4.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external INT interrupt, TMR0, and the weak pull-ups on PORTB.

# FIGURE 4-1: OPTION\_REG REGISTER (ADDRESS 81h)

**Note:** When the prescaler is assigned to the WDT (PSA = '1'), TMR0 has a 1:1 prescaler assignment.

| R/W-1            | R/W-1       | R/W-1            | R/W-1    | R/W-1      | R/W-1        | R/W-1        | R/W-1 |                                       |

|------------------|-------------|------------------|----------|------------|--------------|--------------|-------|---------------------------------------|

| RBPU             | INTEDG      | TOCS             | T0SE     | PSA        | PS2          | PS1          | PS0   | R = Readable bit                      |

| bit7             |             |                  |          |            |              |              | bit0  | W = Writable bit                      |

|                  |             |                  |          |            |              |              |       | U = Unimplemented bit,<br>read as '0' |

|                  |             |                  |          |            |              |              |       | - n = Value at POR reset              |

| bit 7:           | RBPU: PC    |                  | ın Enabl | a hit      |              |              |       |                                       |

| Dit 7.           | 1 = PORTI   |                  |          |            |              |              |       |                                       |

|                  |             |                  |          |            | dividual por | t latch valı | ues)  |                                       |

| bit 6:           | INTEDG:     |                  |          |            | ·            |              | ,     |                                       |

| bit 0.           | 1 = Interru | •                | •        |            | nin          |              |       |                                       |

|                  | 0 = Interru |                  |          |            |              |              |       |                                       |

| bit 5:           | TOCS: TM    |                  |          |            | F.           |              |       |                                       |

| Dit J.           | 1 = Transit |                  |          |            |              |              |       |                                       |

|                  | 0 = Interna |                  |          | •          | OUT)         |              |       |                                       |

| bit 4:           | TOSE: TM    |                  | •        |            |              |              |       |                                       |

| DIL 4.           |             |                  |          |            | on RA4/T00   |              |       |                                       |

|                  |             |                  |          |            | on RA4/T00   |              |       |                                       |

| bit 3:           | PSA: Pres   |                  | •        |            |              | <b>P</b>     |       |                                       |

| DIL 3.           | 1 = Presca  |                  |          |            |              |              |       |                                       |

|                  | 0 = Presca  |                  |          |            |              |              |       |                                       |

| hit 2 0.         | PS2:PS0:    | •                |          |            |              |              |       |                                       |

| bit <u>∠</u> -0. |             |                  |          |            |              |              |       |                                       |

|                  | Bit Value   | TMR0 Ra          | te WD    | Γ Rate     |              |              |       |                                       |

|                  | 000         | 1:2              | 1 :      |            |              |              |       |                                       |

|                  | 001         | 1:4              | 1:       |            |              |              |       |                                       |

|                  | 010<br>011  | 1:8              |          | : 4<br>: 8 |              |              |       |                                       |

|                  | 100         | 1 : 16<br>1 : 32 |          | 16         |              |              |       |                                       |

|                  | 101         | 1:64             |          | 32         |              |              |       |                                       |

|                  | 110         | 1 : 128          |          | 64         |              |              |       |                                       |

|                  | 111         | 1 : 256          | 1:       | 128        |              |              |       |                                       |

|                  |             |                  |          |            |              |              |       |                                       |

|                  |             |                  |          |            |              |              |       |                                       |

# 7.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead it is indirectly addressed through the Special Function Registers. There are four SFRs used to read and write this memory. These registers are:

- EECON1

- EECON2

- EEDATA

- EEADR

EEDATA holds the 8-bit data for read/write, and EEADR holds the address of the EEPROM location being accessed. PIC16F8X devices have 64 bytes of data EEPROM with an address range from 0h to 3Fh.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The writetime will vary with voltage and temperature as well as from chip to chip. Please refer to AC specifications for exact limits.

When the device is code protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access this memory.

# 7.1 <u>EEADR</u>

The EEADR register can address up to a maximum of 256 bytes of data EEPROM. Only the first 64 bytes of data EEPROM are implemented.

The upper two bits are address decoded. This means that these two bits must always be '0' to ensure that the address is in the 64 byte memory space.

| U       | U                                      | U                                                                                                                                                                                                                                                                                                            | R/W-0                    | R/W-x       | R/W-0                                      | R/S-0       | R/S-x        |                                                                                                           |  |  |  |  |  |

|---------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|--------------------------------------------|-------------|--------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| _       | _                                      |                                                                                                                                                                                                                                                                                                              | EEIF                     | WRERR       | WREN                                       | WR          | RD           | R = Readable bit                                                                                          |  |  |  |  |  |

| bit7    |                                        |                                                                                                                                                                                                                                                                                                              |                          |             |                                            |             | bitO         | W = Writable bit<br>S = Settable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |  |  |  |

| bit 7:5 | Unimplem                               | nented: F                                                                                                                                                                                                                                                                                                    | Read as '(               | )'          |                                            |             |              |                                                                                                           |  |  |  |  |  |

| bit 4   | 1 = The w                              | rite opera                                                                                                                                                                                                                                                                                                   | ation com                | oleted (mus | upt Flag bit<br>st be cleare<br>or has not | ed in softw |              |                                                                                                           |  |  |  |  |  |

| bit 3   | $1 = A write(any \overline{M}$         | <ul> <li>0 = The write operation is not complete or has not been started</li> <li>WRERR: EEPROM Error Flag bit</li> <li>1 = A write operation is prematurely terminated <ul> <li>(any MCLR reset or any WDT reset during normal operation)</li> <li>0 = The write operation completed</li> </ul> </li> </ul> |                          |             |                                            |             |              |                                                                                                           |  |  |  |  |  |

| bit 2   | WREN: EB<br>1 = Allows<br>0 = Inhibits | write cyc                                                                                                                                                                                                                                                                                                    | cles                     |             |                                            |             |              |                                                                                                           |  |  |  |  |  |

| bit 1   |                                        | s a write<br>(not clea                                                                                                                                                                                                                                                                                       | cycle. (Ti<br>red) in so | ftware.     | -                                          | ardware or  | nce write is | complete. The WR bit can only                                                                             |  |  |  |  |  |

| bit 0   |                                        | es an EEI<br>(not clea                                                                                                                                                                                                                                                                                       | PROM rea<br>red) in so   | ftware).    | kes one cy                                 | cle. RD is  | cleared in   | hardware. The RD bit can only                                                                             |  |  |  |  |  |

# FIGURE 7-1: EECON1 REGISTER (ADDRESS 88h)

NOTES:

# 8.1 <u>Configuration Bits</u>

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

Address 2007h is beyond the user program memory space and it belongs to the special test/configuration memory space (2000h - 3FFFh). This space can only be accessed during programming.

To find out how to program the PIC16C84, refer to *PIC16C84 EEPROM Memory Programming Specifica-tion* (DS30189).

# FIGURE 8-1: CONFIGURATION WORD - PIC16CR83 AND PIC16CR84

| <b>D</b>  | <b>D</b>             | Π                                                                                                                                                                                 | <b>D</b>                     | <b>D</b>  | <b>D</b>  | D/D         | <b>D</b>  | D         | <b>D</b>  | <b>D</b>     | <b>D</b>    | D                                 | D                                                      |   |

|-----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------|-----------|-------------|-----------|-----------|-----------|--------------|-------------|-----------------------------------|--------------------------------------------------------|---|

| R-u<br>CP | R-u<br>CP            | R-u<br>CP                                                                                                                                                                         | R-u<br>CP                    | R-u<br>CP | R-u<br>CP | R/P-u<br>DP | R-u<br>CP | R-u<br>CP | R-u<br>CP | R-u<br>PWRTE | R-u<br>WDTE | R-u<br>FOSC1                      | R-u<br>FOSC0                                           |   |

| bit13     |                      | 01                                                                                                                                                                                | 01                           |           |           |             | 01        |           | 01        |              |             | R = Rea<br>P = Prog<br>- n = Valu | bit0<br>adable bit<br>grammable bit<br>ie at POR reset | t |

| bit 13:8  | 1 = 0                | Code pro                                                                                                                                                                          | tection                      | off       |           |             | it        |           |           |              |             | u = unch                          | langeu                                                 |   |

| bit 7     | 1 = 0                | <ul> <li>0 = Program memory is code protected</li> <li>DP: Data Memory Code Protection bit</li> <li>1 = Code protection off</li> <li>0 = Data memory is code protected</li> </ul> |                              |           |           |             |           |           |           |              |             |                                   |                                                        |   |

| bit 6:4   | 1 = 0                | Program<br>Code pro<br>Program                                                                                                                                                    | tection                      | off       |           |             | it        |           |           |              |             |                                   |                                                        |   |

| bit 3     | 1 = F                | RTE: Pov<br>Power-up<br>Power-up                                                                                                                                                  | timer                        | is disal  | oled      | bit         |           |           |           |              |             |                                   |                                                        |   |

| bit 2     | 1 = V                | E: Wato<br>VDT ena<br>VDT disa                                                                                                                                                    | abled                        | imer E    | nable I   | oit         |           |           |           |              |             |                                   |                                                        |   |

| bit 1:0   | 11 =<br>10 =<br>01 = | C1:FOS<br>RC osc<br>HS osc<br>XT osci<br>LP osci                                                                                                                                  | illator<br>illator<br>llator | cillator  | Selec     | tion bits   |           |           |           |              |             |                                   |                                                        |   |

FIGURE 8-2: CONFIGURATION WORD - PIC16F83 AND PIC16F84

|          |       |         |          |           |         |         | R/P-u |    | R/P-u | R/P-u | R/P-u | R/P-u   | R/P-u      |   |

|----------|-------|---------|----------|-----------|---------|---------|-------|----|-------|-------|-------|---------|------------|---|

| CP       | CP    | CP      | CP       | CP        | CP      | CP      | CP    | CP | CP    | PWRTE | WDTE  | FOSC1   | FOSC0      |   |

| bit13    |       |         |          |           |         |         |       |    |       |       |       |         | bit0       |   |

|          |       |         |          |           |         |         |       |    |       |       |       | R = Rea | adable bit |   |

|          |       |         |          |           |         |         |       |    |       |       |       |         | grammabl   |   |

|          |       |         |          |           |         |         |       |    |       |       |       |         | ue at POR  |   |

|          |       | ~       | <b>.</b> |           |         |         |       |    |       |       |       | u =     | unchange   | a |

| bit 13:4 |       |         |          |           |         |         |       |    |       |       |       |         |            |   |

|          |       | Code p  |          |           |         | ما      |       |    |       |       |       |         |            |   |

|          |       | All men | -        | -         |         |         |       |    |       |       |       |         |            |   |

| bit 3    |       | RTE: PO |          |           |         | e bit   |       |    |       |       |       |         |            |   |

|          |       | Power-  | -        |           |         |         |       |    |       |       |       |         |            |   |

|          | 0 = I | Power-  | up time  | er is ena | abled   |         |       |    |       |       |       |         |            |   |

| bit 2    | WD.   | TE: Wa  | tchdog   | Timer     | Enable  | e bit   |       |    |       |       |       |         |            |   |

|          | 1 = \ | WDT e   | nabled   |           |         |         |       |    |       |       |       |         |            |   |

|          | 0 = 1 | WDT di  | isabled  |           |         |         |       |    |       |       |       |         |            |   |

| bit 1:0  | FOS   | C1:FO   | SCO.     | Oscillat  | or Sele | ction b | its   |    |       |       |       |         |            |   |

| 511 110  |       | = RC 05 |          |           |         |         | 110   |    |       |       |       |         |            |   |

|          |       | = HS os |          |           |         |         |       |    |       |       |       |         |            |   |

|          |       | = XT os |          |           |         |         |       |    |       |       |       |         |            |   |

|          | 00 =  | = LP os | cillator |           |         |         |       |    |       |       |       |         |            |   |

|          |       |         |          |           |         |         |       |    |       |       |       |         |            |   |

### 8.2 Oscillator Configurations

### 8.2.1 OSCILLATOR TYPES

The PIC16F8X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

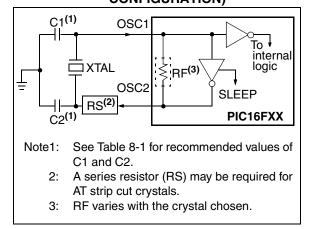

- 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 8-3).

### FIGURE 8-3: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

The PIC16F8X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/CLKIN pin (Figure 8-4).

# FIGURE 8-6: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

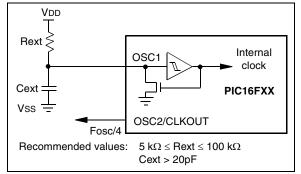

### 8.2.4 RC OSCILLATOR

For timing insensitive applications the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) values, capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types also affects the oscillation frequency, especially for low Cext values. The user needs to take into account variation due to tolerance of the external R and C components. Figure 8-7 shows how an R/C combination is connected to the PIC16F8X. For Rext values below  $4 k\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g.,  $1 \text{ M}\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping Rext between 5 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With little or no external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See the electrical specification section for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance has a greater affect on RC frequency).

See the electrical specification section for variation of oscillator frequency due to VDD for given Rext/Cext values as well as frequency variation due to operating temperature.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-2 for waveform).

### FIGURE 8-7: RC OSCILLATOR MODE

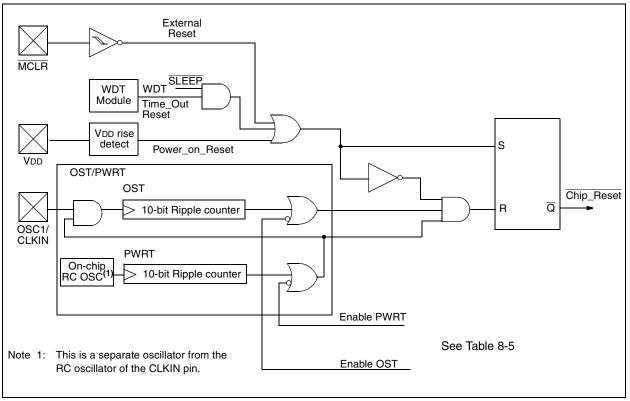

## 8.3 <u>Reset</u>

The PIC16F8X differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

Figure 8-8 shows a simplified block diagram of the on-chip reset circuit. The  $\overline{\text{MCLR}}$  reset path has a noise filter to ignore small pulses. The electrical specifications state the pulse width requirements for the  $\overline{\text{MCLR}}$  pin.

Some registers are not affected in any reset condition; their status is unknown on a POR reset and unchanged in any other reset. Most other registers are reset to a "reset state" on POR,  $\overline{\text{MCLR}}$  or WDT reset during normal operation and on  $\overline{\text{MCLR}}$  reset during SLEEP. They are not affected by a WDT reset during SLEEP, since this reset is viewed as the resumption of normal operation.

Table 8-3 gives a description of reset conditions for the program counter (PC) and the STATUS register. Table 8-4 gives a full description of reset states for all registers.

The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations (Section 8.7). These bits are used in software to determine the nature of the reset.

### FIGURE 8-8: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| Mnemo  |      | Description                  | Cycles   |       | 14-Bit | Opcode | Э    | Status   | Notes |

|--------|------|------------------------------|----------|-------|--------|--------|------|----------|-------|

| Operan | ds   |                              |          | MSb   |        |        | LSb  | Affected |       |

|        |      | BYTE-ORIENTED FILE REG       | STER OPE | RATIC | ONS    |        |      |          |       |

| ADDWF  | f, d | Add W and f                  | 1        | 00    | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF  | f, d | AND W with f                 | 1        | 00    | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF   | f    | Clear f                      | 1        | 00    | 0001   | lfff   | ffff | Z        | 2     |

| CLRW   | -    | Clear W                      | 1        | 00    | 0001   | 0xxx   | xxxx | Z        |       |

| COMF   | f, d | Complement f                 | 1        | 00    | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF   | f, d | Decrement f                  | 1        | 00    | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ | f, d | Decrement f, Skip if 0       | 1(2)     | 00    | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF   | f, d | Increment f                  | 1        | 00    | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ | f, d | Increment f, Skip if 0       | 1(2)     | 00    | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF  | f, d | Inclusive OR W with f        | 1        | 00    | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF   | f, d | Move f                       | 1        | 00    | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF  | f    | Move W to f                  | 1        | 00    | 0000   | lfff   | ffff |          |       |

| NOP    | -    | No Operation                 | 1        | 00    | 0000   | 0xx0   | 0000 |          |       |

| RLF    | f, d | Rotate Left f through Carry  | 1        | 00    | 1101   | dfff   | ffff | С        | 1,2   |

| RRF    | f, d | Rotate Right f through Carry | 1        | 00    | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF  | f, d | Subtract W from f            | 1        | 00    | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF  | f, d | Swap nibbles in f            | 1        | 00    | 1110   | dfff   | ffff |          | 1,2   |

| XORWF  | f, d | Exclusive OR W with f        | 1        | 00    | 0110   | dfff   | ffff | Z        | 1,2   |

|        |      | BIT-ORIENTED FILE REGIS      | TER OPER | RATIO | NS     |        |      |          |       |

| BCF    | f, b | Bit Clear f                  | 1        | 01    | 00bb   | bfff   | ffff |          | 1,2   |

| BSF    | f, b | Bit Set f                    | 1        | 01    | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC  | f, b | Bit Test f, Skip if Clear    | 1 (2)    | 01    | 10bb   | bfff   | ffff |          | 3     |

| BTFSS  | f, b | Bit Test f, Skip if Set      | 1 (2)    | 01    | 11bb   | bfff   | ffff |          | 3     |

|        |      | LITERAL AND CONTRO           | L OPERAT | IONS  |        |        |      |          |       |

| ADDLW  | k    | Add literal and W            | 1        | 11    | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW  | k    | AND literal with W           | 1        | 11    | 1001   | kkkk   | kkkk | Z        |       |

| CALL   | k    | Call subroutine              | 2        | 10    | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT | -    | Clear Watchdog Timer         | 1        | 00    | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO   | k    | Go to address                | 2        | 10    | 1kkk   | kkkk   | kkkk |          |       |

| IORLW  | k    | Inclusive OR literal with W  | 1        | 11    | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW  | k    | Move literal to W            | 1        | 11    | 00xx   | kkkk   | kkkk |          |       |

| RETFIE | -    | Return from interrupt        | 2        | 00    | 0000   | 0000   | 1001 |          |       |

| RETLW  | k    | Return with literal in W     | 2        | 11    | 01xx   | kkkk   | kkkk |          |       |

| RETURN | -    | Return from Subroutine       | 2        | 00    | 0000   | 0000   | 1000 |          |       |

| SLEEP  | -    | Go into standby mode         | 1        | 00    | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW  | k    | Subtract W from literal      | 1        | 11    | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW  | k    | Exclusive OR literal with W  | 1        | 11    | 1010   | レレレレ   | kkkk | Z        |       |

### TABLE 9-2 PIC16FXX INSTRUCTION SET

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# PIC16F8X

| GOTO              | Unconditional                                                                                            | Branch                                     |                           | INCF              | Increme                          | ent f                                                           |                            |                      |

|-------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------|-------------------|----------------------------------|-----------------------------------------------------------------|----------------------------|----------------------|

| Syntax:           | [label] GOTO                                                                                             | k                                          |                           | Syntax:           | [ label ]                        | INCF                                                            | f,d                        |                      |

| Operands:         | $0 \leq k \leq 2047$                                                                                     |                                            |                           | Operands:         | $0 \le f \le 1$<br>$d \in [0,1]$ |                                                                 |                            |                      |

| Operation:        | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> -                                                                | • PC<12:1                                  | 1>                        | Operation:        |                                  | ı<br>→ (destina                                                 | tion)                      |                      |

| Status Affected:  | None                                                                                                     |                                            |                           | Status Affected:  | Z                                |                                                                 |                            |                      |

| Encoding:         | 10 1kkk                                                                                                  | kkkk                                       | kkkk                      | Encoding:         | 0 0                              | 1010                                                            | dfff                       | ffff                 |

| Description:      | GOTO is an uncond<br>eleven bit immedia<br>into PC bits <10:0<br>PC are loaded fro<br>GOTO is a two cycl | te value is lo<br>. The upper<br>n PCLATH< | baded<br>bits of<br>4:3>. | Description:      | mented. I<br>the W reg           | ents of reg<br>If 'd' is 0 th<br>gister. If 'd'<br>ack in regis | e result is<br>is 1 the re | placed in            |

| Words:            | 1                                                                                                        |                                            |                           | Words:            | 1                                |                                                                 |                            |                      |

| Cycles:           | 2                                                                                                        |                                            |                           | Cycles:           | 1                                |                                                                 |                            |                      |

| Q Cycle Activity: | Q1 Q2                                                                                                    | Q3                                         | Q4                        | Q Cycle Activity: | Q1                               | Q2                                                              | Q3                         | Q4                   |

| 1st Cycle         | Decode Read<br>literal 'l                                                                                | Process<br>data                            | Write to<br>PC            |                   | Decode                           | Read<br>register<br>'f'                                         | Process<br>data            | Write to destination |

| 2nd Cycle         | No-Operat<br>ion                                                                                         | at No-Opera<br>tion                        | No-Operat<br>ion          | Example           | INCF                             | CNT,                                                            | 1                          | 11                   |

| Example           | GOTO THERE After Instruction                                                                             |                                            |                           |                   | Before I                         | nstructior<br>CNT<br>Z                                          | n<br>= 0xF<br>= 0          | F                    |

|                   | PC =                                                                                                     | Address                                    | THERE                     |                   |                                  | CNT<br>Z                                                        | = 0x00<br>= 1              | 0                    |

### 10.1 DC CHARACTERISTICS:

### PIC16F84, PIC16F83 (Commercial, Industrial)

| DC Charac<br>Power Sup |      | -                                                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                   |                |                |                                                                                                                                                                            |  |  |  |

|------------------------|------|------------------------------------------------------------------|------------------------------------------------------|-------------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter<br>No.       | Sym  | Characteristic                                                   | Min                                                  | Typ†              | Max            | Units          | Conditions                                                                                                                                                                 |  |  |  |

| D001<br>D001A          | Vdd  | Supply Voltage                                                   | 4.0<br>4.5                                           | _                 | 6.0<br>5.5     | V<br>V         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                    |  |  |  |

| D002                   | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5*                                                 | —                 | —              | V              | Device in SLEEP mode                                                                                                                                                       |  |  |  |

| D003                   | VPOR | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | —                                                    | Vss               | —              | V              | See section on Power-on Reset for details                                                                                                                                  |  |  |  |

| D004                   | Svdd | VDD rise rate to ensure<br>internal Power-on<br>Reset signal     | 0.05*                                                |                   | _              | V/ms           | See section on Power-on Reset for details                                                                                                                                  |  |  |  |

| D010<br>D010A          | IDD  | Supply Current <sup>(2)</sup>                                    | _                                                    | 1.8<br>7.3        | 4.5<br>10      | mA<br>mA       | RC and XT osc configuration <sup>(4)</sup><br>Fosc = 4.0 MHz, VDD = 5.5V<br>Fosc = 4.0 MHz, VDD = 5.5V<br>(During Flash programming)<br>HS osc configuration (PIC16F84-10) |  |  |  |

| D013                   |      |                                                                  |                                                      | 5                 | 10             | mA<            | Fosc = 10 MHz, VDD = 5.5V                                                                                                                                                  |  |  |  |

| D020<br>D021<br>D021A  | IPD  | Power-down Current <sup>(3)</sup>                                |                                                      | 7.0<br>1.0<br>1.0 | 28<br>14<br>16 | μΑ<br>μΑ<br>μΑ | VDD = 4.0V, WDT enabled, industrial<br>VDD = 4.0V, WDT disabled, commercial<br>VDD = 4.0V, WDT disabled, industrial                                                        |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1=external square wave, from rail to rail, all I/O pins tristated, pulled to VDD, TOCKI = VDD,

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula IP = Vp0/2Rext (mA) with Rext in kOhm.

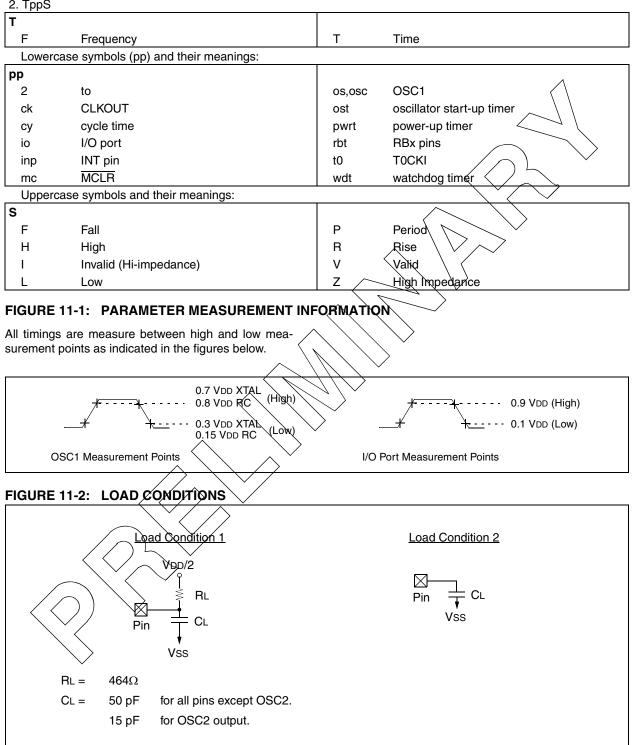

#### **TABLE 11-2** TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

- 1. TppS2ppS

- 2. TppS

###

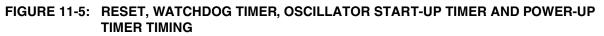

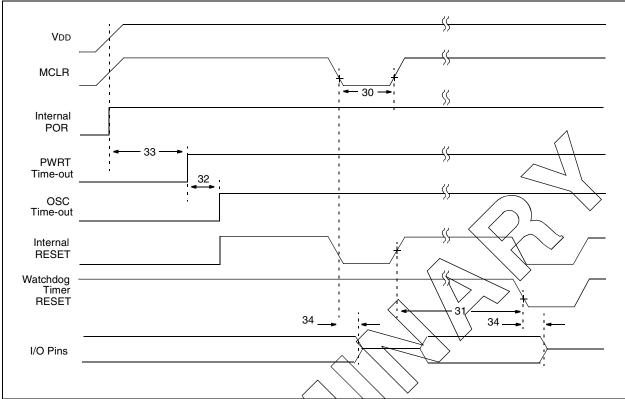

| Parameter<br>No. | Sym   | Characteristic                                   | Min   | Tunt     | Max   | Units | Conditions                       |

|------------------|-------|--------------------------------------------------|-------|----------|-------|-------|----------------------------------|

| NO.              | Sym   | Characteristic                                   |       | Тур†     | wax   | Units | Conditions                       |

| 30               | TmcL  | MCLR Pulse Width (low)                           | 1000* |          | —     | ns    | $2.0V \leq V\text{DD} \leq 6.0V$ |

| 31               | Twdt  | Watchdog Timer Time-out Period<br>(No Prescater) | 7*    | 18       | 33 *  | ms    | VDD = 5.0V                       |

| 32               | Tost  | Oscillation Start-up Timer Period                |       | 1024Tosc |       | ms    | Tosc = OSC1 period               |

| 33               | Tpwrt | Power-up Timer Period                            | 28 *  | 72       | 132 * | ms    | VDD = 5.0V                       |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low                   | —     | _        | 100 * | ns    |                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 50, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested

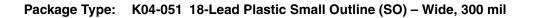

# **13.0 PACKAGING INFORMATION**

# 13.1 Package Marking Information

#

### Example

### 18L SOIC

## Example

| L | .egend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|---|---------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N | I       | be carrie                              | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                    |

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |                |       | INCHES* |       | М     | ILLIMETERS | 3     |

|-------------------------|----------------|-------|---------|-------|-------|------------|-------|

| Dimension Limits        |                | MIN   | NOM     | MAX   | MIN   | NOM        | MAX   |

| Pitch                   | р              |       | 0.050   |       |       | 1.27       |       |

| Number of Pins          | n              |       | 18      |       |       | 18         |       |

| Overall Pack. Height    | А              | 0.093 | 0.099   | 0.104 | 2.36  | 2.50       | 2.64  |

| Shoulder Height         | A1             | 0.048 | 0.058   | 0.068 | 1.22  | 1.47       | 1.73  |

| Standoff                | A2             | 0.004 | 0.008   | 0.011 | 0.10  | 0.19       | 0.28  |

| Molded Package Length   | D‡             | 0.450 | 0.456   | 0.462 | 11.43 | 11.58      | 11.73 |

| Molded Package Width    | E‡             | 0.292 | 0.296   | 0.299 | 7.42  | 7.51       | 7.59  |

| Outside Dimension       | E1             | 0.394 | 0.407   | 0.419 | 10.01 | 10.33      | 10.64 |

| Chamfer Distance        | Х              | 0.010 | 0.020   | 0.029 | 0.25  | 0.50       | 0.74  |

| Shoulder Radius         | R1             | 0.005 | 0.005   | 0.010 | 0.13  | 0.13       | 0.25  |

| Gull Wing Radius        | R2             | 0.005 | 0.005   | 0.010 | 0.13  | 0.13       | 0.25  |

| Foot Length             | L              | 0.011 | 0.016   | 0.021 | 0.28  | 0.41       | 0.53  |

| Foot Angle              | φ              | 0     | 4       | 8     | 0     | 4          | 8     |

| Radius Centerline       | L1             | 0.010 | 0.015   | 0.020 | 0.25  | 0.38       | 0.51  |

| Lead Thickness          | С              | 0.009 | 0.011   | 0.012 | 0.23  | 0.27       | 0.30  |

| Lower Lead Width        | B <sup>†</sup> | 0.014 | 0.017   | 0.019 | 0.36  | 0.42       | 0.48  |

| Mold Draft Angle Top    | α              | 0     | 12      | 15    | 0     | 12         | 15    |

| Mold Draft Angle Bottom | β              | 0     | 12      | 15    | 0     | 12         | 15    |

Controlling Parameter.

<sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

# PIC16F8X

NOTES:

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (602) 786-7578.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:        | Technical Publications Manager Total Pages Sent                                            |

|------------|--------------------------------------------------------------------------------------------|

| RE:        | Reader Response                                                                            |

| From       | n: Name                                                                                    |

|            | Company                                                                                    |

|            | Address                                                                                    |

|            | City / State / ZIP / Country                                                               |

| ٨٥٥        | Telephone: ()       FAX: ()         lication (optional):       FAX: ()                     |

| • •        |                                                                                            |

| vvou       | Ild you like a reply?YN                                                                    |

| Devi       | ice: PIC16F8X Literature Number: DS30430D                                                  |

| Questions: |                                                                                            |

| 1. \       | What are the best features of this document?                                               |

|            |                                                                                            |

| -          |                                                                                            |

| 2. 1       | How does this document meet your hardware and software development needs?                  |

| -          |                                                                                            |

| -          |                                                                                            |

| 3.         | Do you find the organization of this data sheet easy to follow? If not, why?               |

| -          |                                                                                            |

|            |                                                                                            |

| 4.         | What additions to the data sheet do you think would enhance the structure and subject?     |

| -          |                                                                                            |

| 5.         | What deletions from the data sheet could be made without affecting the overall usefulness? |

| 0.         |                                                                                            |

| -          |                                                                                            |

| 6. I       | Is there any incorrect or misleading information (what and where)?                         |

|            |                                                                                            |

| -          |                                                                                            |

| 7. I       | How would you improve this document?                                                       |

| -          |                                                                                            |

| -          |                                                                                            |

| 8. I       | How would you improve our software, systems, and silicon products?                         |

|            |                                                                                            |

# PIC16F8X

NOTES: