Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 68 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 18-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f84-10-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16F8X is a group in the PIC16CXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers. This group contains the following devices:

- PIC16F83

- PIC16F84

- PIC16CR83

- PIC16CR84

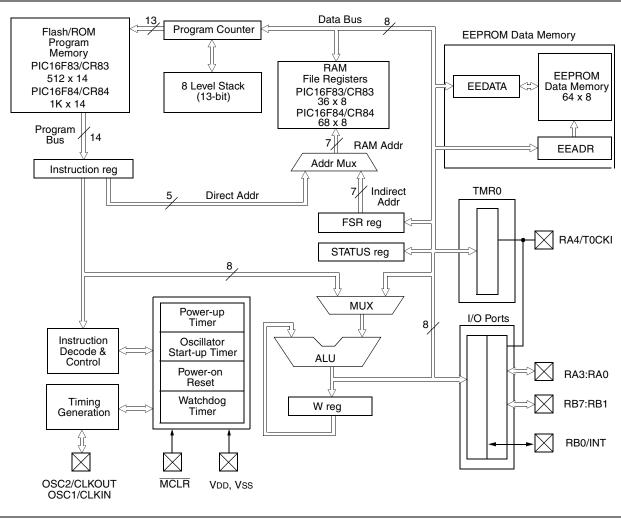

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. PIC16F8X devices have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with a separate 8-bit wide data bus. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set is used to achieve a very high performance level.

PIC16F8X microcontrollers typically achieve a 2:1 code compression and up to a 4:1 speed improvement (at 20 MHz) over other 8-bit microcontrollers in their class.

The PIC16F8X has up to 68 bytes of RAM, 64 bytes of Data EEPROM memory, and 13 I/O pins. A timer/counter is also available.

The PIC16CXX family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers power saving. The user can wake the chip from sleep through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

The devices with Flash program memory allow the same device package to be used for prototyping and production. In-circuit reprogrammability allows the code to be updated without the device being removed from the end application. This is useful in the development of many applications where the device may not be easily accessible, but the prototypes may require code updates. This is also useful for remote applications where the code may need to be updated (such as rate information). Table 1-1 lists the features of the PIC16F8X. A simplified block diagram of the PIC16F8X is shown in Figure 3-1.

The PIC16F8X fits perfectly in applications ranging from high speed automotive and appliance motor control to low-power remote sensors, electronic locks, security devices and smart cards. The Flash/EEPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, security codes, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high performance, ease-of-use and I/O flexibility make the PIC16F8X very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions; serial communication; capture, compare and PWM functions; and co-processor applications).

The serial in-system programming feature (via two pins) offers flexibility of customizing the product after complete assembly and testing. This feature can be used to serialize a product, store calibration data, or program the device with the current firmware before shipping.

### 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for PIC16C5X devices can be easily ported to PIC16F8X devices (Appendix B).

## 1.2 <u>Development Support</u>

The PIC16CXX family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler and fuzzy logic support tools are also available.

# PIC16F8X

NOTES:

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register), and the other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram for the PIC16F8X is shown in Figure 3-1, its corresponding pin description is shown in Table 3-1.

| Pin Name         | DIP<br>No.     | SOIC<br>No.       | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                                                                                                                              |

|------------------|----------------|-------------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN       | 16             | 16                | Ι             | ST/CMOS (3)           | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT      | 15             | 15                | 0             |                       | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR             | 4              | 4                 | I/P           | ST                    | Master clear (reset) input/programming voltage input. This pin is an active low reset to the device.                                                                                                     |

|                  |                |                   |               |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0              | 17             | 17                | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA1              | 18             | 18                | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA2              | 1              | 1                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA3              | 2              | 2                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA4/T0CKI        | 3              | 3                 | I/O           | ST                    | Can also be selected to be the clock input to the TMR0 timer/ counter. Output is open drain type.                                                                                                        |

|                  |                |                   |               |                       | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                       |

| RB0/INT          | 6              | 6                 | I/O           | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                               |

| RB1              | 7              | 7                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB2              | 8              | 8                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB3              | 9              | 9                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB4              | 10             | 10                | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB5              | 11             | 11                | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB6              | 12             | 12                | I/O           | TTL/ST <sup>(2)</sup> | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7              | 13             | 13                | I/O           | TTL/ST (2)            | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Vss              | 5              | 5                 | Р             | —                     | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| Vdd              | 14             | 14                | Р             | —                     | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Legend: I= input | 0 = 0<br>— = N | utput<br>lot used |               | /O = Input/Out        | •                                                                                                                                                                                                        |

## TABLE 3-1 PIC16F8X PINOUT DESCRIPTION

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

### 3.1 <u>Clocking Scheme/Instruction Cycle</u>

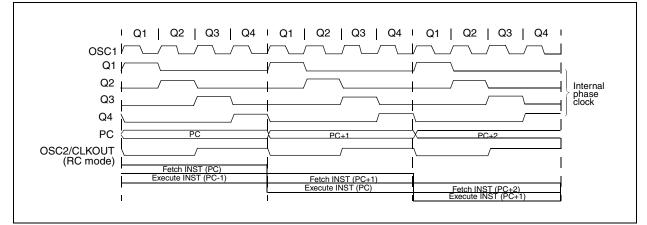

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

### 3.2 Instruction Flow/Pipelining

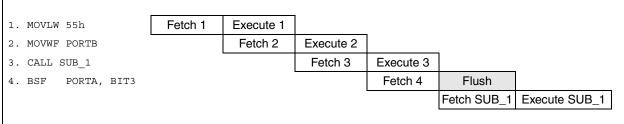

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

### 4.2 Data Memory Organization

The data memory is partitioned into two areas. The first is the Special Function Registers (SFR) area, while the second is the General Purpose Registers (GPR) area. The SFRs control the operation of the device.

Portions of data memory are banked. This is for both the SFR area and the GPR area. The GPR area is banked to allow greater than 116 bytes of general purpose RAM. The banked areas of the SFR are for the registers that control the peripheral functions. Banking requires the use of control bits for bank selection. These control bits are located in the STATUS Register. Figure 4-1 and Figure 4-2 show the data memory map organization.

Instructions MOVWF and MOVF can move values from the W register to any location in the register file ("F"), and vice-versa.

The entire data memory can be accessed either directly using the absolute address of each register file or indirectly through the File Select Register (FSR) (Section 4.5). Indirect addressing uses the present value of the RP1:RP0 bits for access into the banked areas of data memory.

Data memory is partitioned into two banks which contain the general purpose registers and the special function registers. Bank 0 is selected by clearing the RP0 bit (STATUS<5>). Setting the RP0 bit selects Bank 1. Each Bank extends up to 7Fh (128 bytes). The first twelve locations of each Bank are reserved for the Special Function Registers. The remainder are General Purpose Registers implemented as static RAM.

### 4.2.1 GENERAL PURPOSE REGISTER FILE

All devices have some amount of General Purpose Register (GPR) area. Each GPR is 8 bits wide and is accessed either directly or indirectly through the FSR (Section 4.5).

The GPR addresses in bank 1 are mapped to addresses in bank 0. As an example, addressing location 0Ch or 8Ch will access the same GPR.

### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (Figure 4-1, Figure 4-2 and Table 4-1) are used by the CPU and Peripheral functions to control the device operation. These registers are static RAM.

The special function registers can be classified into two sets, core and peripheral. Those associated with the core functions are described in this section. Those related to the operation of the peripheral features are described in the section for that specific feature.

# PIC16F8X

NOTES:

# 7.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead it is indirectly addressed through the Special Function Registers. There are four SFRs used to read and write this memory. These registers are:

- EECON1

- EECON2

- EEDATA

- EEADR

EEDATA holds the 8-bit data for read/write, and EEADR holds the address of the EEPROM location being accessed. PIC16F8X devices have 64 bytes of data EEPROM with an address range from 0h to 3Fh.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The writetime will vary with voltage and temperature as well as from chip to chip. Please refer to AC specifications for exact limits.

When the device is code protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access this memory.

## 7.1 <u>EEADR</u>

The EEADR register can address up to a maximum of 256 bytes of data EEPROM. Only the first 64 bytes of data EEPROM are implemented.

The upper two bits are address decoded. This means that these two bits must always be '0' to ensure that the address is in the 64 byte memory space.

| U       | U                                                                                                                                                                                                                                                     | U                      | R/W-0                  | R/W-x | R/W-0      | R/S-0       | R/S-x      |                                                                                                           |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|-------|------------|-------------|------------|-----------------------------------------------------------------------------------------------------------|--|

| _       | _                                                                                                                                                                                                                                                     |                        | EEIF                   | WRERR | WREN       | WR          | RD         | R = Readable bit                                                                                          |  |

| bit7    |                                                                                                                                                                                                                                                       |                        |                        |       |            |             | bitO       | W = Writable bit<br>S = Settable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |

| bit 7:5 | Unimplem                                                                                                                                                                                                                                              | nented: F              | Read as '(             | )'    |            |             |            |                                                                                                           |  |

| bit 4   | bit 4 <b>EEIF</b> : EEPROM Write Operation Interrupt Flag bit<br>1 = The write operation completed (must be cleared in software)<br>0 = The write operation is not complete or has not been started                                                   |                        |                        |       |            |             |            |                                                                                                           |  |

| bit 3   | <ul> <li>WRERR: EEPROM Error Flag bit</li> <li>1 = A write operation is prematurely terminated         <ul> <li>(any MCLR reset or any WDT reset during normal operation)</li> <li>0 = The write operation completed</li> </ul> </li> </ul>           |                        |                        |       |            |             |            |                                                                                                           |  |

| bit 2   | <ul> <li>WREN: EEPROM Write Enable bit</li> <li>1 = Allows write cycles</li> <li>0 = Inhibits write to the data EEPROM</li> </ul>                                                                                                                     |                        |                        |       |            |             |            |                                                                                                           |  |

| bit 1   | <ul> <li>WR: Write Control bit</li> <li>1 = initiates a write cycle. (The bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.</li> <li>0 = Write cycle to the data EEPROM is complete</li> </ul> |                        |                        |       |            |             |            |                                                                                                           |  |

| bit 0   | be set                                                                                                                                                                                                                                                | es an EEI<br>(not clea | PROM rea<br>red) in so |       | kes one cy | /cle. RD is | cleared in | hardware. The RD bit can only                                                                             |  |

### FIGURE 7-1: EECON1 REGISTER (ADDRESS 88h)

# 8.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real time applications. The PIC16F8X has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These features are:

- OSC Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

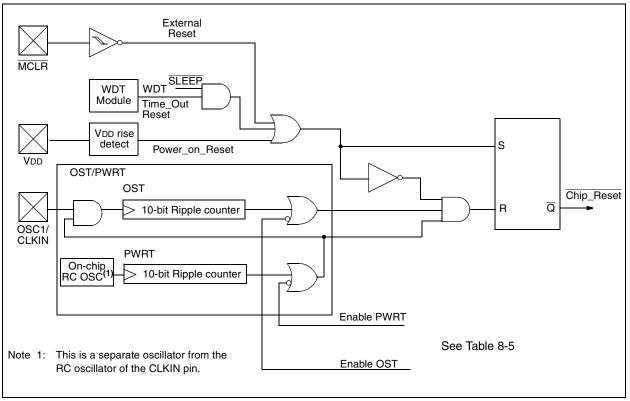

The PIC16F8X has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. This design keeps the device in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode offers a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer time-out or through an interrupt. Several oscillator options are provided to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select the various options.

### FIGURE 8-8: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

### 8.12 Power-down Mode (SLEEP)

A device may be powered down (SLEEP) and later powered up (Wake-up from SLEEP).

### 8.12.1 SLEEP

The Power-down mode is entered by executing the SLEEP instruction.

If enabled, the Watchdog Timer is cleared (but keeps running), the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  bit (STATUS<4>) is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For the lowest current consumption in SLEEP mode, place all I/O pins at either at VDD or VSS, with no external circuitry drawing current from the I/O pins, and disable external clocks. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

It should be noted that a RESET generated by a WDT time-out does not drive the MCLR pin low.

### 8.12.2 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. WDT Wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, RB port change, or data EEPROM write complete.

Peripherals cannot generate interrupts during SLEEP, since no on-chip Q clocks are present.

The first event ( $\overline{\text{MCLR}}$  reset) will cause a device reset. The two latter events are considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits can be used to determine the cause of a device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

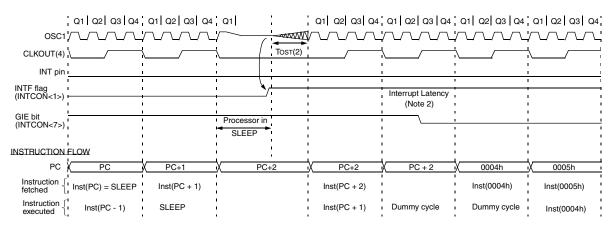

While the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the state of the substant of the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

## FIGURE 8-19: WAKE-UP FROM SLEEP THROUGH INTERRUPT

Note 1: XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

# PIC16F8X

| RETLW             | Return with Literal in W         |                                           | RETURN                           | Return f                                | rom Sub           | routine             |                  |                                      |                  |

|-------------------|----------------------------------|-------------------------------------------|----------------------------------|-----------------------------------------|-------------------|---------------------|------------------|--------------------------------------|------------------|

| Syntax:           | [ label ]                        | RETLW                                     | k                                |                                         | Syntax:           | [ label ]           | RETUR            | N                                    |                  |

| Operands:         | $0 \le k \le 2$                  | 55                                        |                                  |                                         | Operands:         | None                |                  |                                      |                  |

| Operation:        | $k \rightarrow (W);$             |                                           |                                  |                                         | Operation:        | $TOS \rightarrow F$ | ъС               |                                      |                  |

|                   | $TOS \rightarrow F$              | ъС                                        |                                  |                                         | Status Affected:  | None                |                  |                                      |                  |

| Status Affected:  | None                             |                                           |                                  |                                         | Encoding:         | 00                  | 0000             | 0000                                 | 1000             |

| Encoding:         | 11                               | 01xx                                      | kkkk                             | kkkk                                    | Description:      | Return fro          | m subrout        | ine. The st                          | ack is           |

| Description:      |                                  | gister is loa<br><'. The pro<br>m the top | gram coun                        | iter is                                 |                   |                     | nto the pro      | of the stack<br>ogram cour<br>ction. | · /              |

|                   | return add                       | dress). This                              |                                  |                                         | Words:            | 1                   |                  |                                      |                  |

| Manda.            | instructior                      | 1.                                        |                                  |                                         | Cycles:           | 2                   |                  |                                      |                  |

| Words:            | 1                                |                                           |                                  |                                         | Q Cycle Activity: | Q1                  | Q2               | Q3                                   | Q4               |

| Cycles:           | 2                                | 00                                        | 00                               | 04                                      | 1st Cycle         | Decode              | No-Opera         |                                      | Pop from         |

| Q Cycle Activity: | Q1                               | Q2                                        | Q3                               | Q4                                      |                   |                     | tion             | tion                                 | the Stack        |

| 1st Cycle         | Decode                           | Read<br>literal 'k'                       | No-Opera<br>tion                 | Write to<br>W, Pop<br>from the<br>Stack | 2nd Cycle         | No-Operat<br>ion    | No-Opera<br>tion | No-Opera<br>tion                     | No-Opera<br>tion |

| 2nd Cycle         |                                  | No-Opera                                  |                                  | No-Operat                               | Example           | RETURN              |                  |                                      |                  |

|                   | No-Operat<br>ion                 | tion                                      | tion                             | ion                                     |                   | After Inte          | errupt           |                                      |                  |

|                   |                                  |                                           | •                                |                                         |                   |                     |                  | TOS                                  |                  |

| Example           | CALL TABL                        | ;offset                                   | tains tabl<br>value<br>has table |                                         |                   |                     |                  |                                      |                  |

| TABLE             | ADDWF PC<br>RETLW k1<br>RETLW k2 | ;W = off<br>;Begin t<br>;                 |                                  |                                         |                   |                     |                  |                                      |                  |

|                   | •                                |                                           |                                  |                                         |                   |                     |                  |                                      |                  |

|                   | •<br>RETLW kn                    | ; End of                                  | table                            |                                         |                   |                     |                  |                                      |                  |

|                   | Before In                        | struction                                 |                                  |                                         |                   |                     |                  |                                      |                  |

|                   |                                  |                                           | 0x07                             |                                         |                   |                     |                  |                                      |                  |

|                   | After Inst                       |                                           | value of k                       | 3                                       |                   |                     |                  |                                      |                  |

|                   |                                  | •• -                                      |                                  | -                                       |                   |                     |                  |                                      |                  |

# **10.0 DEVELOPMENT SUPPORT**

### 10.1 <u>Development Tools</u>

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- PICMASTER<sup>®</sup>/PICMASTER CE Real-Time In-Circuit Emulator

- ICEPIC<sup>™</sup> Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB<sup>™</sup> SIM Software Simulator

- MPLAB-C17 (C Compiler)

- Fuzzy Logic Development System (*fuzzy*TECH<sup>®</sup>–MP)

### 10.2 <u>PICMASTER: High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The PICMASTER Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for all microcontrollers in the PIC14C000, PIC12CXXX, PIC16C5X, PIC16CXXX and PIC17CXX families. PICMASTER is supplied with the MPLAB<sup>™</sup> Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable target probes allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the PICMASTER allows expansion to support all new Microchip microcontrollers.

The PICMASTER Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x environment were chosen to best make these features available to you, the end user.

A CE compliant version of PICMASTER is available for European Union (EU) countries.

### 10.3 ICEPIC: Low-Cost PIC MCU In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC12CXXX, PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 286-AT<sup>®</sup> through Pentium<sup>™</sup> based machines under Windows 3.x environment. ICE-PIC features real time, non-intrusive emulation.

### 10.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

### 10.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, low-cost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923, PIC16C924 and PIC17C756 may be supported with an adapter socket. PICSTART Plus is CE compliant.

### 10.6 <u>PICDEM-1 Low-Cost PIC MCU</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the PICMASTER emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

### 10.7 <u>PICDEM-2 Low-Cost PIC16CXX</u> <u>Demonstration Board</u>

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

### 10.8 <u>PICDEM-3 Low-Cost PIC16CXXX</u> Demonstration Board

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

### 10.9 <u>MPLAB™ Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE Software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a windows based application which contains:

- A full featured editor

- Three operating modes

- editor

- emulator

- simulator

- A project manager

- Customizable tool bar and key mapping

- A status bar with project information

- Extensive on-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- Transfer data dynamically via DDE (soon to be replaced by OLE)

- Run up to four emulators on the same PC

The ability to use MPLAB with Microchip's simulator allows a consistent platform and the ability to easily switch from the low cost simulator to the full featured emulator with minimal retraining due to development tools.

### 10.10 Assembler (MPASM)

The MPASM Universal Macro Assembler is a PC-hosted symbolic assembler. It supports all microcontroller series including the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX, and PIC17CXX families.

MPASM offers full featured Macro capabilities, conditional assembly, and several source and listing formats. It generates various object code formats to support Microchip's development tools as well as third party programmers.

MPASM allows full symbolic debugging from PICMASTER, Microchip's Universal Emulator System.

NOTES:

# 11.0 ELECTRICAL CHARACTERISTICS FOR PIC16CR83 AND PIC16CR84

### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                                                              | 55°C to +125°C                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Ambient temperature under bias<br>Storage temperature                                                                                                                       | 65°C to +150°C                                                                                       |

| Voltage on VDD with respect to Vss                                                                                                                                          |                                                                                                      |

| Voltage on MCLR with respect to Vss <sup>(2)</sup>                                                                                                                          |                                                                                                      |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                                                                                |                                                                                                      |

| Total power dissipation <sup>(1)</sup>                                                                                                                                      |                                                                                                      |

| Maximum current out of Vss pin                                                                                                                                              |                                                                                                      |

| Maximum current into VDD pin                                                                                                                                                |                                                                                                      |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                                                                                |                                                                                                      |

| Output clamp current, Iок (Vo < 0 or Vo > VDD)                                                                                                                              |                                                                                                      |

| Maximum output current sunk by any I/O pin                                                                                                                                  |                                                                                                      |

| Maximum output current sunk by any I/O pin<br>Maximum output current sourced by any I/O pin                                                                                 |                                                                                                      |

| Maximum current sunk by PORTA                                                                                                                                               |                                                                                                      |

| Maximum current sourced by PORTA                                                                                                                                            |                                                                                                      |

| Maximum current sourced by PORTA<br>Maximum current sunk by PORTB                                                                                                           | \                                                                                                    |

| Maximum current sourced by PORTB.                                                                                                                                           | ,                                                                                                    |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD $\chi$ {IDD - $\Sigma$ D                                                                              |                                                                                                      |

| Note 2: Voltage spikes below Vss at the $\overline{\text{MCLR}}$ pin, inducing currents greate<br>a series resistor of 50-100 $\Omega$ should be used when applying a "low" | rthan 80 mA, may cause latch-up. Thus, level to the $\overline{\text{MCLR}}$ pin rather than pulling |

this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 11.1 DC CHARACTERISTICS:

### PIC16CR84, PIC16CR83 (Commercial, Industrial)

| DC Characteristics<br>Power Supply Pins |      |                                                                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial) |                   |                |                |                                                                                                                                                                              |  |

|-----------------------------------------|------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter<br>No.                        | Sym  | Characteristic                                                   | Min                                                                                                                                                                                    | Тур†              | Max            | Units          | Conditions                                                                                                                                                                   |  |

| D001<br>D001A                           | Vdd  | Supply Voltage                                                   | 4.0<br>4.5                                                                                                                                                                             | _                 | 6.0<br>5.5     | V<br>V         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                      |  |

| D002                                    | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5*                                                                                                                                                                                   | —                 | —              | V              | Device in SLEEP mode                                                                                                                                                         |  |

| D003                                    | VPOR | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | —                                                                                                                                                                                      | Vss               | —              | V              | See section on Power-on Reset for details                                                                                                                                    |  |

| D004                                    | Svdd | VDD rise rate to ensure<br>internal Power-on<br>Reset signal     | 0.05*                                                                                                                                                                                  | —                 | —              | V/ms           | See section on Power-on Reset for details                                                                                                                                    |  |

| D010<br>D010A                           | IDD  | Supply Current <sup>(2)</sup>                                    |                                                                                                                                                                                        | 1.8<br>7.3        | 4.5<br>10      | mA<br>mA       | RC and XT ose configuration <sup>(4)</sup><br>Fosc = 4.0 MHz, VDD = 5.5V<br>Fosc = 4.0 MHz, VDD = 5.5V<br>(During EERROM programming)<br>HS oso configuration (PIC16CR84-10) |  |

| D013                                    |      | (0)                                                              |                                                                                                                                                                                        | 5                 | 10             | mA<            | Fosc = $10$ MHz, VDD = 5.5V                                                                                                                                                  |  |

| D020<br>D021<br>D021A                   | IPD  | Power-down Current <sup>(3)</sup>                                |                                                                                                                                                                                        | 7.0<br>1.0<br>1.0 | 28<br>14<br>16 | μΑ<br>μΑ<br>μΑ | $V_{DD} = 4.0V$ , WDT enabled, industrial<br>$V_{DD} = 4.0V$ , WDT disabled, commercial<br>$V_{DD} = 4.0V$ , WDT disabled, industrial                                        |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1=external square wave, from rail to rail, all I/O pins tristated, pulled to VDD, T0CKI = VDD,  $\overline{MCLR} = VDD$ ; WDT applied displayed as approximate

MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula IB = VpD/2Rext (mA) with Rext in kOhm.

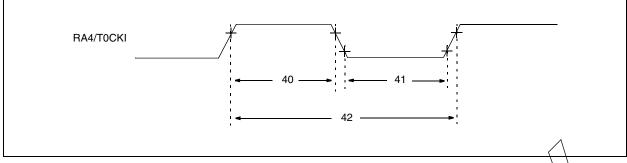

### FIGURE 11-6: TIMER0 CLOCK TIMINGS

### TABLE 11-6 TIMER0 CLOCK REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic         |                | Min           | Тур†           | Max         | Units   | Conditions                                                                                        |

|------------------|------|------------------------|----------------|---------------|----------------|-------------|---------|---------------------------------------------------------------------------------------------------|

| 40               | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5TCY + 20 * |                | É           | ns      | 5                                                                                                 |

|                  |      |                        | With Prescaler | 50 *<br>30 *  | ) I            | _           |         | $\begin{array}{l} 2.0V \neq V \text{DD} \leq 3.0V \\ 3.0V \leq V \text{DD} \leq 6.0V \end{array}$ |

| 41               | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5Tcy + 20 * | Л              | X           | ns      | $\rightarrow$                                                                                     |

|                  |      |                        | With Prescaler | 50 *<br>20 *  | $\overline{1}$ | $\searrow$  | )<br>ns | $\begin{array}{l} 2.0V \leq V \text{DD} \leq 3.0V \\ 3.0V \leq V \text{DD} \leq 6.0V \end{array}$ |

| 42               | Tt0P | T0CKI Period           |                | Tcy + 40 *    |                | $\rangle -$ | ns      | N = prescale value<br>(2, 4,, 256)                                                                |

\* These parameters are characterized but not tested.

+ Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

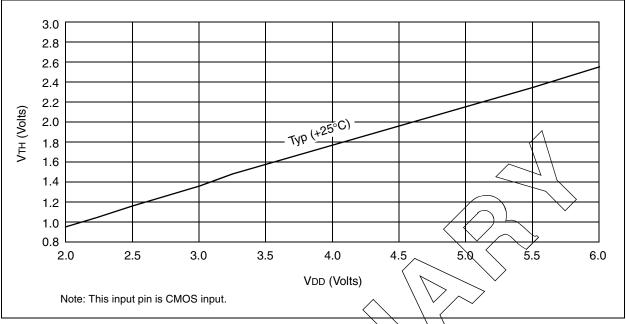

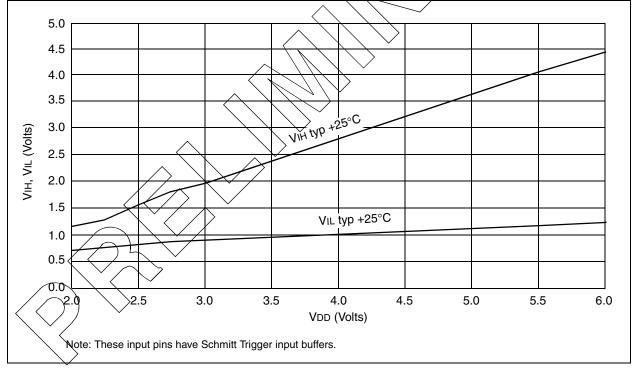

FIGURE 12-9: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) vs. VDD

# **PIC16F8X PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br> <br>Device | -XX     X     /XX     XXX                                 Frequency Temperature     Package     Pattern       Range     Range                                                                                                                                                                                                                  | Examples:<br>a) PIC16F84 -04/P 301 = Commercial<br>temp., PDIP package, 4 MHz, normal                                                                                                                                                                                          |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                  | PIC16F8X <sup>(2)</sup> , PIC16F8XT <sup>(3)</sup><br>PIC16LF8X <sup>(2)</sup> , PIC16LF8XT <sup>(3)</sup><br>PIC16F8XA <sup>(2)</sup> , PIC16F8XAT <sup>(3)</sup><br>PIC16LF8XA <sup>(2)</sup> , PIC16LF8XAT <sup>(3)</sup><br>PIC16CR8X <sup>(2)</sup> , PIC16CR8XT <sup>(3)</sup><br>PIC16LCR8X <sup>(2)</sup> , PIC16LCR8XT <sup>(3)</sup> | <ul> <li>VDD limits, QTP pattern #301.</li> <li>b) PIC16LF84 - 04I/SO = Industrial temp.,<br/>SOIC package, 200 kHz, Extended VDD<br/>limits.</li> <li>c) PIC16CR84 - 10I/P = ROM program<br/>memory, Industrial temp., PDIP package,<br/>10MHz, normal VDD limits.</li> </ul> |

| Frequency<br>Range      | 04 = 4 MHz<br>10 = 10 MHz<br>20 = 20 MHz                                                                                                                                                                                                                                                                                                       | Note 1: b = blank                                                                                                                                                                                                                                                              |

| Temperature<br>Range    | $b^{(1)} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ (Commercial)}$<br>I = -40°C to +85°C (Industrial)                                                                                                                                                                                                                                        | 2: F = Standard VDD range<br>LF = Extended VDD range<br>CR = ROM Version, Standard VDD                                                                                                                                                                                         |

| Package<br>Pattern      | P = PDIP<br>SO = SOIC (Gull Wing, 300 mil body)<br>SS = SSOP<br>3-digit Pattern Code for QTP, ROM (blank otherwise)                                                                                                                                                                                                                            | range<br>LCR = ROM Version, Extended VDD<br>range<br>3: T = in tape and reel - SOIC, SSOP                                                                                                                                                                                      |

|                         |                                                                                                                                                                                                                                                                                                                                                | packages only.                                                                                                                                                                                                                                                                 |

# SALES AND SUPPORT

Products supported by a preliminary Data Sheet may possibly have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office.

- 2. The Microchip's Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).