Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 68 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f84-10i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register), and the other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

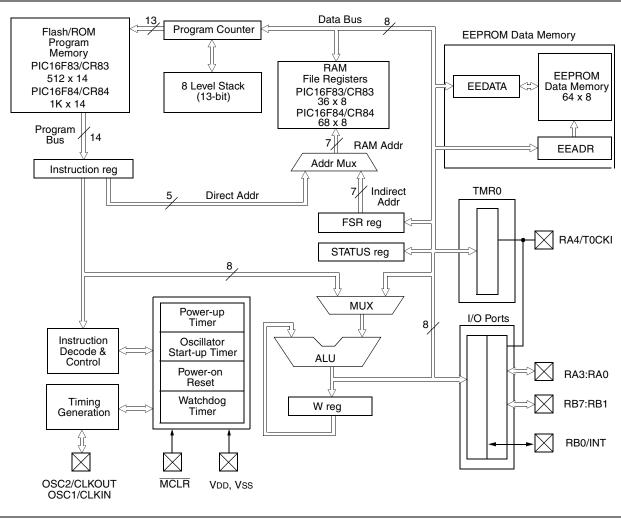

A simplified block diagram for the PIC16F8X is shown in Figure 3-1, its corresponding pin description is shown in Table 3-1.

| Pin Name         | DIP<br>No.     | SOIC<br>No.       | l/O/P<br>Type | Buffer<br>Type        | Description                                                                                                                                                                                              |

|------------------|----------------|-------------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN       | 16             | 16                | Ι             | ST/CMOS (3)           | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT      | 15             | 15                | 0             |                       | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR             | 4              | 4                 | I/P           | ST                    | Master clear (reset) input/programming voltage input. This pin is an active low reset to the device.                                                                                                     |

|                  |                |                   |               |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0              | 17             | 17                | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA1              | 18             | 18                | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA2              | 1              | 1                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA3              | 2              | 2                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RA4/T0CKI        | 3              | 3                 | I/O           | ST                    | Can also be selected to be the clock input to the TMR0 timer/<br>counter. Output is open drain type.                                                                                                     |

|                  |                |                   |               |                       | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                       |

| RB0/INT          | 6              | 6                 | I/O           | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                               |

| RB1              | 7              | 7                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB2              | 8              | 8                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB3              | 9              | 9                 | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB4              | 10             | 10                | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB5              | 11             | 11                | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB6              | 12             | 12                | I/O           | TTL/ST <sup>(2)</sup> | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7              | 13             | 13                | I/O           | TTL/ST (2)            | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Vss              | 5              | 5                 | Р             | —                     | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| Vdd              | 14             | 14                | Р             | —                     | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Legend: I= input | 0 = 0<br>— = N | utput<br>lot used |               | /O = Input/Out        | •                                                                                                                                                                                                        |

#### TABLE 3-1 PIC16F8X PINOUT DESCRIPTION

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

#### 4.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external INT interrupt, TMR0, and the weak pull-ups on PORTB.

#### FIGURE 4-1: OPTION\_REG REGISTER (ADDRESS 81h)

**Note:** When the prescaler is assigned to the WDT (PSA = '1'), TMR0 has a 1:1 prescaler assignment.

| R/W-1            | R/W-1                                                                                                                         | R/W-1            | R/W-1    | R/W-1      | R/W-1      | R/W-1 | R/W-1 |                                       |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|----------|------------|------------|-------|-------|---------------------------------------|--|--|--|

| RBPU             | INTEDG                                                                                                                        | TOCS             | T0SE     | PSA        | PS2        | PS1   | PS0   | R = Readable bit                      |  |  |  |

| bit7             |                                                                                                                               |                  |          |            |            |       | bit0  | W = Writable bit                      |  |  |  |

|                  |                                                                                                                               |                  |          |            |            |       |       | U = Unimplemented bit,<br>read as '0' |  |  |  |

|                  |                                                                                                                               |                  |          |            |            |       |       | - n = Value at POR reset              |  |  |  |

| bit 7:           | RBPU: PC                                                                                                                      |                  | ın Enabl | a hit      |            |       |       |                                       |  |  |  |

| Dit 7.           |                                                                                                                               |                  |          |            |            |       |       |                                       |  |  |  |

|                  | <ul> <li>1 = PORTB pull-ups are disabled</li> <li>0 = PORTB pull-ups are enabled (by individual port latch values)</li> </ul> |                  |          |            |            |       |       |                                       |  |  |  |

| bit 6:           | INTEDG:                                                                                                                       |                  |          |            |            |       | ,     |                                       |  |  |  |

| bit 0.           | 1 = Interru                                                                                                                   | •                | •        |            | nin        |       |       |                                       |  |  |  |

|                  | 0 = Interru                                                                                                                   |                  |          |            |            |       |       |                                       |  |  |  |

| bit 5:           | TOCS: TM                                                                                                                      |                  |          |            | r          |       |       |                                       |  |  |  |

| Dit J.           | 1 = Transit                                                                                                                   |                  |          |            |            |       |       |                                       |  |  |  |

|                  | 0 = Interna                                                                                                                   |                  |          | •          | OUT)       |       |       |                                       |  |  |  |

| bit 4:           | TOSE: TM                                                                                                                      |                  | •        |            |            |       |       |                                       |  |  |  |

| DIL 4.           |                                                                                                                               |                  |          |            | on RA4/T00 |       |       |                                       |  |  |  |

|                  |                                                                                                                               |                  |          |            | on RA4/T00 |       |       |                                       |  |  |  |

| bit 3:           | PSA: Pres                                                                                                                     |                  | •        |            |            | p     |       |                                       |  |  |  |

| DIL 3.           | 1 = Presca                                                                                                                    |                  |          |            |            |       |       |                                       |  |  |  |

|                  | 0 = Presca                                                                                                                    |                  |          |            |            |       |       |                                       |  |  |  |

| hit 2 0.         | PS2:PS0:                                                                                                                      | •                |          |            |            |       |       |                                       |  |  |  |

| bit <u>∠</u> -0. |                                                                                                                               |                  |          |            |            |       |       |                                       |  |  |  |

|                  | Bit Value                                                                                                                     | TMR0 Ra          | te WD    | Γ Rate     |            |       |       |                                       |  |  |  |

|                  | 000                                                                                                                           | 1:2              | 1 :      |            |            |       |       |                                       |  |  |  |

|                  | 001                                                                                                                           | 1:4              | 1:       |            |            |       |       |                                       |  |  |  |

|                  | 010<br>011                                                                                                                    | 1:8              |          | : 4<br>: 8 |            |       |       |                                       |  |  |  |

|                  | 100                                                                                                                           | 1 : 16<br>1 : 32 |          | 16         |            |       |       |                                       |  |  |  |

|                  | 101                                                                                                                           | 1:64             |          | 32         |            |       |       |                                       |  |  |  |

|                  | 110                                                                                                                           | 1 : 128          |          | 64         |            |       |       |                                       |  |  |  |

|                  | 111                                                                                                                           | 1 : 256          | 1:       | 128        |            |       |       |                                       |  |  |  |

|                  |                                                                                                                               |                  |          |            |            |       |       |                                       |  |  |  |

|                  |                                                                                                                               |                  |          |            |            |       |       |                                       |  |  |  |

#### 4.2.2.3 INTCON REGISTER

The INTCON register is a readable and writable register which contains the various enable bits for all interrupt sources.

# **Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

#### FIGURE 4-1: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0  | R/W-0                                                                                                                                                                                                                                                                 | R/W-0       | R/W-0       | R/W-0      | R/W-0         | R/W-0      | R/W-x        |                                                                                                                      |  |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------------|---------------|------------|--------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| GIE    | EEIE                                                                                                                                                                                                                                                                  | T0IE        | INTE        | RBIE       | T0IF          | INTF       | RBIF         | R = Readable bit                                                                                                     |  |  |  |

| bit7   |                                                                                                                                                                                                                                                                       |             |             |            |               |            | bitO         | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |  |  |  |

| bit 7: | <b>GIE:</b> Glob<br>1 = Enabl<br>0 = Disab                                                                                                                                                                                                                            | es all un-r | nasked inf  |            |               |            |              |                                                                                                                      |  |  |  |

|        | Note: For                                                                                                                                                                                                                                                             | the opera   | tion of the | interrupt  | structure, p  | lease refe | r to Section | 8.5.                                                                                                                 |  |  |  |

| bit 6: | <ul> <li>Note: For the operation of the interrupt structure, please refer to Section 8.5.</li> <li>EEIE: EE Write Complete Interrupt Enable bit</li> <li>1 = Enables the EE write complete interrupt</li> <li>0 = Disables the EE write complete interrupt</li> </ul> |             |             |            |               |            |              |                                                                                                                      |  |  |  |

| bit 5: | <b>TOIE</b> : TMI<br>1 = Enabl<br>0 = Disab                                                                                                                                                                                                                           | es the TM   | R0 interru  | pt         | bit           |            |              |                                                                                                                      |  |  |  |

| bit 4: | INTE: RB<br>1 = Enabl<br>0 = Disab                                                                                                                                                                                                                                    | es the RB   | 0/INT inte  | rrupt      |               |            |              |                                                                                                                      |  |  |  |

| bit 3: | <b>RBIE</b> : RB<br>1 = Enabl<br>0 = Disab                                                                                                                                                                                                                            | es the RB   | port char   | ge interru | pt            |            |              |                                                                                                                      |  |  |  |

| bit 2: | <b>TOIF</b> : TMF<br>1 = TMR0<br>0 = TMR0                                                                                                                                                                                                                             | has over    | flowed (m   |            | ared in softw | vare)      |              |                                                                                                                      |  |  |  |

| bit 1: | INTF: RB<br>1 = The R<br>0 = The R                                                                                                                                                                                                                                    | B0/INT in   | terrupt oc  | curred     |               |            |              |                                                                                                                      |  |  |  |

| bit 0: |                                                                                                                                                                                                                                                                       | at least o  | ne of the l | RB7:RB4    |               |            | nust be clea | ared in software)                                                                                                    |  |  |  |

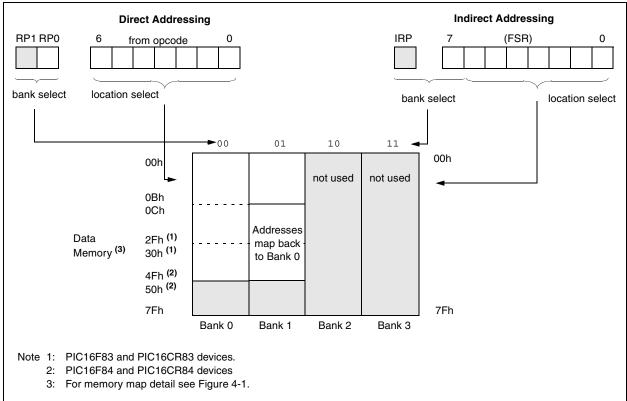

#### 4.5 Indirect Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 4-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

FIGURE 4-1: DIRECT/INDIRECT ADDRESSING

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-2.

#### EXAMPLE 4-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | movwf | FSR   | ; to RAM             |

| NEXT     | clrf  | INDF  | ;clear INDF register |

|          | incf  | FSR   | ;inc pointer         |

|          | btfss | FSR,4 | ;all done?           |

|          | goto  | NEXT  | ;NO, clear next      |

| CONTINUE |       |       |                      |

|          | :     |       | ;YES, continue       |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-1. However, IRP is not used in the PIC16F8X.

#### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch is unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output current may damage the chip.

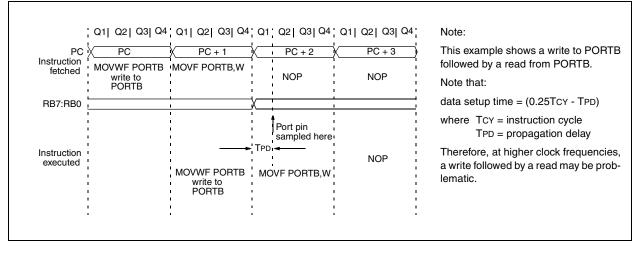

### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-5). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such that the pin voltage stabilizes (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}\,,\,\,{\tt BSF},\, etc.)$  on an I/O port.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ;PORTB<7:6> have external pull-ups and are ;not connected to other circuitry

| ' |     |        |       |   |      |       |      |      |

|---|-----|--------|-------|---|------|-------|------|------|

| ; |     |        |       |   | PORT | latch | PORT | pins |

| ; |     |        |       |   |      |       |      |      |

|   | BCF | PORTB, | 7     | ; | 01pp | ppp   | 11pp | ppp  |

|   | BCF | PORTB, | 6     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BSF | STATUS | , RPO | ; |      |       |      |      |

|   | BCF | TRISB, | 7     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BCF | TRISB, | 6     | ; | 10pp | ppp   | 10pp | ppp  |

| : |     |        |       |   |      |       |      |      |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

#### FIGURE 5-5: SUCCESSIVE I/O OPERATION

NOTES:

# 8.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real time applications. The PIC16F8X has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These features are:

- OSC Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

The PIC16F8X has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. This design keeps the device in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode offers a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer time-out or through an interrupt. Several oscillator options are provided to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select the various options.

#### TABLE 8-3 RESET CONDITION FOR PROGRAM COUNTER AND THE STATUS REGISTER

| Condition                           | Program Counter       | STATUS Register |

|-------------------------------------|-----------------------|-----------------|

| Power-on Reset                      | 000h                  | 0001 1xxx       |

| MCLR Reset during normal operation  | 000h                  | 000u uuuu       |

| MCLR Reset during SLEEP             | 000h                  | 0001 0uuu       |

| WDT Reset (during normal operation) | 000h                  | 0000 luuu       |

| WDT Wake-up                         | PC + 1                | uuu0 0uuu       |

| Interrupt wake-up from SLEEP        | PC + 1 <sup>(1)</sup> | uuul 0uuu       |

Legend: u = unchanged, x = unknown.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| Register   | Address | Power-on Reset | MCLR Reset during:<br>– normal operation<br>– SLEEP<br>WDT Reset during nor-<br>mal operation | Wake-up from SLEEP:<br>– through interrupt<br>– through WDT Time-out |

|------------|---------|----------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| W          | _       | XXXX XXXX      | սսսս սսսս                                                                                     | սսսս սսսս                                                            |

| INDF       | 00h     |                |                                                                                               |                                                                      |

| TMR0       | 01h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| PCL        | 02h     | 0000h          | 0000h                                                                                         | PC + 1 <sup>(2)</sup>                                                |

| STATUS     | 03h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                                      | uuuq quuu <sup>(3)</sup>                                             |

| FSR        | 04h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| PORTA      | 05h     | x xxxx         | u uuuu                                                                                        | u uuuu                                                               |

| PORTB      | 06h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| EEDATA     | 08h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| EEADR      | 09h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| PCLATH     | 0Ah     | 0 0000         | 0 0000                                                                                        | u uuuu                                                               |

| INTCON     | 0Bh     | 0000 000x      | 0000 000u                                                                                     | uuuu uuuu <sup>(1)</sup>                                             |

| INDF       | 80h     |                |                                                                                               |                                                                      |

| OPTION_REG | 81h     | 1111 1111      | 1111 1111                                                                                     | uuuu uuuu                                                            |

| PCL        | 82h     | 0000h          | 0000h                                                                                         | PC + 1                                                               |

| STATUS     | 83h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                                      | uuuq quuu <sup>(3)</sup>                                             |

| FSR        | 84h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| TRISA      | 85h     | 1 1111         | 1 1111                                                                                        | u uuuu                                                               |

| TRISB      | 86h     | 1111 1111      | 1111 1111                                                                                     | սսսս սսսս                                                            |

| EECON1     | 88h     | 0 x000         | 0 q000                                                                                        | 0 uuuu                                                               |

| EECON2     | 89h     |                |                                                                                               |                                                                      |

| PCLATH     | 8Ah     | 0 0000         | 0 0000                                                                                        | u uuuu                                                               |

| INTCON     | 8Bh     | 0000 000x      | 0000 000u                                                                                     | uuuu uuuu <sup>(1)</sup>                                             |

#### TABLE 8-4 RESET CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0',

q = value depends on condition.

Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: Table 8-3 lists the reset value for each specific condition.

#### 8.4 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, just tie the  $\overline{MCLR}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A minimum rise time for VDD must be met for this to operate properly. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be meet to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting.*"

The POR circuit does not produce an internal reset when VDD declines.

#### 8.5 Power-up Timer (PWRT)

The Power-up Timer (PWRT) provides a fixed 72 ms nominal time-out (TPWRT) from POR (Figure 8-10, Figure 8-11, Figure 8-12 and Figure 8-13). The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level (Possible exception shown in Figure 8-13).

A configuration bit, PWRTE, can enable/disable the PWRT. See either Figure 8-1 or Figure 8-2 for the operation of the PWRTE bit for a particular device.

The power-up time delay TPWRT will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

#### 8.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle delay (from OSC1 input) after the PWRT delay ends (Figure 8-10, Figure 8-11, Figure 8-12 and Figure 8-13). This ensures the crystal oscillator or resonator has started and stabilized.

The OST time-out (TOST) is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

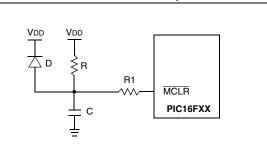

When VDD rises very slowly, it is possible that the TPWRT time-out and TOST time-out will expire before VDD has reached its final value. In this case (Figure 8-13), an external power-on reset circuit may be necessary (Figure 8-9).

#### FIGURE 8-9: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up rate is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not exceed 0.2V (max leakage current spec on MCLR pin is 5 μA). A larger voltage drop will degrade VIH level on the MCLR pin.

- 3: R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of an MCLR pin breakdown due to ESD or EOS.

#### 8.7 <u>Time-out Sequence and Power-down</u> Status Bits (TO/PD)

On power-up (Figure 8-10, Figure 8-11, Figure 8-12 and Figure 8-13) the time-out sequence is as follows: First PWRT time-out is invoked after a POR has expired. Then the OST is activated. The total time-out will vary based on oscillator configuration and PWRTE configuration bit status. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

### TABLE 8-5TIME-OUT IN VARIOUSSITUATIONS

| Oscillator    | Powe                | Wake-up          |               |  |

|---------------|---------------------|------------------|---------------|--|

| Configuration | PWRT<br>Enabled     | PWRT<br>Disabled | from<br>SLEEP |  |

| XT, HS, LP    | 72 ms +<br>1024Tosc | 1024Tosc         | 1024Tosc      |  |

| RC            | 72 ms               | _                | _             |  |

Since the time-outs occur from the POR reset pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high, execution will begin immediately (Figure 8-10). This is useful for testing purposes or to synchronize more than one PIC16F8X device when operating in parallel.

Table 8-6 shows the significance of the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits. Table 8-3 lists the reset conditions for some special registers, while Table 8-4 lists the reset conditions for all the registers.

### TABLE 8-6STATUS BITS AND THEIRSIGNIFICANCE

| то | PD | Condition                                                         |

|----|----|-------------------------------------------------------------------|

| 1  | 1  | Power-on Reset                                                    |

| 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| x  | 0  | Illegal, PD is set on POR                                         |

| 0  | 1  | WDT Reset (during normal operation)                               |

| 0  | 0  | WDT Wake-up                                                       |

| 1  | 1  | MCLR Reset during normal operation                                |

| 1  | 0  | MCLR Reset during SLEEP or interrupt                              |

|    |    | wake-up from SLEEP                                                |

#### 8.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

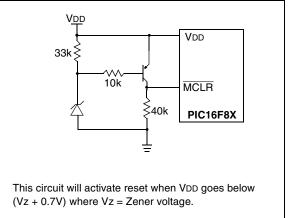

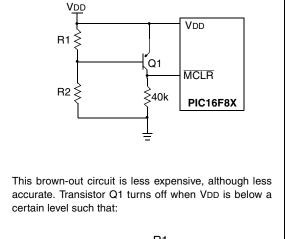

To reset a PIC16F8X device when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 8-14 and Figure 8-15.

#### FIGURE 8-14: BROWN-OUT PROTECTION CIRCUIT 1

#### FIGURE 8-15: BROWN-OUT PROTECTION CIRCUIT 2

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

#### 8.12 Power-down Mode (SLEEP)

A device may be powered down (SLEEP) and later powered up (Wake-up from SLEEP).

#### 8.12.1 SLEEP

The Power-down mode is entered by executing the SLEEP instruction.

If enabled, the Watchdog Timer is cleared (but keeps running), the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  bit (STATUS<4>) is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For the lowest current consumption in SLEEP mode, place all I/O pins at either at VDD or VSS, with no external circuitry drawing current from the I/O pins, and disable external clocks. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

It should be noted that a RESET generated by a WDT time-out does not drive the MCLR pin low.

#### 8.12.2 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. WDT Wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, RB port change, or data EEPROM write complete.

Peripherals cannot generate interrupts during SLEEP, since no on-chip Q clocks are present.

The first event ( $\overline{\text{MCLR}}$  reset) will cause a device reset. The two latter events are considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits can be used to determine the cause of a device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

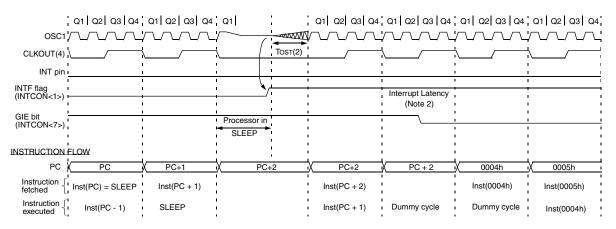

While the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the state of the substant of the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### FIGURE 8-19: WAKE-UP FROM SLEEP THROUGH INTERRUPT

Note 1: XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

| BTFSS             | Bit Test f, Skip if Set                                       |                  |                        |                  | CALL              | Call Sub                                                                                                                                                                                                  | proutine                |                  |                  |  |

|-------------------|---------------------------------------------------------------|------------------|------------------------|------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------|------------------|--|

| Syntax:           | [ <i>label</i> ] BTFS                                         | SS f,b           |                        |                  | Syntax:           | [ label ]                                                                                                                                                                                                 | [ <i>label</i> ] CALL k |                  |                  |  |

| Operands:         | $0 \leq f \leq 127$                                           |                  |                        |                  | Operands:         | $0 \le k \le 2$                                                                                                                                                                                           |                         |                  |                  |  |

|                   | 0 ≤ b < 7                                                     |                  |                        |                  | Operation:        | (PC)+ 1-                                                                                                                                                                                                  | → TOS,                  |                  |                  |  |

| Operation:        | skip if (f <b>)</b>                                           | -) = 1           |                        |                  |                   | $k \rightarrow PC <$                                                                                                                                                                                      | ,                       | 50 /0            |                  |  |

| Status Affected:  | None                                                          |                  |                        |                  | <b>.</b>          | ,                                                                                                                                                                                                         | 1<4:3>) -               | → PC<12          | :11>             |  |

| Encoding:         | 01 1                                                          | 11bb             | bfff                   | ffff             | Status Affected:  | None                                                                                                                                                                                                      | 1                       |                  | 1 1              |  |

| Description:      | If bit 'b' in regi                                            |                  |                        | ne next          | Encoding:         | 10                                                                                                                                                                                                        | 0kkk                    | kkkk             | kkkk             |  |

| Words:            | If bit 'b' is '1', t<br>discarded and<br>instead, making<br>1 | then the         | next instruits execute | ed               | Description:      | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is loaded<br>into PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH. CALL |                         |                  |                  |  |

| Cycles:           | 1(2)                                                          |                  |                        |                  |                   |                                                                                                                                                                                                           | ycle instru             | ction.           |                  |  |

| Q Cycle Activity: | Q1                                                            | Q2               | Q3                     | Q4               | Words:            | 1                                                                                                                                                                                                         |                         |                  |                  |  |

|                   |                                                               | Read             | Process                | No-Operat        | Cycles:           | 2                                                                                                                                                                                                         | 0.0                     | 0.0              | <u>.</u>         |  |

|                   | re                                                            | egister 'f'      | data                   | ion              | Q Cycle Activity: | Q1                                                                                                                                                                                                        | Q2                      | Q3               | Q4               |  |

| If Skip:          | (2nd Cycle)                                                   | )                |                        |                  | 1st Cycle         | Decode                                                                                                                                                                                                    | Read<br>literal 'k',    | Process<br>data  | Write to<br>PC   |  |

|                   | Q1                                                            | Q2               | Q3                     | Q4               |                   |                                                                                                                                                                                                           | Push PC<br>to Stack     |                  |                  |  |

|                   | No-Operat<br>ion                                              | o-Operati<br>on  | No-Opera<br>tion       | No-Operat<br>ion | 2nd Cycle         | No-Opera<br>tion                                                                                                                                                                                          | No-Opera<br>tion        | No-Opera<br>tion | No-Operat<br>ion |  |

| Example           |                                                               |                  | FLAG,1<br>PROCESS      | CODE             | Example           | HERE                                                                                                                                                                                                      | CALL                    | THERE            |                  |  |

|                   | TRUE •                                                        | •                | -                      | _                |                   | Before Ir                                                                                                                                                                                                 | nstruction              |                  |                  |  |

|                   | •                                                             | •                |                        |                  |                   | After Ins                                                                                                                                                                                                 | -                       | ddress HE        | RE               |  |

|                   | Before Instru                                                 | ruction          |                        |                  |                   |                                                                                                                                                                                                           |                         | ddress TH        | IERE             |  |

|                   | PC                                                            | C = a            | ddress H               | IERE             |                   |                                                                                                                                                                                                           | TOS = A                 | ddress HE        | IRE+1            |  |

|                   | After Instruc                                                 |                  |                        |                  |                   |                                                                                                                                                                                                           |                         |                  |                  |  |

|                   | if Fl<br>PC                                                   | FLAG<1><br>C = a | = 0,<br>address F#     | ALSE             |                   |                                                                                                                                                                                                           |                         |                  |                  |  |

|                   | if Fl                                                         | -LAG<1>          |                        |                  |                   |                                                                                                                                                                                                           |                         |                  |                  |  |

|                   | PC                                                            | C = 6            | address TI             | RUE              |                   |                                                                                                                                                                                                           |                         |                  |                  |  |

### PIC16F8X

| ff                |

|-------------------|

| n the<br>d        |

|                   |

| ' is              |

| truc-             |

|                   |

|                   |

| <b>Q</b> 4        |

| ite to<br>ination |

|                   |

| <b>Q</b> 4        |

| Operati<br>on     |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

|                   |

# PIC16F8X

| RLF               | Rotate Left f thr                                                                                                                                                                                                                                                                                          | ough Carry                   | RRF               | Rotate Right f through Carry                                                                                                                                                                                 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                                                                  | RLF f,d                      | Syntax:           | [ <i>label</i> ] RRF f,d                                                                                                                                                                                     |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                          |                              | Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                           |

| Operation:        | See description I                                                                                                                                                                                                                                                                                          | below                        | Operation:        | See description below                                                                                                                                                                                        |

| Status Affected:  | С                                                                                                                                                                                                                                                                                                          |                              | Status Affected:  | С                                                                                                                                                                                                            |

| Encoding:         | 00 1101                                                                                                                                                                                                                                                                                                    | dfff ffff                    | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                            |

| Description:      | •                                                                                                                                                                                                                                                                                                          |                              | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'. |

| Words:            | 1                                                                                                                                                                                                                                                                                                          |                              | Words:            | 1                                                                                                                                                                                                            |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                          |                              | Cycles:           | 1                                                                                                                                                                                                            |

| Q Cycle Activity: | Q1 Q2                                                                                                                                                                                                                                                                                                      | Q3 Q4                        | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                  |

|                   | Decode Read<br>register<br>'f'                                                                                                                                                                                                                                                                             | Process Write to destination |                   | Decode Read register data Vite to destination                                                                                                                                                                |

| Example           | $\begin{array}{cccc} RLF & REGI, 0 \\ \hline \mbox{Before Instruction} \\ \hline \mbox{REG1} & = & 1110 & 0110 \\ \mbox{C} & = & 0 \\ \hline \mbox{After Instruction} \\ \hline \mbox{REG1} & = & 1110 & 0110 \\ \mbox{W} & = & 1100 & 1100 \\ \mbox{C} & = & 1 \\ \hline \mbox{C} & = & 1 \\ \end{array}$ |                              | Example           | RRF REG1,0                                                                                                                                                                                                   |

|                   |                                                                                                                                                                                                                                                                                                            |                              |                   | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                         |

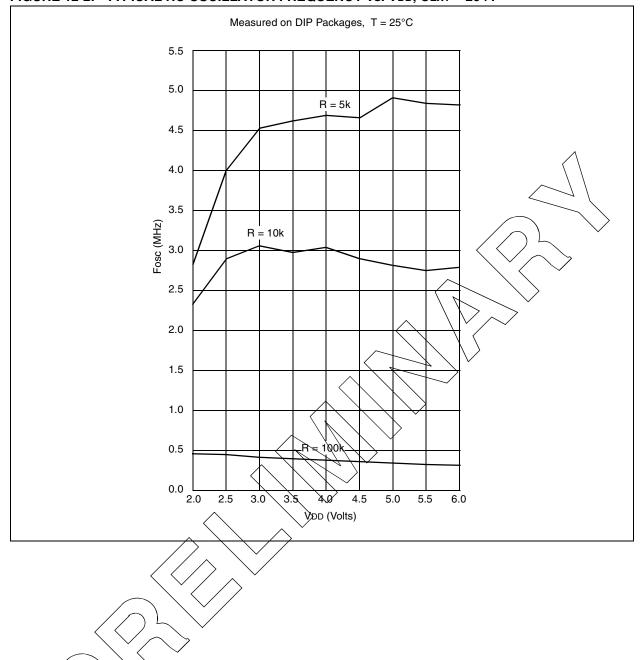

#### FIGURE 12-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 20 PF

# PIC16F8X

NOTES: