Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 × 8                                                                    |

| RAM Size                   | 68 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

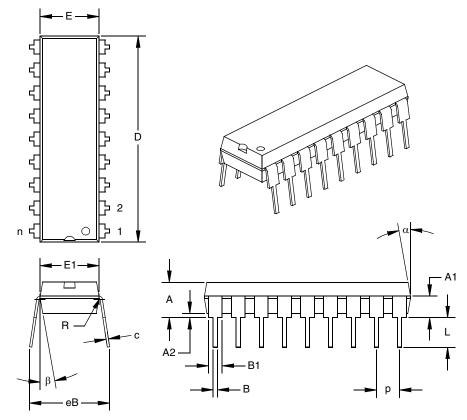

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f84t-04-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 PIC16F8X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in this section. When placing orders, please use the "PIC16F8X Product Identification System" at the back of this data sheet to specify the correct part number.

There are four device "types" as indicated in the device number.

- 1. **F**, as in PIC16**F**84. These devices have Flash program memory and operate over the standard voltage range.

- LF, as in PIC16LF84. These devices have Flash program memory and operate over an extended voltage range.

- 3. **CR**, as in PIC16**CR**83. These devices have ROM program memory and operate over the standard voltage range.

- 4. **LCR**, as in PIC16**LCR**84. These devices have ROM program memory and operate over an extended voltage range.

When discussing memory maps and other architectural features, the use of **F** and **CR** also implies the **LF** and **LCR** versions.

#### 2.1 Flash Devices

These devices are offered in the lower cost plastic package, even though the device can be erased and reprogrammed. This allows the same device to be used for prototype development and pilot programs as well as production.

A further advantage of the electrically-erasable Flash version is that it can be erased and reprogrammed incircuit, or by device programmers, such as Microchip's PICSTART<sup>®</sup> Plus or PRO MATE<sup>®</sup> II programmers.

#### 2.2 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices have all Flash locations and configuration options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available.

For information on submitting a QTP code, please contact your Microchip Regional Sales Office.

#### 2.3 <u>Serialized Quick-Turnaround-</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers the unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

For information on submitting a SQTP code, please contact your Microchip Regional Sales Office.

#### 2.4 ROM Devices

Some of Microchip's devices have a corresponding device where the program memory is a ROM. These devices give a cost savings over Microchip's traditional user programmed devices (EPROM, EEPROM).

ROM devices (PIC16CR8X) do not allow serialization information in the program memory space. The user may program this information into the Data EEPROM.

For information on submitting a ROM code, please contact your Microchip Regional Sales Office.

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture. This architecture has the program and data accessed from separate memories. So the device has a program memory bus and a data memory bus. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory (accesses over the same bus). Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. PIC16CXX opcodes are 14-bits wide, enabling single word instructions. The full 14-bit wide program memory bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions execute in a single cycle except for program branches.

The PIC16F83 and PIC16CR83 address 512 x 14 of program memory, and the PIC16F84 and PIC16CR84 address 1K x 14 program memory. All program memory is internal.

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. An orthogonal (symmetrical) instruction set makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

#### TABLE 5-1 PORTA FUNCTIONS

| Name      | Bit0 | Buffer Type | Function                                                                     |

|-----------|------|-------------|------------------------------------------------------------------------------|

| RA0       | bit0 | TTL         | Input/output                                                                 |

| RA1       | bit1 | TTL         | Input/output                                                                 |

| RA2       | bit2 | TTL         | Input/output                                                                 |

| RA3       | bit3 | TTL         | Input/output                                                                 |

| RA4/T0CKI | bit4 | ST          | Input/output or external clock input for TMR0.<br>Output is open drain type. |

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 5-2 SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|-------|-------|-------|-------|-----------|--------|--------|--------|--------|-------------------------------|---------------------------|

| 05h     | PORTA | —     | —     | —     | RA4/T0CKI | RA3    | RA2    | RA1    | RA0    | x xxxx                        | u uuuu                    |

| 85h     | TRISA | -     | —     | _     | TRISA4    | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111                        | 1 1111                    |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are unimplemented, read as '0'

#### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch is unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output current may damage the chip.

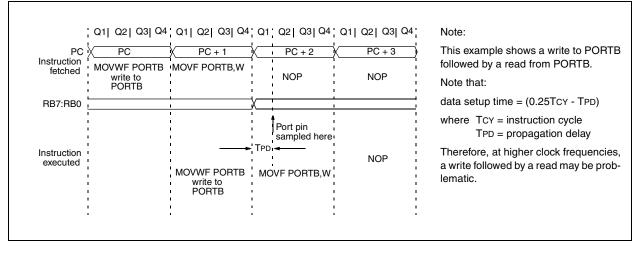

### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-5). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such that the pin voltage stabilizes (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}\,,\,\,{\tt BSF},\, etc.)$  on an I/O port.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ;PORTB<7:6> have external pull-ups and are ;not connected to other circuitry

| ' |     |        |       |   |      |       |      |      |

|---|-----|--------|-------|---|------|-------|------|------|

| ; |     |        |       |   | PORT | latch | PORT | pins |

| ; |     |        |       |   |      |       |      |      |

|   | BCF | PORTB, | 7     | ; | 01pp | ppp   | 11pp | ppp  |

|   | BCF | PORTB, | 6     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BSF | STATUS | , RPO | ; |      |       |      |      |

|   | BCF | TRISB, | 7     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BCF | TRISB, | 6     | ; | 10pp | ppp   | 10pp | ppp  |

| : |     |        |       |   |      |       |      |      |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

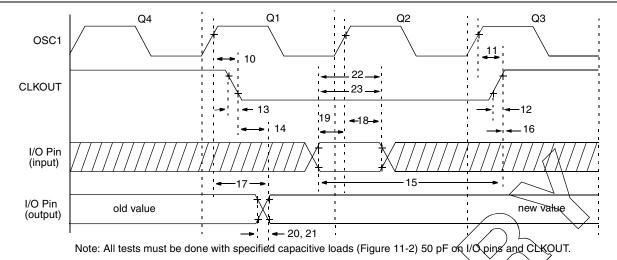

#### FIGURE 5-5: SUCCESSIVE I/O OPERATION

NOTES:

#### 7.2 EECON1 and EECON2 Registers

EECON1 is the control register with five low order bits physically implemented. The upper-three bits are nonexistent and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$  reset or a WDT time-out reset during normal operation. In these situations, following reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit EEIF is set when write is complete. It must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the Data EEPROM write sequence.

#### 7.3 Reading the EEPROM Data Memory

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD (EECON1<0>). The data is available, in the very next cycle, in the EEDATA register; therefore it can be read in the next instruction. EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

#### EXAMPLE 7-1: DATA EEPROM READ

| BCF   | STATUS, RPO | ; Bank 0          |

|-------|-------------|-------------------|

| MOVLW | CONFIG_ADDR | ;                 |

| MOVWF | EEADR       | ; Address to read |

| BSF   | STATUS, RPO | ; Bank 1          |

| BSF   | EECON1, RD  | ; EE Read         |

| BCF   | STATUS, RPO | ; Bank 0          |

| MOVF  | EEDATA, W   | ; W = EEDATA      |

#### 7.4 Writing to the EEPROM Data Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific sequence to initiate the write for each byte.

#### EXAMPLE 7-1: DATA EEPROM WRITE

|                     | BSF<br>BCF | STATUS, RPO<br>INTCON, GIE | ' | Bank 1<br>Disable INTs. |

|---------------------|------------|----------------------------|---|-------------------------|

|                     | BSF        | EECON1, WREN               | ; | Enable Write            |

|                     | MOVLW      | 55h                        | ; |                         |

|                     | MOVWF      | EECON2                     | ; | Write 55h               |

| p e                 | MOVLW      | AAh                        | ; |                         |

| lequired<br>equence | MOVWF      | EECON2                     | ; | Write AAh               |

| ng ng               | BSF        | EECON1,WR                  | ; | Set WR bit              |

| Se                  |            |                            | ; | begin write             |

|                     | BSF        | INTCON, GIE                | ; | Enable INTs.            |

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

#### 7.5 <u>Write Verify</u>

Depending on the application, good programming practice may dictate that the value written to the Data EEPROM should be verified (Example 7-1) to the desired value to be written. This should be used in applications where an EEPROM bit will be stressed near the specification limit. The Total Endurance disk will help determine your comfort level.

Generally the EEPROM write failure will be a bit which was written as a '1', but reads back as a '0' (due to leakage off the bit).

#### EXAMPLE 7-1: WRITE VERIFY

|    | BCF    | STATUS,   | RP0   | ; | Bank 0               |

|----|--------|-----------|-------|---|----------------------|

|    | :      |           |       | ; | Any code can go here |

|    | :      |           |       | ; |                      |

|    | MOVF   | EEDATA,   | W     | ; | Must be in Bank 0    |

|    | BSF    | STATUS,   | RP0   | ; | Bank 1               |

| RE | EAD    |           |       |   |                      |

|    | BSF    | EECON1,   | RD    | ; | YES, Read the        |

|    |        |           |       | ; | value written        |

|    | BCF    | STATUS,   | RP0   | ; | Bank 0               |

| ;  |        |           |       |   |                      |

| ;  | Is the | value wr: | itter | ı | (in W reg) and       |

| ;  | read   | (in EEDA  | ΓA) t | h | e same?              |

|    |        |           |       |   |                      |

| SUBWF | EEDATA, W | ;               |     |

|-------|-----------|-----------------|-----|

| BTFSS | STATUS, Z | ; Is difference | 0?  |

| GOTO  | WRITE_ERR | ; NO, Write err | or  |

| :     |           | ; YES, Good wri | te  |

| :     |           | ; Continue prog | ram |

#### 7.6 Protection Against Spurious Writes

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built in. On power-up, WREN is cleared. Also, the Power-up Timer (72 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch, or software malfunction.

#### 7.7 Data EEPROM Operation during Code Protect

When the device is code protected, the CPU is able to read and write unscrambled data to the Data EEPROM.

For ROM devices, there are two code protection bits (Section 8.1). One for the ROM program memory and one for the Data EEPROM memory.

#### TABLE 7-1 REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name   | Bit 7    | Bit 6                   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|--------|----------|-------------------------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------|

| 08h     | EEDATA | EEPROM   | data regis              | ter   |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                 |

| 09h     | EEADR  | EEPROM a | EPROM address register  |       |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                 |

| 88h     | EECON1 | —        | _                       | _     | EEIF  | WRERR | WREN  | WR    | RD    | 0 x000                        | 0 q000                    |

| 89h     | EECON2 | EEPROM   | PROM control register 2 |       |       |       |       |       |       |                               |                           |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by Data EEPROM.

#### TABLE 8-3 RESET CONDITION FOR PROGRAM COUNTER AND THE STATUS REGISTER

| Condition                           | Program Counter       | STATUS Register |

|-------------------------------------|-----------------------|-----------------|

| Power-on Reset                      | 000h                  | 0001 1xxx       |

| MCLR Reset during normal operation  | 000h                  | 000u uuuu       |

| MCLR Reset during SLEEP             | 000h                  | 0001 0uuu       |

| WDT Reset (during normal operation) | 000h                  | 0000 luuu       |

| WDT Wake-up                         | PC + 1                | uuu0 0uuu       |

| Interrupt wake-up from SLEEP        | PC + 1 <sup>(1)</sup> | uuul 0uuu       |

Legend: u = unchanged, x = unknown.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| Register   | Address | Power-on Reset | MCLR Reset during:<br>– normal operation<br>– SLEEP<br>WDT Reset during nor-<br>mal operation | Wake-up from SLEEP:<br>– through interrupt<br>– through WDT Time-out |

|------------|---------|----------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| W          | _       | XXXX XXXX      | นนนน นนนน                                                                                     | սսսս սսսս                                                            |

| INDF       | 00h     |                |                                                                                               |                                                                      |

| TMR0       | 01h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| PCL        | 02h     | 0000h          | 0000h                                                                                         | PC + 1 <sup>(2)</sup>                                                |

| STATUS     | 03h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                                      | uuuq quuu <sup>(3)</sup>                                             |

| FSR        | 04h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| PORTA      | 05h     | x xxxx         | u uuuu                                                                                        | u uuuu                                                               |

| PORTB      | 06h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| EEDATA     | 08h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| EEADR      | 09h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| PCLATH     | 0Ah     | 0 0000         | 0 0000                                                                                        | u uuuu                                                               |

| INTCON     | 0Bh     | 0000 000x      | 0000 000u                                                                                     | uuuu uuuu <sup>(1)</sup>                                             |

| INDF       | 80h     |                |                                                                                               |                                                                      |

| OPTION_REG | 81h     | 1111 1111      | 1111 1111                                                                                     | uuuu uuuu                                                            |

| PCL        | 82h     | 0000h          | 0000h                                                                                         | PC + 1                                                               |

| STATUS     | 83h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                                      | uuuq quuu <sup>(3)</sup>                                             |

| FSR        | 84h     | xxxx xxxx      | uuuu uuuu                                                                                     | uuuu uuuu                                                            |

| TRISA      | 85h     | 1 1111         | 1 1111                                                                                        | u uuuu                                                               |

| TRISB      | 86h     | 1111 1111      | 1111 1111                                                                                     | սսսս սսսս                                                            |

| EECON1     | 88h     | 0 x000         | 0 q000                                                                                        | 0 uuuu                                                               |

| EECON2     | 89h     |                |                                                                                               |                                                                      |

| PCLATH     | 8Ah     | 0 0000         | 0 0000                                                                                        | u uuuu                                                               |

| INTCON     | 8Bh     | 0000 000x      | 0000 000u                                                                                     | uuuu uuuu <sup>(1)</sup>                                             |

#### TABLE 8-4 RESET CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0',

q = value depends on condition.

Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: Table 8-3 lists the reset value for each specific condition.

#### 8.12.3 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### 8.13 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting widowed devices.               |

#### 8.14 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations to store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable only during program/verify. Only the 4 least significant bits of ID location are usable.

For ROM devices, these values are submitted along with the ROM code.

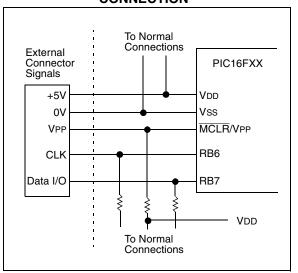

#### 8.15 In-Circuit Serial Programming

PIC16F8X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. Customers can manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product, allowing the most recent firmware or custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low, while raising the MCLR pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) points to location 00h. A 6-bit command is then supplied to the device, 14-bits of program data is then supplied to or from the device, using load or read-type instructions. For complete details of serial programming, please refer to the PIC16CXX Programming Specifications (Literature #DS30189).

#### FIGURE 8-20: TYPICAL IN-SYSTEM SERIAL PROGRAMMING CONNECTION

For ROM devices, both the program memory and Data EEPROM memory may be read, but only the Data EEPROM memory may be programmed.

| INCFSZ            | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IORLW             | Inclusive OR Literal with W                                                   |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------|

| Syntax:           | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Syntax:           | [ <i>label</i> ] IORLW k                                                      |

| Operands:         | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Operands:         | $0 \le k \le 255$                                                             |

|                   | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Operation:        | (W) .OR. $k \rightarrow$ (W)                                                  |

| Operation:        | (f) + 1 $\rightarrow$ (destination),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Status Affected:  | Z                                                                             |

|                   | skip if result = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Encoding:         | 11 1000 kkkk kkkk                                                             |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Description:      | The contents of the W register is                                             |

| Encoding:         | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   | OR'ed with the eight bit literal 'k'. The result is placed in the W register. |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Words:            | 1                                                                             |

|                   | the W register. If 'd' is 1 the result is<br>placed back in register 'f'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cycles:           | 1                                                                             |

|                   | If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is exe-<br>cuted instead making it a 2TCY instruc-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                   |

|                   | cuted instead making it a 2TCY instruc-<br>tion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q Cycle Activity. | Decode Read Process Write to                                                  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   | literal 'k' data W                                                            |

| Cycles:           | 1(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |                                                                               |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Example           | IORLW 0x35                                                                    |

|                   | Decode Read Process Write to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   | Before Instruction<br>W = 0x9A                                                |

|                   | register 'f' data destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   | After Instruction                                                             |

| If Skip:          | (2nd Cycle)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   | W = 0xBF<br>Z = 1                                                             |

|                   | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   | $\mathcal{L} = 1$                                                             |

|                   | No-Operation No- |                   |                                                                               |

| Example           | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                                                                               |

|                   | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1<br>if CNT= 0,<br>PC = address CONTINUE<br>if CNT $\neq$ 0,<br>PC = address HERE +1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                                                                               |

| RLF               | Rotate Left f throug                                                                                                                         | gh Carry                                      | RRF               | Rotate Right f through Carry                                                                                                                                                                                                                                  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [label] RI                                                                                                                                   | lLF f,d                                       | Syntax:           | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                                                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                            |                                               | Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                            |

| Operation:        | See description belo                                                                                                                         | WC                                            | Operation:        | See description below                                                                                                                                                                                                                                         |

| Status Affected:  | С                                                                                                                                            |                                               | Status Affected:  | С                                                                                                                                                                                                                                                             |

| Encoding:         | 00 1101 d                                                                                                                                    | lfff ffff                                     | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                                                                             |

| Description:      | The contents of registe<br>one bit to the left throug<br>Flag. If 'd' is 0 the resul<br>W register. If 'd' is 1 the<br>back in register 'f'. | igh the Carry<br>It is placed in the          | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.                                                  |

| Words:            | 1                                                                                                                                            |                                               | Words:            | 1                                                                                                                                                                                                                                                             |

| Cycles:           | 1                                                                                                                                            |                                               | Cycles:           | 1                                                                                                                                                                                                                                                             |

| Q Cycle Activity: | Q1 Q2                                                                                                                                        | Q3 Q4                                         | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                   |