Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | 36 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

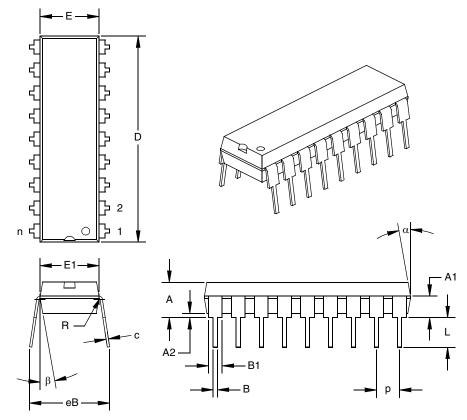

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf83-04-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1 PIC16F8X FAMILY OF DEVICES

|             |                                         | PIC16F83            | PIC16CR83           | PIC16F84            | PIC16CR84           |

|-------------|-----------------------------------------|---------------------|---------------------|---------------------|---------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz) | 10                  | 10                  | 10                  | 10                  |

|             | Flash Program Memory                    | 512                 | —                   | 1K                  | —                   |

|             | EEPROM Program Memory                   | —                   | —                   | —                   | —                   |

| Memory      | ROM Program Memory                      | —                   | 512                 | —                   | 1K                  |

|             | Data Memory (bytes)                     | 36                  | 36                  | 68                  | 68                  |

|             | Data EEPROM (bytes)                     | 64                  | 64                  | 64                  | 64                  |

| Peripherals | Timer Module(s)                         | TMR0                | TMR0                | TMR0                | TMR0                |

|             | Interrupt Sources                       | 4                   | 4                   | 4                   | 4                   |

|             | I/O Pins                                | 13                  | 13                  | 13                  | 13                  |

| Features    | Voltage Range (Volts)                   | 2.0-6.0             | 2.0-6.0             | 2.0-6.0             | 2.0-6.0             |

|             | Packages                                | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC |

All PIC<sup>®</sup> Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16F8X Family devices use serial programming with clock pin RB6 and data pin RB7.

## 2.0 PIC16F8X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in this section. When placing orders, please use the "PIC16F8X Product Identification System" at the back of this data sheet to specify the correct part number.

There are four device "types" as indicated in the device number.

- 1. **F**, as in PIC16**F**84. These devices have Flash program memory and operate over the standard voltage range.

- LF, as in PIC16LF84. These devices have Flash program memory and operate over an extended voltage range.

- 3. **CR**, as in PIC16**CR**83. These devices have ROM program memory and operate over the standard voltage range.

- 4. **LCR**, as in PIC16**LCR**84. These devices have ROM program memory and operate over an extended voltage range.

When discussing memory maps and other architectural features, the use of **F** and **CR** also implies the **LF** and **LCR** versions.

#### 2.1 Flash Devices

These devices are offered in the lower cost plastic package, even though the device can be erased and reprogrammed. This allows the same device to be used for prototype development and pilot programs as well as production.

A further advantage of the electrically-erasable Flash version is that it can be erased and reprogrammed incircuit, or by device programmers, such as Microchip's PICSTART<sup>®</sup> Plus or PRO MATE<sup>®</sup> II programmers.

#### 2.2 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices have all Flash locations and configuration options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available.

For information on submitting a QTP code, please contact your Microchip Regional Sales Office.

#### 2.3 <u>Serialized Quick-Turnaround-</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers the unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

For information on submitting a SQTP code, please contact your Microchip Regional Sales Office.

### 2.4 ROM Devices

Some of Microchip's devices have a corresponding device where the program memory is a ROM. These devices give a cost savings over Microchip's traditional user programmed devices (EPROM, EEPROM).

ROM devices (PIC16CR8X) do not allow serialization information in the program memory space. The user may program this information into the Data EEPROM.

For information on submitting a ROM code, please contact your Microchip Regional Sales Office.

### TABLE 4-1 REGISTER FILE SUMMARY

| Address | Name                  | Bit 7     | Bit 6        | Bit 5        | Bit 4             | Bit 3          | Bit 2         | Bit 1 | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note3) |

|---------|-----------------------|-----------|--------------|--------------|-------------------|----------------|---------------|-------|---------|-------------------------------|-----------------------------------------|

| Bank 0  |                       |           |              |              | •                 |                |               |       |         |                               | •                                       |

| 00h     | INDF                  | Uses co   | ntents of F  | SR to addre  | ess data memor    | y (not a phys  | sical registe | r)    |         |                               |                                         |

| 01h     | TMR0                  | 8-bit rea | I-time clock | /counter     |                   |                |               |       |         | xxxx xxxx                     | uuuu uuuu                               |

| 02h     | PCL                   | Low ord   | er 8 bits of | the Program  | m Counter (PC)    |                |               |       |         | 0000 0000                     | 0000 0000                               |

| 03h     | STATUS <sup>(2)</sup> | IRP       | RP1          | RP0          | TO                | PD             | Z             | DC    | С       | 0001 1xxx                     | 000q quuu                               |

| 04h     | FSR                   | Indirect  | data memo    | ry address   | pointer 0         |                |               |       |         | xxxx xxxx                     | uuuu uuuu                               |

| 05h     | PORTA                 | —         | —            | _            | RA4/T0CKI         | RA3            | RA2           | RA1   | RA0     | x xxxx                        | u uuuu                                  |

| 06h     | PORTB                 | RB7       | RB6          | RB5          | RB4               | RB3            | RB2           | RB1   | RB0/INT | XXXX XXXX                     | uuuu uuuu                               |

| 07h     |                       | Unimple   | mented loc   | ation, read  | as '0'            |                |               | •     | •       |                               |                                         |

| 08h     | EEDATA                | EEPRO     | V data regi  | ster         |                   |                |               |       |         | XXXX XXXX                     | uuuu uuuu                               |

| 09h     | EEADR                 | EEPROI    | M address    | register     |                   |                |               |       |         | XXXX XXXX                     | uuuu uuuu                               |

| 0Ah     | PCLATH                | _         |              | _            | Write buffer for  | r upper 5 bit  | s of the PC   | (1)   |         | 0 0000                        | 0 0000                                  |

| 0Bh     | INTCON                | GIE       | EEIE         | TOIE         | INTE              | RBIE           | TOIF          | INTF  | RBIF    | 0000 000x                     | 0000 000u                               |

| Bank 1  |                       |           |              |              |                   |                |               |       |         |                               |                                         |

| 80h     | INDF                  | Uses co   | ntents of F  | SR to addre  | ess data memor    | y (not a phys  | sical registe | r)    |         |                               |                                         |

| 81h     | OPTION_<br>REG        | RBPU      | INTEDG       | TOCS         | TOSE              | PSA            | PS2           | PS1   | PS0     | 1111 1111                     | 1111 1111                               |

| 82h     | PCL                   | Low ord   | er 8 bits of | Program C    | ounter (PC)       |                |               | •     | •       | 0000 0000                     | 0000 0000                               |

| 83h     | STATUS (2)            | IRP       | RP1          | RP0          | TO                | PD             | Z             | DC    | С       | 0001 1xxx                     | 000q quuu                               |

| 84h     | FSR                   | Indirect  | data memo    | ry address   | pointer 0         |                |               |       |         | xxxx xxxx                     | uuuu uuuu                               |

| 85h     | TRISA                 | —         | —            | —            | PORTA data d      | irection regis | ster          |       |         | 1 1111                        | 1 1111                                  |

| 86h     | TRISB                 | PORTB     | data directi | on register  | •                 |                |               |       |         | 1111 1111                     | 1111 1111                               |

| 87h     |                       | Unimple   | mented loc   | ation, read  | as '0'            |                |               |       |         |                               |                                         |

| 88h     | EECON1                | —         | —            | _            | EEIF              | WRERR          | WREN          | WR    | RD      | 0 x000                        | 0 q000                                  |

| 89h     | EECON2                | EEPRO     | V control re | gister 2 (no | ot a physical reg | ister)         | -             |       |         |                               |                                         |

| 0Ah     | PCLATH                | _         | _            | _            | Write buffer for  | r upper 5 bit  | s of the PC   | (1)   |         | 0 0000                        | 0 0000                                  |

| 0Bh     | INTCON                | GIE       | EEIE         | TOIE         | INTE              | RBIE           | TOIF          | INTF  | RBIF    | 0000 000x                     | 0000 000u                               |

Legend: x = unknown, u = unchanged. - = unimplemented read as '0', q = value depends on condition.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a slave register for PC<12:8>. The contents of PCLATH can be transferred to the upper byte of the program counter, but the contents of PC<12:8> is never transferred to PCLATH.

2: The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  status bits in the STATUS register are not affected by a  $\overline{\text{MCLR}}$  reset.

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

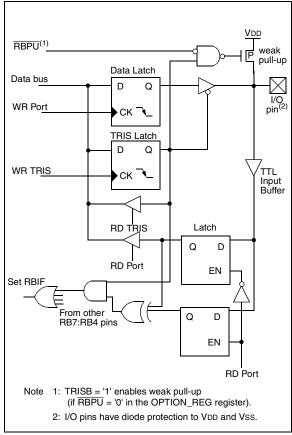

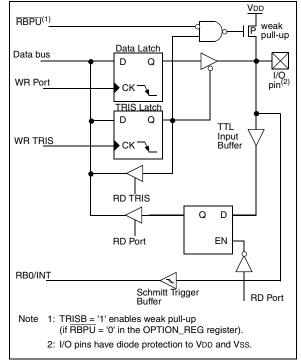

#### 5.2 **PORTB and TRISB Registers**

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' on any bit in the TRISB register puts the corresponding output driver in a hi-impedance mode. A '0' on any bit in the TRISB register puts the contents of the output latch on the selected pin(s).

Each of the PORTB pins have a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION\_REG<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The pins value in input mode are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of the pins are OR'ed together to generate the RB port change interrupt.

#### FIGURE 5-3: BLOCK DIAGRAM OF PINS RB7:RB4

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Read (or write) PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set the RBIF bit. Reading PORTB will end the mismatch condition, and allow the RBIF bit to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression (see AN552 in the Embedded Control Handbook).

Note 1: For a change on the I/O pin to be recognized, the pulse width must be at least TcY (4/fosc) wide.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

#### FIGURE 5-4: BLOCK DIAGRAM OF PINS RB3:RB0

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution).

Note: To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be taken even if the WDT is disabled. To change prescaler from the WDT to the Timer0 module use the sequence shown in Example 6-2.

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|        | •           | ,                |

|--------|-------------|------------------|

| BCF    | STATUS, RPO | ;Bank 0          |

| CLRF   | TMR0        | ;Clear TMR0      |

|        |             | ; and Prescaler  |

| BSF    | STATUS, RPO | ;Bank 1          |

| CLRWDT |             | ;Clears WDT      |

| MOVLW  | b'xxxx1xxx' | ;Select new      |

| MOVWF  | OPTION_REG  | ; prescale value |

| BCF    | STATUS, RPO | ;Bank 0          |

|        |             |                  |

#### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

|        | (=.         | / · · · · · · · · · · · · · · · · · · · |

|--------|-------------|-----------------------------------------|

| CLRWDT |             | ;Clear WDT and                          |

|        |             | ; prescaler                             |

| BSF    | STATUS, RPO | ;Bank 1                                 |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new                       |

|        |             | ; prescale value                        |

|        |             | ' and clock source                      |

| MOVWF  | OPTION_REG  | ;                                       |

| BCF    | STATUS, RPO | ;Bank 0                                 |

|        |             |                                         |

| Address | Name           | Bit 7 | Bit 6  | Bit 5     | Bit 4     | Bit 3  | Bit 2 Bit 1 |        | Bit 0  | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|----------------|-------|--------|-----------|-----------|--------|-------------|--------|--------|-------------------------------|---------------------------|

| 01h     | TMR0           |       |        | xxxx xxxx | uuuu uuuu |        |             |        |        |                               |                           |

| 0Bh     | INTCON         | GIE   | EEIE   | TOIE      | INTE      | RBIE   | T0IF        | INTF   | RBIF   | 0000 000x                     | 0000 0000                 |

| 81h     | OPTION_<br>REG | RBPU  | INTEDG | TOCS      | TOSE      | PSA    | PS2         | PS1    | PS0    | 1111 1111                     | 1111 1111                 |

| 85h     | TRISA          | _     | _      | _         | TRISA4    | TRISA3 | TRISA2      | TRISA1 | TRISA0 | 1 1111                        | 1 1111                    |

### TABLE 6-1 REGISTERS ASSOCIATED WITH TIMER0

Legend: x = unknown, u = unchanged. - = unimplemented read as '0'. Shaded cells are not associated with Timer0.

#### 8.1 <u>Configuration Bits</u>

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

Address 2007h is beyond the user program memory space and it belongs to the special test/configuration memory space (2000h - 3FFFh). This space can only be accessed during programming.

To find out how to program the PIC16C84, refer to *PIC16C84 EEPROM Memory Programming Specifica-tion* (DS30189).

### FIGURE 8-1: CONFIGURATION WORD - PIC16CR83 AND PIC16CR84

| D.u       | <b>D</b>                                                                                                                                      | <b>D</b>                                         | <b>D</b>                     | <b>D</b>  | <b>D</b>  | D/D         | <b>D</b>  | D         | <b>D</b>  | <b>D</b>     | <b>D</b>    | D                                 | D                                                      |   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------|-----------|-----------|-------------|-----------|-----------|-----------|--------------|-------------|-----------------------------------|--------------------------------------------------------|---|

| R-u<br>CP | R-u<br>CP                                                                                                                                     | R-u<br>CP                                        | R-u<br>CP                    | R-u<br>CP | R-u<br>CP | R/P-u<br>DP | R-u<br>CP | R-u<br>CP | R-u<br>CP | R-u<br>PWRTE | R-u<br>WDTE | R-u<br>FOSC1                      | R-u<br>FOSC0                                           |   |

| bit13     |                                                                                                                                               | 01                                               | 01                           |           |           |             | 01        |           | 01        |              |             | R = Rea<br>P = Prog<br>- n = Valu | bit0<br>adable bit<br>grammable bit<br>ue at POR reset | t |

| bit 13:8  | <ul> <li>3:8 CP: Program Memory Code Protection bit</li> <li>1 = Code protection off</li> <li>0 = Program memory is code protected</li> </ul> |                                                  |                              |           |           |             |           |           |           |              |             |                                   |                                                        |   |

| bit 7     | <ul> <li>DP: Data Memory Code Protection bit</li> <li>1 = Code protection off</li> <li>0 = Data memory is code protected</li> </ul>           |                                                  |                              |           |           |             |           |           |           |              |             |                                   |                                                        |   |

| bit 6:4   | 1 = 0                                                                                                                                         | Program<br>Code pro<br>Program                   | tection                      | off       |           |             | it        |           |           |              |             |                                   |                                                        |   |

| bit 3     | 1 = F                                                                                                                                         | RTE: Pov<br>Power-up<br>Power-up                 | timer                        | is disal  | oled      | bit         |           |           |           |              |             |                                   |                                                        |   |

| bit 2     | 1 = V                                                                                                                                         | E: Wato<br>VDT ena<br>VDT disa                   | abled                        | imer E    | nable I   | oit         |           |           |           |              |             |                                   |                                                        |   |

| bit 1:0   | 11 =<br>10 =<br>01 =                                                                                                                          | C1:FOS<br>RC osc<br>HS osc<br>XT osci<br>LP osci | illator<br>illator<br>llator | cillator  | Selec     | tion bits   |           |           |           |              |             |                                   |                                                        |   |

# FIGURE 8-4: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

Clock from OSC1 ext. system Open OSC2

# TABLE 8-1CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Ranges Tested:                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |             |             |  |  |  |  |  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|--|--|--|--|--|

| Mode                                                     | Freq                                                                                                                                                                                                                                                                                                                                                                                                         | OSC2/C2     |             |  |  |  |  |  |

| XT                                                       | 455 kHz                                                                                                                                                                                                                                                                                                                                                                                                      | 47 - 100 pF | 47 - 100 pF |  |  |  |  |  |

|                                                          | 2.0 MHz                                                                                                                                                                                                                                                                                                                                                                                                      | 15 - 33 pF  | 15 - 33 pF  |  |  |  |  |  |

|                                                          | 4.0 MHz                                                                                                                                                                                                                                                                                                                                                                                                      | 15 - 33 pF  | 15 - 33 pF  |  |  |  |  |  |

| HS                                                       | 8.0 MHz                                                                                                                                                                                                                                                                                                                                                                                                      | 15 - 33 pF  | 15 - 33 pF  |  |  |  |  |  |

|                                                          | 10.0 MHz                                                                                                                                                                                                                                                                                                                                                                                                     | 15 - 33 pF  | 15 - 33 pF  |  |  |  |  |  |

| the ran<br>Highe<br>oscilla<br>These<br>each r<br>should | Note :       Recommended values of C1 and C2 are identical to the ranges tested table.         Higher capacitance increases the stability of the oscillator but also increases the start-up time.         These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for the appropriate values of external components. |             |             |  |  |  |  |  |

| 455 kHz                                                  | Panasonic E                                                                                                                                                                                                                                                                                                                                                                                                  | FO-A455K04E | 3 ± 0.3%    |  |  |  |  |  |

| 2.0 MHz                                                  | Murata Erie                                                                                                                                                                                                                                                                                                                                                                                                  | CSA2.00MG   | ± 0.5%      |  |  |  |  |  |

| 4.0 MHz                                                  | Murata Erie                                                                                                                                                                                                                                                                                                                                                                                                  | CSA4.00MG   | $\pm 0.5\%$ |  |  |  |  |  |

| 8.0 MHz                                                  | Murata Erie                                                                                                                                                                                                                                                                                                                                                                                                  | CSA8.00MT   | $\pm 0.5\%$ |  |  |  |  |  |

| 10.0 MHz                                                 | Murata Erie                                                                                                                                                                                                                                                                                                                                                                                                  | CSA10.00MT2 | Z ±0.5%     |  |  |  |  |  |

None of the resonators had built-in capacitors.

# TABLE 8-2CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Mode                                              | Freq                                                                                                                                                | OSC1/C1      | OSC2/C2                                                                                                            |  |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| LP                                                | 32 kHz                                                                                                                                              | 68 - 100 pF  | 68 - 100 pF                                                                                                        |  |  |

|                                                   | 200 kHz                                                                                                                                             | 15 - 33 pF   | 15 - 33 pF                                                                                                         |  |  |

| XT                                                | 100 kHz                                                                                                                                             | 100 - 150 pF | 100 - 150 pF                                                                                                       |  |  |

|                                                   | 2 MHz                                                                                                                                               | 15 - 33 pF   | 15 - 33 pF                                                                                                         |  |  |

|                                                   | 4 MHz                                                                                                                                               | 15 - 33 pF   | 15 - 33 pF                                                                                                         |  |  |

| HS                                                | 4 MHz                                                                                                                                               | 15 - 33 pF   | 15 - 33 pF                                                                                                         |  |  |

|                                                   | 10 MHz                                                                                                                                              | 15 - 33 pF   | 15 - 33 pF                                                                                                         |  |  |

| os<br>Th<br>be<br>avv<br>fica<br>tice<br>ma<br>co | cillator but also<br>esse values are<br>required in HS<br>oid overdriving<br>ation. Since eac<br>s, the user shou<br>anufacturer for a<br>mponents. | •            | art-up time.<br>nee only. Rs may<br>XT mode to<br>drive level speci-<br>own characteris-<br>ystal<br>s of external |  |  |

| Crystals Tested:                          |                       |              |  |  |  |  |  |  |

|-------------------------------------------|-----------------------|--------------|--|--|--|--|--|--|

| 32.768 kHz Epson C-001R32.768K-A ± 20 PPM |                       |              |  |  |  |  |  |  |

| 100 kHz                                   | Epson C-2 100.00 KC-P | $\pm$ 20 PPM |  |  |  |  |  |  |

| 200 kHz                                   | STD XTL 200.000 KHz   | $\pm$ 20 PPM |  |  |  |  |  |  |

| 1.0 MHz                                   | ECS ECS-10-13-2       | $\pm$ 50 PPM |  |  |  |  |  |  |

| 2.0 MHz                                   | ECS ECS-20-S-2        | $\pm$ 50 PPM |  |  |  |  |  |  |

| 4.0 MHz                                   | ECS ECS-40-S-4        | $\pm$ 50 PPM |  |  |  |  |  |  |

| 10.0 MHz                                  | ECS ECS-100-S-4       | $\pm$ 50 PPM |  |  |  |  |  |  |

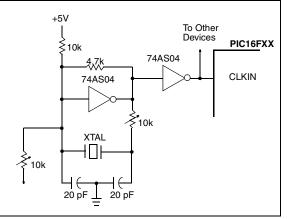

#### 8.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits are available; one with series resonance, and one with parallel resonance.

Figure 8-5 shows a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 8-5: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

Figure 8-6 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### 8.12.3 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### 8.13 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting widowed devices.               |

#### 8.14 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations to store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable only during program/verify. Only the 4 least significant bits of ID location are usable.

For ROM devices, these values are submitted along with the ROM code.

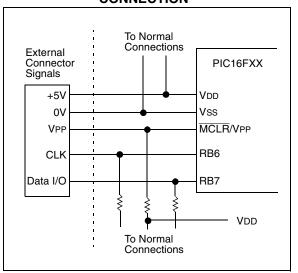

### 8.15 In-Circuit Serial Programming

PIC16F8X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. Customers can manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product, allowing the most recent firmware or custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low, while raising the MCLR pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) points to location 00h. A 6-bit command is then supplied to the device, 14-bits of program data is then supplied to or from the device, using load or read-type instructions. For complete details of serial programming, please refer to the PIC16CXX Programming Specifications (Literature #DS30189).

#### FIGURE 8-20: TYPICAL IN-SYSTEM SERIAL PROGRAMMING CONNECTION

For ROM devices, both the program memory and Data EEPROM memory may be read, but only the Data EEPROM memory may be programmed.

| BTFSS             | Bit Test f, Skip if Set                                                   |                        |                              |                  | CALL              | Call Sub                                           | oroutine                             |                                                                               |                                             |  |

|-------------------|---------------------------------------------------------------------------|------------------------|------------------------------|------------------|-------------------|----------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------|--|

| Syntax:           | [ <i>label</i> ] BTFS                                                     | SS f,b                 |                              |                  | Syntax:           | [ label ]                                          | CALL 4                               | K                                                                             |                                             |  |

| Operands:         | $0 \leq f \leq 127$                                                       |                        |                              |                  | Operands:         | $0 \le k \le 2047$                                 |                                      |                                                                               |                                             |  |

|                   | 0 ≤ b < 7                                                                 |                        |                              |                  | Operation:        | (PC)+ 1-                                           | → TOS,                               |                                                                               |                                             |  |

| Operation:        | skip if (f <b></b>                                                        | >) = 1                 |                              |                  | ·                 | $k \rightarrow PC <$                               | ,                                    |                                                                               |                                             |  |

| Status Affected:  | None                                                                      |                        |                              |                  |                   | (PCLATH                                            | H<4:3>) -                            | → PC<12                                                                       | :11>                                        |  |

| Encoding:         | 01 1                                                                      | 11bb                   | bfff                         | ffff             | Status Affected:  | None                                               |                                      |                                                                               |                                             |  |

| Description:      | If bit 'b' in reg                                                         | gister 'f' is          | i'0' then th                 | ne next          | Encoding:         | 10                                                 | 0kkk                                 | kkkk                                                                          | kkkk                                        |  |

| Words:            | instruction is<br>If bit 'b' is '1',<br>discarded an<br>instead, mak<br>1 | , then the<br>nd a NOP | next instruction is executed | ed               | Description:      | (PC+1) is<br>eleven bit<br>into PC bi<br>the PC ar | pushed or<br>immediate<br>ts <10:0>. | at, return ac<br>nto the stac<br>address i<br>The upper<br>om PCLAT<br>ction. | ck. The<br>s loaded<br><sup>r</sup> bits of |  |

| Cycles:           | 1(2)                                                                      |                        |                              |                  | Words:            | 1                                                  | , 010 111011 0                       |                                                                               |                                             |  |

| Q Cycle Activity: | Q1                                                                        | Q2                     | Q3                           | Q4               | Cycles:           | 2                                                  |                                      |                                                                               |                                             |  |

|                   | Decode                                                                    | Read<br>register 'f'   | Process<br>data              | No-Operat<br>ion | Q Cycle Activity: | Q1                                                 | Q2                                   | Q3                                                                            | Q4                                          |  |

| If Skip:          | (2nd Cycle)                                                               | .)                     |                              |                  | 1st Cycle         | Decode                                             | Read<br>literal 'k',                 | Process<br>data                                                               | Write to<br>PC                              |  |

|                   | Q1                                                                        | Q2                     | Q3                           | Q4               |                   |                                                    | Push PC<br>to Stack                  | ullu                                                                          | 10                                          |  |

|                   | No-Operat<br>ion                                                          | lo-Operati<br>on       | No-Opera<br>tion             | No-Operat<br>ion | 2nd Cycle         | No-Opera<br>tion                                   | No-Opera<br>tion                     | No-Opera<br>tion                                                              | No-Operat<br>ion                            |  |

| Example           |                                                                           |                        | FLAG,1<br>PROCESS            | CODE             | Example           | HERE                                               | CALL                                 | THERE                                                                         |                                             |  |

|                   | TRUE •                                                                    | •                      |                              |                  |                   | Before Ir                                          | nstruction                           |                                                                               |                                             |  |

|                   | •                                                                         | •                      |                              |                  |                   | After Ins                                          | -                                    | ddress HE                                                                     | RE                                          |  |

|                   | Before Instr                                                              | ruction                |                              |                  |                   |                                                    |                                      | ddress TH                                                                     | ERE                                         |  |

|                   |                                                                           |                        | ddress H                     | IERE             |                   |                                                    | TOS = A                              | ddress HE                                                                     | RE+1                                        |  |

|                   | After Instruc                                                             |                        |                              |                  |                   |                                                    |                                      |                                                                               |                                             |  |

|                   |                                                                           | FLAG<1>                |                              |                  |                   |                                                    |                                      |                                                                               |                                             |  |

|                   |                                                                           | C = a<br>FLAG<1>       | address Fi<br>$\cdot = 1$ .  | ALSE             |                   |                                                    |                                      |                                                                               |                                             |  |

|                   |                                                                           |                        | address TI                   | RUE              |                   |                                                    |                                      |                                                                               |                                             |  |

| GOTO              | Uncondition                                                                                                                                                                                   | nal Brar            | nch              |                  | INCF              | Increme                                                                                                                                                             | ent f                   |                 |                      |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------|

| Syntax:           | [ <i>label</i> ] GOTO k                                                                                                                                                                       |                     |                  |                  | Syntax:           | [ label ]                                                                                                                                                           | [label] INCF f,d        |                 |                      |

| Operands:         | $0 \le k \le 2047$                                                                                                                                                                            | 7                   |                  |                  | Operands:         | $0 \le f \le 1$<br>$d \in [0,1]$                                                                                                                                    |                         |                 |                      |

| Operation:        | $k \rightarrow PC < 10$ :<br>PCLATH < 4:3                                                                                                                                                     | -                   | C<12:11          | >                | Operation:        | (f) + 1 $\rightarrow$ (destination)                                                                                                                                 |                         |                 |                      |

| Status Affected:  | None                                                                                                                                                                                          |                     |                  |                  | Status Affected:  | Z                                                                                                                                                                   |                         |                 |                      |

| Encoding:         | 10 1]                                                                                                                                                                                         | .kkk [              | kkkk             | kkkk             | Encoding:         | 0 0                                                                                                                                                                 | 1010                    | dfff            | ffff                 |

| Description:      | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. |                     |                  |                  | Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |                         |                 | placed in            |

| Words:            | 1                                                                                                                                                                                             | ,                   |                  |                  | Words:            | 1                                                                                                                                                                   |                         |                 |                      |

| Cycles:           | 2                                                                                                                                                                                             |                     |                  |                  | Cycles:           | 1                                                                                                                                                                   |                         |                 |                      |

| Q Cycle Activity: |                                                                                                                                                                                               | Q2                  | Q3               | Q4               | Q Cycle Activity: | Q1                                                                                                                                                                  | Q2                      | Q3              | Q4                   |

| 1st Cycle         |                                                                                                                                                                                               | Read I<br>teral 'k' | Process<br>data  | Write to<br>PC   |                   | Decode                                                                                                                                                              | Read<br>register<br>'f' | Process<br>data | Write to destination |

| 2nd Cycle         |                                                                                                                                                                                               | o-Operat N<br>ion   | No-Opera<br>tion | No-Operat<br>ion | Example           | INCF                                                                                                                                                                | CNT,                    | 1               | II                   |

| Example           | GOTO THER                                                                                                                                                                                     |                     |                  |                  |                   | Before I                                                                                                                                                            | nstruction<br>CNT<br>Z  | = 0xFl<br>= 0   | Ŧ                    |

|                   | PC                                                                                                                                                                                            |                     | ddress 1         | THERE            |                   | After Ins                                                                                                                                                           | truction<br>CNT<br>Z    | = 0x00<br>= 1   | )                    |

| IORWF             | Inclusive                                                                                                                                                            | OR W                    | with f           |                      |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------|----------------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                            | IORWF                   | f,d              |                      |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                                                                                                       | 27                      |                  |                      |  |  |  |

| Operation:        | (W) .OR.                                                                                                                                                             | $(f) \rightarrow (de)$  | estinatior       | ı)                   |  |  |  |

| Status Affected:  | Z                                                                                                                                                                    |                         |                  |                      |  |  |  |

| Encoding:         | 00                                                                                                                                                                   | 0100                    | dfff             | ffff                 |  |  |  |

| Description:      | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'. |                         |                  |                      |  |  |  |

| Words:            | 1                                                                                                                                                                    |                         |                  |                      |  |  |  |

| Cycles:           | 1                                                                                                                                                                    |                         |                  |                      |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                   | Q2                      | Q3               | Q4                   |  |  |  |

|                   | Decode                                                                                                                                                               | Read<br>register<br>'f' | Process<br>data  | Write to destination |  |  |  |

| Example           | IORWF                                                                                                                                                                |                         | RESULT,          | 0                    |  |  |  |

|                   | Before In                                                                                                                                                            |                         |                  |                      |  |  |  |

|                   |                                                                                                                                                                      | RESULT<br>W             | = 0x13<br>= 0x91 | -                    |  |  |  |

|                   | After Inst                                                                                                                                                           | ••                      |                  | 3                    |  |  |  |

| MOVLW             | Move Lite                                                                                  | eral to V                         | v               |               |  |  |

|-------------------|--------------------------------------------------------------------------------------------|-----------------------------------|-----------------|---------------|--|--|

| Syntax:           | [ label ]                                                                                  | MOVLW                             | / k             |               |  |  |

| Operands:         | $0 \le k \le 25$                                                                           | 55                                |                 |               |  |  |

| Operation:        | $k \to (W)$                                                                                |                                   |                 |               |  |  |

| Status Affected:  | None                                                                                       |                                   |                 |               |  |  |

| Encoding:         | 11                                                                                         | 00xx                              | kkkk            | kkkk          |  |  |

| Description:      | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |                                   |                 |               |  |  |

| Words:            | 1                                                                                          |                                   |                 |               |  |  |

| Cycles:           | 1                                                                                          |                                   |                 |               |  |  |

| Q Cycle Activity: | Q1                                                                                         | Q2                                | Q3              | Q4            |  |  |

|                   | Decode                                                                                     | Read<br>literal 'k'               | Process<br>data | Write to<br>W |  |  |

| Example           | MOVLW<br>After Instr                                                                       | <sup>0x5A</sup><br>ruction<br>N = | 0x5A            |               |  |  |

| MOVF                                                   | Move f                                                                                                                                                                                                                                                          |                                                                 |                 |                      |  |  |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------|----------------------|--|--|--|

| Syntax:                                                | [ label ]                                                                                                                                                                                                                                                       | MOVF                                                            | f,d             |                      |  |  |  |

| Operands:                                              | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                  | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ |                 |                      |  |  |  |

| Operation:                                             | (f) $\rightarrow$ (des                                                                                                                                                                                                                                          | stination                                                       | )               |                      |  |  |  |

| Status Affected:                                       | Z                                                                                                                                                                                                                                                               |                                                                 |                 |                      |  |  |  |

| Encoding:                                              | 00                                                                                                                                                                                                                                                              | 1000                                                            | dfff            | ffff                 |  |  |  |

| Description:                                           | The contents of register f is moved to a destination dependant upon the status of d. If $d = 0$ , destination is W register. If $d = 1$ , the destination is file register f itself. $d = 1$ is useful to test a file register since status flag Z is affected. |                                                                 |                 |                      |  |  |  |

| Words:                                                 | 1                                                                                                                                                                                                                                                               |                                                                 |                 |                      |  |  |  |

| Cycles:                                                | 1                                                                                                                                                                                                                                                               |                                                                 |                 |                      |  |  |  |

| Q Cycle Activity:                                      | Q1                                                                                                                                                                                                                                                              | Q2                                                              | Q3              | Q4                   |  |  |  |

|                                                        | Decode                                                                                                                                                                                                                                                          | Read<br>register<br>'f'                                         | Process<br>data | Write to destination |  |  |  |

|                                                        |                                                                                                                                                                                                                                                                 |                                                                 |                 |                      |  |  |  |

| Example                                                | MOVF                                                                                                                                                                                                                                                            | FSR,                                                            | 0               |                      |  |  |  |

| After Instruction<br>W = value in FSR registe<br>Z = 1 |                                                                                                                                                                                                                                                                 |                                                                 |                 |                      |  |  |  |

| MOVWF             | Move W to f                                                      |

|-------------------|------------------------------------------------------------------|

| Syntax:           | [label] MOVWF f                                                  |

| Operands:         | $0 \leq f \leq 127$                                              |

| Operation:        | $(W) \rightarrow (f)$                                            |

| Status Affected:  | None                                                             |

| Encoding:         | 00 0000 1fff fff                                                 |

| Description:      | Move data from W register to register<br>'f'.                    |

| Words:            | 1                                                                |

| Cycles:           | 1                                                                |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                      |

|                   | Decode Read register data register 'f'                           |

| Example           | MOVWF OPTION_REG                                                 |

|                   | Before Instruction                                               |

|                   | OPTION = 0xFF<br>W = 0x4F                                        |

|                   | After Instruction                                                |

|                   | $\begin{array}{rcl} OPTION &= & 0x4F \\ W &= & 0x4F \end{array}$ |

|                   | W = 0X4F                                                         |

| RETLW             | Return v                                  | vith Liter                | al in W                          |                                         | RETURN            | Return f                                                                                                  | rom Sub          | routine          |                  |

|-------------------|-------------------------------------------|---------------------------|----------------------------------|-----------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|

| Syntax:           | [ label ]                                 | RETLW                     | k                                |                                         | Syntax:           | [ label ]                                                                                                 | RETUR            | N                |                  |

| Operands:         | $0 \le k \le 255$                         |                           |                                  | Operands:                               | nds: None         |                                                                                                           |                  |                  |                  |

| Operation:        | $k \rightarrow (W);$                      |                           |                                  |                                         | Operation:        | $TOS \rightarrow F$                                                                                       | ъС               |                  |                  |

|                   | $TOS \rightarrow F$                       | ъС                        |                                  |                                         | Status Affected:  | None                                                                                                      |                  |                  |                  |

| Status Affected:  | None                                      |                           |                                  |                                         | Encoding:         | 00                                                                                                        | 0000             | 0000             | 1000             |

| Encoding:         | 11                                        | 01xx                      | kkkk                             | kkkk                                    | Description:      | Return fro                                                                                                | m subrout        | ine. The st      | ack is           |

| Description:      | The W reg<br>bit literal 'k<br>loaded fro | <. The pro                | gram coun                        | iter is                                 |                   | POPed and the top of the stack (TOS) is loaded into the program counter. This is a two cycle instruction. |                  |                  |                  |

|                   | return add                                | Iress). This              |                                  |                                         | Words:            | 1                                                                                                         |                  |                  |                  |